Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 368 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | A/D 8x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc77t-04i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 PIC16C7X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C7X Product Identification System section at the end of this data sheet. When placing orders, please use that page of the data sheet to specify the correct part number.

For the PIC16C7X family, there are two device "types" as indicated in the device number:

- 1. **C**, as in PIC16**C**74. These devices have EPROM type memory and operate over the standard voltage range.

- 2. LC, as in PIC16LC74. These devices have EPROM type memory and operate over an extended voltage range.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> Plus and PRO MATE<sup>®</sup> II programmers both support programming of the PIC16C7X.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

## 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

## 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random, or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password, or ID number.

#### TABLE 3-2:PIC16C73/73A/76 PINOUT DESCRIPTION

| Pin Name                | DIP<br>Pin# | SOIC<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                                  |

|-------------------------|-------------|--------------|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN              | 9           | 9            | I             | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                        |

| OSC2/CLKOUT             | 10          | 10           | 0             | -                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp                | 1           | 1            | I/P           | ST                     | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                      |

|                         |             |              |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                          |

| RA0/AN0                 | 2           | 2            | I/O           | TTL                    | RA0 can also be analog input0                                                                                                                                                                                |

| RA1/AN1                 | 3           | 3            | I/O           | TTL                    | RA1 can also be analog input1                                                                                                                                                                                |

| RA2/AN2                 | 4           | 4            | I/O           | TTL                    | RA2 can also be analog input2                                                                                                                                                                                |

| RA3/AN3/VREF            | 5           | 5            | I/O           | TTL                    | RA3 can also be analog input3 or analog reference voltage                                                                                                                                                    |

| RA4/T0CKI               | 6           | 6            | I/O           | ST                     | RA4 can also be the clock input to the Timer0 module.<br>Output is open drain type.                                                                                                                          |

| RA5/ <del>SS</del> /AN4 | 7           | 7            | I/O           | TTL                    | RA5 can also be analog input4 or the slave select for the<br>synchronous serial port.                                                                                                                        |

|                         |             |              |               |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT                 | 21          | 21           | I/O           | TTL/ST(1)              | RB0 can also be the external interrupt pin.                                                                                                                                                                  |

| RB1                     | 22          | 22           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB2                     | 23          | 23           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB3                     | 24          | 24           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB4                     | 25          | 25           | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |

| RB5                     | 26          | 26           | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |

| RB6                     | 27          | 27           | I/O           | TTL/ST(2)              | Interrupt on change pin. Serial programming clock.                                                                                                                                                           |

| RB7                     | 28          | 28           | I/O           | TTL/ST(2)              | Interrupt on change pin. Serial programming data.                                                                                                                                                            |

|                         |             |              |               |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                          |

| RC0/T1OSO/T1CKI         | 11          | 11           | I/O           | ST                     | RC0 can also be the Timer1 oscillator output or Timer1 clock input.                                                                                                                                          |

| RC1/T1OSI/CCP2          | 12          | 12           | I/O           | ST                     | RC1 can also be the Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output.                                                                                                                   |

| RC2/CCP1                | 13          | 13           | I/O           | ST                     | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                                                                                                                          |

| RC3/SCK/SCL             | 14          | 14           | I/O           | ST                     | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                           |

| RC4/SDI/SDA             | 15          | 15           | I/O           | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                              |

| RC5/SDO                 | 16          | 16           | I/O           | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |

| RC6/TX/CK               | 17          | 17           | I/O           | ST                     | RC6 can also be the USART Asynchronous Transmit of<br>Synchronous Clock.                                                                                                                                     |

| RC7/RX/DT               | 18          | 18           | I/O           | ST                     | RC7 can also be the USART Asynchronous Receive or<br>Synchronous Data.                                                                                                                                       |

| Vss                     | 8, 19       | 8, 19        | Р             | <u> </u>               | Ground reference for logic and I/O pins.                                                                                                                                                                     |

| VDD                     | 20          | 20           | P             | <u> </u>               | Positive supply for logic and I/O pins.                                                                                                                                                                      |

| Legend: I = input       | O = outp    |              |               | input/output           | P = power                                                                                                                                                                                                    |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

#### 4.0 MEMORY ORGANIZATION Applicable Devices

72 73 73A 74 74A 76 77

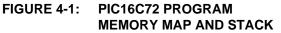

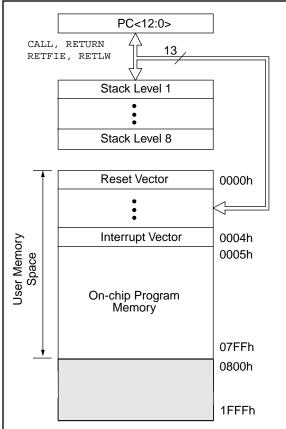

# 4.1 Program Memory Organization

The PIC16C7X family has a 13-bit program counter capable of addressing an  $8K \times 14$  program memory space. The amount of program memory available to each device is listed below:

| Device    | Program<br>Memory | Address Range |

|-----------|-------------------|---------------|

| PIC16C72  | 2K x 14           | 0000h-07FFh   |

| PIC16C73  | 4K x 14           | 0000h-0FFFh   |

| PIC16C73A | 4K x 14           | 0000h-0FFFh   |

| PIC16C74  | 4K x 14           | 0000h-0FFFh   |

| PIC16C74A | 4K x 14           | 0000h-0FFFh   |

| PIC16C76  | 8K x 14           | 0000h-1FFFh   |

| PIC16C77  | 8K x 14           | 0000h-1FFFh   |

For those devices with less than 8K program memory, accessing a location above the physically implemented address will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

# FIGURE 4-2: PIC16C73/73A/74/74A PROGRAM MEMORY MAP AND STACK

### TABLE 5-1: PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                                                       |

|--------------|------|--------|--------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF                                           |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0                                |

|              |      |        | Output is open drain type                                                      |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input |

Legend: TTL = TTL input, ST = Schmitt Trigger input

## TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5                         | Bit 4 | Bit 3 | Bit 2 |       |       | ,       | Value on all other resets |

|---------|--------|-------|-------|-------------------------------|-------|-------|-------|-------|-------|---------|---------------------------|

| 05h     | PORTA  | —     | _     | RA5                           | RA4   | RA3   | RA2   | RA1   | RA0   | 0x 0000 | 0u 0000                   |

| 85h     | TRISA  | —     | —     | PORTA Data Direction Register |       |       |       |       |       | 11 1111 | 11 1111                   |

| 9Fh     | ADCON1 | —     |       | —                             | _     | _     | PCFG2 | PCFG1 | PCFG0 | 000     | 000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

# 5.6 <u>I/O Programming Considerations</u> Applicable Devices 72 73 73A 74 74A 76 77

#### 5.6.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched to an output, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-4 shows the effect of two sequential readmodify-write instructions on an I/O port.

#### EXAMPLE 5-4: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings: PORTB<7:4> Inputs

; PORTB<3:0> Outputs

;PORTB<7:6> have external pull-ups and are

;not connected to other circuitry

| i |     |         |     |   |      |       |           |  |

|---|-----|---------|-----|---|------|-------|-----------|--|

| ; |     |         |     |   | PORT | latch | PORT pins |  |

| ; |     |         |     |   |      |       |           |  |

|   | BCF | PORTB,  | 7   | ; | 01pp | pppp  | 11pp pppp |  |

|   | BCF | PORTB,  | 6   | ; | 10pp | pppp  | llpp pppp |  |

|   | BSF | STATUS, | RP0 | ; |      |       |           |  |

|   | BCF | TRISB,  | 7   | ; | 10pp | pppp  | 11pp pppp |  |

|   | BCF | TRISB,  | 6   | ; | 10pp | pppp  | 10pp pppp |  |

| ; |     |         |     |   |      |       |           |  |

|   |     |         |     |   |      |       |           |  |

;Note that the user may have expected the ;pin values to be 00pp ppp. The 2nd BCF ;caused RB7 to be latched as the pin value ;(high).

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

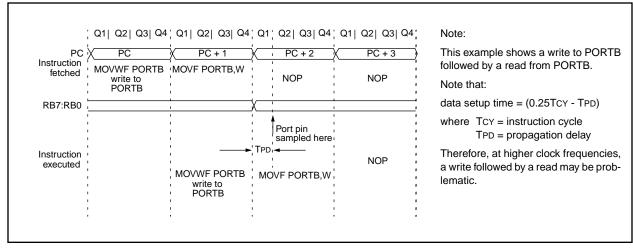

#### 5.6.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-10). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/ O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

## FIGURE 5-10: SUCCESSIVE I/O OPERATION

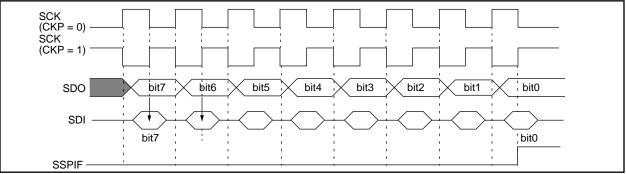

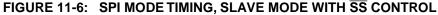

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode (SSPCON<3:0> = 04h) and the TRISA<5> bit must be set the for synchronous slave mode to be enabled. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. If the  $\overline{SS}$  pin is taken low without resetting SPI mode, the transmission will continue from the

point at which it was taken high. External pull-up/ pull-down resistors may be desirable, depending on the application.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

|  | <b>TABLE 11-1:</b> | <b>REGISTERS ASSOCIATED WITH SPI OPERATION</b> |

|--|--------------------|------------------------------------------------|

|--|--------------------|------------------------------------------------|

| Address | Name    | Bit 7                  | Bit 6       | Bit 5                         | Bit 4               | Bit 3     | Bit 2    | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR |      | Value o<br>all othe<br>resets |      |

|---------|---------|------------------------|-------------|-------------------------------|---------------------|-----------|----------|--------|--------|--------------------------|------|-------------------------------|------|

| 0Bh,8Bh | INTCON  | GIE                    | PEIE        | TOIE                          | INTE                | RBIE      | TOIF     | INTF   | RBIF   | 0000 0                   | 200x | 0000                          | 000u |

| 0Ch     | PIR1    | PSPIF <sup>(1,2)</sup> | ADIF        | RCIF <sup>(2)</sup>           | TXIF <sup>(2)</sup> | SSPIF     | CCP1IF   | TMR2IF | TMR1IF | 0000 0                   | 0000 | 0000                          | 0000 |

| 8Ch     | PIE1    | PSPIE <sup>(1,2)</sup> | ADIE        | RCIE <sup>(2)</sup>           | TXIE <sup>(2)</sup> | SSPIE     | CCP1IE   | TMR2IE | TMR1IE | 0000 0                   | 0000 | 0000                          | 0000 |

| 87h     | TRISC   | PORTC Da               | ta Directio | on Registe                    | er                  |           |          |        |        | 1111 1                   | 1111 | 1111                          | 1111 |

| 13h     | SSPBUF  | Synchronou             | us Serial I | Port Rece                     | ive Buffer          | /Transmit | Register |        |        | xxxx x                   | xxxx | uuuu                          | uuuu |

| 14h     | SSPCON  | WCOL                   | SSPOV       | SSPEN                         | CKP                 | SSPM3     | SSPM2    | SSPM1  | SSPM0  | 0000 0                   | 0000 | 0000                          | 0000 |

| 85h     | TRISA   | _                      | _           | PORTA Data Direction Register |                     |           |          |        |        |                          | 1111 | 11                            | 1111 |

| 94h     | SSPSTAT | —                      | —           | D/Ā                           | Р                   | S         | R/W      | UA     | BF     | 00 C                     | 0000 | 00                            | 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A, always maintain these bits clear.

2: The PIC16C72 does not have a Parallel Slave Port or USART, these bits are unimplemented, read as '0'.

#### TABLE 12-3: BAUD RATES FOR SYNCHRONOUS MODE

| BAUD        | Fosc = 2 | 20 MHz     | SPBRG              | 16 MHz |            | SPBRG              | 10 MHz |            | SPBRG              | 7.15909 I | MHz        | SPBRG              |

|-------------|----------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|-----------|------------|--------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD     | %<br>ERROR | value<br>(decimal) |

| 0.3         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 1.2         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 2.4         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 9.6         | NA       | -          | -                  | NA     | -          | -                  | 9.766  | +1.73      | 255                | 9.622     | +0.23      | 185                |

| 19.2        | 19.53    | +1.73      | 255                | 19.23  | +0.16      | 207                | 19.23  | +0.16      | 129                | 19.24     | +0.23      | 92                 |

| 76.8        | 76.92    | +0.16      | 64                 | 76.92  | +0.16      | 51                 | 75.76  | -1.36      | 32                 | 77.82     | +1.32      | 22                 |

| 96          | 96.15    | +0.16      | 51                 | 95.24  | -0.79      | 41                 | 96.15  | +0.16      | 25                 | 94.20     | -1.88      | 18                 |

| 300         | 294.1    | -1.96      | 16                 | 307.69 | +2.56      | 12                 | 312.5  | +4.17      | 7                  | 298.3     | -0.57      | 5                  |

| 500         | 500      | 0          | 9                  | 500    | 0          | 7                  | 500    | 0          | 4                  | NA        | -          | -                  |

| HIGH        | 5000     | -          | 0                  | 4000   | -          | 0                  | 2500   | -          | 0                  | 1789.8    | -          | 0                  |

| LOW         | 19.53    | -          | 255                | 15.625 | -          | 255                | 9.766  | -          | 255                | 6.991     | -          | 255                |

|                     | Fosc = | 5.0688 M   | Hz                          | 4 MHz  |            |                             | 3.579545 | 5 MHz      |                             | 1 MHz  |            |                             | 32.768 kHz |            |                             |

|---------------------|--------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|--------|------------|-----------------------------|------------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD      | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | NA     | -          | -                           | 0.303      | +1.14      | 26                          |

| 1.2                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | 1.202  | +0.16      | 207                         | 1.170      | -2.48      | 6                           |

| 2.4                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | 2.404  | +0.16      | 103                         | NA         | -          | -                           |

| 9.6                 | 9.6    | 0          | 131                         | 9.615  | +0.16      | 103                         | 9.622    | +0.23      | 92                          | 9.615  | +0.16      | 25                          | NA         | -          | -                           |

| 19.2                | 19.2   | 0          | 65                          | 19.231 | +0.16      | 51                          | 19.04    | -0.83      | 46                          | 19.24  | +0.16      | 12                          | NA         | -          | -                           |

| 76.8                | 79.2   | +3.13      | 15                          | 76.923 | +0.16      | 12                          | 74.57    | -2.90      | 11                          | 83.34  | +8.51      | 2                           | NA         | -          | -                           |

| 96                  | 97.48  | +1.54      | 12                          | 1000   | +4.17      | 9                           | 99.43    | +3.57      | 8                           | NA     | -          | -                           | NA         | -          | -                           |

| 300                 | 316.8  | +5.60      | 3                           | NA     | -          | -                           | 298.3    | -0.57      | 2                           | NA     | -          | -                           | NA         | -          | -                           |

| 500                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | NA     | -          | -                           | NA         | -          | -                           |

| HIGH                | 1267   | -          | 0                           | 100    | -          | 0                           | 894.9    | -          | 0                           | 250    | -          | 0                           | 8.192      | -          | 0                           |

| LOW                 | 4.950  | -          | 255                         | 3.906  | -          | 255                         | 3.496    | -          | 255                         | 0.9766 | -          | 255                         | 0.032      | -          | 255                         |

# TABLE 12-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD | Fosc = 2 | 20 MHz     | SPBRG     | 16 MHz |       | SPBRG     | 10 MHz |       | SPBRG     | 7.15909 | MHz        | SPBRG     |

|------|----------|------------|-----------|--------|-------|-----------|--------|-------|-----------|---------|------------|-----------|

| RATE |          | %<br>ERROR | value     |        | %     | value     |        | %     | value     |         | %<br>ERROR | value     |

| (K)  | KBAUD    | ERROR      | (decimal) | RBAUD  | ERROR | (decimal) | REAUD  | ERROR | (decimal) | REAUD   | ERROR      | (decimal) |

| 0.3  | NA       | -          | -         | NA     | -     | -         | NA     | -     | -         | NA      | -          | -         |

| 1.2  | 1.221    | +1.73      | 255       | 1.202  | +0.16 | 207       | 1.202  | +0.16 | 129       | 1.203   | +0.23      | 92        |

| 2.4  | 2.404    | +0.16      | 129       | 2.404  | +0.16 | 103       | 2.404  | +0.16 | 64        | 2.380   | -0.83      | 46        |

| 9.6  | 9.469    | -1.36      | 32        | 9.615  | +0.16 | 25        | 9.766  | +1.73 | 15        | 9.322   | -2.90      | 11        |

| 19.2 | 19.53    | +1.73      | 15        | 19.23  | +0.16 | 12        | 19.53  | +1.73 | 7         | 18.64   | -2.90      | 5         |

| 76.8 | 78.13    | +1.73      | 3         | 83.33  | +8.51 | 2         | 78.13  | +1.73 | 1         | NA      | -          | -         |

| 96   | 104.2    | +8.51      | 2         | NA     | -     | -         | NA     | -     | -         | NA      | -          | -         |

| 300  | 312.5    | +4.17      | 0         | NA     | -     | -         | NA     | -     | -         | NA      | -          | -         |

| 500  | NA       | -          | -         | NA     | -     | -         | NA     | -     | -         | NA      | -          | -         |

| HIGH | 312.5    | -          | 0         | 250    | -     | 0         | 156.3  | -     | 0         | 111.9   | -          | 0         |

| LOW  | 1.221    | -          | 255       | 0.977  | -     | 255       | 0.6104 | -     | 255       | 0.437   | -          | 255       |

|                     | Fosc = | 5.0688 MI  | Hz                          | 4 MHz  |            |                             | 3.57954 | 5 MHz      |                             | 1 MHz  |            |                             | 32.768 k | Hz         |                             |

|---------------------|--------|------------|-----------------------------|--------|------------|-----------------------------|---------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | 0.31   | +3.13      | 255                         | 0.3005 | -0.17      | 207                         | 0.301   | +0.23      | 185                         | 0.300  | +0.16      | 51                          | 0.256    | -14.67     | 1                           |

| 1.2                 | 1.2    | 0          | 65                          | 1.202  | +1.67      | 51                          | 1.190   | -0.83      | 46                          | 1.202  | +0.16      | 12                          | NA       | -          | -                           |

| 2.4                 | 2.4    | 0          | 32                          | 2.404  | +1.67      | 25                          | 2.432   | +1.32      | 22                          | 2.232  | -6.99      | 6                           | NA       | -          | -                           |

| 9.6                 | 9.9    | +3.13      | 7                           | NA     | -          | -                           | 9.322   | -2.90      | 5                           | NA     | -          | -                           | NA       | -          | -                           |

| 19.2                | 19.8   | +3.13      | 3                           | NA     | -          | -                           | 18.64   | -2.90      | 2                           | NA     | -          | -                           | NA       | -          | -                           |

| 76.8                | 79.2   | +3.13      | 0                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 96                  | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 300                 | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 500                 | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| HIGH                | 79.2   | -          | 0                           | 62.500 | -          | 0                           | 55.93   | -          | 0                           | 15.63  | -          | 0                           | 0.512    | -          | 0                           |

| LOW                 | 0.3094 | -          | 255                         | 3.906  | -          | 255                         | 0.2185  | -          | 255                         | 0.0610 | -          | 255                         | 0.0020   | -          | 255                         |

#### TABLE 12-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address | Name                               | Bit 7                | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|------------------------------------|----------------------|-----------|---------|-------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1                               | PSPIF <sup>(1)</sup> | ADIF      | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA                              | SPEN                 | RX9       | SREN    | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                 |

| 19h     | TXREG                              | USART Tra            | ansmit Re | egister |       |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1                               | PSPIE <sup>(1)</sup> | ADIE      | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA                              | CSRC                 | TX9       | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG Baud Rate Generator Register |                      |           |         |       |       |        |        |        | 0000 0000                | 0000 0000                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Transmission. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

#### TABLE 12-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address | Name  | Bit 7                        | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|-------|------------------------------|-----------|---------|-------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup>         | ADIF      | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA | SPEN                         | RX9       | SREN    | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                 |

| 1Ah     | RCREG | USART Re                     | eceive Re | egister |       |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup>         | ADIE      | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA | CSRC                         | TX9       | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG | Baud Rate Generator Register |           |         |       |       |        |        |        | 0000 0000                | 0000 0000                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

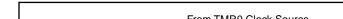

#### 14.7 Watchdog Timer (WDT) **Applicable Devices** 72 73 73A 74 74A 76 77

The Watchdog Timer is as a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The WDT can be permanently disabled by clearing configuration bit WDTE (Section 14.1).

#### 14.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a

FIGURE 14-18: WATCHDOG TIMER BLOCK DIAGRAM

prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

14.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst case conditions (VDD = Min., Temperature = Max., and max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

Note: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

# FIGURE 14-19: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION       | RBPU  | INTEDG               | TOCS  | TOSE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Figure 14-1, and Figure 14-2 for operation of these bits.

# PIC16C7X

| IORWF             | Inclusive                                                        | e OR W v                                                | with f          |                      |  |  |  |  |  |  |

|-------------------|------------------------------------------------------------------|---------------------------------------------------------|-----------------|----------------------|--|--|--|--|--|--|

| Syntax:           | [ label ]                                                        | IORWF                                                   | f,d             |                      |  |  |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$ | 27                                                      |                 |                      |  |  |  |  |  |  |

| Operation:        | (W) .OR.                                                         | (f) $\rightarrow$ (de                                   | estination      | )                    |  |  |  |  |  |  |

| Status Affected:  | Z                                                                |                                                         |                 |                      |  |  |  |  |  |  |

| Encoding:         | 00                                                               | 0100                                                    | dfff            | ffff                 |  |  |  |  |  |  |

| Description:      | Inclusive C<br>ter 'f'. If 'd'<br>W register<br>back in reg      | is 0 the re<br>. If 'd' is 1                            | sult is plac    | ced in the           |  |  |  |  |  |  |

| Words:            | 1                                                                |                                                         |                 |                      |  |  |  |  |  |  |

| Cycles:           | 1                                                                |                                                         |                 |                      |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                               | Q2                                                      | Q3              | Q4                   |  |  |  |  |  |  |

|                   | Decode                                                           | Read<br>register<br>'f'                                 | Process<br>data | Write to destination |  |  |  |  |  |  |

| Example           | IORWF                                                            |                                                         | RESULT,         | 0                    |  |  |  |  |  |  |

|                   | Before In                                                        |                                                         |                 |                      |  |  |  |  |  |  |

|                   | RESULT = 0x13<br>W = 0x91                                        |                                                         |                 |                      |  |  |  |  |  |  |

|                   | After Inst                                                       | r Instruction<br>RESULT = $0x13$<br>W = $0x93$<br>Z = 1 |                 |                      |  |  |  |  |  |  |

| MOVLW             | Move Literal to W                                                                          |  |  |  |  |  |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] MOVLW k                                                                   |  |  |  |  |  |  |  |  |  |

| Operands:         | $0 \le k \le 255$                                                                          |  |  |  |  |  |  |  |  |  |

| Operation:        | $k \rightarrow (W)$                                                                        |  |  |  |  |  |  |  |  |  |

| Status Affected:  | None                                                                                       |  |  |  |  |  |  |  |  |  |

| Encoding:         | 11 00xx kkkk kkkk                                                                          |  |  |  |  |  |  |  |  |  |

| Description:      | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |  |  |  |  |  |  |  |  |  |

| Words:            | 1                                                                                          |  |  |  |  |  |  |  |  |  |

| Cycles:           | 1                                                                                          |  |  |  |  |  |  |  |  |  |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                |  |  |  |  |  |  |  |  |  |

|                   | Decode Read literal 'k' Process Write to W                                                 |  |  |  |  |  |  |  |  |  |

| Example           | MOVLW $0x5A$<br>After Instruction<br>W = 0x5A                                              |  |  |  |  |  |  |  |  |  |

| MOVF              | Move f                                                                                                                                                                                                                                                          |           |             |          |  |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|----------|--|--|--|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                                                                       | MOVF      | f,d         |          |  |  |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                | 7         |             |          |  |  |  |  |  |  |

| Operation:        | $(f) \rightarrow (de)$                                                                                                                                                                                                                                          | stination | )           |          |  |  |  |  |  |  |

| Status Affected:  | Z                                                                                                                                                                                                                                                               |           |             |          |  |  |  |  |  |  |

| Encoding:         | 00 1000 dfff ffff                                                                                                                                                                                                                                               |           |             |          |  |  |  |  |  |  |

| Description:      | The contents of register f is moved to a destination dependant upon the status of d. If $d = 0$ , destination is W register. If $d = 1$ , the destination is file register f itself. $d = 1$ is useful to test a file register since status flag Z is affected. |           |             |          |  |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                               |           |             |          |  |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                               |           |             |          |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                                                              | Q2        | Q3          | Q4       |  |  |  |  |  |  |

|                   | Decode Read Process Write to register 'f'                                                                                                                                                                                                                       |           |             |          |  |  |  |  |  |  |

| Example           | MOVF FSR, 0<br>After Instruction                                                                                                                                                                                                                                |           |             |          |  |  |  |  |  |  |

|                   |                                                                                                                                                                                                                                                                 |           | ie in FSR i | register |  |  |  |  |  |  |

| MOVWF             | Move W            | to f                                       |                 |                       |  |  |  |  |  |  |

|-------------------|-------------------|--------------------------------------------|-----------------|-----------------------|--|--|--|--|--|--|

| Syntax:           | [ label ]         | MOVW                                       | = f             |                       |  |  |  |  |  |  |

| Operands:         | $0 \le f \le 12$  | 27                                         |                 |                       |  |  |  |  |  |  |

| Operation:        | $(W) \to (f)$     |                                            |                 |                       |  |  |  |  |  |  |

| Status Affected:  | None              |                                            |                 |                       |  |  |  |  |  |  |

| Encoding:         | 00                | 0000                                       | lfff            | ffff                  |  |  |  |  |  |  |

| Description:      | Move data<br>'f'. | Move data from W register to register 'f'. |                 |                       |  |  |  |  |  |  |

| Words:            | 1                 |                                            |                 |                       |  |  |  |  |  |  |

| Cycles:           | 1                 |                                            |                 |                       |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                | Q2                                         | Q3              | Q4                    |  |  |  |  |  |  |

|                   | Decode            | Read<br>register<br>'f'                    | Process<br>data | Write<br>register 'f' |  |  |  |  |  |  |

| Example           | MOVWF             | OPTIC                                      | DN_REG          |                       |  |  |  |  |  |  |

|                   | Before In         |                                            |                 | -                     |  |  |  |  |  |  |

|                   |                   | OPTION<br>W                                | = 0xF<br>= 0x4  | -                     |  |  |  |  |  |  |

|                   | After Inst        | ruction                                    |                 |                       |  |  |  |  |  |  |

|                   |                   | OPTION                                     |                 |                       |  |  |  |  |  |  |

|                   |                   | W                                          | = 0x4           | F                     |  |  |  |  |  |  |

# 17.2 DC Characteristics: PIC16LC72-04 (Commercial, Industrial)

| DC CHA                | ARACTERISTICS                                                    |               |             | ard Ope<br>ing tem |              |                | itions (unless otherwise stated)<br>$0^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and<br>$C \leq TA \leq +70^{\circ}C$ for commercial                           |

|-----------------------|------------------------------------------------------------------|---------------|-------------|--------------------|--------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Characteristic                                                   | Sym           | Min         | Тур†               | Max          | Units          | Conditions                                                                                                                                                              |

| D001                  | Supply Voltage                                                   | Vdd           | 2.5         | -                  | 6.0          | V              | LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                                               |

| D002*                 | RAM Data Retention Volt-<br>age (Note 1)                         | Vdr           | -           | 1.5                | -            | V              |                                                                                                                                                                         |

| D003                  | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR          | -           | Vss                | -            | V              | See section on Power-on Reset for details                                                                                                                               |

| D004*                 | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | Svdd          | 0.05        | -                  | -            | V/ms           | See section on Power-on Reset for details                                                                                                                               |

| D005                  | Brown-out Reset Voltage                                          | Bvdd          | 3.7         | 4.0                | 4.3          | V              | BODEN bit in configuration word enabled                                                                                                                                 |

| D010                  | Supply Current<br>(Note 2,5)                                     | IDD           | -           | 2.0                | 3.8          | mA             | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                           |

| D010A                 |                                                                  |               | -           | 22.5               | 48           | μA             | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                         |

| D015*                 | Brown-out Reset Current (Note 6)                                 | $\Delta$ IBOR | -           | 350                | 425          | μA             | BOR enabled VDD = 5.0V                                                                                                                                                  |

| D020<br>D021<br>D021A | Power-down Current<br>(Note 3,5)                                 | IPD           | -<br>-<br>- | 7.5<br>0.9<br>0.9  | 30<br>5<br>5 | μΑ<br>μΑ<br>μΑ | $VDD = 3.0V, WDT enabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 3.0V, WDT disabled, 0^{\circ}C to +70^{\circ}C$ $VDD = 3.0V, WDT disabled, -40^{\circ}C to +85^{\circ}C$ |

| D023*                 | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ IBOR | -           | 350                | 425          | μA             | BOR enabled VDD = 5.0V                                                                                                                                                  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption. The test conditions for all IDD measurements in active operation mode are:

$OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD <math>\overline{MCLR} = VDD; WDT$  enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

# PIC16C7X

# Applicable Devices 72 73 73A 74 74A 76 77

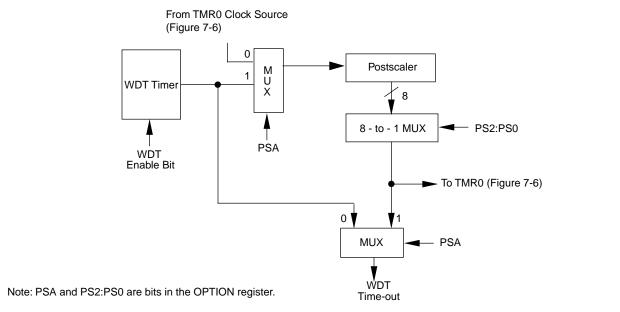

# TABLE 17-8: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Parameter<br>No. | Sym     | Characteristic  |              | Min  | Тур | Max | Units | Conditions                        |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|-----------------------------------|

| 90               | TSU:STA | START condition | 100 kHz mode | 4700 | —   | —   | ns    | Only relevant for repeated START  |

|                  |         | Setup time      | 400 kHz mode | 600  | —   | —   |       | condition                         |

| 91               | THD:STA | START condition | 100 kHz mode | 4000 | —   | —   | ns    | After this period the first clock |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | 115   | pulse is generated                |

| 92               | Tsu:sto | STOP condition  | 100 kHz mode | 4700 | —   | —   | ns    |                                   |

|                  |         | Setup time      | 400 kHz mode | 600  | —   | —   | 113   |                                   |

| 93               | THD:STO | STOP condition  | 100 kHz mode | 4000 | —   | —   | ns    |                                   |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | 113   |                                   |

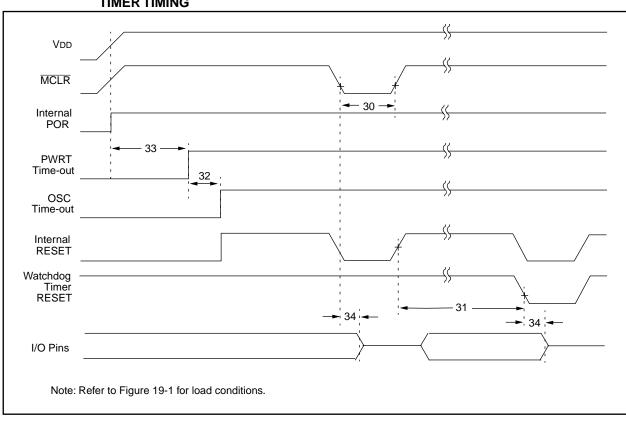

# FIGURE 19-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

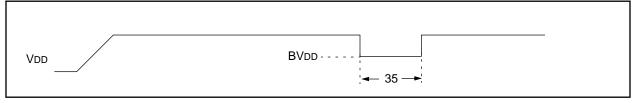

#### FIGURE 19-5: BROWN-OUT RESET TIMING

# TABLE 19-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Max | Units | Conditions                |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|---------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 2   | _        | _   | μs    | VDD = 5V, -40°C to +125°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32               | Tost  | Oscillation Start-up Timer Period                      | _   | 1024Tosc | _   | —     | Tosc = OSC1 period        |

| 33*              | Tpwrt | Power up Timer Period                                  | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34               | Tioz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | _        | 2.1 | μs    |                           |

| 35               | TBOR  | Brown-out Reset pulse width                            | 100 |          | _   | μs    | $VDD \le BVDD$ (D005)     |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

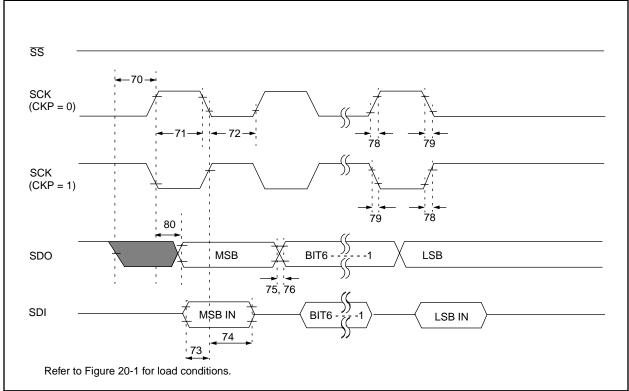

# FIGURE 20-9: SPI MASTER MODE TIMING (CKE = 0)

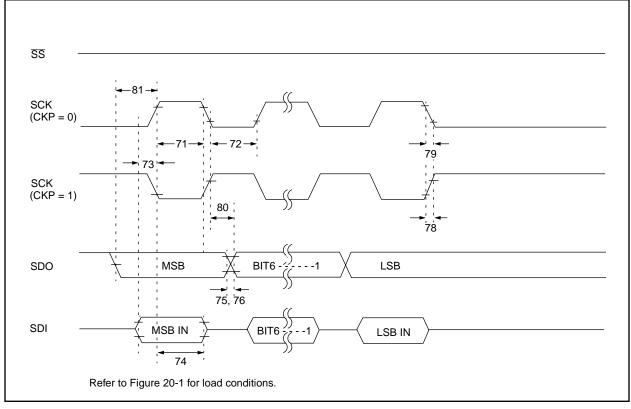

## FIGURE 20-10: SPI MASTER MODE TIMING (CKE = 1)

# Applicable Devices 72 73 73A 74 74A 76 77

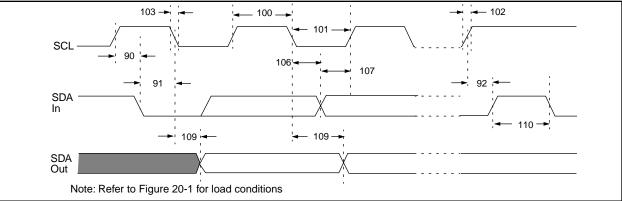

# FIGURE 20-14: I<sup>2</sup>C BUS DATA TIMING

# TABLE 20-10: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Parameter<br>No. | Sym     | Characteristic         |              | Min        | Мах  | Units | Conditions                                       |

|------------------|---------|------------------------|--------------|------------|------|-------|--------------------------------------------------|

| 100              | Thigh   | Clock high time        | 100 kHz mode | 4.0        | _    | μs    | Device must operate at a mini-<br>mum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 0.6        | _    | μs    | Device must operate at a mini-<br>mum of 10 MHz  |

|                  |         |                        | SSP Module   | 1.5Tcy     | —    |       |                                                  |

| 101              | TLOW    | Clock low time         | 100 kHz mode | 4.7        | —    | μs    | Device must operate at a mini-<br>mum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 1.3        | _    | μs    | Device must operate at a mini-<br>mum of 10 MHz  |

|                  |         |                        | SSP Module   | 1.5Tcy     | _    |       |                                                  |

| 102              | Tr      | SDA and SCL rise       | 100 kHz mode | -          | 1000 | ns    |                                                  |

|                  |         | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF       |

| 103              | Tf      | SDA and SCL fall time  | 100 kHz mode | -          | 300  | ns    |                                                  |

|                  |         |                        | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF       |

| 90               | TSU:STA | START condition        | 100 kHz mode | 4.7        | —    | μs    | Only relevant for repeated                       |

|                  |         | setup time             | 400 kHz mode | 0.6        | —    | μs    | START condition                                  |

| 91               | THD:STA | START condition hold   | 100 kHz mode | 4.0        | —    | μs    | After this period the first clock                |

|                  |         | time                   | 400 kHz mode | 0.6        | —    | μs    | pulse is generated                               |

| 106              | THD:DAT | Data input hold time   | 100 kHz mode | 0          | —    | ns    |                                                  |

|                  |         |                        | 400 kHz mode | 0          | 0.9  | μs    |                                                  |

| 107              | TSU:DAT | Data input setup time  | 100 kHz mode | 250        | —    | ns    | Note 2                                           |

|                  |         |                        | 400 kHz mode | 100        | —    | ns    |                                                  |

| 92               | TSU:STO | STOP condition setup   | 100 kHz mode | 4.7        | —    | μs    |                                                  |

|                  |         | time                   | 400 kHz mode | 0.6        | —    | μs    |                                                  |

| 109              | ΤΑΑ     | Output valid from      | 100 kHz mode | _          | 3500 | ns    | Note 1                                           |

|                  |         | clock                  | 400 kHz mode | _          | —    | ns    |                                                  |

| 110              | TBUF    | Bus free time          | 100 kHz mode | 4.7        | —    | μs    | Time the bus must be free                        |

|                  |         |                        | 400 kHz mode | 1.3        | —    | μs    | before a new transmission can start              |

|                  | Cb      | Bus capacitive loading |              |            | 400  | pF    |                                                  |

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A fast-mode (400 kHz) I<sup>2</sup>C-bus device can be used in a standard-mode (100 kHz) I<sup>2</sup>C-bus system, but the requirement tsu;DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+tsu;DAT = 1000 + 250 = 1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

#### TABLE 20-13: A/D CONVERTER CHARACTERISTICS:

PIC16C76/77-04 (Commercial, Industrial, Extended) PIC16C76/77-10 (Commercial, Industrial, Extended) PIC16C76/77-20 (Commercial, Industrial, Extended) PIC16LC76/77-04 (Commercial, Industrial)

| Param<br>No. | Sym  | Characteristic                               |                       | Min       | Тур†       | Мах        | Units                                                                                        | Conditions                                                                                                  |

|--------------|------|----------------------------------------------|-----------------------|-----------|------------|------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| A01          | NR   | Resolution                                   |                       |           |            | 8-bits     | bit                                                                                          | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A02          | EABS | Total Absolute error                         |                       | _         | <±1        | LSb        | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |                                                                                                             |

| A03          | EIL  | Integral linearity error                     | _                     | _         | <±1        | LSb        | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |                                                                                                             |

| A04          | EDL  | Differential linearity error                 | —                     | _         | <±1        | LSb        | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |                                                                                                             |

| A05          | EFS  | Full scale error                             | —                     | —         | <±1        | LSb        | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |                                                                                                             |

| A06          | EOFF | Offset error                                 |                       | _         | _          | <±1        | LSb                                                                                          | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A10          | —    | Monotonicity                                 |                       | —         | guaranteed | _          | -                                                                                            | $VSS \leq VAIN \leq VREF$                                                                                   |

| A20          | Vref | Reference voltage                            |                       | 3.0V      | —          | Vdd + 0.3  | V                                                                                            |                                                                                                             |

| A25          | VAIN | Analog input voltage                         |                       | Vss - 0.3 | —          | Vref + 0.3 | V                                                                                            |                                                                                                             |

| A30          | ZAIN | Recommended impedan<br>analog voltage source | ice of                |           | _          | 10.0       | kΩ                                                                                           |                                                                                                             |

| A40          | IAD  | A/D conversion current                       | PIC16 <b>C</b> 76/77  | —         | 180        | _          | μΑ                                                                                           | Average current consump-                                                                                    |

|              |      | (VDD)                                        | PIC16 <b>LC</b> 76/77 | —         | 90         |            | μΑ                                                                                           | tion when A/D is on.<br>(Note 1)                                                                            |

| A50          | IREF | VREF input current (Note 2)                  |                       | 10        | _          | 1000       | μA                                                                                           | During VAIN acquisition.<br>Based on differential of<br>VHOLD to VAIN to charge<br>CHOLD, see Section 13.1. |

|              |      |                                              |                       | —         | —          | 10         | μA                                                                                           | During A/D Conversion cycle                                                                                 |

These parameters are characterized but not tested.