Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Last Time Buy                                                                                            |

|----------------------------|----------------------------------------------------------------------------------------------------------|

| Core Processor             | SH-4                                                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                                       |

| Speed                      | 200MHz                                                                                                   |

| Connectivity               | Audio Codec, CANbus, EBI/EMI, FIFO, I <sup>2</sup> C, MFI, Memory Card, SCI, Serial Sound, SIM, SPI, USB |

| Peripherals                | DMA, LCD, POR, WDT                                                                                       |

| Number of I/O              | 69                                                                                                       |

| Program Memory Size        | -                                                                                                        |

| Program Memory Type        | ROMIess                                                                                                  |

| EEPROM Size                | -                                                                                                        |

| RAM Size                   | 48K x 8                                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.4V ~ 1.6V                                                                                              |

| Data Converters            | A/D 4x10b                                                                                                |

| Oscillator Type            | Internal                                                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                        |

| Mounting Type              | Surface Mount                                                                                            |

| Package / Case             | 256-LFBGA                                                                                                |

| Supplier Device Package    | 256-LFBGA (17x17)                                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/d17760bp200adv                          |

|                            |                                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

If the delay slot instruction has a second data transfer, two checks are performed in step 2, as in the above case (Instructions that make two accesses to memory).

If the accepted exception (the highest-priority exception) is a delay slot instruction reexecution type exception, the branch instruction PR register write operation (PC  $\rightarrow$  PR operation performed in a BSR, BSRF, or JSR instruction) is not disabled.

## 8.6 Usage Notes

- 1. Return from exception handling

- A. Check the BL bit in SR with software. If SPC and SSR have been saved to external memory, set the BL bit in SR to 1 before restoring them.

- B. Issue an RTE instruction. When RTE is executed, the SPC contents are saved in PC, the SSR contents are saved in SR, and branch is made to the SPC address to return from the exception handling routine.

- 2. If an exception or interrupt occurs when BL bit in SR = 1

- A. Exception

When an exception other than a user break occurs, a manual reset is executed. The value in EXPEVT at this time is H'0000 0020; the SPC and SSR contents are undefined.

B. Interrupt

If an ordinary interrupt occurs, the interrupt request is held pending and is accepted after the BL bit in SR has been cleared to 0 by software. If a nonmaskable interrupt (NMI) occurs, it can be held pending or accepted according to the setting made by software. In sleep or standby mode, however, an interrupt is accepted even if the BL bit in SR is set to 1.

- 3. SPC when an exception occurs

- A. Re-execution type exception

The PC value for the instruction at which the exception occurred is set in SPC, and the instruction is re-executed after returning from the exception handling routine. If an exception occurs in a delay slot instruction, however, the PC value for the delay slot instruction is saved in SPC regardless of whether or not the preceding delay slot instruction condition is satisfied.

B. Completion type exception or interrupt

The PC value for the instruction following that at which the exception occurred is set in SPC. If an exception occurs in a branch instruction with delay slot, however, the PC value for the branch destination is saved in SPC.

4. An exception must not be generated in an RTE instruction delay slot, as the operation cannot be guaranteed in this case.

|        | Bit              | Initial |            |                                                                                                                                                                                                                                                                                                                                |

|--------|------------------|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit    | Name             | Value   | R/W        | Description                                                                                                                                                                                                                                                                                                                    |

| 7      | A6BST2           | 0       | R/W        | Area 6 Burst ROM Control                                                                                                                                                                                                                                                                                                       |

| 6<br>5 | A6BST1<br>A6BST0 | 0<br>0  | R/W<br>R/W | These bits specify whether burst ROM interface is used<br>in area 6. When burst ROM interface is used, they also<br>specify the number of accesses in a burst. When area 6<br>is an MPX interface area, the settings of these bits are<br>ignored. When area 6 is used as a PCMCIA area, these<br>bits should be cleared to 0. |

|        |                  |         |            | 000: Area 6 is accessed as SRAM interface.                                                                                                                                                                                                                                                                                     |

|        |                  |         |            | 001: Area 6 is accessed as burst ROM interface<br>(4 consecutive accesses). Can be used with 8-, 16-,<br>or 32-bit bus width                                                                                                                                                                                                   |

|        |                  |         |            | 010: Area 6 is accessed as burst ROM interface<br>(8 consecutive accesses). Can be used with 8-, 16-,<br>or 32-bit bus width                                                                                                                                                                                                   |

|        |                  |         |            | 011: Area 6 is accessed as burst ROM interface<br>(16 consecutive accesses). Can only be used with 8-<br>or 16-bit bus width. The setting of 32-bit bus width is<br>prohibited.                                                                                                                                                |

|        |                  |         |            | <ul><li>100: Area 6 is accessed as burst ROM interface<br/>(32 consecutive accesses). Can only be used with 8-<br/>bit bus width</li></ul>                                                                                                                                                                                     |

|        |                  |         |            | 101: Setting prohibited                                                                                                                                                                                                                                                                                                        |

|        |                  |         |            | 110: Setting prohibited                                                                                                                                                                                                                                                                                                        |

|        |                  |         |            | 111: Setting prohibited                                                                                                                                                                                                                                                                                                        |

| Bit      | Bit<br>Name  | Initial<br>Value | R/W        | Description |                                                                                        |                       |  |  |  |  |

|----------|--------------|------------------|------------|-------------|----------------------------------------------------------------------------------------|-----------------------|--|--|--|--|

| 28       | A6B2         | 1                | R/W        | Area 6      | Burst Pitch                                                                            |                       |  |  |  |  |

| 27<br>26 | A6B1<br>A6B0 | 1<br>1           | R/W<br>R/W | inserte     | bits specify the number or<br>d for the second and follo<br>ransfer when area 6 is spe | wing data accesses in |  |  |  |  |

|          |              |                  |            |             | Inserted wait cycles                                                                   | RDY pin               |  |  |  |  |

|          |              |                  |            | 000:        | 0                                                                                      | Disabled              |  |  |  |  |

|          |              |                  |            | 001:        | 1                                                                                      | Enabled               |  |  |  |  |

|          |              |                  |            | 010:        | 2                                                                                      | Enabled               |  |  |  |  |

|          |              |                  |            | 011:        | 3                                                                                      | Enabled               |  |  |  |  |

|          |              |                  |            | 100:        | 4                                                                                      | Enabled               |  |  |  |  |

|          |              |                  |            | 101:        | 5                                                                                      | Enabled               |  |  |  |  |

|          |              |                  |            | 110:        | 6                                                                                      | Enabled               |  |  |  |  |

|          |              |                  |            | 111:        | 7                                                                                      | Enabled               |  |  |  |  |

| 25       | A5W2         | 1                | R/W        | Area 5      | Wait Control                                                                           |                       |  |  |  |  |

| 24<br>23 | A5W1<br>A5W0 | 1<br>1           | R/W<br>R/W | inserte     | bits specify the number of<br>d for area 5. For the case<br>is made, see table 10.7.   |                       |  |  |  |  |

|          |              |                  |            |             | Inserted wait cycles                                                                   | RDY pin               |  |  |  |  |

|          |              |                  |            | 000:        | 0                                                                                      | Disabled              |  |  |  |  |

|          |              |                  |            | 001:        | 1                                                                                      | Enabled               |  |  |  |  |

|          |              |                  |            | 010:        | 2                                                                                      | Enabled               |  |  |  |  |

|          |              |                  |            | 011:        | 3                                                                                      | Enabled               |  |  |  |  |

|          |              |                  |            | 100:        | 6                                                                                      | Enabled               |  |  |  |  |

|          |              |                  |            | 101:        | 9                                                                                      | Enabled               |  |  |  |  |

|          |              |                  |            | 110:        | 12                                                                                     | Enabled               |  |  |  |  |

|          |              |                  |            | 111:        | 15                                                                                     | Enabled               |  |  |  |  |

| Bit      | Bit<br>Name  | Initial<br>Value | R/W | Descr                     | intion                                                                                                                                         |                                                                             |

|----------|--------------|------------------|-----|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 15       | A3W2         | 1                | R/W |                           | Wait Control                                                                                                                                   |                                                                             |

| 15<br>14 | A3W2<br>A3W1 | 1                | R/W |                           |                                                                                                                                                | f welt evelop to be                                                         |

| 13       | A3W0         | 1                | R/W | inserte<br>SRAM<br>synchr | bits specify the number of<br>ed for area 3. An external<br>and MPX interfaces and<br>ronous DRAM interface. F<br>interface setting is made, s | wait input is available for<br>is not available for<br>or the case where an |

|          |              |                  |     | • Wh                      | nen SRAM interface is in ι                                                                                                                     | lse:                                                                        |

|          |              |                  |     |                           | Inserted wait cycles                                                                                                                           | RDY pin                                                                     |

|          |              |                  |     | 000:                      | 0                                                                                                                                              | Disabled                                                                    |

|          |              |                  |     | 001:                      | 1                                                                                                                                              | Enabled                                                                     |

|          |              |                  |     | 010:                      | 2                                                                                                                                              | Enabled                                                                     |

|          |              |                  |     | 011:                      | 3                                                                                                                                              | Enabled                                                                     |

|          |              |                  |     | 100:                      | 6                                                                                                                                              | Enabled                                                                     |

|          |              |                  |     | 101:                      | 9                                                                                                                                              | Enabled                                                                     |

|          |              |                  |     | 110:                      | 12                                                                                                                                             | Enabled                                                                     |

|          |              |                  |     | 111:                      | 15                                                                                                                                             | Enabled                                                                     |

|          |              |                  |     | • Wh                      | nterface is in use*1:                                                                                                                          |                                                                             |

|          |              |                  |     |                           | Synchronous DRAM C                                                                                                                             | AS latency cycles                                                           |

|          |              |                  |     | 000:                      | Setting prohibited                                                                                                                             |                                                                             |

|          |              |                  |     | 001:                      | <b>1</b> * <sup>2</sup>                                                                                                                        |                                                                             |

|          |              |                  |     | 010:                      | 2                                                                                                                                              |                                                                             |

|          |              |                  |     | 011:                      | 3                                                                                                                                              |                                                                             |

|          |              |                  |     | 100:                      | 4* <sup>2</sup>                                                                                                                                |                                                                             |

|          |              |                  |     | 101:                      | 5* <sup>2</sup>                                                                                                                                |                                                                             |

|          |              |                  |     | 110:                      | Setting prohibited                                                                                                                             |                                                                             |

|          |              |                  |     | 111:                      | Setting prohibited                                                                                                                             |                                                                             |

| 12       |              | 0                | R   | Reserv                    | ved                                                                                                                                            |                                                                             |

|          |              |                  |     | This bi<br>always         | it is always read as 0. The<br>s be 0.                                                                                                         | e write value should                                                        |

RENESAS

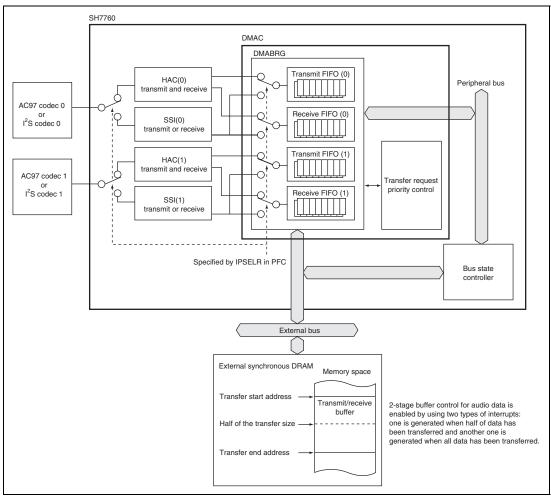

Figure 11.31 Configuration of DMA for HAC/SSI

|     | Bit  | Initial |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Name | Value   | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6   | RDRF | 0       | R/W | Receive Data Register Full<br>Indicates that received data is stored in SIRDR* <sup>1</sup> .                                                                                                                                                                                                                                                                                                                                                                          |

|     |      |         |     | 0: Indicates that no valid received data is stored in SIRDR.                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |      |         |     | [Clearing Conditions]                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |      |         |     | On reset                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |      |         |     | When data is read from SIRDR                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |      |         |     | When 0 is written to the RDRF bit                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |      |         |     | 1: Indicates that valid received data is stored in SIRDR.                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |      |         |     | [Setting Condition]* <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |      |         |     | <ul> <li>When serial reception is completed normally, and<br/>received data is transferred from SIRSR to SIRDR.</li> </ul>                                                                                                                                                                                                                                                                                                                                             |

|     |      |         |     | Notes: 1. In the T = 0 mode, when the receiver detects a parity error, it retains the previous state without affecting the SIRDR contents and RDRF flag. On the other hand, in the T = 1 mode, when the receiver detects a parity error, it transfers the received data to SIRDR, and sets the RDRF flag to 1. In both the T = 0 and T = 1 modes, clearing the RE bit in SISCR to 0 will retain the previous state without affecting the SIRDR contents and RDRF flag. |

|     |      |         |     | 2. Writing 1 will retain the original value.                                                                                                                                                                                                                                                                                                                                                                                                                           |

#### (2) Slave Transmitter

This mode cannot be used.

### (3) Master Receiver

This mode allows the SSI module to receive a serial bit stream from another device and store it in memory.

The shift register clock can be supplied from an external device or from an internal clock.

The word select pin is used as an output flow control. The module always asserts the word select signal to indicate it can receive more data continuously. It is the responsibility of the host CPU to ensure it can transmit data to the SSI module in time to ensure no data is lost.

#### (4) Master Transmitter

This mode allows the module to transmit a serial bit stream from internal memory to another device.

The shift register clock can be supplied from an external device or from an internal clock.

The word select pin is used as an output flow control. The module always asserts the word select signal to indicate it will transmit more data continuously. Word select signal is not asserted until the first word is ready to transmit however. It is the responsibility of the receiving device to ensure it can receive the serial data in time to ensure no data is lost.

When the configuration for data transfer is completed, the SSI module can work with the minimum interaction with CPU. The CPU specifies settings for the SSI module and DMAC then handles overflow/ underflow interrupts if required.

## 20.4.4 Operation Modes

There are three modes of operation: configuration, enabled and disabled. Figure 20.20 shows the transition diagram between these operation modes.

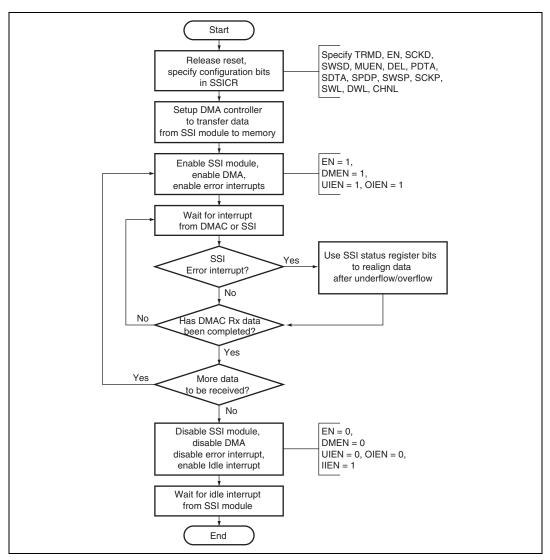

#### (1) Reception Using DMA Controller

| Bit    | Bit Name | Initial Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|----------|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12     | IRR12    | 0             | R/W | Wake-up on Bus Activity<br>Indicates that a CAN bus activity is present. When<br>the HCAN is in sleep mode and a recessive to<br>dominant bit transition takes place on the CAN<br>bus, this bit is set. The operation of this interrupt<br>is configured in the Master Control Register.<br>(MCR7 – Auto-wake Mode). This interrupt is<br>cleared by writing a 1 to this bit position. Writing a<br>0 has no effect.                                                                                                                                    |

|        |          |               |     | <ol> <li>Bus idle state<br/>Clearing condition: Write a 1 to this bit.</li> <li>CAN bus activity is detected in HCAN2 sleep<br/>mode.<br/>Setting condition: Bit transition, from recessive<br/>to dominant, is detected in sleep mode.</li> </ol>                                                                                                                                                                                                                                                                                                       |

| 11, 10 | _        | All 0         | R   | Reserved<br>The write value should always be 0. The read<br>value is not guaranteed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9      | IRR9     | 0             | R/W | Message Overrun/Overwrite Interrupt Flag<br>Indicates that a message has been received but<br>the existing message in the matching Mailbox has<br>not been read due to the corresponding<br>CANRXPR or CANRFPR set to 1. The received<br>message is either abandoned (overrun) or<br>overwritten depeding on the value of the NMC<br>(New Message Control) bit. This bit is cleared by<br>writing a 1 to the correspondent bit position in<br>CANUMSR (Unread Message Status Register).<br>Writing a 0 has no effect.<br>0: No message overrun/overwrite |

|        |          |               |     | Clearing condition: Clean all bits in CANUMSR.<br>1: Receive message overrun and its storage has<br>been rejected or message overwrite.<br>Setting condition: Message is received while<br>the corresponding CANRXPR or CANRFPR =1<br>and CANMBIMR = 0.                                                                                                                                                                                                                                                                                                  |

| Bit     | Bit Name     | Initial Value | R/W  | Description                                                                                                                                                                                                                                                                         |

|---------|--------------|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 0 | ABACK1[15:0] | All O         | R/W* | Notifies that requested transmission<br>cancellation requested of the corresponding<br>Mailbox has been performed successfully. Bits<br>15 to 0 correspond to Mailboxes 31 to 16<br>respectively.                                                                                   |

|         |              |               |      | <ul> <li>0: Clearing condition: Write a 1 to this bit.</li> <li>1: Corresponding Mailbox has cancelled<br/>transmission of message (Data or Remote<br/>Frame).</li> <li>Setting condition: Completion of<br/>transmission cancellation for the<br/>corresponding Mailbox</li> </ul> |

Note: \* Only a write of 1 is allowed to clear the bit.

#### • CANABACK0

| Bit:           | 15            | 14            | 13            | 12            | 11            | 10            | 9            | 8            | 7            | 6            | 5            | 4            | 3            | 2            | 1            | 0 |

|----------------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---|

|                | ABACK0<br>_15 | ABACK0<br>_14 | ABACK0<br>_13 | ABACK0<br>_12 | ABACK0<br>_11 | ABACK0<br>_10 | ABACK0<br>_9 | ABACK0<br>_8 | ABACK0<br>_7 | ABACK0<br>_6 | ABACK0<br>_5 | ABACK0<br>_4 | ABACK0<br>_3 | ABACK0<br>_2 | ABACK0<br>_1 | - |

| Initial value: | 0             | 0             | 0             | 0             | 0             | 0             | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0 |

| R/W:           | R/W*          | R/W*          | R/W*          | R/W*          | R/W*          | R/W*          | R/W*         | R/W*         | R/W*         | R/W*         | R/W*         | R/W*         | R/W*         | R/W*         | R/W*         | R |

| Bit     | Bit Name     | Initial Value | R/W  | Description                                                                                                                                                                                                                                                                         |

|---------|--------------|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 1 | ABACK0[15:1] | All O         | R/W* | Notifies that requested transmission<br>cancellation requested of the corresponding<br>Mailbox has been performed successfully. Bits<br>15 to 1 correspond to Mailboxes 15 to 1<br>respectively.                                                                                    |

|         |              |               |      | <ul> <li>0: Clearing condition: Write a 1 to this bit.</li> <li>1: Corresponding Mailbox has cancelled<br/>transmission of message (Data or Remote<br/>Frame).</li> <li>Setting condition: Completion of<br/>transmission cancellation for the<br/>corresponding Mailbox</li> </ul> |

| 0       |              | 0             | R    | Reserved<br>This bit is always 0 as this is receive-only.<br>Writing a 1 to this bit has no effect. This bit is<br>always read as 0.                                                                                                                                                |

Note: \* Only a write of 1 is allowed to clear the bit.

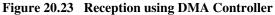

Figure 23.1 is a block diagram of the HSPI.

Figure 23.1 Block Diagram of HSPI

# 23.2 Input/Output Pins

The input/output pins of the HSPI is shown in table 23.1.

## Table 23.1 Pin Configuration

| Name                 | Abbreviation | I/O          | Function             |

|----------------------|--------------|--------------|----------------------|

| Serial bit clock pin | HSPI_CLK     | Input/Output | Clock input/output   |

| Transmit data pin    | HSPI_TX      | Output       | Transmit data output |

| Receive data pin     | HSPI_RX      | Input        | Receive data input   |

| Chip select pin      | HSPI_CS      | Input/Output | Chip select          |

#### 23.3.3 System Control Register (SPSCR)

SPSCR is a 32-bit readable/writable register that enables or disables interrupts or FIFO mode, selects either LSB first or MSB first in transmitting/receiving date, and master or slave mode.

If any of the FFEN, LMSB, CSA or MASL bit values are changed, then the module will undergo the HSPI software reset.

| Bit:           | 31 | 30 | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22  | 21  | 20   | 19   | 18   | 17   | 16   |

|----------------|----|----|------|------|------|------|------|------|------|-----|-----|------|------|------|------|------|

|                | -  | -  | -    | -    | -    | -    | -    | -    | -    | -   | -   | -    | -    | -    | -    | -    |

| Initial value: | -  | -  | -    | -    | -    | -    | -    | -    | -    | -   | -   | -    | -    | -    | -    | -    |

| R/W:           | R  | R  | R    | R    | R    | R    | R    | R    | R    | R   | R   | R    | R    | R    | R    | R    |

| Bit:           | 15 | 14 | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6   | 5   | 4    | 3    | 2    | 1    | 0    |

|                | -  | -  | TEIE | THIE | RNIE | RHIE | RFIE | FFEN | LMSB | CSV | CSA | TFIE | ROIE | RXDE | TXDE | MASL |

| Initial value: | -  | -  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1   | 0   | 0    | 0    | 0    | 0    | 0    |

| R/W:           | R  | R  | R/W  | R/W | R/W | R/W  | R/W  | R/W  | R/W  | R/W  |

| Bit      | Bit Name | Initial Value | R/W | Description                                                                                          |

|----------|----------|---------------|-----|------------------------------------------------------------------------------------------------------|

| 31 to 14 | ·        | All —         | R   | Reserved<br>These bits are always read as an undefined<br>value. The write value should always be 0. |

| 13       | TEIE     | 0             | R/W | Transmit FIFO Empty Interrupt Enable                                                                 |

|          |          |               |     | 0:Transmit FIFO empty interrupt disabled<br>1:Transmit FIFO empty interrupt enabled                  |

| 12       | THIE     | 0             | R/W | Transmit FIFO Halfway Interrupt Enable                                                               |

|          |          |               |     | 0:Transmit FIFO halfway interrupt disabled<br>1:Transmit FIFO halfway interrupt enabled              |

| 11       | RNIE     | 0             | R/W | Receive FIFO Not Empty Interrupt Enable                                                              |

|          |          |               |     | 0: Receive FIFO not empty interrupt disabled<br>1: Receive FIFO not empty interrupt enabled          |

| 10       | RHIE     | 0             | R/W | Receive FIFO Halfway Interrupt Enable                                                                |

|          |          |               |     | 0: Receive FIFO halfway interrupt disabled<br>1: Receive FIFO halfway interrupt enabled              |

| 9        | RFIE     | 0             | R/W | Receive FIFO Full Interrupt Enable                                                                   |

|          |          |               |     | 0: Receive FIFO full interrupt disabled<br>1: Receive FIFO full interrupt enabled                    |

| Bit | Bit Name | Initial value | R/W | Description                                                                                                                        |

|-----|----------|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------|

| 1   | PF0MD1   | 0             | R/W | PTF0 Mode                                                                                                                          |

| 0   | PF0MD0   | 0             | R/W | 00: Peripheral module (HSPI/MMCIF/SIM)<br>01: Port output<br>10: Port input (pull-up MOS: Off)<br>11: Port input (pull-up MOS: On) |

#### Section 24 Pin Function Controller (PFC)

## 24.2.7 Port G Control Register (PGCR)

PGCR is a 16-bit readable/writable register that selects the pin function and input pull-up MOS control.

|         | Bit: | 15         | 14         | 13         | 12         | 11         | 10         | 9          | 8          | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|---------|------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

|         |      | PG7<br>MD1 | PG7<br>MD0 | PG6<br>MD1 | PG6<br>MD0 | PG5<br>MD1 | PG5<br>MD0 | PG4<br>MD1 | PG4<br>MD0 | PG3<br>MD1 | PG3<br>MD0 | PG2<br>MD1 | PG2<br>MD0 | PG1<br>MD1 | PG1<br>MD0 | PG0<br>MD1 | PG0<br>MD0 |

| Initial |      | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          |

|         | R/W: | R/W        |

|         |      |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |

| Bit     |      | Bit N      | ame        | Ir         | nitial v   | value      | R/V        | V          | Desc       | riptio     | n          |            |            |            |            |            |            |

| 15      |      | PG7N       | /ID1       | 0          |            |            | R/V        | V          | PTG7       | 7 Mod      | е          |            |            |            |            |            |            |

| 14      |      | PG7N       | ND0        | 0          |            |            | R/V        | V          | 00: P      | eriphe     | eral m     | odule      | (SCI       | -[0]       |            |            |            |

|         |      |            |            |            |            |            |            |            |            | ort ou     |            |            | <b>\</b>   | L - 1/     |            |            |            |

|         |      |            |            |            |            |            |            |            | 10: P      | ort inp    | but (pi    | ull-up     | MOS:       | Off)       |            |            |            |

|         |      |            |            |            |            |            |            |            | 11: P      | ort inp    | out (pi    | ıll-up     | MOS:       | On)        |            |            |            |

| 13      |      | PG6N       | /ID1       | 0          |            |            | R/V        | V          | PTG        | 6 Mod      | е          |            |            |            |            |            |            |

| 12      |      | PG6N       | MD0        | 0          |            |            | R/V        | V          | 00: P      | eriphe     | eral m     | odule      | (SCIF      | -[0]       |            |            |            |

|         |      |            |            |            |            |            |            |            |            | ort ou     |            |            | <b>\</b>   | L - 1/     |            |            |            |

|         |      |            |            |            |            |            |            |            | 10: P      | ort inp    | but (pi    | ull-up     | MOS:       | Off)       |            |            |            |

|         |      |            |            |            |            |            |            |            | 11: P      | ort inp    | out (pi    | ull-up     | MOS:       | On)        |            |            |            |

| 11      |      | PG5N       | /ID1       | 0          |            |            | R/V        | V          | PTG        | 5 Mod      | е          |            |            |            |            |            |            |

| 10      |      | PG5N       | MD0        | 0          |            |            | R/V        | V          | 00: P      | eriphe     | eral m     | odule      | (SCI       | =[0])      |            |            |            |

|         |      |            |            |            |            |            |            |            |            | ort ou     |            |            | (          | [-]/       |            |            |            |

|         |      |            |            |            |            |            |            |            | 10: P      | ort inp    | but (pi    | ull-up     | MOS:       | Off)       |            |            |            |

|         |      |            |            |            |            |            |            |            | 11: P      | ort inp    | out (pi    | ull-up     | MOS:       | On)        |            |            |            |

| 9       |      | PG4N       | /ID1       | 0          |            |            | R/V        | V          | PTG4       | 1 Mod      | е          |            |            |            |            |            |            |

| 8       |      | PG4N       | ND0        | 0          |            |            | R/V        | V          | 00: P      | eriphe     | eral m     | odule      | (SCI       | =[1])      |            |            |            |

|         |      |            |            |            |            |            |            |            |            | ort ou     |            |            | `          | - 1/       |            |            |            |

|         |      |            |            |            |            |            |            |            | 10: P      | ort inp    | out (pu    | ull-up     | MOS:       | Off)       |            |            |            |

|         |      |            |            |            |            |            |            |            |            | ort inp    |            |            |            |            |            |            |            |

| Bit  | Bit Name | Initial value | R/W | Description                                                              |  |  |  |  |

|------|----------|---------------|-----|--------------------------------------------------------------------------|--|--|--|--|

| 3    | PJ1MD1   | 0             | R/W | PTJ1 Mode                                                                |  |  |  |  |

| 2    | PJ1MD0   | 0             | R/W | 00: Peripheral module (DCK)<br>01: Port output                           |  |  |  |  |

|      |          |               |     | Other than above: Setting prohibited                                     |  |  |  |  |

| 1, 0 |          | All 0         | R   | Reserved                                                                 |  |  |  |  |

|      |          |               |     | These bits are always read as 0, and the write value should always be 0. |  |  |  |  |

Section 24 Pin Function Controller (PFC)

Note: \*The following settings are prohibited: the combination of port3 set to output and port 4 to input or port3 to input and port4 to output.

#### 24.2.10 Port K Control Register (PKCR)

PKCR is a 16-bit readable/writable register that selects the pin function and input pull-up MOS control.

| Bit:           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3 | 2 | 1 | 0 |

|----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|---|---|---|

|                | PK7 | PK7 | PK6 | PK6 | PK5 | PK5 | PK4 | PK4 | PK3 | PK3 | PK2 | PK2 |   |   |   |   |

|                | MD1 | MD0 |   |   |   |   |

| Initial value: | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0 | 0 | 0 | 0 |

| R/W:           | R/W | R | R | R | R |

| Bit      | Bit Name         | Initial value | R/W        | Description                                                                                                                      |

|----------|------------------|---------------|------------|----------------------------------------------------------------------------------------------------------------------------------|

| 15<br>14 | PK7MD1<br>PK7MD0 | 0<br>0        | R/W<br>R/W | PTK7 Mode                                                                                                                        |

| 14       | T TO MEDO        | 0             | 10,00      | 00: Peripheral module (Reserved/AUD)<br>01: Port output                                                                          |

|          |                  |               |            | 10: Port input (pull-up MOS: Off)                                                                                                |

|          |                  |               |            | 11: Port input (pull-up MOS: On)                                                                                                 |

| 13       | PK6MD1           | 0             | R/W        | PTK6 Mode                                                                                                                        |

| 12       | PK6MD0           | 0             | R/W        | 00: Peripheral module (Reserved/AUD)<br>01: Port output<br>10: Port input (pull-up MOS: Off)                                     |

|          |                  |               |            | 11: Port input (pull-up MOS: On)                                                                                                 |

| 11       | PK5MD1           | 0             | R/W        | PTK5 Mode                                                                                                                        |

| 10       | PK5MD0           | 0             | R/W        | 00: Peripheral module (Reserved/AUD)<br>01: Port output<br>10: Port input (pull-up MOS: Off)<br>11: Port input (pull-up MOS: On) |

# 28.4 Operation

## 28.4.1 TAP Control

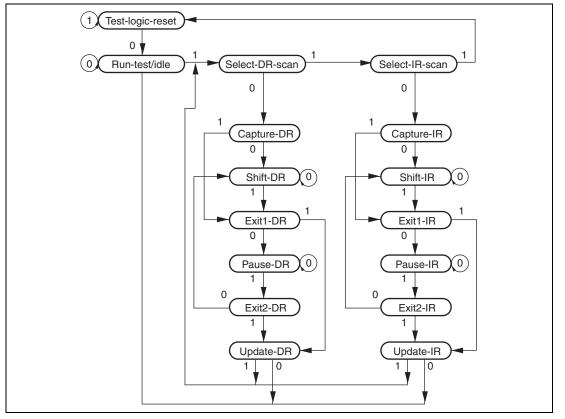

Figure 28.2 shows the internal states of TAP controller. The state transitions conform to the JTAG standards.

- State transitions occur according to the TMS value at the rising edge of a TCK signal.

- The TDI value is sampled at the rising edge of a TCK signal and shifted at the falling edge of a TCK signal.

- The TDO value is changed at the falling edge of a TCK signal. The TDO signal is in a Hi-Z state other than in the Shift-DR or Shift-IR state.

- Clearing TRST to 0 places the TAP controller into the Test-Logic-Reset state asynchronously with a TCK signal.

Figure 28.2 TAP Controller State Transitions

# Section 30 LCD Controller (LCDC)

A unified memory architecture is adopted for the LCD controller (LCDC) so that the image data for display is stored in system memory. The LCDC module reads data from system memory, uses the palette memory to determine the colors, then puts the display on the LCD panel. It is possible to connect the LCDC to the LCD module of most types other than microcomputer bus interface types and NTSC/PAL types and those that apply the LVDS interface.

# 30.1 Features

The LCDC has the following features.

- Panel interface

- Serial interface method

- Supports data formats for STN/dual-STN/TFT panels (8/12/16/18-bit bus width) \*<sup>1</sup>

- Supports 4/8/15/16-bpp (bits per pixel) color modes

- Supports 1/2/4/6-bpp grayscale modes

- Supports LCD-panel sizes from  $16 \times 1$  to  $1024 \times 1024^{*^2}$

- 24-bit color palette memory (16 of the 24 bits are valid; R:5/G:6/B:5)

- STN/DSTN panels are prone to flicker and shadowing. The controller applies 65536-color control by 24-bit space-modulation FRC with 8-bit RGB values for reduced flicker.

- Dedicated display memory is unnecessary using part of the SDRAM connected to area 3 of the CPU as system memory.

- The display is stable because of the large 2.4-kbyte line buffer

- Supports the inversion of the output signal to suit the LCD panel's signal polarity

- Supports the selection of data formats (the endian setting for bytes, backed pixel method) by register settings

- A hardware-rotation mode is included to support the use of landscape-format LCD panels as portrait-format LCD panels (the horizontal width of the panel before rotation must be within 320 pixels—see table 30.4).

- Notes: 1. When connecting the LCDC to a TFT panel with an unwired 18-bit bus, the lower bit lines should be connected to GND or to the lowest bit from which data is output.

- 2. For details, see section 30.4.1, Size of LCD Modules Which Can Be Displayed with this LCDC.

| Abbrev.     | Bit 31/<br>23/15/7 | Bit 30/<br>22/14/6 | Bit 29/<br>21/13/5 | Bit 28/<br>20/12/4 | Bit 27/<br>19/11/3 | Bit 26/<br>18/10/2 | Bit 25/<br>17/9/ 1 | Bit 24/<br>16/8/0 | Module |

|-------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|-------------------|--------|

| DMAARXTCNT0 | _                  | _                  | _                  | _                  | _                  | _                  | _                  | _                 | DMAC   |

|             | _                  | _                  | _                  | _                  | _                  | _                  | _                  | _                 |        |

|             | _                  | _                  | _                  | _                  | _                  | _                  | _                  | _                 | _      |

|             | _                  | _                  | _                  | _                  | _                  | _                  | _                  | _                 | _      |

| DMAATXSAR1  |                    | _                  |                    | _                  |                    | _                  | _                  | _                 |        |

|             | _                  | _                  | _                  | _                  | _                  | _                  |                    |                   |        |

|             | _                  | _                  | _                  | _                  | _                  | _                  | _                  | _                 |        |

|             | _                  | —                  | _                  | _                  | _                  | _                  | _                  | _                 |        |

| DMAARXDAR1  | _                  | _                  | _                  | _                  | _                  | _                  | _                  | _                 |        |

|             | _                  | _                  | _                  | _                  | _                  | _                  | _                  | _                 |        |

|             | _                  | _                  | _                  | _                  | _                  | _                  | _                  | _                 |        |

|             | _                  | _                  | —                  | —                  | —                  | —                  | _                  |                   |        |

| DMAATXTCR1  | _                  | _                  | _                  | _                  | _                  | _                  | _                  |                   |        |

|             | _                  |                    |                    |                    |                    |                    |                    |                   |        |

|             | _                  | _                  |                    | _                  |                    | _                  | _                  | _                 |        |

|             | _                  | _                  |                    | _                  |                    | _                  | _                  | _                 |        |

| DMAARXTCR1  | _                  | _                  |                    | _                  |                    | _                  | _                  | _                 |        |

|             | _                  | _                  |                    | _                  |                    | _                  | _                  | _                 |        |

|             | _                  | —                  | —                  | —                  | —                  | —                  | —                  |                   | _      |

|             | _                  | —                  | —                  | —                  | —                  | —                  | —                  |                   | _      |

| DMAACR1     | —                  | —                  | —                  | —                  | —                  | —                  | RAM1               | RAM0              | _      |

|             | _                  | _                  | _                  | —                  | _                  | RAR                | RDS                | RDE               | _      |

|             | _                  | _                  | _                  | _                  | _                  | _                  | TAM1               | TAM0              |        |

|             | _                  | —                  | —                  | —                  | —                  | TAR                | TDS                | TDE               | _      |

| DMAATXTCNT1 | —                  | —                  | —                  | —                  | —                  | —                  | —                  |                   | _      |

|             | _                  | —                  | —                  | —                  | —                  | —                  | —                  |                   | _      |

|             |                    | _                  |                    |                    |                    |                    |                    |                   |        |

|             | _                  | _                  |                    |                    |                    |                    |                    |                   |        |

| DMAARXTCNT1 | _                  | _                  | _                  | _                  | _                  | _                  | _                  |                   | _      |

|             |                    | _                  |                    |                    |                    |                    |                    |                   |        |

|             |                    | _                  |                    |                    |                    |                    |                    |                   |        |

|             |                    | _                  | _                  |                    | _                  |                    | _                  |                   | _      |

| Abbrev.    | Bit 31/<br>23/15/7 | Bit 30/<br>22/14/6 | Bit 29/<br>21/13/5 | Bit 28/<br>20/12/4 | Bit 27/<br>19/11/3 | Bit 26/<br>18/10/2 | Bit 25/<br>17/9/ 1 | Bit 24/<br>16/8/0 | Module |

|------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|-------------------|--------|

| SSIRDR0    |                    | _                  | _                  |                    | _                  | _                  | _                  |                   | SSI(0) |

|            |                    |                    |                    |                    |                    | _                  |                    |                   | _      |

|            |                    | _                  | _                  | _                  | _                  | _                  | _                  |                   | _      |

|            |                    | _                  | _                  |                    | _                  |                    |                    |                   | _      |

| SSICR1     | _                  | _                  | _                  | DMEN               | UIEN               | OIEN               | IIEN               | DIEN              | SSI(1) |

|            | CHNL1              | CHNL0              | DWL2               | DWL1               | DWL0               | SWL2               | SWL1               | SWL0              | _      |

|            | SCKD               | SWSD               | SCKP               | SWSP               | SPDP               | SDTA               | PDTA               | DEL               | _      |

|            | BREN               | CKDV               | CKDV               | CKDV               | MUEN               | CPEN               | TRMD               | EN                | _      |

| SSISR1     | _                  | _                  | _                  | DMRQ               | UIRQ               | OIRQ               | IIRQ               | DIRQ              | _      |

|            |                    |                    | _                  |                    |                    |                    | _                  |                   | _      |

|            |                    | _                  | _                  | _                  | _                  | _                  |                    | _                 | _      |

|            | _                  | —                  | _                  | —                  | CHNO1              | CHNO0              | SWNO               | IDST              |        |

| SSITDR1    | _                  | _                  | _                  | _                  | _                  | _                  | _                  | _                 | _      |

|            |                    |                    |                    |                    | _                  | _                  | _                  |                   | _      |

|            |                    |                    |                    |                    | _                  | _                  | _                  |                   | _      |

|            |                    | _                  | _                  | _                  | _                  | _                  | _                  |                   |        |

| SSIRDR1    |                    |                    |                    |                    | _                  | _                  | _                  |                   | _      |

|            |                    | _                  | _                  | _                  | _                  | _                  |                    |                   | _      |

|            |                    |                    |                    |                    | _                  | _                  | _                  |                   | _      |

|            |                    |                    |                    |                    | _                  | _                  | _                  |                   | _      |

| HcRevision |                    | _                  |                    | _                  | _                  | _                  | _                  |                   | USB    |

|            |                    | _                  | _                  | _                  | _                  | _                  | _                  |                   |        |

|            |                    | _                  | _                  | _                  | _                  | _                  | _                  |                   |        |

|            | REV                | REV               |        |

| HcControl  |                    |                    |                    |                    |                    |                    | _                  |                   | _      |

|            |                    |                    |                    |                    |                    |                    | _                  |                   | _      |

|            |                    |                    |                    |                    | _                  | RWE                | RWC                | IR                | _      |

|            | HCFS1              | HCFS0              | BLE                | CLE                | IE                 | PLE                | CBSR1              | CBSR0             | _      |

| HcCommand  |                    |                    |                    |                    |                    |                    |                    |                   | _      |

| status     |                    | _                  |                    |                    | _                  | _                  | SOC1               | SOC0              | _      |

|            |                    | _                  | _                  | _                  | _                  | _                  | _                  | _                 |        |

|            |                    |                    |                    |                    | OCR                | BLF                | CLF                | HCR               |        |