Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

# **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                        |

|---------------------------------|--------------------------------------------------------|

| Product Status                  | Obsolete                                               |

| Core Processor                  | Z8S180                                                 |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                          |

| Speed                           | 33MHz                                                  |

| Co-Processors/DSP               | -                                                      |

| RAM Controllers                 | DRAM                                                   |

| Graphics Acceleration           | No                                                     |

| Display & Interface Controllers | -                                                      |

| Ethernet                        | -                                                      |

| SATA                            | -                                                      |

| USB                             | -                                                      |

| Voltage - I/O                   | 5.0V                                                   |

| Operating Temperature           | 0°C ~ 70°C (TA)                                        |

| Security Features               | -                                                      |

| Package / Case                  | 68-LCC (J-Lead)                                        |

| Supplier Device Package         | 68-PLCC                                                |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8s18033vsc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **GENERAL DESCRIPTION** (Continued)

Power connections follow the conventional descriptions below:

| Connection | Circuit         | Device          |  |

|------------|-----------------|-----------------|--|

| Power      | V <sub>CC</sub> | V <sub>DD</sub> |  |

| Ground     | GND             | V <sub>SS</sub> |  |

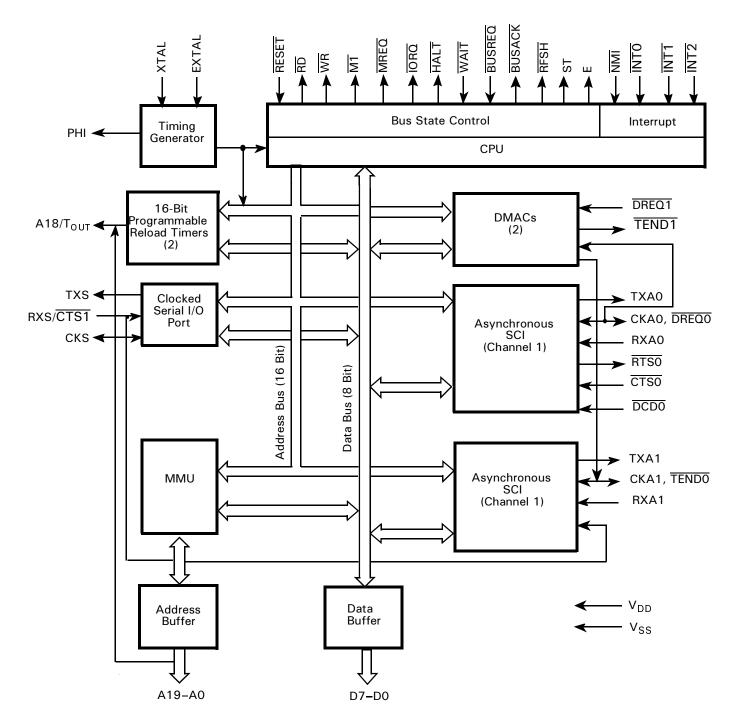

Figure 1. Z8S180/Z8L180 Functional Block Diagram

# PIN IDENTIFICATION (Continued)

Table 2. Pin Status During RESET, BUSACK, and SLEEP Modes

| Pin Num  | ber and Packa | age Type |                     |                       |                 | Pin Status      |                 |

|----------|---------------|----------|---------------------|-----------------------|-----------------|-----------------|-----------------|

| QFP      | PLCC          | DIP      | Default<br>Function | Secondary<br>Function | RESET           | BUSACK          | SLEEP           |

|          |               |          | NMI                 | runction              |                 |                 |                 |

| 1        | 9             | 8        |                     |                       | IN              | IN              | IN              |

| 3        |               |          | NC                  |                       |                 |                 |                 |

|          | 10            | 9        | NC<br>INTO          |                       | INI             | INI             | INI             |

| 4        |               | 10       | INTO<br>INT1        |                       | IN              | IN              | IN              |

| 5        | 11<br>12      | 11       | INT 1               |                       | IN<br>IN        | IN<br>IN        | IN<br>IN        |

| 6<br>7   | 13            | 12       | ST                  |                       |                 |                 |                 |

|          | 14            |          |                     |                       | High            | High            | High            |

| 9        | 15            | 13<br>14 | A0                  |                       | 3T<br>3T        | 3T<br>3T        | High            |

| 10       | 16            | 15       | A1                  |                       | 3T              |                 | High            |

|          | 17            | 16       | A2<br>A3            |                       | 3T              | 3T<br>3T        | High            |

| 11       | 17            | 10       |                     |                       |                 |                 | High            |

|          |               | 47       | V <sub>SS</sub>     |                       | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> |

| 13       | 19            | 17       | A4                  |                       | 3T              | 3T              | High            |

| 14       | 00            | 40       | NC                  |                       | 0.7             | 0.7             |                 |

| 15       | 20            | 18       | A5                  |                       | 3T              | 3T              | High            |

| 16       | 21            | 19       | A6                  |                       | 3T              | 3T              | High            |

| 17       | 22            | 20       | A7                  |                       | 3T              | 3T              | High            |

| 18       | 23            | 21       | A8                  |                       | 3T              | 3T              | High            |

| 19       | 24            | 22       | A9                  |                       | 3T              | 3T              | High            |

| 20       | 25            | 23       | A10                 |                       | 3T              | 3T              | High            |

| 21       | 26            | 24       | A11                 |                       | 3T              | 3T              | High            |

| 22       |               |          | NC                  |                       |                 |                 |                 |

| 23       | 0.7           | 0.5      | NC<br>A 1 2         |                       | 0.7             | O.T.            | 11.1            |

| 24       | 27            | 25       | A12                 |                       | 3T              | 3T              | High            |

| 25       | 28            | 26       | A13                 |                       | 3T              | 3T              | High            |

| 26<br>27 | 29<br>30      | 27       | A14                 |                       | 3T<br>3T        | 3T              | High            |

| 28       | 30            | 28<br>29 | A15<br>A16          |                       | 31<br>3T        | 3T<br>3T        | High<br>High    |

| 29       | 31            | 30       | A16                 |                       | 31<br>3T        | 3T              | High            |

| 30       | ٥٧            | 30       | NC                  |                       | <b>ا</b> ا      | 31              | піуп            |

| 31       | 33            | 31       | A18                 |                       | 3T              | 3T              | High            |

| JI       | JJ            | JI       |                     |                       | N/A             | OUT             | OUT             |

| 22       | 2.4           | 20       | T <sub>OUT</sub>    |                       |                 |                 |                 |

| 32       | 34            | 32       | V <sub>DD</sub>     |                       | V <sub>DD</sub> | V <sub>DD</sub> | V <sub>DD</sub> |

| 33       | 35            |          | A19                 |                       | 3T              | 3T              | High            |

| 34       | 36            | 33       | V <sub>SS</sub>     |                       | $V_{SS}$        | V <sub>SS</sub> | V <sub>SS</sub> |

| 35       | 37            | 34       | D0                  |                       | 3T              | 3T              | 3T              |

| 36       | 38            | 35       | D1                  |                       | 3T              | 3T              | 3T              |

| 37       | 39            | 36       | D2                  |                       | 3T              | 3T              | 3T              |

| 38       | 40            | 37       | D3                  |                       | 3T              | 3T              | 3T              |

Table 2. Pin Status During RESET, BUSACK, and SLEEP Modes (Continued)

| Pin Num | ber and Packa | age Type     |                     |                       |       | Pin Status |       |

|---------|---------------|--------------|---------------------|-----------------------|-------|------------|-------|

| QFP     | PLCC          | DIP          | Default<br>Function | Secondary<br>Function | RESET | BUSACK     | SLEEF |

| 39      | 41            | 38           | D4                  |                       | 3T    | 3T         | 3T    |

| 40      | 42            | 39           | D5                  |                       | 3T    | 3T         | 3T    |

| 41      | 43            | 40           | D6                  |                       | 3T    | 3T         | 3T    |

| 42      |               |              | NC                  |                       |       |            |       |

| 43      |               |              | NC                  |                       |       |            |       |

| 44      | 44            | 41           | D7                  |                       | 3T    | 3T         | 3T    |

| 45      | 45            | 42           | RTS0                |                       | High  | OUT        | High  |

| 46      | 46            | 43           | CTS0                |                       | IN    | OUT        | IN    |

| 47      | 47            | 44           | DCD0                |                       | IN    | IN         | IN    |

| 48      | 48            | 45           | TXA0                |                       | High  | OUT        | OUT   |

| 49      | 49            | 46           | RXA0                |                       | IN    | IN         | IN    |

| 50      | 50            | 47           | CKA0                |                       | 3T    | I/O        | I/O   |

|         |               |              | DREQ0               |                       | N/A   | IN         | IN    |

| 51      |               |              | NC                  |                       |       |            |       |

| 52      | 51            | 48           | TXA1                |                       | High  | OUT        | OUT   |

| 53      | 52            |              | TEST                |                       |       |            |       |

| 54      | 53            | 49           | RXA1                |                       | IN    | IN         | IN    |

| 55      | 54            | 50           | CKA1                |                       | 3T    | I/O        | I/O   |

|         |               |              | TEND0               |                       | N/A   | High       | High  |

| 56      | 55            | 51           | TXS                 |                       | High  | OUT        | OUT   |

| 57      | 56            | 52           | RXS                 |                       | IN    | IN         | IN    |

|         |               |              | CTS1                |                       | N/A   | IN         | IN    |

| 58      | 57            | 53           | CKS                 |                       | 3T    | I/O        | I/O   |

| 59      | 58            | 54           | DREQ1               |                       | IN    | 3T         | IN    |

| 60      | 59            | 55           | TEND1               |                       | High  | OUT        | High  |

| 61      | 60            | 56           | HALT                |                       | High  | High       | Low   |

| 62      |               |              | NC                  |                       |       |            |       |

| 63      |               |              | NC                  |                       |       |            |       |

| 64      | 61            | 57           | RFSH                |                       | High  | OUT        | High  |

| 65      | 62            | 58           | ĪORQ                |                       | High  | 3T         | High  |

| 66      | 63            | 59           | MREQ                |                       | High  | 3T         | High  |

| 67      | 64            | 60           | Е                   |                       | Low   | OUT        | OUT   |

| 68      | 65            | 61           | M1                  |                       | High  | High       | High  |

| 69      | 66            | 62           | WR                  |                       | High  | 3T         | High  |

| 70      | 67            | 63           | RD                  |                       | High  | 3T         | High  |

| 71      | 68            | 64           | PHI                 |                       | OUT   | OUT        | OUT   |

| 72      | 1             | 1            | V <sub>SS</sub>     |                       | GND   | GND        | GND   |

| 73      | 2             |              | V <sub>SS</sub>     |                       | GND   | GND        | GND   |

| 74      | 3             | 2            | XTAL                |                       | OUT   | OUT        | OUT   |

| 75      | <del>-</del>  | <del>-</del> | NC                  |                       |       |            |       |

## PIN DESCRIPTIONS (Continued)

ways recognized at the end of an instruction, regardless of the state of the interrupt-enable flip-flops. This signal forces CPU execution to continue at location 0066H.

**PHI.** System Clock (Output). The output is used as a reference clock for the MPU and the external system. The frequency of this output may be one-half, equal to, or twice the crystal or input clock frequency.

RD. Read (Output, active Low, 3-state). RD indicates that the CPU wants to read data from either memory or an I/O device. The addressed I/O or memory device should use this signal to gate data onto the CPU data bus.

RFSH. Refresh (Output, active Low). Together with MREQ, RFSH indicates that the current CPU machine cycle and the contents of the address bus should be used for refresh of dynamic memories. The low-order 8 bits of the address bus (A7–A0) contain the refresh address. *This signal is analogous to the REF signal of the Z64180*.

**RTSO**. Request to Send 0 (Output, active Low); a programmable MODEM control signal for ASCI channel 0.

**RXA0**, **RXA1**. Receive Data 0 and 1 (Input). These signals are the receive data for the ASCI channels.

**RXS.** Clocked Serial Receive Data (Input). This line is the receive data for the CSI/O channel. RXS is multiplexed with the CTS1 signal for ASCI channel 1.

**ST.** Status (Output). This signal is used with the  $\overline{M1}$  and  $\overline{HALT}$  output to decode the status of the CPU machine cycle. See Table 3.

Table 3. Status Summary

| ST | HALT | M1 | Operation                                       |

|----|------|----|-------------------------------------------------|

| 0  | 1    | 0  | CPU Operation (1st Opcode Fetch)                |

| 1  | 1    | 0  | CPU Operation (2nd Opcode and 3rd Opcode Fetch) |

| 1  | 1    | 1  | CPU Operation (MC Except Opcode Fetch)          |

| 0  | Χ    | 1  | DMA Operation                                   |

| 0  | 0    | 0  | HALT Mode                                       |

| 1  | 0    | 1  | SLEEP Mode (Including SYSTEM STOP Mode)         |

Notes:

X = Do not care.

MC = Machine Cycle.

**TENDO**, **TEND1**. Transfer End 0 and 1 (Outputs, active Low). This output is asserted active during the most recent WRITE cycle of a DMA operation. It is used to indicate the end of the block transfer. **TENDO** is multiplexed with CKA1.

**TEST.** Test (Output, not in DIP version). This pin is for test and should be left open.

$T_{OUT}$ . Timer Out (Output).  $T_{OUT}$  is the output from PRT channel 1. This line is multiplexed with A18 of the address bus.

**TXA0.** TXA1. Transmit Data 0 and 1 (Outputs). These signals are the transmitted data from the ASCI channels. Transmitted data changes are with respect to the falling edge of the transmit clock.

**TXS.** Clocked Serial Transmit Data (Output). This line is the transmitted data from the CSI/O channel.

WAIT. Wait (Input, active Low). WAIT indicates to the MPU that the addressed memory or I/O devices are not ready for data transfer. This input is sampled on the falling edge of T2 (and subsequent WAIT states). If the input is sampled Low, then the additional WAIT states are inserted until the WAIT input is sampled High, at which time execution continues.

WR. WRITE (Output, active Low, 3-state). WR indicates that the CPU data bus holds valid data to be stored at the addressed I/O or memory location.

**XTAL.** Crystal Oscillator Connection (Input). This pin should be left open if an external clock is used instead of a crystal. The oscillator input is not a TTL level (see <u>DC Characteristics</u>).

Several pins are used for different conditions, depending on the circumstance.

#### **ARCHITECTURE**

The Z180 combines a high-performance CPU core with a variety of system and I/O resources useful in a broad range of applications. The CPU core consists of five functional blocks: clock generator, bus state controller, Interrupt controller, memory management unit (MMU), and the central processing unit (CPU). The integrated I/O resources make up the remaining four functional blocks: direct memory access (DMA) control (2 channels), asynchronous serial communication interface (ASCI, 2 channels) programmable reload timers (PRT, 2 channels), and a clock serial I/O (CSI/O) channel.

**Clock Generator.** This logic generates a system clock from an external crystal or clock input. The external clock is divided by 2 or 1 and provides the timing for both internal and external devices.

**Bus State Controller.** This logic performs all of the status and bus-control activity associated with the CPU and some on-chip peripherals. Also includes wait-state timing, reset cycles, DRAM refresh, and DMA bus exchanges.

**Interrupt Controller.** This logic monitors and prioritizes the variety of internal and external interrupts and traps to provide the correct responses from the CPU. To maintain compatibility with the Z80 CPU, three different interrupts modes are supported.

Memory Management Unit. The MMU allows the user to map the memory used by the CPU (logically only 64KB) into the 1-MB addressing range supported by the Z8S180/Z8L180. The organization of the MMU object

code maintains compatibility with the Z80 CPU, while offering access to an extended memory space. Accomplished by using an effective common-area/banked-area scheme.

Central Processing Unit. The CPU is microcoded to provide a core that is object-code compatible with the Z80 CPU. It also provides a superset of the Z80 instruction set, including 8-bit multiplication. The core is modified to allow many of the instructions to execute in fewer clock cycles.

**DMA Controller.** The DMA controller provides high-speed transfers between memory and I/O devices. Transfer operations supported are memory-to-memory, memory to/from I/O, and I/O-to-I/O. Transfer modes supported are request, burst, and cycle steal. DMA transfers can access the full 1-MB address range with a block length up to 64 KB, and can cross over 64K boundaries.

#### Asynchronous Serial Communication Interface (ASCI).

The ASCI logic provides two individual full-duplex UARTs. Each channel includes a programmable baud rate generator and modem control signals. The ASCI channels can also support a multiprocessor communication format as well as break detection and generation

Programmable Reload Timers (PRT). This logic consists of two separate channels, each containing a 16-bit counter (timer) and count reload register. The time base for the counters is derived from the system clock (divided by 20) before reaching the counter. PRT channel 1 provides an optional output to allow for waveform generation.

# **OPERATION MODES** (Continued)

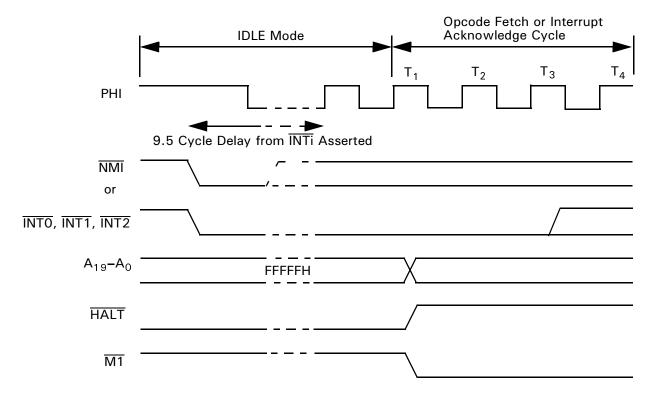

Figure 15. Z8S180/Z8L180 IDLE Mode Exit Due To External Interrupt

While the Z8S180/Z8L180 is in IDLE mode, it grants the bus to an external Master if the BREXT bit (CCR5) is 1. Figure 16 depicts the timing for this sequence.

After the external Master negates the Bus Request, the Z8S180/Z8L180 disables the PHI clock and remains in IDLE mode.

**Note:** A response to a bus request takes 8 clock cycles longer than in normal operation.

Table 7. Z8L180 DC Characteristics  $V_{DD} = 3.3V \pm 10\%; V_{SS} = 0V$

| Symbol           | Item                                                      | Condition                                        | Min                  | Тур | Max                     | Unit |

|------------------|-----------------------------------------------------------|--------------------------------------------------|----------------------|-----|-------------------------|------|

| V <sub>IH1</sub> | Input H Voltage<br>RESET, EXTAL, NMI                      |                                                  | V <sub>DD</sub> -0.6 |     | V <sub>DD</sub><br>+0.3 | V    |

| V <sub>IH2</sub> | Input H Voltage<br>Except RESET, EXTAL, NMI               |                                                  | 2.0                  |     | V <sub>DD</sub><br>+0.3 | V    |

| V <sub>IL1</sub> | Input L Voltage<br>RESET, EXTAL, NMI                      |                                                  | -0.3                 |     | 0.6                     | V    |

| V <sub>IL2</sub> | Input L Voltage<br>Except RESET, EXTAL, NMI               |                                                  | -0.3                 |     | 0.8                     | V    |

| V <sub>OH</sub>  | Outputs H Voltage                                         | $I_{OH} = -200  \mu A$                           | 2.15                 |     |                         | V    |

|                  | All outputs                                               | $I_{OH} = -20 \mu A$                             | V <sub>DD</sub> -0.6 |     |                         | V    |

| V <sub>OL</sub>  | Outputs L Voltage<br>All Outputs                          | $I_{OL} = 4 \text{ mA}$                          |                      |     | 0.4                     | V    |

| I <sub>IL</sub>  | Input Leakage<br>Current All Inputs<br>Except XTAL, EXTAL | $V_{IN} = 0.5 \sim V_{DD} - 0.5$                 |                      |     | 1.0                     | μΑ   |

| I <sub>TL</sub>  | Three State Leakage<br>Current                            | $V_{ N} = 0.5 \sim V_{DD} - 0.5$                 |                      |     | 1.0                     | μΑ   |

| I <sub>DD1</sub> | Power Dissipation                                         | F = 20  MHz                                      |                      | 30  | 60                      | mA   |

|                  | (Normal Operation)                                        | 4 MHz                                            |                      | 4   | 10                      |      |

|                  | Power Dissipation                                         | F = 20 MHz                                       |                      | 5   | 10                      |      |

|                  | (SYSTEM STOP mode)                                        | 4 MHz                                            |                      | 2   | 5                       |      |

| C <sub>P</sub>   | Pin Capacitance                                           | $V_{IN} = OV, f = 1 MHz$<br>$T_A = 25^{\circ} C$ |                      |     | 12                      | pF   |

| Note:            |                                                           |                                                  |                      |     |                         |      |

<sup>1.</sup>  $V_{IHmin} = V_{DD}$  –1.0V,  $V_{ILmax} = 0.6V$  (All output terminals are at NO LOAD.)  $V_{DD} = 3.0V$ .

# AC CHARACTERISTICS—Z8S180 (Continued)

Table 8. Z8S180 AC Characteristics (Continued)  $V_{DD}=5V\pm10\%$  or  $V_{DD}=3.3V\pm10\%$ ; 33-MHz Characteristics Apply Only to 5V Operation

|        |                   |                                                           | Z8S180 | —20 MHz                     | Z8S180 | -33 MHz                    |      |

|--------|-------------------|-----------------------------------------------------------|--------|-----------------------------|--------|----------------------------|------|

| Number | Symbol            | Item                                                      | Min    | Max                         | Min    | Max                        | Unit |

| 32     | t <sub>INTH</sub> | INT Hold Time from PHI Fall                               | 10     | _                           | 10     | _                          | ns   |

| 33     | t <sub>NMIW</sub> | NMI Pulse Width                                           | 35     | _                           | 25     | _                          | ns   |

| 34     | t <sub>BRS</sub>  | BUSREQ Set-up Time to PHI Fall                            | 10     | _                           | 10     | _                          | ns   |

| 35     | t <sub>BRH</sub>  | BUSREQ Hold Time from PHI Fall                            | 10     | _                           | 10     |                            | ns   |

| 36     | t <sub>BAD1</sub> | PHI Rise to BUSACK Fall Delay                             | _      | 25                          | _      | 15                         | ns   |

| 37     | t <sub>BAD2</sub> | PHI Fall to BUSACK Rise Delay                             | _      | 25                          | _      | 15                         | ns   |

| 38     | t <sub>BZD</sub>  | PHI Rise to Bus Floating Delay Time                       |        | 40                          | _      | 30                         | ns   |

| 39     | t <sub>MEWH</sub> | MREQ Pulse Width (High)                                   | 35     | _                           | 25     | _                          | ns   |

| 40     | t <sub>MEWL</sub> | MREQ Pulse Width (Low)                                    | 35     | _                           | 25     | _                          | ns   |

| 41     | t <sub>RFD1</sub> | PHI Rise to RFSH Fall Delay                               | _      | 20                          | _      | 15                         | ns   |

| 42     | t <sub>RFD2</sub> | PHI Rise to RFSH Rise Delay                               | _      | 20                          | _      | 15                         | ns   |

| 43     | t <sub>HAD1</sub> | PHI Rise to HALT Fall Delay                               | _      | 15                          | _      | 15                         | ns   |

| 44     | t <sub>HAD2</sub> | PHI Rise to HALT Rise Delay                               | _      | 15                          | _      | 15                         | ns   |

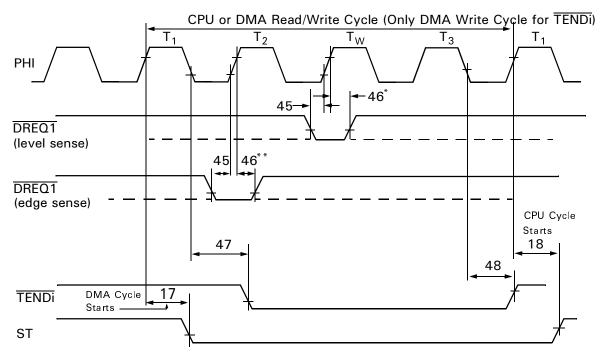

| 45     | t <sub>DRQS</sub> | DREQ1 Set-up Time to PHI Rise                             | 20     | _                           | 15     | _                          | ns   |

| 46     | t <sub>DRQH</sub> | DREQ1 Hold Time from PHI Rise                             | 20     | _                           | 15     | _                          | ns   |

| 47     | t <sub>TED1</sub> | PHI Fall to TENDi Fall Delay                              | _      | 25                          | _      | 15                         | ns   |

| 48     | t <sub>TED2</sub> | PHI Fall to TENDi Rise Delay                              | _      | 25                          | _      | 15                         | ns   |

| 49     | t <sub>ED1</sub>  | PHI Rise to E Rise Delay                                  | _      | 30                          | _      | 15                         | ns   |

| 50     | t <sub>ED2</sub>  | PHI Fall or Rise to E Fall Delay                          | _      | 30                          | _      | 15                         | ns   |

| 51     | P <sub>WEH</sub>  | E Pulse Width (High)                                      | 25     | _                           | 20     | _                          | ns   |

| 52     | P <sub>WEL</sub>  | E Pulse Width (Low)                                       | 50     | _                           | 40     | _                          | ns   |

| 53     | t <sub>Er</sub>   | Enable Rise Time                                          | _      | 10                          | _      | 10                         | ns   |

| 54     | t <sub>Ef</sub>   | Enable Fall Time                                          | _      | 10                          | _      | 10                         | ns   |

| 55     | t <sub>TOD</sub>  | PHI Fall to Timer Output Delay                            | _      | 75                          | _      | 50                         | ns   |

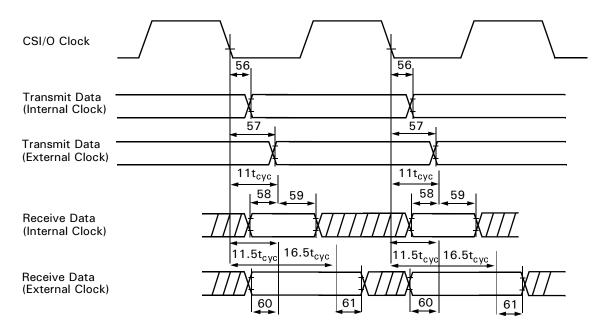

| 56     | t <sub>STDI</sub> | CSI/O Transmit Data Delay Time (Internal Clock Operation) | _      | 2                           | _      | 2                          | tcyc |

| 57     | t <sub>STDE</sub> | CSI/O Transmit Data Delay Time (External Clock Operation) | _      | 7.5 t <sub>CYC</sub><br>+75 | -      | 75 t <sub>CYC</sub><br>+60 | ns   |

| 58     | t <sub>SRSI</sub> | CSI/O Receive Data Set-up Time (Internal Clock Operation) | 1      | _                           | 1      | _                          | tcyc |

| 59     | t <sub>SRHI</sub> | CSI/O Receive Data Hold Time (Internal Clock Operation)   | 1      | _                           | 1      | _                          | tcyc |

| 60     | t <sub>SRSE</sub> | CSI/O Receive Data Set-up Time (External Clock Operation) | 1      | _                           | 1      | _                          | tcyc |

| 61     | t <sub>SRHE</sub> | CSI/O Receive Data Hold Time (External Clock Operation)   | 1      | _                           | 1      | _                          | tcyc |

| 62     | t <sub>RES</sub>  | RESET Set-up Time to PHI Fall                             | 40     | _                           | 25     | _                          | ns   |

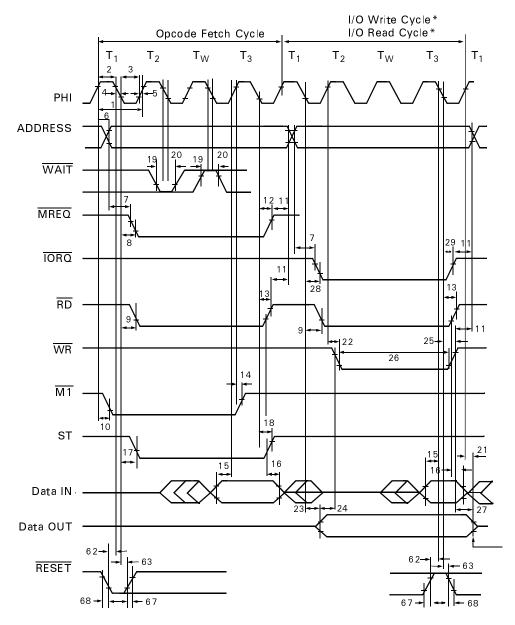

# **TIMING DIAGRAMS**

Note: \*Memory Read/Write Cycle timing is the same as I/O Read/Write Cycle except there are no automatic wait states  $(T_W)$ , and  $\overline{MREQ}$  is active instead of  $\overline{IORQ}$ .

Figure 20. CPU Timing

(Opcode Fetch Cycle, Memory Read Cycle,

Memory Write Cycle, I/O Write Cycle, I/O Read Cycle)

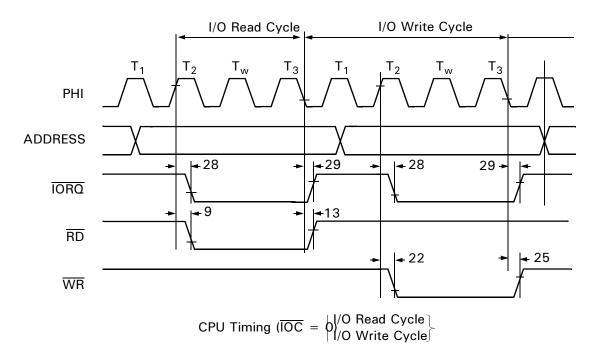

# **TIMING DIAGRAMS** (Continued)

Figure 22. CPU Timing ( $\overline{IOC} = 0$ ) (I/O Read Cycle, I/O Write Cycle)

#### Notes:

$^*T_{DRQS}$  and  $T_{DRQH}$  are specified for the rising edge of the clock followed by  $T_3$ .

Figure 23. DMA Control Signals

$<sup>**</sup>T_{DRQS}$  and  $T_{DRQH}$  are specified for the rising edge of the clock.

Figure 29. CSI/O Receive/Transmit Timing

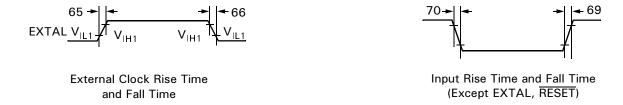

Figure 30. Rise Time and Fall Times

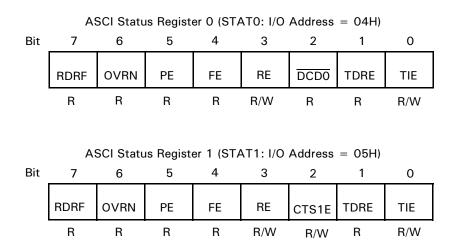

#### **ASCI STATUS REGISTER 0,1**

Each ASCI channel status register (STATO,1) allows interrogation of ASCI communication, error and modem control

signal status, and the enabling or disabling of ASCI interrupts.

Figure 35. ASCI Status Registers

RDRF: Receive Data Register Full (Bit 7). RDRF is set to 1 when an incoming data byte is loaded into an empty Rx FIFO. If a framing or parity error occurs, RDRF is still set and the receive data (which generated the error) is still loaded into the FIFO. RDRF is cleared to 0 by reading RDR and most recently received character in the FIFO from IOSTOP mode, during RESET and for ASCIO if the DCDO input is auto-enabled and is negated (High).

**OVRN:** Overrun Error (Bit 6). An overrun condition occurs if the receiver finishes assembling a character but the Rx FIFO is full so there is no room for the character. However, this status bit is not set until the most recent character received before the overrun becomes the oldest byte in the FIFO. This bit is cleared when software writes a 1 to the EFR bit in the CNTLA register. The bit may also be cleared by RESET in IOSTOP mode or ASCIO if the DCDO pin is auto enabled and is negated (High).

**Note:** When an overrun occurs, the receiver does not place the character in the shift register into the FIFO, nor any subsequent characters, until the most recent good character enters the top of the FIFO so that OVRN is set. Software then writes a 1 to EFR to clear it.

**PE: Parity Error (Bit 5).** A parity error is detected when parity checking is enabled. When the MOD1 bit in the

CNTLA register is 1, a character is assembled in which the parity does not match the PEO bit in the CNTLB register. However, this status bit is not set until or unless the error character becomes the oldest one in the Rx FIFO. PE is cleared when software writes a 1 to the EFR bit in the CNTRLA register. PE is also cleared by RESET in IOSTOP mode, or on ASCIO, if the DCDO pin is auto-enabled and is negated (High).

FE: Framing Error (Bit 4). A framing error is detected when the stop bit of a character is sampled as O/SPACE. However, this status bit is not set until/unless the error character becomes the oldest one in the Rx FIFO. FE is cleared when software writes a 1 to the EFR bit in the CNTLA register. FE is also cleared by RESET in IOSTOP mode, or on ASCIO, if the DCDO pin is auto-enabled and is negated (High).

REI: Receive Interrupt Enable (Bit 3). RIE should be set to 1 to enable ASCI receive interrupt requests. When RIE is 1, the Receiver requests an interrupt when a character is received and RDRF is set, but only if neither DMA channel requires its request-routing field to be set to receive data from this ASCI. That is, if SM1-0 are 11 and SAR17-16 are 10, or DIM1 is 1 and IAR17-16 are 10, then ASCII does not request an interrupt for RDRF. If RIE is 1, either ASCI requests an interrupt when OVRN, PE or FE is set, and

never both set to 1 at the same time. TE is cleared to 0 during RESET and IOSTOP mode.

SS2, 1, 0: Speed Select 2, 1, 0 (Bits 2–0). SS2, SS1 and SS0 select the CSI/O transmit/receive clock source and speed. SS2, SS1 and SS0 are all set to 1 during RESET. Table 11 indicates CSI/O Baud Rate Selection.

Table 11. CSI/O Baud Rate Selection

| SS2 | SS1 | SS0 | Divide Ratio                            |

|-----|-----|-----|-----------------------------------------|

| 0   | 0   | 0   | ÷20                                     |

| 0   | 0   | 1   | ÷40                                     |

| 0   | 1   | 0   | ÷80                                     |

| 0   | 1   | 1   | ÷160                                    |

| 1   | 0   | 0   | ÷320                                    |

| 1   | 0   | 1   | ÷640                                    |

| 1   | 1   | 0   | ÷1280                                   |

| 1   | 1   | 1   | External Clock Input<br>(Less Than ÷20) |

After  $\overline{\text{RESET}}$ , the CKS pin is configured as an external clock input (SS2, SS1, SS0 = 1). Changing these values causes CKS to become an output pin and the selected clock is output when transmit or receive operations are enabled.

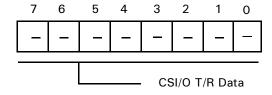

# CSI/O Transmit/Receive Data Register

#### Mnemonic TRDR Address 0BH

Figure 41. CSI/O Transmit/Receive Data Register

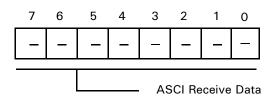

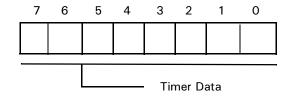

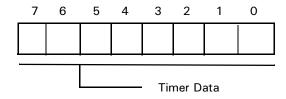

# Timer Data Register Channel 0 Low Mnemonic TMDR0L Address 0CH

Figure 42. Timer Register Channel 0 Low

# **Timer Data Register Channel 0H**

#### Mnemonic TMDR0H Address 0DH

Figure 43. Timer Data Register Channel 0 High

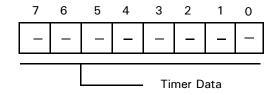

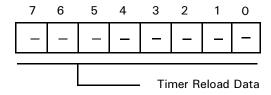

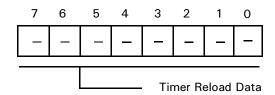

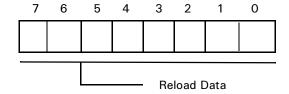

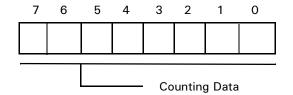

#### **Timer Reload Register Channel 0 Low**

Mnemonic RLDR0L Address 0EH

Figure 44. Timer Reload Register Low

#### **Timer Reload Register Channel 0 High**

Mnemonic RLDR0H Address 0FH

Figure 45. Timer Reload Register Channel 0 High

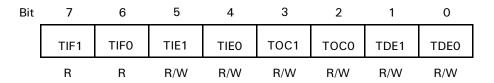

#### TIMER CONTROL REGISTER

The Timer Control Register (TCR) monitors both channels (PRTO, PRT1) TMDR status. It also controls the enabling

and disabling of down-counting and interrupts, and controls the output pin A18/T<sub>OUT</sub> for PRT1.

Figure 46. Timer Control Register (TCR: I/O Address = 10H)

TIF1: Timer Interrupt Flag 1 (Bit 7). When TMDR1 decrements to 0, TIF1 is set to 1. This condition generates an interrupt request if enabled by TIE1 = 1. TIF1 is reset to 0 when TCR is read and the higher or lower byte of TMDR1 is read. During RESET, TIF1 is cleared to 0.

**TIFO:** Timer Interrupt Flag 0 (Bit 6). When TMDRO decrements to 0, TIFO is set to 1. This condition generates an interrupt request if enabled by TIEO = 1. TIFO is reset to 0 when TCR is read and the higher or lower byte of TMDRO is read. During RESET, TIFO is cleared to 0.

**TIE1: Timer Interrupt Enable 1 (Bit 5).** When TIE0 is set to 1, TIF1 = 1 generates a CPU interrupt request. When TIE0 is reset to 0, the interrupt request is inhibited. During RESET, TIE0 is cleared to 0.

**TOC1**, **0**: **Timer Output Control (Bits 3, 2)**. TOC1 and TOC0 control the output of PRT1 using the multiplexed A18/T<sub>OUT</sub> pin as indicated in Table 12. During RESET, TOC1 and TOC0 are cleared to 0. If bit 3 of the IAR1B register is 1, the T<sub>OUT</sub> function is selected. By programming

TOC1 and TOC0, the A18/T<sub>OUT</sub> pin can be forced High, Low, or toggled when TMDR1 decrements to 0.

Table 12. Timer Output Control

| TOC1 | TOC0 |           | Output                                 |

|------|------|-----------|----------------------------------------|

| 0    | 0    | Inhibited | The A18/T <sub>OUT</sub> pin is not    |

|      |      |           | affected by the PRT                    |

| 0    | 1    | Toggled   | If bit 3 of IAR1B is 1, the            |

| 1    | 0    | 0         | A18/T <sub>OUT</sub> pin is toggled or |

| 1    | 1    | 1         | set Low or High as indicated           |

**TDE1**, **0**: **Timer Down Count Enable (Bits 1, 0)**. TDE1 and TDE0 enable and disable down-counting for TMDR1 and TMDR0, respectively. When TDEn (n = 0,1) is set to 1, down-counting is stopped and TMDRn is freely read or written. TDE1 and TDE0 are cleared to 0 during RESET and TMDRn does not decrement until TDEn is set to 1.

# ASCI EXTENSION CONTROL REGISTER CHANNEL 0 AND CHANNEL 1 (Continued)

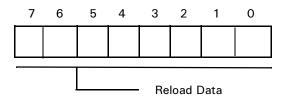

# **Timer Data Register Channel 1 Low**

Mnemonic TMDR1L Address 14H

Figure 48. Timer Data Register 1 Low

# **Timer Reload Register Channel 1 High**

Mnemonic RLDR1H Address 17H

Figure 51. Timer Reload Register Channel 1 High

# **Timer Data Register Channel 1 High**

Mnemonic TMDR1H Address 15H

Figure 49. Timer Data Register 1 High

# Free Running Counter (Read Only)

Mnemonic FRC Address 18H

Figure 52. Free Running Counter

# **Timer Reload Register Channel 1 Low**

Mnemonic RLDR1L Address 16

Figure 50. Timer Reload Channel 1 Low

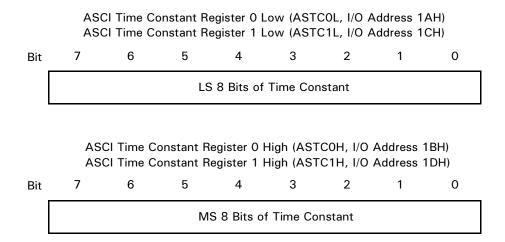

## **ASCI TIME CONSTANT REGISTERS**

If the SS2-0 bits of the CNTLB register are not 111, and the BRG mode bit in the ASEXT register is 1, the ASCI divides the PHI clock by two times the registers' 16-bit value, plus two. As a result, the clock is presented to the transmitter and receiver for division by 1, 16, or 64, and is output on the CKA pin.

If the SS2-0 bits in an ASCI CNTLB register are not 111, and the BRG mode bit in its Extension Control Register is 1, its *new* baud rate generator divides PHI for serial clocking, as follows:

bits/second =

$$f_{PHI}/(2*(TC+2) \times sampling rate)$$

where TC is the 16-bit value programmed into the ASCI Time Constant High and Low registers. If the ASCI multiplexed CKA pin is selected for the CKA function, it outputs the clock before the final division by the sampling rate, as follows:

$$f_{CKAout} = f_{PHI}/(2*(TC+2))$$

Find the TC value for a particular serial bit rate as follows:

$TC = (f_{PHI}/(2 \text{ x bits/second x sampling rate})) - 2$

Figure 53. ASCI Time Constant Registers

#### DMA SOURCE ADDRESS REGISTER CHANNEL 0

The DMA Source Address Register Channel 0 specifies the physical source address for channel 0 transfers. The register contains 20 bits and can specify up to 1024 KB memory addresses or up to 64-KB I/O addresses. Channel 0 source can be memory, I/O, or memory mapped I/O. For I/O, bits 17–16 of this register identify the Request Handshake signal.

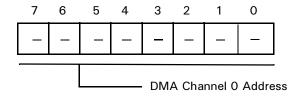

### **DMA Source Address Register, Channel 0 Low**

#### Mnemonic SAR0L Address 20H

Figure 55. DMA Source Address Register 0 Low

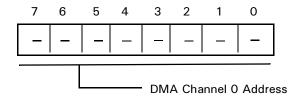

# DMA Source Address Register, Channel 0 High

Mnemonic SAR0H Address 21H

Figure 56. DMA Source Address Register 0 High

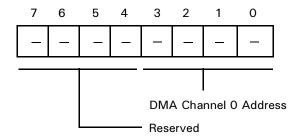

# **DMA Source Address Register Channel 0B**

#### Mnemonic SAR0B Address 22H

Figure 57. DMA Source Address Register 0B

If the source is in I/O space, bits 1–0 of this register select the DMA request signal for DMA0, as follows:

| Bit 1<br>(A17) | Bit 0<br>(A16) | DMA Transfer Request |

|----------------|----------------|----------------------|

| 0              | 0              | DREQ0 (external)     |

| 0              | 1              | RDRF (ASCIO)         |

| 1              | 0              | RDRF (ASCI1)         |

| 1              | 1              | Reserved             |

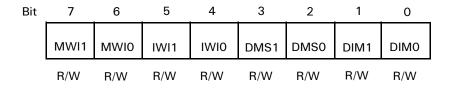

#### **DMA/WAIT CONTROL REGISTER**

The DMA/WAIT Control Register (DCNTL) controls the insertion of wait states into DMAC (and CPU) accesses of memory or I/O. Also, the register defines the Request signal

for each channel as level or edge sense. DCNTL also sets the DMA transfer mode for channel 1, which is limited to memory to/from I/O transfers.

Figure 73. DMA/WAIT Control Register (DCNTL: I/O Address = 32H)

MWI1, MWI0: Memory Wait Insertion (Bits 7–6). This bit specifies the number of wait states introduced into CPU or DMAC memory access cycles. MWI1 and MWI0 are set to 1 during RESET.

| MWI1 | MWIO | Wait State |

|------|------|------------|

| 0    | 0    | 0          |

| 0    | 1    | 1          |

| 1    | 0    | 2          |

| 1    | 1    | 3          |

**IWI1, IWI0:** I/O Wait Insertion (Bits 5–4). This bit specifies the number of wait states introduced into CPU or DMAC I/O access cycles. IWI1 and IWI0 are set to 1 during RESET.

| IWIO | Wait State       |

|------|------------------|

| 0    | 1                |

| 1    | 2                |

| 0    | 3                |

| 1    | 4                |

|      | 0<br>1<br>0<br>1 |

**Note:** These wait states are added to the 3-clock I/O cycle that is used to access the on-chip I/O registers. It is equally valid to regard these as 0 to 3 wait states added to a 4-clock external I/O cycle.

**DMS1**, **DMS0**: **DMA** Request Sense (Bits 3–2). DMS1 and DMS0 specify the DMA request sense for channel 0 and channel 1 respectively. When reset to 0, the input is level sense. When set to 1, the input is edge sense. DMS1 and DMS0 are cleared to 0 during RESET.

| DMSi | Sense       |

|------|-------------|

| 1    | Edge Sense  |

| 0    | Level Sense |

Typically, for an input/source device, the associated DMS bit should be programmed as 0 for level sense. The device takes a relatively long time to update its Request signal after the DMA channel reads data (in the first of the two machine cycles involved in transferring a byte).

An output/destination device takes much less time to update its Request signal after the DMA channel starts a WRITE operation to it (the second machine cycle of the two cycles involved in transferring a byte). With zero-wait state I/O cycles, a device cannot update its request signal in the required time, so edge sensing must be used.

A one-wait-state I/O cycle also does not provide sufficient time for updating, so edge sensing is again required.

**DIM1**, **DIM0**: **DMA Channel 1 I/O** and **Memory Mode (Bits 1–0)**. Specifies the source/destination and address modifier for channel 1 memory to/from I/O transfer modes. DIM1 and DIM0 are cleared to 0 during RESET.

Table 17. Channel 1 Transfer Mode

| DIM1  | DMIO   | Transfer Mode  | Address<br>Increment/Decrement |

|-------|--------|----------------|--------------------------------|

| DIIVI | DIVIIO | Transfer Wiode | mcrement/Decrement             |

| 0     | 0      | Memory→I/O     | MAR1 +1, IAR1 fixed            |

| 0     | 1      | Memory→I/O     | MAR1 -1, IAR1 fixed            |

| 1     | 0      | I/O→Memory     | IAR1 fixed, MAR1 +1            |

| 1     | 1      | I/O→Memory     | IAR1 fixed, MAR1 -1            |

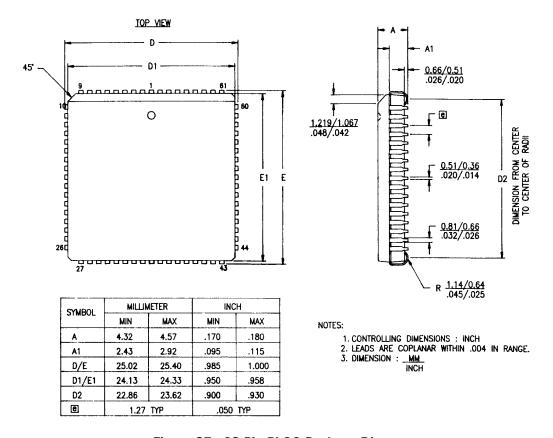

Figure 87. 68-Pin PLCC Package Diagram

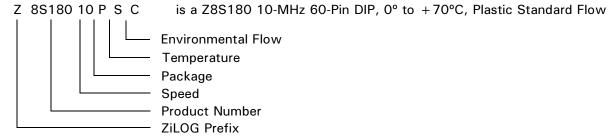

#### ORDERING INFORMATION

| Codes         |                                           |

|---------------|-------------------------------------------|

| Speed         | 10 = 10 MHz                               |

|               | 20 = 20  MHz                              |

|               | 33 = 33  MHz                              |

| Package       | P = 60-Pin Plastic DIP                    |

|               | V = 68-Pin PLCC                           |

|               | F = 80-Pin QFP                            |

| Temperature   | $S = 0^{\circ}C \text{ to } +70^{\circ}C$ |

|               | E = -40 °C to $+85$ °C                    |

| Environmental | C = Plastic Standard                      |

For fast results, contact your local ZiLOG sales office for assistance in ordering the part(s) required.

#### Example:

#### **Pre-Characterization Product**

The product represented by this document is newly introduced and ZiLOG has not completed the full characterization of the product. The document states what ZiLOG knows about this product at this time, but additional features or non-conformance with some aspects of the document may be found, either by ZiLOG or its customers in the course of further application and characterization work. In addition, ZiLOG cautions that delivery may be uncertain at times, due to start-up yield issues.

©2000 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZiLOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE.

Except with the express written approval of ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

ZiLOG, Inc.

910 East Hamilton Avenue, Suite 110

Campbell, CA 95008

Telephone (408) 558-8500

FAX (408) 558-8300

Internet: http://www.zilog.com