Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

# **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                        |

|---------------------------------|--------------------------------------------------------|

| Product Status                  | Obsolete                                               |

| Core Processor                  | Z8S180                                                 |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                          |

| Speed                           | 33MHz                                                  |

| Co-Processors/DSP               | -                                                      |

| RAM Controllers                 | DRAM                                                   |

| Graphics Acceleration           | No                                                     |

| Display & Interface Controllers | -                                                      |

| Ethernet                        | -                                                      |

| SATA                            | -                                                      |

| USB                             | -                                                      |

| Voltage - I/O                   | 5.0V                                                   |

| Operating Temperature           | 0°C ~ 70°C (TA)                                        |

| Security Features               | -                                                      |

| Package / Case                  | 68-LCC (J-Lead)                                        |

| Supplier Device Package         | 68-PLCC                                                |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8s18033vsg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **GENERAL DESCRIPTION** (Continued)

Power connections follow the conventional descriptions below:

| Connection | Circuit         | Device          |  |

|------------|-----------------|-----------------|--|

| Power      | V <sub>CC</sub> | V <sub>DD</sub> |  |

| Ground     | GND             | V <sub>SS</sub> |  |

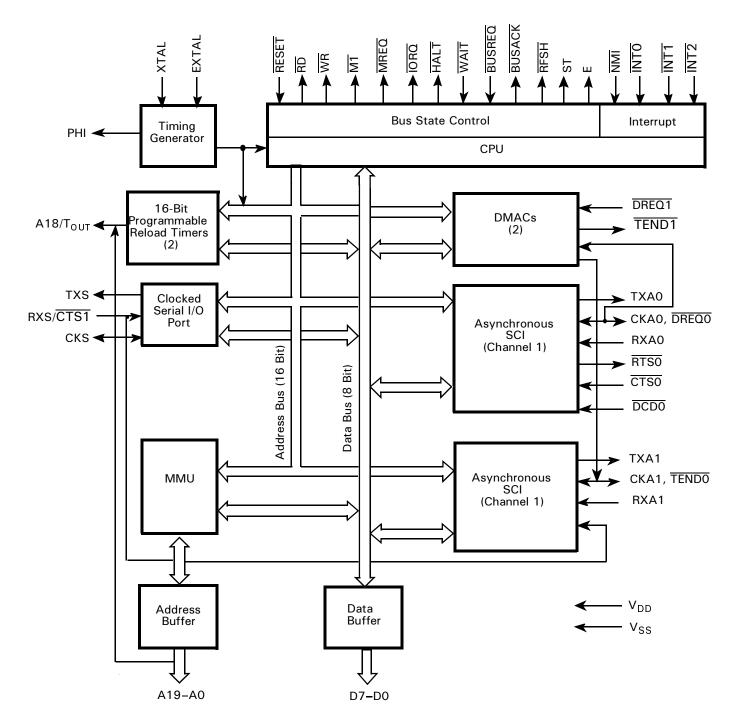

Figure 1. Z8S180/Z8L180 Functional Block Diagram

# PIN IDENTIFICATION (Continued)

Table 2. Pin Status During RESET, BUSACK, and SLEEP Modes (Continued)

| Pin Num | ber and Packa | ige Type | Pin Status          |                       |       |        |       |

|---------|---------------|----------|---------------------|-----------------------|-------|--------|-------|

| QFP     | PLCC          | DIP      | Default<br>Function | Secondary<br>Function | RESET | BUSACK | SLEEP |

| 76      | 4             | 3        | EXTAL               |                       | IN    | IN     | IN    |

| 77      | 5             | 4        | WAIT                |                       | IN    | IN     | IN    |

| 78      | 6             | 5        | BUSACK              |                       | High  | OUT    | OUT   |

| 79      | 7             | 6        | BUSREQ              |                       | IN    | IN     | IN    |

| 80      | 8             | 7        | RESET               |                       | IN    | IN     | IN    |

#### **OPERATION MODES** (Continued)

| Table 5. F | RETI Control | Signal | States |

|------------|--------------|--------|--------|

|------------|--------------|--------|--------|

| Machine<br>Cycle | States | Address    | Data    | RD | WR | MREQ | ĪORQ | M1<br>M1E=<br>1 | M1<br>M1E =<br>0 | HALT | ST |

|------------------|--------|------------|---------|----|----|------|------|-----------------|------------------|------|----|

| 1                | T1-T3  | 1st Opcode | EDH     | 0  | 1  | 0    | 1    | 0               | 1                | 1    | 0  |

| 2                | T1-T3  | 2nd Opcode | 4DH     | 0  | 1  | 0    | 1    | 0               | 1                | 1    | 0  |

|                  | Ti     | NA         | 3-state | 1  | 1  | 1    | 1    | 1               | 1                | 1    | 1  |

|                  | Ti     | NA         | 3-state | 1  | 1  | 1    | 1    | 1               | 1                | 1    | 1  |

|                  | Ti     | NA         | 3-state | 1  | 1  | 1    | 1    | 1               | 1                | 1    | 1  |

| 3                | T1-T3  | 1st Opcode | EDH     | 0  | 1  | 0    | 1    | 0               | 0                | 1    | 1  |

|                  | Ti     | NA         | 3-state | 1  | 1  | 1    | 1    | 1               | 1                | 1    | 1  |

| 4                | T1-T3  | 2nd Opcode | 4DH     | 0  | 1  | 0    | 1    | 0               | 1                | 1    | 1  |

| 5                | T1-T3  | SP         | Data    | 0  | 1  | 0    | 1    | 1               | 1                | 1    | 1  |

| 6                | T1-T3  | SP + 1     | Data    | 0  | 1  | 0    | 1    | 1               | 1                | 1    | 1  |

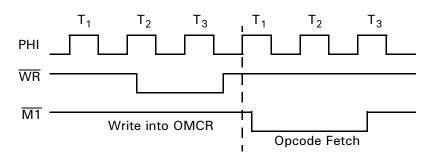

$\overline{\text{M1TE}}$  ( $\overline{\text{M1}}$  Temporary Enable). This bit controls the temporary assertion of the  $\overline{\text{M1}}$  signal. It is always read back as a 1 and is set to 1 during RESET.

When M1E is set to 0 to accommodate certain external Z80 peripheral(s), those same device(s) may require a pulse on M1 after programming certain of their registers to complete the function being programmed.

For example, when a control word is written to the Z80 PIO to enable interrupts, no enable actually takes place until the PIO sees an active  $\overline{\text{M1}}$  signal. When  $\overline{\text{M1TE}} = 1$ , there is no change in the operation of the  $\overline{\text{M1}}$  signal, and M1E controls its function. When  $\overline{\text{M1TE}} = 0$ , the  $\overline{\text{M1}}$  output is asserted during the next opcode fetch cycle regardless of the state programmed into the M1E bit. This condition is only momentary (one time) and it is not necessary to preprogram a 1 to disable the function (see Figure 10).

Figure 10. M1 Temporary Enable Timing

IOC (I/O Compatibility). This bit controls the timing of the  $\overline{\text{IORO}}$  and  $\overline{\text{RD}}$  signals. The bit is set to 1 by RESET.

When  $\overline{\mathsf{IOC}} = 1$ , the  $\overline{\mathsf{IORQ}}$  and  $\overline{\mathsf{RD}}$  signals function the same as the Z64180 (Figure 11).

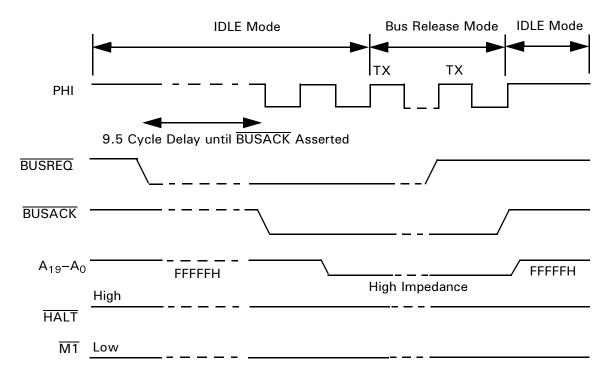

Figure 16. Bus Granting to External Master in IDLE Mode

#### STANDBY Mode (With or Without QUICK RECOVERY).

Software can put the Z8S180/Z8L180 into this mode by setting the IOSTOP bit (ICR5) to 1, CCR6 to 1, and executing the SLP instruction. This mode stops the on-chip oscillator and thus draws the least power of any mode, less than  $10\mu A$ .

As with IDLE mode, the Z8S180/Z8L180 leaves STANDBY mode in response to a Low on  $\overline{\text{RESET}}$ , on  $\overline{\text{NMI}}$ , or a Low on  $\overline{\text{INTO-2}}$  that is enabled by a 1 in the corresponding bit in the INT/TRAP Control Register. This action grants the bus to an external Master if the BREXT bit in the CPU Control Register (CCR5) is 1. The time required for all of these operations is greatly increased by the necessity for restarting the on-chip oscillator, and ensuring that it stabilizes to square-wave operation.

When an external clock is connected to the EXTAL pin rather than a crystal to the XTAL and EXTAL pins and the external clock runs continuously, there is little necessity to use STANDBY mode because no time is required to restart the oscillator, and other modes restart faster. However, if external logic stops the clock during STANDBY mode (for example, by decoding HALT Low and M1 High for several clock cycles), then STANDBY mode can be useful to allow the external clock source to stabilize after it is re-enabled.

When external logic drives RESET Low to bring the device out of STANDBY mode, and a crystal is in use or an external clock source is stopped, the external logic must hold RESET Low until the on-chip oscillator or external clock source is restarted and stabilized.

The clock-stability requirements of the Z8S180/Z8L180 are much less in the divide-by-two mode that is selected by a RESET sequence and controlled by the Clock Divide bit in the CPU Control Register (CCR7). As a result, software performs the following actions:

- 1. Sets CCR7 to 0 for divide-by-two mode before an SLP instruction and STANDBY mode.

- Delays setting CCR7 back to 1 for divide-by-one mode as long as possible to allow additional clock stabilization time after a RESET, interrupt, or in-line RESTART after an SLP 01 instruction.

If CCR6 is set to 1 before the SLP instruction places the MPU in STANDBY mode, the value of the CCR3 bit determines the length of the delay before the oscillator restarts and stabilizes when it leaves STANDBY mode due to an external interrupt request. When CCR3 is 0, the Z8S180/Z8L180 waits 2<sup>17</sup> (131,072) clock cycles. When CCR3 is 1, it waits 64 clock cycles. This state is called QUICK RECOVERY mode. The same delay applies to grant-

Table 7. Z8L180 DC Characteristics  $V_{DD} = 3.3V \pm 10\%; V_{SS} = 0V$

| Symbol           | Item                                                      | Condition                                     | Min                  | Тур | Max                     | Unit |

|------------------|-----------------------------------------------------------|-----------------------------------------------|----------------------|-----|-------------------------|------|

| V <sub>IH1</sub> | Input H Voltage<br>RESET, EXTAL, NMI                      |                                               | V <sub>DD</sub> -0.6 |     | V <sub>DD</sub><br>+0.3 | V    |

| V <sub>IH2</sub> | Input H Voltage<br>Except RESET, EXTAL, NMI               |                                               | 2.0                  |     | V <sub>DD</sub><br>+0.3 | V    |

| V <sub>IL1</sub> | Input L Voltage<br>RESET, EXTAL, NMI                      |                                               | -0.3                 |     | 0.6                     | V    |

| V <sub>IL2</sub> | Input L Voltage<br>Except RESET, EXTAL, NMI               |                                               | -0.3                 |     | 0.8                     | V    |

| V <sub>OH</sub>  | Outputs H Voltage                                         | $I_{OH} = -200  \mu A$                        | 2.15                 |     |                         | V    |

|                  | All outputs                                               | $I_{OH} = -20 \mu A$                          | V <sub>DD</sub> -0.6 |     |                         | V    |

| V <sub>OL</sub>  | Outputs L Voltage<br>All Outputs                          | $I_{OL} = 4 \text{ mA}$                       |                      |     | 0.4                     | V    |

| I <sub>IL</sub>  | Input Leakage<br>Current All Inputs<br>Except XTAL, EXTAL | $V_{IN} = 0.5 \sim V_{DD} - 0.5$              |                      |     | 1.0                     | μΑ   |

| I <sub>TL</sub>  | Three State Leakage<br>Current                            | $V_{ N} = 0.5 \sim V_{DD} - 0.5$              |                      |     | 1.0                     | μΑ   |

| I <sub>DD1</sub> | Power Dissipation                                         | F = 20  MHz                                   |                      | 30  | 60                      | mA   |

|                  | (Normal Operation)                                        | 4 MHz                                         |                      | 4   | 10                      |      |

|                  | Power Dissipation                                         | F = 20 MHz                                    |                      | 5   | 10                      |      |

|                  | (SYSTEM STOP mode)                                        | 4 MHz                                         |                      | 2   | 5                       |      |

| C <sub>P</sub>   | Pin Capacitance                                           | $V_{IN} = 0V$ , $f = 1 MHz$<br>$T_A = 25$ ° C |                      |     | 12                      | pF   |

| Note:            |                                                           |                                               |                      |     |                         |      |

<sup>1.</sup>  $V_{IHmin} = V_{DD}$  –1.0V,  $V_{ILmax} = 0.6V$  (All output terminals are at NO LOAD.)  $V_{DD} = 3.0V$ .

# Table 8. Z8S180 AC Characteristics (Continued) $V_{DD}=5V\pm10\%$ or $V_{DD}=3.3V\pm10\%$ ; 33-MHz Characteristics Apply Only to 5V Operation

|        |                  |                                       | Z8S180-20 MHz Z8S180-33 MHz |     |     | _   |      |

|--------|------------------|---------------------------------------|-----------------------------|-----|-----|-----|------|

| Number | Symbol           | Item                                  | Min                         | Max | Min | Max | Unit |

| 63     | t <sub>REH</sub> | RESET Hold Time from PHI Fall         | 25                          | _   | 15  | _   | ns   |

| 64     | t <sub>OSC</sub> | Oscillator Stabilization Time         | _                           | 20  | _   | 20  | ns   |

| 65     | t <sub>EXR</sub> | External Clock Rise Time (EXTAL)      | _                           | 5   | _   | 5   | ns   |

| 66     | t <sub>EXF</sub> | External Clock Fall Time (EXTAL)      | _                           | 5   | _   | 5   | ns   |

| 67     | t <sub>RR</sub>  | RESET Rise Time                       | _                           | 50  | _   | 50  | ms   |

| 68     | t <sub>RF</sub>  | RESET Fall Time                       | _                           | 50  | _   | 50  | ms   |

| 69     | t <sub>IR</sub>  | Input Rise Time (except EXTAL, RESET) | _                           | 50  | _   | 50  | ns   |

| 70     | t <sub>IF</sub>  | Input Fall Time (except EXTAL, RESET) | _                           | 50  | _   | 50  | ns   |

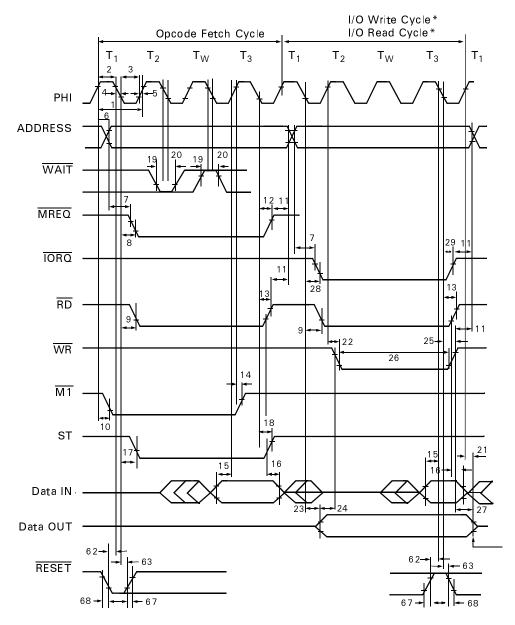

# **TIMING DIAGRAMS**

Note: \*Memory Read/Write Cycle timing is the same as I/O Read/Write Cycle except there are no automatic wait states  $(T_W)$ , and  $\overline{MREQ}$  is active instead of  $\overline{IORQ}$ .

Figure 20. CPU Timing

(Opcode Fetch Cycle, Memory Read Cycle,

Memory Write Cycle, I/O Write Cycle, I/O Read Cycle)

#### **ASCI REGISTER DESCRIPTION**

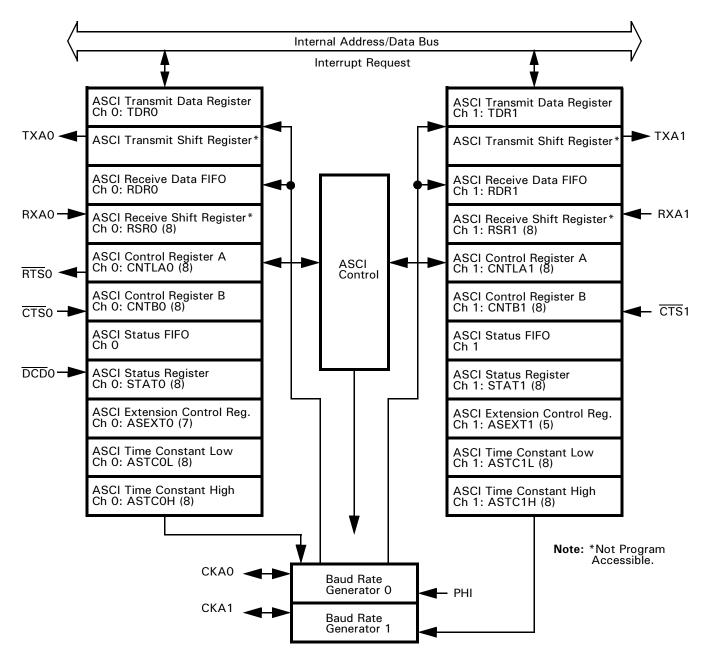

Figure 32. ASCI Block Diagram

ASCI Transmit Shift Register 0,1. When the ASCI Transmit Shift Register (TSR) receives data from the ASCI Transmit Data Register (TDR), the data is shifted out to the TXA pin. When transmission is completed, the next byte (if available) is automatically loaded from TDR into TSR and the next transmission starts. If no data is available for trans-

mission, TSR idles by outputting a continuous High level. This register is not program-accessible

ASCI Transmit Data Register 0,1 (TDR0, 1: I/O address = 06H, 07H). Data written to the ASCI Transmit Data Register is transferred to the TSR as soon as TSR is empty. Data can be written while TSR is shifting out the previous byte of data. Thus, the ASCI transmitter is double buffered.

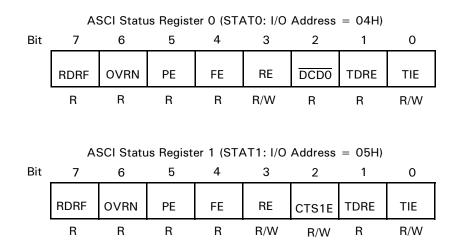

#### **ASCI STATUS REGISTER 0,1**

Each ASCI channel status register (STATO,1) allows interrogation of ASCI communication, error and modem control

signal status, and the enabling or disabling of ASCI interrupts.

Figure 35. ASCI Status Registers

RDRF: Receive Data Register Full (Bit 7). RDRF is set to 1 when an incoming data byte is loaded into an empty Rx FIFO. If a framing or parity error occurs, RDRF is still set and the receive data (which generated the error) is still loaded into the FIFO. RDRF is cleared to 0 by reading RDR and most recently received character in the FIFO from IOSTOP mode, during RESET and for ASCIO if the DCDO input is auto-enabled and is negated (High).

**OVRN:** Overrun Error (Bit 6). An overrun condition occurs if the receiver finishes assembling a character but the Rx FIFO is full so there is no room for the character. However, this status bit is not set until the most recent character received before the overrun becomes the oldest byte in the FIFO. This bit is cleared when software writes a 1 to the EFR bit in the CNTLA register. The bit may also be cleared by RESET in IOSTOP mode or ASCIO if the DCDO pin is auto enabled and is negated (High).

**Note:** When an overrun occurs, the receiver does not place the character in the shift register into the FIFO, nor any subsequent characters, until the most recent good character enters the top of the FIFO so that OVRN is set. Software then writes a 1 to EFR to clear it.

**PE:** Parity Error (Bit 5). A parity error is detected when parity checking is enabled. When the MOD1 bit in the

CNTLA register is 1, a character is assembled in which the parity does not match the PEO bit in the CNTLB register. However, this status bit is not set until or unless the error character becomes the oldest one in the Rx FIFO. PE is cleared when software writes a 1 to the EFR bit in the CNTRLA register. PE is also cleared by RESET in IOSTOP mode, or on ASCIO, if the DCDO pin is auto-enabled and is negated (High).

FE: Framing Error (Bit 4). A framing error is detected when the stop bit of a character is sampled as O/SPACE. However, this status bit is not set until/unless the error character becomes the oldest one in the Rx FIFO. FE is cleared when software writes a 1 to the EFR bit in the CNTLA register. FE is also cleared by RESET in IOSTOP mode, or on ASCIO, if the DCDO pin is auto-enabled and is negated (High).

REI: Receive Interrupt Enable (Bit 3). RIE should be set to 1 to enable ASCI receive interrupt requests. When RIE is 1, the Receiver requests an interrupt when a character is received and RDRF is set, but only if neither DMA channel requires its request-routing field to be set to receive data from this ASCI. That is, if SM1-0 are 11 and SAR17-16 are 10, or DIM1 is 1 and IAR17-16 are 10, then ASCII does not request an interrupt for RDRF. If RIE is 1, either ASCI requests an interrupt when OVRN, PE or FE is set, and

ASCIO requests an interrupt when  $\overline{DCDO}$  goes High. RIE is cleared to 0 by RESET.

**DCDO:** Data Carrier Detect (Bit 2 STATO). This bit is set to 1 when the pin is High. It is cleared to 0 on the first READ of STATO following the pin's transition from High to Low and during RESET. When bit 6 of the ASEXTO register is 0 to select auto-enabling, and the pin is negated (High), the receiver is reset and its operation is inhibited.

CTS1E: Clear To Send (Bit 2 STAT1). Channel 1 features an external CTS1 input, which is multiplexed with the receive data pin RSX for the CSI/O. Setting this bit to 1 selects the CTS1 function; clearing the bit to 0 selects the RXS function.

**TDRE:** Transmit Data Register Empty (Bit 1). TDRE = 1 indicates that the TDR is empty and the next transmit data byte is written to TDR. After the byte is written to TDR, TDRE is cleared to 0 until the ASCI transfers the byte from TDR to the TSR and then TDRE is again set to 1. TDRE is set to 1 in IOSTOP mode and during RESET. On ASCIO, if the  $\overline{\text{CTSO}}$  pin is auto-enabled in the ASEXTO register and the pin is High, TDRE is reset to 0.

**TIE: Transmit Interrupt Enable (Bit 0).** TIE should be set to 1 to enable ASCI transmit interrupt requests. If TIE = 1, an interrupt is requested when TDRE = 1. TIE is cleared to 0 during RESET.

#### **ASCI TRANSMIT DATA REGISTERS**

Register addresses 06H and 07H hold the ASCI transmit data for channel 0 and channel 1, respectively.

# **ASCI Transmit Data Registers Channel 0**

#### Mnemonic TDR0 Address 06H

Figure 36. ASCI Register

# **ASCI Transmit Data Registers Channel 1**

#### Mnemonic TDR1 Address 07H

Figure 37. ASCI Register

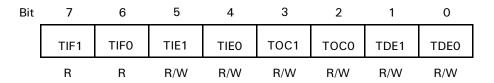

#### TIMER CONTROL REGISTER

The Timer Control Register (TCR) monitors both channels (PRTO, PRT1) TMDR status. It also controls the enabling

and disabling of down-counting and interrupts, and controls the output pin  $A18/T_{OUT}$  for PRT1.

Figure 46. Timer Control Register (TCR: I/O Address = 10H)

TIF1: Timer Interrupt Flag 1 (Bit 7). When TMDR1 decrements to 0, TIF1 is set to 1. This condition generates an interrupt request if enabled by TIE1 = 1. TIF1 is reset to 0 when TCR is read and the higher or lower byte of TMDR1 is read. During RESET, TIF1 is cleared to 0.

**TIFO:** Timer Interrupt Flag 0 (Bit 6). When TMDRO decrements to 0, TIFO is set to 1. This condition generates an interrupt request if enabled by TIEO = 1. TIFO is reset to 0 when TCR is read and the higher or lower byte of TMDRO is read. During RESET, TIFO is cleared to 0.

**TIE1: Timer Interrupt Enable 1 (Bit 5).** When TIE0 is set to 1, TIF1 = 1 generates a CPU interrupt request. When TIE0 is reset to 0, the interrupt request is inhibited. During RESET, TIE0 is cleared to 0.

**TOC1**, **0**: **Timer Output Control (Bits 3, 2)**. TOC1 and TOC0 control the output of PRT1 using the multiplexed A18/T<sub>OUT</sub> pin as indicated in Table 12. During RESET, TOC1 and TOC0 are cleared to 0. If bit 3 of the IAR1B register is 1, the T<sub>OUT</sub> function is selected. By programming

TOC1 and TOC0, the A18/T<sub>OUT</sub> pin can be forced High, Low, or toggled when TMDR1 decrements to 0.

Table 12. Timer Output Control

| TOC1 | TOC0 |           | Output                                 |

|------|------|-----------|----------------------------------------|

| 0    | 0    | Inhibited | The A18/T <sub>OUT</sub> pin is not    |

|      |      |           | affected by the PRT                    |

| 0    | 1    | Toggled   | If bit 3 of IAR1B is 1, the            |

| 1    | 0    | 0         | A18/T <sub>OUT</sub> pin is toggled or |

| 1    | 1    | 1         | set Low or High as<br>indicated        |

**TDE1**, **0**: **Timer Down Count Enable (Bits 1, 0)**. TDE1 and TDE0 enable and disable down-counting for TMDR1 and TMDR0, respectively. When TDEn (n = 0,1) is set to 1, down-counting is stopped and TMDRn is freely read or written. TDE1 and TDE0 are cleared to 0 during RESET and TMDRn does not decrement until TDEn is set to 1.

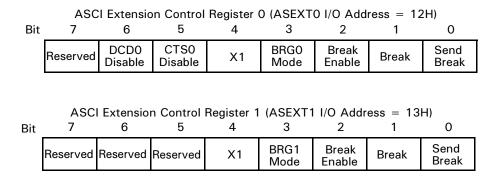

#### ASCI EXTENSION CONTROL REGISTER CHANNEL 0 AND CHANNEL 1

The ASCI Extension Control Registers (ASEXTO and ASEXT1) control functions that have been added to the

ASCIs in the Z8S180/Z8L180 family. All bits in this register reset to 0.

Figure 47. ASCI Extension Control Registers, Channels 0 and 1

**DCD0 Disable (Bit 6, ASCIO Only).** If this bit is 0, then the  $\overline{DCD0}$  pin auto-enables the ASCI0 receiver, such that when the pin is negated/High, the Receiver is held in a RE-SET state. If this bit is 1, the state of the  $\overline{DCD}$ -pin has no effect on receiver operation. In either state of this bit, software can read the state of the  $\overline{DCD0}$  pin in the STAT0 register, and the receiver interrupts on a rising edge of  $\overline{DCD0}$ .

CTSO Disable (Bit 5, ASCIO Only). If this bit is 0, then the  $\overline{\text{CTSO}}$  pin auto-enables the ASCIO transmitter, in that when the pin is negated/High, the TDRE bit in the STATO register is forced to 0. If this bit is 1, the state of the  $\overline{\text{CTSO}}$  pin has no effect on the transmitter. Regardless of the state of this bit, software can read the state of the  $\overline{\text{CTSO}}$  pin the CNTLBO register.

**X1** (**Bit 4**). If this bit is 1, the clock from the Baud Rate Generator or CKA pin is taken as a 1X-bit clock (sometimes called *isochronous mode*). In this mode, receive data on the RXA pin must be synchronized to the clock on the CKA pin, regardless of whether CKA is an input or an output. If this bit is 0, the clock from the Baud Rate Generator or CKA pin is divided by 16 or 64 per the DR bit in the CNTLB register, to obtain the actual bit rate. In this mode, receive data on the RXA pin is not required to be synchronized to a clock.

**BRG Mode (Bit 3).** If the SS2-0 bits in the CNTLB register are not 111, and this bit is 0, the ASCI Baud Rate Generator

divides PHI by 10 or 30, depending on the PS bit in CNTLB, and factored by a power of two (selected by the SS2–0 bits), to obtain the clock that is presented to the transmitter and receiver and output on the CKA pin. If SS2–0 are not 111, and this bit is 1, the Baud Rate Generator divides PHI by twice the sum of the 16-bit value (programmed into the Time Constant registers) and 2. This mode is identical to the operation of the baud rate generator in the ESCC.

**Break Enable (Bit 2).** If this bit is 1, the receiver detects BREAK conditions and report them in bit 1, and the transmitter sends BREAKs under the control of bit 0.

Break Detect (Bit 1). The receiver sets this read-only bit to 1 when an all-zero character with a Framing Error becomes the oldest character in the Rx FIFO. The bit is cleared when software writes a 0 to the EFR bit in CNTLA register, also by RESET, by IOSTOP mode, and for ASCIO, if the DCDO pin is auto-enabled and is negated (High).

**Send Break (Bit 0).** If this bit and bit 2 are both 1, the transmitter holds the TXA pin Low to send a BREAK condition. The duration of the BREAK is under software control (one of the PRTs or CTCs can be used to time it). This bit resets to 0, in which state TXA carries the serial output of the transmitter.

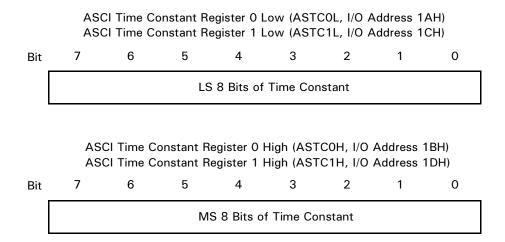

### **ASCI TIME CONSTANT REGISTERS**

If the SS2-0 bits of the CNTLB register are not 111, and the BRG mode bit in the ASEXT register is 1, the ASCI divides the PHI clock by two times the registers' 16-bit value, plus two. As a result, the clock is presented to the transmitter and receiver for division by 1, 16, or 64, and is output on the CKA pin.

If the SS2-0 bits in an ASCI CNTLB register are not 111, and the BRG mode bit in its Extension Control Register is 1, its *new* baud rate generator divides PHI for serial clocking, as follows:

bits/second =

$$f_{PHI}/(2*(TC+2) \times sampling rate)$$

where TC is the 16-bit value programmed into the ASCI Time Constant High and Low registers. If the ASCI multiplexed CKA pin is selected for the CKA function, it outputs the clock before the final division by the sampling rate, as follows:

$$f_{CKAout} = f_{PHI}/(2*(TC+2))$$

Find the TC value for a particular serial bit rate as follows:

$TC = (f_{PHI}/(2 \text{ x bits/second x sampling rate})) - 2$

Figure 53. ASCI Time Constant Registers

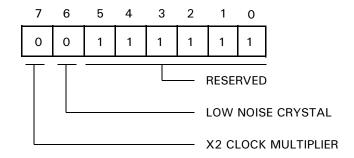

#### **CLOCK MULTIPLIER REGISTER**

(Z180 MPU Address 1EH)

Figure 54. Clock Multiplier Register

Bit 7. X2 Clock Multiplier Mode. When this bit is set to 1, the programmer can double the internal clock speed from the speed of the external clock. This feature only operates effectively with frequencies of 10–16 MHz (20–32 MHz internal). When this bit is set to 0, the Z8S180/Z8L180 device operates in normal mode. At power-up, this feature is disabled.

**Bit 6. Low Noise Crystal Option.** Setting this bit to 1 enables the low-noise option for the EXTAL and XTAL pins. This option reduces the gain in addition to reducing the output drive capability to 30% of its original drive capability. The Low Noise Crystal Option is recommended in the use of crystals for PCMCIA applications, where the crystal may be driven too hard by the oscillator. Setting this bit to 0 is selected for normal operation of the EXTAL and XTAL pins. The default for this bit is 0.

**Note:** Operating restrictions for device operation are listed below. If a low-noise option is required, and normal device operation is required, use the clock multiplier feature.

Table 13. Low Noise Option

| Low Noise<br>ADDR 1E, bit 6 = 1 | Normal<br>ADDR 1E, bit 6 = 0 |

|---------------------------------|------------------------------|

| 20 MHz @ 4.5V, 100°C            | 33 MHz @ 4.5V, 100°C         |

| 10 MHz @ 3.0V, 100°C            | 20 MHz @ 3.0V, 100°C         |

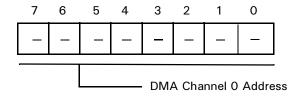

#### DMA SOURCE ADDRESS REGISTER CHANNEL 0

The DMA Source Address Register Channel 0 specifies the physical source address for channel 0 transfers. The register contains 20 bits and can specify up to 1024 KB memory addresses or up to 64-KB I/O addresses. Channel 0 source can be memory, I/O, or memory mapped I/O. For I/O, bits 17–16 of this register identify the Request Handshake signal.

### **DMA Source Address Register, Channel 0 Low**

#### Mnemonic SAR0L Address 20H

Figure 55. DMA Source Address Register 0 Low

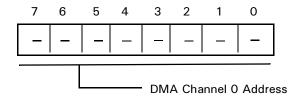

# DMA Source Address Register, Channel 0 High

Mnemonic SAR0H Address 21H

Figure 56. DMA Source Address Register 0 High

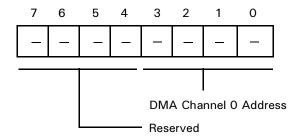

# **DMA Source Address Register Channel 0B**

#### Mnemonic SAR0B Address 22H

Figure 57. DMA Source Address Register 0B

If the source is in I/O space, bits 1–0 of this register select the DMA request signal for DMA0, as follows:

| Bit 1<br>(A17) | Bit 0<br>(A16) | DMA Transfer Request |

|----------------|----------------|----------------------|

| 0              | 0              | DREQ0 (external)     |

| 0              | 1              | RDRF (ASCIO)         |

| 1              | 0              | RDRF (ASCI1)         |

| 1              | 1              | Reserved             |

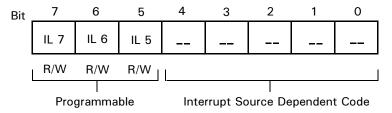

#### INTERRUPT VECTOR LOW REGISTER

Bits 7–5 of the Interrupt Vector Low Register ( $I_L$ ) are used as bits 7–5 of the synthesized interrupt vector during interrupts for the  $\overline{INT1}$  and  $\overline{INT2}$  pins and for the DMAs, ASCIs,

PRTs, and CSI/O. These three bits are cleared to 0 during RESET (Figure 74).

#### **Interrupt Vector Low Register**

Mnemonic: IL Address 33H

Figure 74. Interrupt Vector Low Register (IL: I/O Address = 33H)

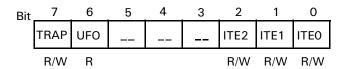

#### INT/TRAP CONTROL REGISTER

This register is used in handling TRAP interrupts and to enable or disable Maskable Interrupt Level 0 and the  $\overline{\text{INT1}}$  and  $\overline{\text{INT2}}$  pins.

# **INT/TRAP Control Register**

Mnemonics ITC Address 34H

**TRAP (Bit 7).** This bit is set to 1 when an undefined opcode is fetched. TRAP can be reset under program control by writing it with a 0; however, TRAP cannot be written with 1 under program control. TRAP is reset to 0 during RESET.

**UFO: Undefined Fetch Object (Bit 6).** When a TRAP interrupt occurs, the contents of UFO allow the starting address of the undefined instruction to be determined. This interrupt is necessary because the TRAP may occur on either the second or third byte of the opcode. UFO allows the stacked PC value to be correctly adjusted. If UFO = 0, the first opcode should be interpreted as the stacked PC-1. If UFO = 1, the first opcode address is stacked PC-2. UFO is Read-Only.

ITE2, 1, 0: Interrupt Enable 2, 1, 0 (Bits 2–0). ITE2 and ITE1 enable and disable the external interrupt inputs

INT2 and INT1, respectively. ITEO enables and disables interrupts from:

- ESCC

- Bidirectional Centronics controller

- CTCs

- External interrupt input INTO

A 1 in a bit enables the corresponding interrupt level while a 0 disables it. A RESET sets ITEO to 1 and clears ITE1 and ITE2 to 0.

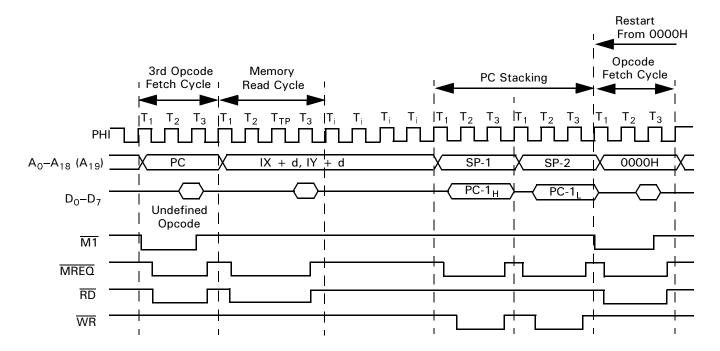

**TRAP** Interrupt. The Z8S180/Z8L180 generates a TRAP sequence when an undefined opcode fetch occurs. This feature can be used to increase software reliability, implement an *extended* instruction set, or both. TRAP may occur during opcode fetch cycles and also if an undefined opcode is fetched during the interrupt acknowledge cycle for INTO when Mode O is used.

When a TRAP sequence occurs, the Z8S180/Z8L180:

- 1. Sets the TRAP bit in the Interrupt TRAP/Control (ITC) register to 1.

- 2. Saves the current Program Counter (PC) value, reflecting the location of the undefined opcode, on the stack.

- 3. Resumes execution at logical address 0.

**Note:** If logical address 0000H is mapped to physical address 00000H, the vector is the same as for RESET. In this case, testing the TRAP bit in ITC reveals whether the restart at physical address 00000H was caused by RESET or TRAP.

Figure 76. TRAP Timing—3<sup>rd</sup> Opcode Undefined

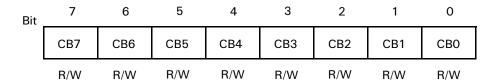

#### MMU COMMON BASE REGISTER

The Common Base Register (CBR) specifies the base address (on 4-KB boundaries) used to generate a 20-bit phys-

ical address for Common Area 1 accesses. All bits of CBR are reset to 0 during RESET.

#### **MMU Common Base Register**

Mnemonic CBR Address 38H

Figure 78. MMU Common Base Register (CBR: I/O Address = 38H)

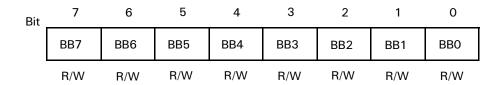

#### MMU BANK BASE REGISTER

The Bank Base Register (BBR) specifies the base address (on 4-KB boundaries) used to generate a 20-bit physical ad-

dress for Bank Area accesses. All bits of BBR are reset to 0 during RESET.

### **MMU Bank Base Register**

Mnemonic BBR Address 39H

Figure 79. MMU Bank Base Register (BBR: I/O Address = 39H)

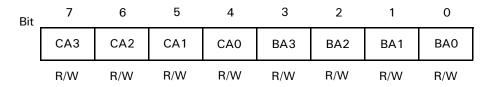

#### MMU COMMON/BANK AREA REGISTER

The Common/Bank Area Register (CBAR) specifies boundaries within the Z8S180/Z8L180 64-KB logical address

space for up to three areas; Common Area), Bank Area and Common Area 1.

### MMU Common/Bank Area Register

Mnemonic CBAR Address 3AH

Figure 80. MMU Common/Bank Area Register (CBAR: I/O Address = 3AH)

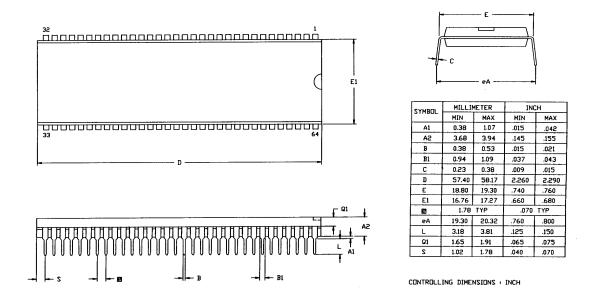

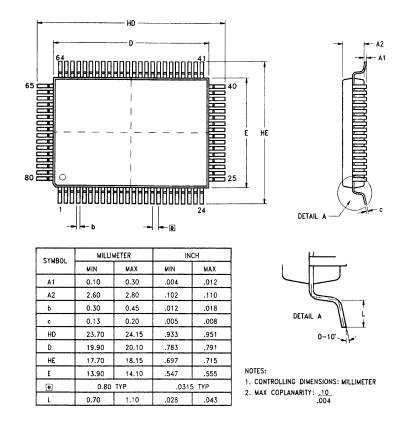

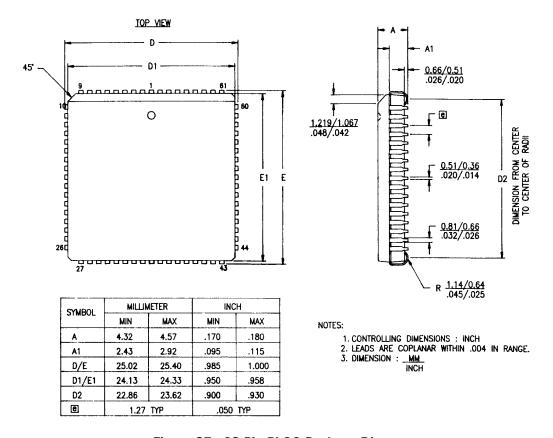

# **PACKAGE INFORMATION**

Figure 85. 64-Pin DIP Package Diagram

Figure 86. 80-Pin QFP Package Diagram

Figure 87. 68-Pin PLCC Package Diagram