Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 16 x 8                                                    |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f011ahj020ec |

# Z8 Encore! XP® F082A Series **Product Specification**

| Hardware Overflow                                            | 123     |

|--------------------------------------------------------------|---------|

| Automatic Powerdown                                          |         |

| Single-Shot Conversion                                       |         |

| Continuous Conversion                                        |         |

| Interrupts                                                   |         |

| Calibration and Compensation                                 |         |

| ADC Compensation Details                                     |         |

| Input Buffer Stage                                           |         |

| ADC Control Register Definitions                             |         |

| ADC Control Register 0                                       |         |

| ADC Control/Status Register 1                                |         |

| ADC Data High Byte Register                                  |         |

| ADC Data Low Byte Register                                   |         |

| Low Power Operational Amplifier                              | 134     |

| Overview                                                     | 134     |

| Operation                                                    | 134     |

| Comparator                                                   |         |

| •                                                            |         |

| Operation                                                    |         |

| Comparator Control Register Definitions                      | 136     |

| Temperature Sensor                                           | 139     |

| Temperature Sensor Operation                                 | 139     |

| Flash Memory                                                 | 141     |

| Architecture                                                 | 141     |

| Flash Information Area                                       |         |

| Operation                                                    |         |

|                                                              |         |

| Flash Operation Timing Using the Flash Frequency Registers   |         |

| Flash Code Protection Against Accidental Program and Erasure |         |

| · · · · · · · · · · · · · · · · · · ·                        | 147     |

|                                                              | <br>147 |

|                                                              | <br>147 |

|                                                              | 148     |

| <b>71</b>                                                    | 148     |

|                                                              | 149     |

| <u> </u>                                                     | 149     |

| •                                                            | 150     |

|                                                              | 150     |

PS022825-0908 **Table of Contents**

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

| Flash Sector Protect Register                                                                                                                                                                                                                                                                                                                                                                                    |                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Flash Option Bits                                                                                                                                                                                                                                                                                                                                                                                                | 53                                                 |

| Operation1Option Bit Configuration By Reset1Option Bit Types1Reading the Flash Information Page1Flash Option Bit Control Register Definitions1Trim Bit Address Register1Trim Bit Data Register1Flash Option Bit Address Space1Flash Program Memory Address 0000H1Flash Program Memory Address 0001H1Trim Bit Address Space1Trim Bit Address Space1Trim Bit Address 0000H1                                        | 53<br>54<br>55<br>55<br>56<br>56<br>56<br>58<br>58 |

| Trim Bit Address 0001H       1         Trim Bit Address 0002H       1         Trim Bit Address 0003H       1         Trim Bit Address 0004H       1         Zilog Calibration Data       1         ADC Calibration Data       1         Temperature Sensor Calibration Data       1         Watchdog Timer Calibration Data       1         Serialization Data       1         Randomized Lot Identifier       1 | 59<br>61<br>61<br>64<br>64<br>65                   |

| Non-Volatile Data Storage                                                                                                                                                                                                                                                                                                                                                                                        | 69                                                 |

| Operation       1         NVDS Code Interface       1         Byte Write       1         Byte Read       1         Power Failure Protection       1         Optimizing NVDS Memory Usage for Execution Speed       1                                                                                                                                                                                             | 69<br>69<br>70<br>71                               |

| On-Chip Debugger1                                                                                                                                                                                                                                                                                                                                                                                                | 73                                                 |

| Operation                                                                                                                                                                                                                                                                                                                                                                                                        | 73<br>74<br>74<br>75                               |

PS022825-0908 Table of Contents

# **Block Diagram**

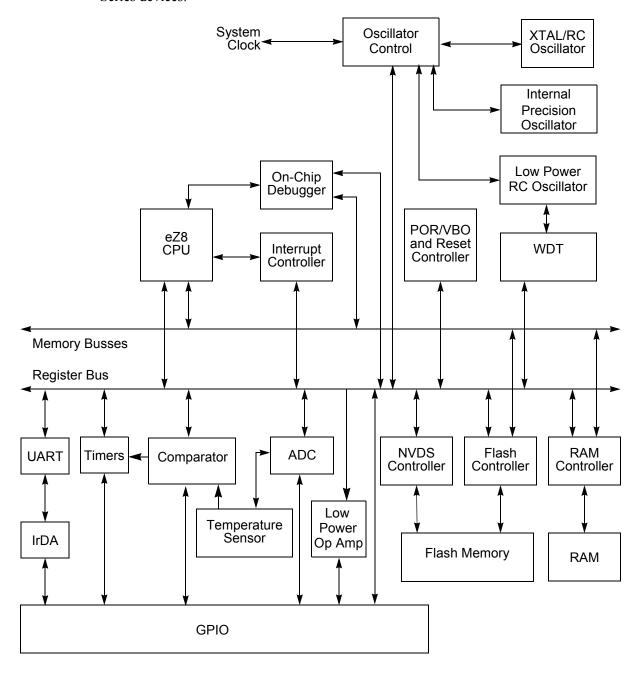

Figure 1 displays the block diagram of the architecture of the Z8 Encore! XP® F082A Series devices.

Figure 1. Z8 Encore! XP F082A Series Block Diagram

PS022825-0908 Overview

# Reset, Stop Mode Recovery, and Low Voltage Detection

The Reset Controller within the Z8 Encore! XP<sup>®</sup> F082A Series controls Reset and Stop Mode Recovery operation and provides indication of low supply voltage conditions. In typical operation, the following events cause a Reset:

- Power-On Reset (POR)

- Voltage Brownout (VBO)

- Watchdog Timer time-out (when configured by the WDT\_RES Flash Option Bit to initiate a reset)

- External RESET pin assertion (when the alternate RESET function is enabled by the GPIO register)

- On-chip debugger initiated Reset (OCDCTL[0] set to 1)

When the device is in STOP mode, a Stop Mode Recovery is initiated by either of the following:

- Watchdog Timer time-out

- GPIO Port input pin transition on an enabled Stop Mode Recovery source

The low voltage detection circuitry on the device (available on the 8-pin product versions only) performs the following functions:

- Generates the VBO reset when the supply voltage drops below a minimum safe level.

- Generates an interrupt when the supply voltage drops below a user-defined level (8-pin devices only).

# **Reset Types**

The Z8 Encore! XP F082A Series provides several different types of Reset operation. Stop Mode Recovery is considered as a form of Reset. Table 8 lists the types of Reset and their operating characteristics. The System Reset is longer if the external crystal oscillator is enabled by the Flash option bits, allowing additional time for oscillator start-up.

and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the  $\overline{RESET}$  input pin is asserted Low, the Z8 Encore!  $XP^{\circledR}$  F082A Series devices remain in the Reset state. If the  $\overline{RESET}$  pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following  $\overline{RESET}$  pin deassertion. Following a System Reset initiated by the external  $\overline{RESET}$  pin, the EXT status bit in the Reset Status (RSTSTAT) register is set to 1.

#### **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see Port A–D Control Registers on page 46), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows a Z8 Encore! XP F082A Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the RESET pin Low. The RESET pin is held Low by the internal circuitry until the appropriate delay listed in Table 8 has elapsed.

#### **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control register. The On-Chip Debugger block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset the POR bit in the Reset Status (RSTSTAT) register is set.

# **Stop Mode Recovery**

STOP mode is entered by execution of a STOP instruction by the eZ8 CPU. See Low-Power Modes on page 33 for detailed STOP mode information. During Stop Mode Recovery (SMR), the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay (see Table 131 on page 229)  $T_{SMR}$ , also includes the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control register (WDTCTL) and the Oscillator Control register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset

LEDEN[7:0]—LED Drive Enable

These bits determine which Port C pins are connected to an internal current sink.

0 = Tristate the Port C pin.

1= Enable controlled current sink on the Port C pin.

#### **LED Drive Level High Register**

The LED Drive Level registers contain two control bits for each Port C pin (Table 30). These two bits select between four programmable drive levels. Each pin is individually programmable.

Table 30. LED Drive Level High Register (LEDLVLH)

| BITS  | 7   | 6   | 5   | 4     | 3       | 2   | 1   | 0   |

|-------|-----|-----|-----|-------|---------|-----|-----|-----|

| FIELD |     |     |     | LEDLV | LH[7:0] |     |     |     |

| RESET | 0   | 0   | 0   | 0     | 0       | 0   | 0   | 0   |

| R/W   | R/W | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |

| ADDR  |     |     |     | F8    | 3H      |     |     |     |

LEDLVLH[7:0]—LED Level High Bit

{LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin.

00 = 3 mA

01 = 7 mA

10= 13 mA

11 = 20 mA

# **LED Drive Level Low Register**

The LED Drive Level registers contain two control bits for each Port C pin (Table 31). These two bits select between four programmable drive levels. Each pin is individually programmable.

Caution: The following coding style that clears bits in the Interrupt Request registers is not recommended. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost.

#### Poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 AND ro, MASK LDX IRQ0, r0

Caution:

To avoid missing interrupts, use the following coding style to clear bits in the *Interrupt Request 0 register:*

#### Good coding style that avoids lost interrupt requests:

ANDX IRQ0, MASK

#### Software Interrupt Assertion

Program code can generate interrupts directly. Writing a 1 to the correct bit in the Interrupt Request register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request register is automatically cleared to 0.

**Caution:** *The following coding style used to generate software interrupts by setting bits in the* Interrupt Request registers is not recommended. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost.

#### Poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 OR r0, MASK LDX IRQ0, r0

**Caution:** To avoid missing interrupts, use the following coding style to set bits in the Interrupt Request registers:

#### Good coding style that avoids lost interrupt requests:

ORX IRQ0, MASK

# Watchdog Timer Interrupt Assertion

The Watchdog Timer interrupt behavior is different from interrupts generated by other sources. The Watchdog Timer continues to assert an interrupt as long as the timeout condition continues. As it operates on a different (and usually slower) clock domain than the rest of the device, the Watchdog Timer continues to assert this interrupt for many system clocks until the counter rolls over.

PS022825-0908 Interrupt Controller U0RXI—UART 0 Receiver Interrupt Request

0 = No interrupt request is pending for the UART 0 receiver.

1 = An interrupt request from the UART 0 receiver is awaiting service.

U0TXI—UART 0 Transmitter Interrupt Request

0 = No interrupt request is pending for the UART 0 transmitter.

1 = An interrupt request from the UART 0 transmitter is awaiting service.

ADCI—ADC Interrupt Request

0 = No interrupt request is pending for the analog-to-digital Converter.

1 = An interrupt request from the Analog-to-Digital Converter is awaiting service.

#### **Interrupt Request 1 Register**

The Interrupt Request 1 (IRQ1) register (Table 34) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ1 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 1 register to determine if any interrupt requests are pending.

Table 34. Interrupt Request 1 Register (IRQ1)

| BITS  | 7     | 6     | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|-------|-------|------|------|------|------|------|------|

| FIELD | PA7VI | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |

| RESET | 0     | 0     | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| ADDR  |       |       |      | FC   | 3H   |      |      |      |

PA7VI—Port A Pin 7 or LVD Interrupt Request

0 = No interrupt request is pending for GPIO Port A or LVD.

1 = An interrupt request from GPIO Port A or LVD.

PA6CI—Port A Pin 6 or Comparator Interrupt Request

0 = No interrupt request is pending for GPIO Port A or Comparator.

1 = An interrupt request from GPIO Port A or Comparator.

PAxI—Port A Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port A pin x.

1 = An interrupt request from GPIO Port A pin x is awaiting service.

where x indicates the specific GPIO Port pin number (0-5).

PS022825-0908 Interrupt Controller

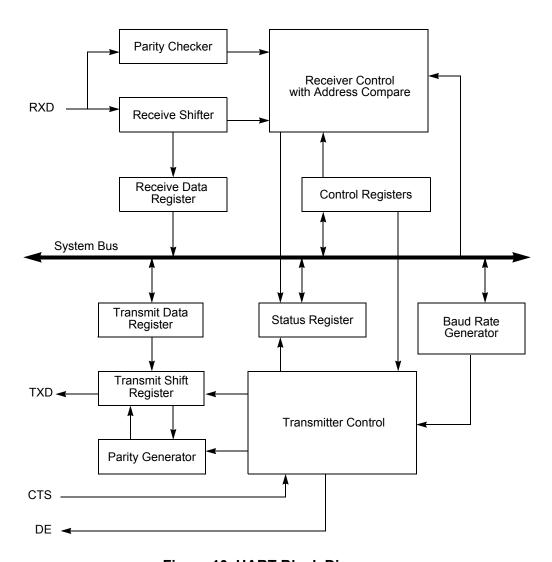

Figure 10. UART Block Diagram

# Operation

#### **Data Format**

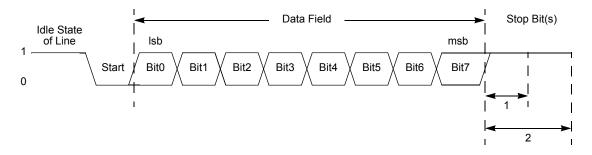

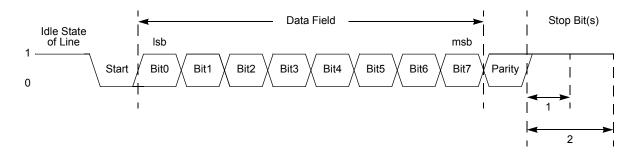

The UART always transmits and receives data in an 8-bit data format, least-significant bit first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low START bit and ends with either 1 or 2 active High STOP bits. Figure 11 and Figure 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

Figure 11. UART Asynchronous Data Format without Parity

Figure 12. UART Asynchronous Data Format with Parity

#### Transmitting Data using the Polled Method

Follow the steps below to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Write to the UART Control 1 register, if MULTIPROCESSOR mode is appropriate, to enable MULTIPROCESSOR (9-bit) mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR mode.

- 5. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR mode is not enabled, and select either even or odd parity (PSEL).

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin.

zilog

baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal, allowing the Endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

# Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined in Universal Asynchronous Receiver/Transmitter on page 97.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the *UART Control 1 register to 1 to enable the Infrared Encoder/Decoder before enabling* the GPIO Port alternate function for the corresponding pin.

PS022825-0908 Infrared Encoder/Decoder

zilog',

138

PS022825-0908 Comparator

#### **Trim Bit Data Register**

The Trim Bid Data (TRMDR) register contains the read or write data for access to the trim option bits (Table 85).

**Table 85. Trim Bit Data Register (TRMDR)**

| BITS  | 7   | 6   | 5   | 4         | 3            | 2   | 1   | 0   |

|-------|-----|-----|-----|-----------|--------------|-----|-----|-----|

| FIELD |     |     |     | TRMDR - T | rim Bit Data |     |     |     |

| RESET | 0   | 0   | 0   | 0         | 0            | 0   | 0   | 0   |

| R/W   | R/W | R/W | R/W | R/W       | R/W          | R/W | R/W | R/W |

| ADDR  |     |     |     | FF        | 7H           |     |     |     |

# Flash Option Bit Address Space

The first two bytes of Flash program memory at addresses 0000H and 0001H are reserved for the user-programmable Flash option bits.

# Flash Program Memory Address 0000H

Table 86. Flash Option Bits at Program Memory Address 0000H

| BITS      | 7            | 6            | 5            | 4          | 3          | 2   | 1        | 0   |

|-----------|--------------|--------------|--------------|------------|------------|-----|----------|-----|

| FIELD     | WDT_RES      | WDT_AO       | OSC_S        | EL[1:0]    | VBO_AO     | FRP | Reserved | FWP |

| RESET     | U            | U            | U            | U          | U          | U   | U        | U   |

| R/W       | R/W          | R/W          | R/W          | R/W        | R/W        | R/W | R/W      | R/W |

| ADDR      |              |              |              | Program Me | mory 0000H |     |          |     |

| Note: U = | Unchanged by | y Reset. R/W | = Read/Write | ).         |            |     |          |     |

WDT\_RES—Watchdog Timer Reset

0 = Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.

1 = Watchdog Timer time-out causes a system reset. This setting is the default for unprogrammed (erased) Flash.

WDT AO—Watchdog Timer Always On

0 = Watchdog Timer is automatically enabled upon application of system power. Watchdog Timer can not be disabled.

PS022825-0908 Flash Option Bits

164

#### **Temperature Sensor Calibration Data**

Table 95. Temperature Sensor Calibration High Byte at 003A (TSCALH)

| BITS      | 7            | 6            | 5            | 4           | 3          | 2   | 1   | 0   |

|-----------|--------------|--------------|--------------|-------------|------------|-----|-----|-----|

| FIELD     |              |              |              | TSC         | ALH        |     |     |     |

| RESET     | U            | U            | U            | U           | U          | U   | U   | U   |

| R/W       | R/W          | R/W          | R/W          | R/W         | R/W        | R/W | R/W | R/W |

| ADDR      |              |              | Info         | rmation Pag | e Memory 0 | 03A |     |     |

| Note: U = | Unchanged by | y Reset. R/W | = Read/Write | <b>)</b> .  |            |     |     |     |

TSCALH – Temperature Sensor Calibration High Byte

The TSCALH and TSCALL bytes combine to form the 12-bit temperature sensor offset calibration value. For more details, see Temperature Sensor Operation on page 139.

Table 96. Temperature Sensor Calibration Low Byte at 003B (TSCALL)

| BITS      | 7           | 6            | 5            | 4              | 3          | 2   | 1   | 0   |

|-----------|-------------|--------------|--------------|----------------|------------|-----|-----|-----|

| FIELD     |             |              |              | TSC            | ALL        |     |     |     |

| RESET     | U           | U            | U            | U              | U          | U   | U   | U   |

| R/W       | R/W         | R/W          | R/W          | R/W            | R/W        | R/W | R/W | R/W |

| ADDR      |             |              | Info         | rmation Pag    | e Memory 0 | 03B |     |     |

| Note: U = | Unchanged b | y Reset. R/W | = Read/Write | <del>)</del> . |            |     |     |     |

TSCALL – Temperature Sensor Calibration Low Byte

The TSCALH and TSCALL bytes combine to form the 12-bit temperature sensor offset calibration value. For usage details, see Temperature Sensor Operation on page 139.

# **Watchdog Timer Calibration Data**

Table 97. Watchdog Calibration High Byte at 007EH (WDTCALH)

| BITS      | 7           | 6            | 5            | 4           | 3         | 2   | 1   | 0   |

|-----------|-------------|--------------|--------------|-------------|-----------|-----|-----|-----|

| FIELD     |             |              |              | WDT         | CALH      |     |     |     |

| RESET     | U           | U            | U            | U           | U         | U   | U   | U   |

| R/W       | R/W         | R/W          | R/W          | R/W         | R/W       | R/W | R/W | R/W |

| ADDR      |             |              | Infor        | mation Page | Memory 00 | 7EH |     |     |

| Note: U = | Unchanged b | y Reset. R/W | = Read/Write | <b>)</b> .  |           |     |     |     |

PS022825-0908 Flash Option Bits

read operations to illegal addresses. Also, the user code must pop the address byte off the stack.

The read routine uses 9 bytes of stack space in addition to the one byte of address pushed by the user. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS reads exhibit a non-uniform execution time. A read operation takes between 44 µs and 489 µs (assuming a 20 MHz system clock). Slower system clock speeds result in proportionally higher execution times.

NVDS byte reads from invalid addresses (those exceeding the NVDS array size) return 0xff. Illegal read operations have a 2 µs execution time.

The status byte returned by the NVDS read routine is zero for successful read, as determined by a CRC check. If the status byte is non-zero, there was a corrupted value in the NVDS array at the location being read. In this case, the value returned in R0 is the byte most recently written to the array that does not have a CRC error.

#### **Power Failure Protection**

The NVDS routines employ error checking mechanisms to ensure a power failure endangers only the most recently written byte. Bytes previously written to the array are not perturbed.

A system reset (such as a pin reset or Watchdog Timer reset) that occurs during a write operation also perturbs the byte currently being written. All other bytes in the array are unperturbed.

# **Optimizing NVDS Memory Usage for Execution Speed**

The NVDS read time varies drastically, this discrepancy being a trade-off for minimizing the frequency of writes that require post-write page erases (see Table 104). The NVDS read time of address N is a function of the number of writes to addresses other than N since the most recent write to address N, as well as the number of writes since the most recent page erase. Neglecting effects caused by page erases and results caused by the initial condition in which the NVDS is blank, a rule of thumb is that every write since the most recent page erase causes read times of unwritten addresses to increase by 1 µs, up to a maximum of (511-NVDS SIZE) us.

Table 104, NVDS Read Time

| Operation            | Minimum<br>Latency | Maximum<br>Latency |

|----------------------|--------------------|--------------------|

| Read (16 byte array) | 875                | 9961               |

| Read (64 byte array) | 876                | 8952               |

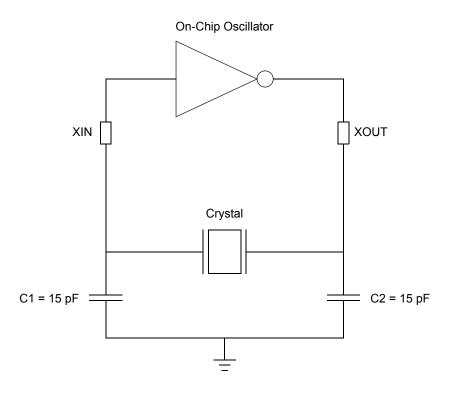

Figure 27 displays a recommended configuration for connection with an external fundamental-mode, parallel-resonant crystal operating at 20 MHz. Recommended 20 MHz crystal specifications are provided in Table 110. Printed circuit board layout must add no more than 4 pF of stray capacitance to either the  $X_{IN}$  or  $X_{OUT}$  pins. If oscillation does not occur, reduce the values of capacitors  $C_1$  and  $C_2$  to decrease loading.

Figure 27. Recommended 20 MHz Crystal Oscillator Configuration

**Table 110. Recommended Crystal Oscillator Specifications**

| Parameter                           | Value       | Units | Comments |

|-------------------------------------|-------------|-------|----------|

| Frequency                           | 20          | MHz   |          |

| Resonance                           | Parallel    |       |          |

| Mode                                | Fundamental |       |          |

| Series Resistance (R <sub>S</sub> ) | 60          | Ω     | Maximum  |

| Load Capacitance (C <sub>L</sub> )  | 30          | pF    | Maximum  |

| Shunt Capacitance (C <sub>0</sub> ) | 7           | pF    | Maximum  |

| Drive Level                         | 1           | mW    | Maximum  |

PS022825-0908 Crystal Oscillator

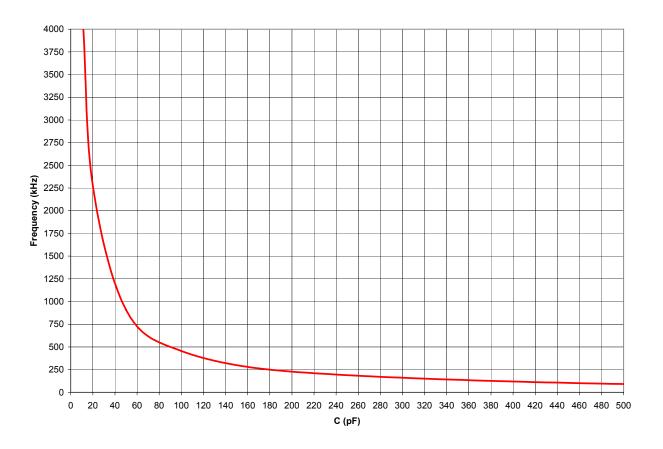

Figure 29 displays the typical (3.3 V and 25 °C) oscillator frequency as a function of the capacitor (C in pF) employed in the RC network assuming a 45 K $\Omega$  external resistor. For very small values of C, the parasitic capacitance of the oscillator XIN pin and the printed circuit board must be included in the estimation of the oscillator frequency.

It is possible to operate the RC oscillator using only the parasitic capacitance of the package and printed circuit board. To minimize sensitivity to external parasitics, external capacitance values in excess of 20 pF are recommended.

Figure 29. Typical RC Oscillator Frequency as a Function of the External Capacitance with a 45  $k\Omega$  Resistor

Caution:

When using the external RC oscillator mode, the oscillator can stop oscillating if the power supply drops below 2.7 V, but before the power supply drops to the Voltage Brownout threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7 V.

PS022825-0908 Crystal Oscillator

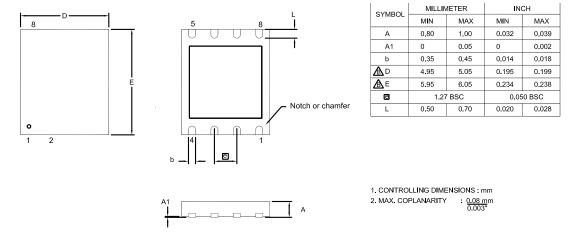

Figure 41 displays the 8-pin Quad Flat No-Lead package (QFN)/MLF-S available for the Z8 Encore! XP F082A Series devices. This package has a footprint identical to that of the 8-pin SOIC, but with a lower profile.

Figure 41. 8-Pin Quad Flat No-Lead Package (QFN)/MLF-S

PS022825-0908 Packaging

**z**ilog°

259

| Part Number                                 | Flash | RAM                                               | NVDS    | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description |  |

|---------------------------------------------|-------|---------------------------------------------------|---------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|-------------|--|

| Z8 Encore! XP® F082A Series Development Kit |       |                                                   |         |           |            |                     |                     |                |            |                    |             |  |

| Z8F08A28100KITG                             |       | Z8 Enc                                            | ore! XP | F082      | A Se       | ries                | 28-Pi               | in De          | velop      | mer                | nt Kit      |  |

| Z8F04A28100KITG                             |       | Z8 Encore! XP F042A Series 28-Pin Development Kit |         |           |            |                     |                     |                |            |                    |             |  |

| Z8F04A08100KITG                             |       | Z8 Encore! XP F042A Series 8-Pin Development Kit  |         |           |            |                     |                     |                |            |                    |             |  |

| ZUSBSC00100ZACG                             |       | USB Smart Cable Accessory Kit                     |         |           |            |                     |                     |                |            |                    |             |  |

| ZUSBOPTSC01ZACG                             |       | USB Opto-Isolated Smart Cable Accessory Kit       |         |           |            |                     |                     |                |            |                    |             |  |

| ZENETSC0100ZACG                             |       | Ethernet Smart Cable Accessory Kit                |         |           |            |                     |                     |                |            |                    |             |  |

|                                             |       |                                                   |         |           |            |                     |                     |                |            |                    |             |  |

PS022825-0908 Ordering Information

zilog

267

| register 201                                | RLC 206                                             |  |  |  |  |  |  |

|---------------------------------------------|-----------------------------------------------------|--|--|--|--|--|--|

| ADC control (ADCCTL) 130, 132               | rotate and shift instuctions 206                    |  |  |  |  |  |  |

| ADC data high byte (ADCDH) 132              | rotate left 206                                     |  |  |  |  |  |  |

| ADC data low bits (ADCDL) 133               | rotate left through carry 206                       |  |  |  |  |  |  |

| flash control (FCTL) 149, 155, 156          | rotate right 206                                    |  |  |  |  |  |  |

| flash high and low byte (FFREQH and         | rotate right through carry 206                      |  |  |  |  |  |  |

| FREEQL) 152                                 | RP 202                                              |  |  |  |  |  |  |

| flash page select (FPS) 150, 151            | RR 201, 206                                         |  |  |  |  |  |  |

| flash status (FSTAT) 150                    | rr 201                                              |  |  |  |  |  |  |

| GPIO port A-H address (PxADDR) 46           | RRC 206                                             |  |  |  |  |  |  |

| GPIO port A-H alternate function sub-regis- |                                                     |  |  |  |  |  |  |

| ters 48                                     |                                                     |  |  |  |  |  |  |

| GPIO port A-H control address (PxCTL) 47    | S                                                   |  |  |  |  |  |  |

| GPIO port A-H data direction sub-registers  | SBC 203                                             |  |  |  |  |  |  |

| 47                                          | SCF 204, 205                                        |  |  |  |  |  |  |

| OCD control 184                             | second opcode map after 1FH 219                     |  |  |  |  |  |  |

| OCD status 185                              |                                                     |  |  |  |  |  |  |

| UARTx baud rate high byte (UxBRH) 114       | set carry flag 204, 205<br>set register pointer 205 |  |  |  |  |  |  |

| UARTx baud rate low byte (UxBRL) 114        | shift right arithmatic 207                          |  |  |  |  |  |  |

| UARTx Control 0 (UxCTL0) 108, 114           | <del>-</del>                                        |  |  |  |  |  |  |

| UARTx control 1 (UxCTL1) 109                | shift right logical 207 signal descriptions 11      |  |  |  |  |  |  |

| UARTx receive data (UxRXD) 113              |                                                     |  |  |  |  |  |  |

| UARTx status 0 (UxSTAT0) 111                | single-shot conversion (ADC) 123                    |  |  |  |  |  |  |

| UARTx status 1 (UxSTAT1) 112                | software trap 206                                   |  |  |  |  |  |  |

| UARTx transmit data (UxTXD) 113             | source operand 202                                  |  |  |  |  |  |  |

| Watchdog Timer control (WDTCTL) 31, 94,     | SP 202                                              |  |  |  |  |  |  |

| 136, 190                                    | SRA 207                                             |  |  |  |  |  |  |

| Watchdog Timer reload high byte (WDTH)      | src 202                                             |  |  |  |  |  |  |

| 95                                          | SRL 207                                             |  |  |  |  |  |  |

| Watchdog Timer reload low byte (WDTL)       | SRP 205                                             |  |  |  |  |  |  |

| 95                                          | stack pointer 202                                   |  |  |  |  |  |  |

| Watchdog Timer reload upper byte (WD-       | STOP 205                                            |  |  |  |  |  |  |

| TU) 95                                      | STOP mode 33                                        |  |  |  |  |  |  |

| register file 15                            | stop mode 205                                       |  |  |  |  |  |  |

| register pair 201                           | Stop Mode Recovery                                  |  |  |  |  |  |  |

| register pointer 202                        | sources 28                                          |  |  |  |  |  |  |

| reset                                       | using a GPIO port pin transition 29                 |  |  |  |  |  |  |

| and stop mode characteristics 24            | using Watchdog Timer time-out 29                    |  |  |  |  |  |  |

| and Stop Mode Recovery 23                   | stop mode recovery                                  |  |  |  |  |  |  |

| carry flag 204                              | sources 30                                          |  |  |  |  |  |  |

| sources 25                                  | using a GPIO port pin transition 30                 |  |  |  |  |  |  |

| RET 206                                     | SUB 203                                             |  |  |  |  |  |  |

| return 206                                  | subtract 203                                        |  |  |  |  |  |  |

| RL 206                                      | subtract - extended addressing 203                  |  |  |  |  |  |  |

| NL ZUU                                      | subtract with carry 203                             |  |  |  |  |  |  |

PS022825-0908 Index