## E·XFL

#### Zilog - Z8F011AHJ020SC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | IrDA, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT               |

| Number of I/O              | 25                                                            |

| Program Memory Size        | 1KB (1K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | 16 × 8                                                        |

| RAM Size                   | 256 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | -                                                             |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                                |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f011ahj020sc00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| Overview                                            |

|-----------------------------------------------------|

| Features                                            |

| Part Selection Guide                                |

| Block Diagram                                       |

| CPU and Peripheral Overview                         |

| eZ8 CPU Features 5                                  |

| 10-Bit Analog-to-Digital Converter 5                |

| Low-Power Operational Amplifier                     |

| Internal Precision Oscillator                       |

| Temperature Sensor    6      Analog Comparator    6 |

| External Crystal Oscillator                         |

| Low Voltage Detector                                |

| On-Chip Debugger                                    |

| Universal Asynchronous Receiver/Transmitter         |

| Timers                                              |

| General-Purpose Input/Output                        |

| Direct LED Drive                                    |

| Non-Volatile Data Storage                           |

| Interrupt Controller                                |

| Reset Controller                                    |

| Pin Description                                     |

| Available Packages                                  |

| Pin Configurations                                  |

| Signal Descriptions                                 |

| Pin Characteristics                                 |

| Address Space                                       |

|                                                     |

| Register File                                       |

| Program Memory                                      |

| Data Memory                                         |

| Flash Information Area 17                           |

| Register Map                                        |

### **Signal Descriptions**

Table 2 describes the Z8 Encore! XP F082A Series signals. See Pin Configurations on page 9 to determine the signals available for the specific package styles.

| Signal Mnemonic                                     | I/O | Description                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|-----------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| General-Purpose I/O Ports A–D                       |     |                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| PA[7:0]                                             | I/O | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| PB[7:0]                                             | I/O | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |  |  |  |  |  |  |

| PC[7:0]                                             | I/O | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| PD[0]                                               | I/O | Port D. This pin is used for general-purpose output only.                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Note: PB6 and PB7 ar<br>replaced by AV <sub>E</sub> |     | vailable in 28-pin packages without ADC. In 28-pin packages with ADC, they are $V_{\rm SS}.$                                                                                                                                                                                                            |  |  |  |  |  |  |

| UART Controllers                                    |     |                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| TXD0                                                | 0   | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |  |  |  |  |  |  |

| RXD0                                                | Ι   | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| CTS0                                                | Ι   | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| DE                                                  | 0   | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 register. The DE signal may be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |  |  |  |  |  |  |

| Timers                                              |     |                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| T0OUT/T1OUT                                         | 0   | Timer Output 0–1. These signals are outputs from the timers.                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| T0OUT/T1OUT                                         | 0   | Timer Complement Output 0–1. These signals are output from the timers in PWM Dual Output mode.                                                                                                                                                                                                          |  |  |  |  |  |  |

| T0IN/T1IN                                           | Ι   | Timer Input 0–1. These signals are used as the capture, gating and counter inputs.                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Comparator                                          |     |                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| CINP/CINN                                           | Ι   | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |  |  |  |  |  |  |

| COUT                                                | 0   | Comparator Output.                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

#### Table 2. Signal Descriptions

#### Table 2. Signal Descriptions (Continued)

| Signal Mnemonic  | I/O      | Description                                                                       |

|------------------|----------|-----------------------------------------------------------------------------------|

| Power Supply     |          |                                                                                   |

| V <sub>DD</sub>  | Ι        | Digital Power Supply.                                                             |

| AV <sub>DD</sub> | Ι        | Analog Power Supply.                                                              |

| V <sub>SS</sub>  | I        | Digital Ground.                                                                   |

| AV <sub>SS</sub> | Ι        | Analog Ground.                                                                    |

| Note: The AV     | Vee siar | nals are available only in 28-pin packages with ADC. They are replaced by PB6 and |

**Note:** The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

### **Pin Characteristics**

Table 3 describes the characteristics for each pin available on the Z8 Encore! XP F082A Series 20- and 28-pin devices. Data in Table 3 is sorted alphabetically by the pin symbol mnemonic.

Table 4 on page 14 provides detailed information about the characteristics for each pin available on the Z8 Encore! XP F082A Series 8-pin devices.

Note:

All six I/O pins on the 8-pin packages are 5 V-tolerant (unless the pull-up devices are enabled). The column in Table 3 below describes 5 V-tolerance for the 20- and 28-pin packages only.

#### Table 3. Pin Characteristics (20- and 28-pin Devices)

| Symbol<br>Mnemonic | Direction | Reset<br>Direction | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal Pull-<br>up<br>or Pull-down | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output | 5 V<br>Tolerance                        |

|--------------------|-----------|--------------------|---------------------------------------|--------------------|--------------------------------------|------------------------------|----------------------|-----------------------------------------|

| AVDD               | N/A       | N/A                | N/A                                   | N/A                | N/A                                  | N/A                          | N/A                  | N/A                                     |

| AVSS               | N/A       | N/A                | N/A                                   | N/A                | N/A                                  | N/A                          | N/A                  | NA                                      |

| DBG                | I/O       | I                  | N/A                                   | Yes                | Yes                                  | Yes                          | Yes                  | No                                      |

| PA[7:0]            | I/O       | I                  | N/A                                   | Yes                | Programmable<br>Pull-up              | Yes                          | Yes,<br>Programmable | PA[7:2]<br>unless<br>pullups<br>enabled |

| PB[7:0]            | I/O       | I                  | N/A                                   | Yes                | Programmable<br>Pull-up              | Yes                          | Yes,<br>Programmable | PB[7:6]<br>unless<br>pullups<br>enabled |

## **Address Space**

The eZ8 CPU can access the following three distinct address spaces:

- 1. The Register File contains addresses for the general-purpose registers and the eZ8 CPU, peripheral, and general-purpose I/O port control registers.

- 2. The Program Memory contains addresses for all memory locations having executable code and/or data.

- 3. The Data Memory contains addresses for all memory locations that contain data only.

These three address spaces are covered briefly in the following subsections. For more information on eZ8 CPU and its address space, refer to eZ8 CPU Core User Manual (UM0128) available for download at www.zilog.com.

### **Register File**

The Register File address space in the Z8 Encore!<sup>®</sup> MCU is 4 KB (4096 bytes). The Register File is composed of two sections: control registers and general-purpose registers. When instructions are executed, registers defined as sources are read, and registers defined as destinations are written. The architecture of the eZ8 CPU allows all general-purpose registers to function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

The upper 256 bytes of the 4 KB Register File address space are reserved for control of the eZ8 CPU, the on-chip peripherals, and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256 B control register section are reserved (unavailable). Reading from a reserved Register File address returns an undefined value. Writing to reserved Register File addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address 000H in the Register File address space. The Z8 Encore! XP<sup>®</sup> F082A Series devices contain 256 B to 1 KB of on-chip RAM. Reading from Register File addresses outside the available RAM addresses (and not within the control register address space) returns an undefined value. Writing to these Register File addresses produces no effect.

### **Program Memory**

The eZ8 CPU supports 64 KB of Program Memory address space. The Z8 Encore! XP F082A Series devices contain 1 KB to 8 KB of on-chip Flash memory in the Program Memory address space, depending on the device. Reading from Program Memory

| BITS  | 7                      | 6    | 5   | 4   | 3        | 2 | 1 | 0   |

|-------|------------------------|------|-----|-----|----------|---|---|-----|

| FIELD | POR                    | STOP | WDT | EXT | Reserved |   |   | LVD |

| RESET | See descriptions below |      |     | 0   | 0        | 0 | 0 | 0   |

| R/W   | R                      | R    | R   | R   | R        | R | R | R   |

| ADDR  |                        | FFOH |     |     |          |   |   |     |

#### Table 11. Reset Status Register (RSTSTAT)

| Reset or Stop Mode Recovery Event                     | POR | STOP | WDT | EXT |

|-------------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                        | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion                       | 0   | 0    | 0   | 1   |

| Reset using Watchdog Timer time-out                   | 0   | 0    | 1   | 0   |

| Reset using the On-Chip Debugger (OCTCTL[1] set to 1) | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low         | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition          | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using Watchdog Timer time-out      | 0   | 1    | 1   | 0   |

#### POR—Power-On Reset Indicator

If this bit is set to 1, a Power-On Reset event occurs. This bit is reset to 0 if a WDT time-out or Stop Mode Recovery occurs. This bit is also reset to 0 when the register is read.

#### STOP—Stop Mode Recovery Indicator

If this bit is set to 1, a Stop Mode Recovery occurs. If the STOP and WDT bits are both set to 1, the Stop Mode Recovery occurs because of a WDT time-out. If the STOP bit is 1 and the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a Power-On Reset or a WDT time-out that occurred while not in STOP mode. Reading this register also resets this bit.

#### WDT—Watchdog Timer Time-Out Indicator

If this bit is set to 1, a WDT time-out occurs. A POR resets this pin. A Stop Mode Recovery from a change in an input pin also resets this bit. Reading this register resets this bit. This read must occur before clearing the WDT interrupt.

#### EXT-External Reset Indicator

If this bit is set to 1, a Reset initiated by the external  $\overline{\text{RESET}}$  pin occurs. A Power-On Reset or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register resets this bit.

#### Reserved—Must be 0.

LVD—Low Voltage Detection Indicator

If this bit is set to 1 the current state of the supply voltage is below the low voltage detection threshold. This value is not latched but is a real-time indicator of the supply voltage level.

# zilog <sub>37</sub>

## **General-Purpose Input/Output**

The Z8 Encore! XP<sup>®</sup> F082A Series products support a maximum of 25 port pins (Ports A– D) for general-purpose input/output (GPIO) operations. Each port contains control and data registers. The GPIO control registers determine data direction, open-drain, output drive current, programmable pull-ups, Stop Mode Recovery functionality, and alternate pin functions. Each port pin is individually programmable. In addition, the Port C pins are capable of direct LED drive at programmable drive strengths.

### **GPIO Port Availability By Device**

Table 13 lists the port pins available with each device and package type.

| Devices                         | Package | ADC | Port A | Port B | Port C | Port D | Total I/O |

|---------------------------------|---------|-----|--------|--------|--------|--------|-----------|

| Z8F082ASB, Z8F082APB, Z8F082AQB | 8-pin   | Yes | [5:0]  | No     | No     | No     | 6         |

| Z8F042ASB, Z8F042APB, Z8F042AQB |         |     |        |        |        |        |           |

| Z8F022ASB, Z8F022APB, Z8F022AQB |         |     |        |        |        |        |           |

| Z8F012ASB, Z8F012APB, Z8F012AQB |         |     |        |        |        |        |           |

| Z8F081ASB, Z8F081APB, Z8F081AQB | 8-pin   | No  | [5:0]  | No     | No     | No     | 6         |

| Z8F041ASB, Z8F041APB, Z8F041AQB |         |     |        |        |        |        |           |

| Z8F021ASB, Z8F021APB, Z8F021AQB |         |     |        |        |        |        |           |

| Z8F011ASB, Z8F011APB, Z8F011AQB |         |     |        |        |        |        |           |

| Z8F082APH, Z8F082AHH, Z8F082ASH | 20-pin  | Yes | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F042APH, Z8F042AHH, Z8F042ASH |         |     |        |        |        |        |           |

| Z8F022APH, Z8F022AHH, Z8F022ASH |         |     |        |        |        |        |           |

| Z8F012APH, Z8F012AHH, Z8F012ASH |         |     |        |        |        |        |           |

| Z8F081APH, Z8F081AHH, Z8F081ASH | 20-pin  | No  | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F041APH, Z8F041AHH, Z8F041ASH | •       |     |        |        |        |        |           |

| Z8F021APH, Z8F021AHH, Z8F021ASH |         |     |        |        |        |        |           |

| Z8F011APH, Z8F011AHH, Z8F011ASH |         |     |        |        |        |        |           |

| Z8F082APJ, Z8F082ASJ, Z8F082AHJ | 28-pin  | Yes | [7:0]  | [5:0]  | [7:0]  | [0]    | 23        |

| Z8F042APJ, Z8F042ASJ, Z8F042AHJ | •       |     |        |        |        |        |           |

| Z8F022APJ, Z8F022ASJ, Z8F022AHJ |         |     |        |        |        |        |           |

| Z8F012APJ, Z8F012ASJ, Z8F012AHJ |         |     |        |        |        |        |           |

| Z8F081APJ, Z8F081ASJ, Z8F081AHJ | 28-pin  | No  | [7:0]  | [7:0]  | [7:0]  | [0]    | 25        |

| Z8F041APJ, Z8F041ASJ, Z8F041AHJ | •       |     |        |        |        |        |           |

| Z8F021APJ, Z8F021ASJ, Z8F021AHJ |         |     |        |        |        |        |           |

| Z8F011APJ, Z8F011ASJ, Z8F011AHJ |         |     |        |        |        |        |           |

#### Table 13. Port Availability by Device and Package Type

zilog | 1

The UART is now configured for interrupt-driven data transmission. Because the UART Transmit Data register is empty, an interrupt is generated immediately. When the UART Transmit interrupt is detected, the associated interrupt service routine (ISR) performs the following:

- 1. Write the UART Control 1 register to select the multiprocessor bit for the byte to be transmitted:

- 2. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 3. Write the data byte to the UART Transmit Data register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 4. Clear the UART Transmit interrupt bit in the applicable Interrupt Request register.

- 5. Execute the IRET instruction to return from the interrupt-service routine and wait for the Transmit Data register to again become empty.

#### **Receiving Data using the Polled Method**

Follow the steps below to configure the UART for polled data reception:

- 1. Write to the UART Baud Rate High and Low Byte registers to set an acceptable baud rate for the incoming data stream.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Write to the UART Control 1 register to enable MULTIPROCESSOR mode functions, if appropriate.

- 4. Write to the UART Control 0 register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if Multiprocessor mode is not enabled, and select either even or odd parity.

- 5. Check the RDA bit in the UART Status 0 register to determine if the Receive Data register contains a valid data byte (indicated by a 1). If RDA is set to 1 to indicate available data, continue to Step 5. If the Receive Data register is empty (indicated by a 0), continue to monitor the RDA bit awaiting reception of the valid data.

- Read data from the UART Receive Data register. If operating in MULTIPROCESSOR (9-bit) mode, further actions may be required depending on the MULTIPROCESSOR mode bits MPMD[1:0].

- 7. Return to Step 4 to receive additional data.

#### **Receiving Data using the Interrupt-Driven Method**

The UART Receiver interrupt indicates the availability of new data (as well as error conditions). Follow the steps below to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the acceptable baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Receiver interrupt and set the acceptable priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 6. Write to the UART Control 1 Register to enable Multiprocessor (9-bit) mode functions, if appropriate.

- Set the Multiprocessor Mode Select (MPEN) to Enable MULTIPROCESSOR mode.

- Set the Multiprocessor Mode Bits, MPMD[1:0], to select the acceptable address matching scheme.

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore!<sup>®</sup> devices without a DMA block)

- 7. Write the device address to the Address Compare Register (automatic MULTIPRO-CESSOR modes only).

- 8. Write to the UART Control 0 register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if multiprocessor mode is not enabled, and select either even or odd parity.

- 9. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine (ISR) performs the following:

- 1. Checks the UART Status 0 register to determine the source of the interrupt error, break, or received data.

- 2. Reads the data from the UART Receive Data register if the interrupt was because of data available. If operating in MULTIPROCESSOR (9-bit) mode, further actions may be required depending on the MULTIPROCESSOR mode bits MPMD[1:0].

#### MPMD[1:0]—MULTIPROCESSOR Mode

If MULTIPROCESSOR (9-bit) mode is enabled,

00 = The UART generates an interrupt request on all received bytes (data and address).

01 = The UART generates an interrupt request only on received address bytes.

10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs.

11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register.

#### MPEN—MULTIPROCESSOR (9-bit) Enable

This bit is used to enable MULTIPROCESSOR (9-bit) mode.

0 = Disable MULTIPROCESSOR (9-bit) mode.

1 = Enable MULTIPROCESSOR (9-bit) mode.

#### MPBT—Multiprocessor Bit Transmit

This bit is applicable only when MULTIPROCESSOR (9-bit) mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.

0 = Send a 0 in the multiprocessor bit location of the data stream (data byte).

1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).

#### DEPOL—Driver Enable Polarity

0 = DE signal is Active High.

1 = DE signal is Active Low.

#### BRGCTL—Baud Rate Control

This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register.

When the UART receiver is **not** enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value 1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.

When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value. 1 = Reads from the Baud Rate High and Low Byte registers return the current BRG count value. Unlike the Timers, there is no mechanism to latch the Low Byte when the High Byte is read.

RDAIRQ—Receive Data Interrupt Enable

0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.

### Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

zilog

162

| Info Page<br>Address | Memory<br>Address | Compensation Usage      | ADC Mode                 | Reference<br>Type |

|----------------------|-------------------|-------------------------|--------------------------|-------------------|

| 60                   | FE60              | Offset                  | Single-Ended Unbuffered  | Internal 2.0 V    |

| 08                   | FE08              | Gain High Byte          | Single-Ended Unbuffered  | Internal 2.0 V    |

| 09                   | FE09              | Gain Low Byte           | Single-Ended Unbuffered  | Internal 2.0 V    |

| 63                   | FE63              | Offset                  | Single-Ended Unbuffered  | Internal 1.0 V    |

| 0A                   | FE0A              | Gain High Byte          | Single-Ended Unbuffered  | Internal 1.0 V    |

| 0B                   | FE0B              | Gain Low Byte           | Single-Ended Unbuffered  | Internal 1.0 V    |

| 66                   | FE66              | Offset                  | Single-Ended Unbuffered  | External 2.0 V    |

| 0C                   | FE0C              | Gain High Byte          | Single-Ended Unbuffered  | External 2.0 V    |

| 0D                   | FE0D              | Gain Low Byte           | Single-Ended Unbuffered  | External 2.0 V    |

| 69                   | FE69              | Offset                  | Single-Ended 1x Buffered | Internal 2.0 V    |

| 0E                   | FE0E              | Gain High Byte          | Single-Ended 1x Buffered | Internal 2.0 V    |

| 0F                   | FE0F              | Gain Low Byte           | Single-Ended 1x Buffered | Internal 2.0 V    |

| 6C                   | FE6C              | Offset                  | Single-Ended 1x Buffered | External 2.0 V    |

| 10                   | FE10              | Gain High Byte          | Single-Ended 1x Buffered | External 2.0 V    |

| 11                   | FE11              | Gain Low Byte           | Single-Ended 1x Buffered | External 2.0 V    |

| 6F                   | FE6F              | Offset                  | Differential Unbuffered  | Internal 2.0 V    |

| 12                   | FE12              | Positive Gain High Byte | Differential Unbuffered  | Internal 2.0 V    |

| 13                   | FE13              | Positive Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V    |

| 30                   | FE30              | Negative Gain High Byte | Differential Unbuffered  | Internal 2.0 V    |

| 31                   | FE31              | Negative Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V    |

| 72                   | FE72              | Offset                  | Differential Unbuffered  | Internal 1.0 V    |

| 14                   | FE14              | Positive Gain High Byte | Differential Unbuffered  | Internal 1.0 V    |

| 15                   | FE15              | Positive Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V    |

| 32                   | FE32              | Negative Gain High Byte | Differential Unbuffered  | Internal 1.0 V    |

| 33                   | FE33              | Negative Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V    |

| 75                   | FE75              | Offset                  | Differential Unbuffered  | External 2.0 V    |

| 16                   | FE16              | Positive Gain High Byte | Differential Unbuffered  | External 2.0 V    |

| 17                   | FE17              | Positive Gain Low Byte  | Differential Unbuffered  | External 2.0 V    |

|                      |                   |                         |                          |                   |

#### Table 94. ADC Calibration Data Location

zilog

165

WDTCALH—Watchdog Timer Calibration High Byte The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload registers result in a one second timeout at room temperature and 3.3 V supply voltage. To use the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDTCALH and WDTL with WDTCALL.

#### Table 98. Watchdog Calibration Low Byte at 007FH (WDTCALL)

| BITS      | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| FIELD     | WDTCALL                                         |     |     |     |     |     |     |     |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR      | Information Page Memory 007FH                   |     |     |     |     |     |     |     |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |

WDTCALL—Watchdog Timer Calibration Low Byte

The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload registers result in a one second timeout at room temperature and 3.3 V supply voltage. To use the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDTCALH and WDTL with WDTCALL.

### **Serialization Data**

#### Table 99. Serial Number at 001C - 001F (S\_NUM)

| BITS                                            | 7                                 | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------------------------------|-----------------------------------|-----|-----|-----|-----|-----|-----|-----|

| FIELD                                           | S_NUM                             |     |     |     |     |     |     |     |

| RESET                                           | U                                 | U   | U   | U   | U   | U   | U   | U   |

| R/W                                             | R/W                               | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR                                            | Information Page Memory 001C-001F |     |     |     |     |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                                   |     |     |     |     |     |     |     |

S NUM—Serial Number Byte

The serial number is a unique four-byte binary value.

## **On-Chip Debugger**

The Z8 Encore! XP<sup>®</sup> F082A Series devices contain an integrated On-Chip Debugger (OCD) that provides advanced debugging features including:

- Single pin interface.

- Reading and writing of the register file.

- Reading and writing of program and data memory.

- Setting of breakpoints and watchpoints.

- Executing eZ8 CPU instructions.

- Debug pin sharing with general-purpose input-output function to maximize pins available to the user (8-pin product only).

### Architecture

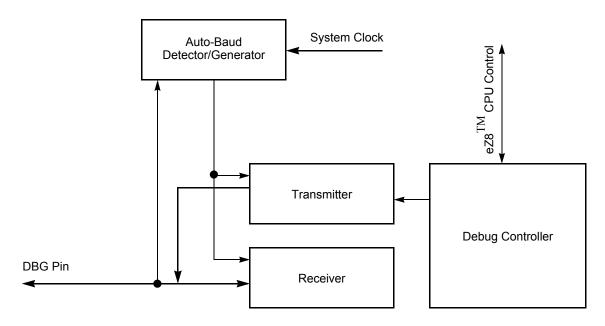

The on-chip debugger consists of four primary functional blocks: transmitter, receiver, auto-baud detector/generator, and debug controller. Figure 23 displays the architecture of the on-chip debugger.

Figure 23. On-Chip Debugger Block Diagram

zilog

#### Table 108. Oscillator Configuration and Selection

| Clock Source                          | Characteristics                                                                                                                                 | Required Setup                                                                                                                                                                                                                                                                                       |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Precision<br>RC Oscillator   | <ul> <li>32.8 kHz or 5.53 MHz</li> <li>High accuracy</li> <li>No external components required</li> </ul>                                        | Unlock and write Oscillator Control<br>Register (OSCCTL) to enable and<br>select oscillator at either 5.53 MHz or<br>32.8 kHz                                                                                                                                                                        |

| External Crystal/<br>Resonator        | <ul> <li>32 kHz to 20 MHz</li> <li>Very high accuracy (dependent on crystal or resonator used)</li> <li>Requires external components</li> </ul> | <ul> <li>Configure Flash option bits for correct<br/>external oscillator mode</li> <li>Unlock and write OSCCTL to enable<br/>crystal oscillator, wait for it to stabilize<br/>and select as system clock (if the<br/>XTLDIS option bit has been de-<br/>asserted, no waiting is required)</li> </ul> |

| External RC<br>Oscillator             | <ul> <li>32 kHz to 4 MHz</li> <li>Accuracy dependent on external components</li> </ul>                                                          | <ul> <li>Configure Flash option bits for correct<br/>external oscillator mode</li> <li>Unlock and write OSCCTL to enable<br/>crystal oscillator and select as system<br/>clock</li> </ul>                                                                                                            |

| External Clock<br>Drive               | <ul> <li>0 to 20 MHz</li> <li>Accuracy dependent on external clock source</li> </ul>                                                            | <ul> <li>Write GPIO registers to configure PB3<br/>pin for external clock function</li> <li>Unlock and write OSCCTL to select<br/>external system clock</li> <li>Apply external clock signal to GPIO</li> </ul>                                                                                      |

| Internal Watchdog<br>Timer Oscillator | <ul> <li>10 kHz nominal</li> <li>Low accuracy; no external components required</li> <li>Very low power consumption</li> </ul>                   | <ul> <li>Enable WDT if not enabled and wait<br/>until WDT Oscillator is operating.</li> <li>Unlock and write Oscillator Control<br/>Register (OSCCTL) to enable and<br/>select oscillator</li> </ul>                                                                                                 |

**Caution:** Unintentional accesses to the oscillator control register can actually stop the chip by switching to a non-functioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

#### **OSC Control Register Unlocking/Locking**

To write the oscillator control register, unlock it by making two writes to the OSCCTL register with the values E7H followed by 18H. A third write to the OSCCTL register changes the value of the actual register and returns the register to a locked state. Any other sequence of oscillator control register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

zilog

189

When selecting a new clock source, the system clock oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If SOFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the OSCCTL register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it may be appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

#### **Clock Failure Detection and Recovery**

#### System Clock Oscillator Failure

The Z8F04xA family devices can generate non-maskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function (see Watchdog Timer on page 91).

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below 1 kHz  $\pm$ 50%. If an external signal is selected as the system oscillator, it is possible that a very slow but non-failing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (SOFEN must be deasserted in the OSCCTL register).

#### Watchdog Timer Failure

In the event of a Watchdog Timer oscillator failure, a similar non-maskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the system clock oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while looking for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

|                           | V <sub>DD</sub> = 2.7 V to 3.6 V                                              |              |                      |          |       |                                                                  |  |  |  |  |

|---------------------------|-------------------------------------------------------------------------------|--------------|----------------------|----------|-------|------------------------------------------------------------------|--|--|--|--|

|                           |                                                                               |              | Maximum <sup>2</sup> | _        |       |                                                                  |  |  |  |  |

| Symbol                    | Parameter                                                                     | Typical $^1$ | Std Temp             | Ext Temp | Units | Conditions                                                       |  |  |  |  |

| I <sub>DD</sub> Stop      | Supply Current in STOP<br>Mode                                                | 0.1          |                      |          | μA    | No peripherals enabled. All pins driven to $V_{DD}$ or $V_{SS}.$ |  |  |  |  |

| I <sub>DD</sub> Halt      | Supply Current in HALT                                                        | 35           | 55                   | 65       | μA    | 32 kHz                                                           |  |  |  |  |

|                           | Mode (with all peripherals disabled)                                          | 520          |                      |          | μA    | 5.5 MHz                                                          |  |  |  |  |

|                           | penpinenaie aleaalea)                                                         | 2.1          | 2.85                 | 2.85     | mA    | 20 MHz                                                           |  |  |  |  |

| I <sub>DD</sub>           | Supply Current in                                                             | 2.8          |                      |          | mA    | 32 kHz                                                           |  |  |  |  |

|                           | ACTIVE Mode (with all peripherals disabled)                                   | 4.5          | 5.2                  | 5.2      | mA    | 5.5 MHz                                                          |  |  |  |  |

|                           |                                                                               | 5.5          | 6.5                  | 6.5      | mA    | 10 MHz                                                           |  |  |  |  |

|                           | -                                                                             | 7.9          | 11.5                 | 11.5     | mA    | 20 MHz                                                           |  |  |  |  |

| I <sub>DD</sub> WDT       | Watchdog Timer Supply<br>Current                                              | 0.9          | 1.0                  | 1.1      | μA    |                                                                  |  |  |  |  |

| I <sub>DD</sub><br>XTAL   | Crystal Oscillator<br>Supply Current                                          | 40           |                      |          | μA    | 32 kHz                                                           |  |  |  |  |

|                           |                                                                               | 230          |                      |          | μA    | 4 MHz                                                            |  |  |  |  |

|                           |                                                                               | 760          |                      |          | μA    | 20 MHz                                                           |  |  |  |  |

| I <sub>DD</sub> IPO       | Internal Precision<br>Oscillator Supply<br>Current                            | 350          | 500                  | 550      | μA    |                                                                  |  |  |  |  |

| I <sub>DD</sub> VBO       | Voltage Brownout and<br>Low-Voltage Detect<br>Supply Current                  | 50           |                      |          | μA    | For 20-/28-pin devices<br>(VBO only); See Notes 4                |  |  |  |  |

|                           |                                                                               |              |                      |          |       | For 8-pin devices; See<br>Notes 4                                |  |  |  |  |

| I <sub>DD</sub> ADC       | Analog to Digital<br>Converter Supply<br>Current (with External<br>Reference) | 2.8          | 3.1                  | 3.2      | mA    | 32 kHz                                                           |  |  |  |  |

|                           |                                                                               | 3.1          | 3.6                  | 3.7      | mA    | 5.5 MHz                                                          |  |  |  |  |

|                           |                                                                               | 3.3          | 3.7                  | 3.8      | mA    | 10 MHz                                                           |  |  |  |  |

|                           | -                                                                             | 3.7          | 4.2                  | 4.3      | mA    | 20 MHz                                                           |  |  |  |  |

| I <sub>DD</sub><br>ADCRef | ADC Internal Reference<br>Supply Current                                      | 0            |                      |          | μA    | See Notes 4                                                      |  |  |  |  |

| I <sub>DD</sub> CMP       | Comparator supply<br>Current                                                  | 150          | 180                  | 190      | μA    | See Notes 4                                                      |  |  |  |  |

### Table 128. Power Consumption

**z**ilog<sup>°</sup>

### 229

### **On-Chip Peripheral AC and DC Electrical Characteristics**

#### Table 131. Power-On Reset and Voltage Brownout Electrical Characteristics and Timing

|                   |                                                                                                                | T <sub>A</sub> = - | 40 °C to +           | 105 °C  |       | Conditions                                                                                            |  |

|-------------------|----------------------------------------------------------------------------------------------------------------|--------------------|----------------------|---------|-------|-------------------------------------------------------------------------------------------------------|--|

| Symbol            | Parameter                                                                                                      | Minimum            | Typical <sup>1</sup> | Maximum | Units |                                                                                                       |  |

| V <sub>POR</sub>  | Power-On Reset<br>Voltage Threshold                                                                            | 2.20               | 2.45                 | 2.70    | V     | V <sub>DD</sub> = V <sub>POR</sub>                                                                    |  |

| V <sub>VBO</sub>  | Voltage Brownout Reset<br>Voltage Threshold                                                                    | 2.15               | 2.40                 | 2.65    | V     | $V_{DD} = V_{VBO}$                                                                                    |  |

|                   | $V_{POR}$ to $V_{VBO}$ hysteresis                                                                              |                    | 50                   | 75      | mV    |                                                                                                       |  |

|                   | Starting V <sub>DD</sub> voltage to<br>ensure valid Power-On<br>Reset.                                         | -                  | $V_{SS}$             | -       | V     |                                                                                                       |  |

| T <sub>ANA</sub>  | Power-On Reset Analog<br>Delay                                                                                 | -                  | 70                   | -       | μs    | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub> Digital<br>Reset delay follows T <sub>ANA</sub> |  |

| T <sub>POR</sub>  | Power-On Reset Digital<br>Delay                                                                                |                    | 16                   |         | μs    | 66 Internal Precision<br>Oscillator cycles + IPO<br>startup time (T <sub>IPOST</sub> )                |  |

| T <sub>POR</sub>  | Power-On Reset Digital<br>Delay                                                                                |                    | 1                    |         | ms    | 5000 Internal Precision<br>Oscillator cycles                                                          |  |

| T <sub>SMR</sub>  | Stop Mode Recovery<br>with crystal oscillator<br>disabled                                                      |                    | 16                   |         | μs    | 66 Internal Precision<br>Oscillator cycles                                                            |  |

| T <sub>SMR</sub>  | Stop Mode Recovery<br>with crystal oscillator<br>enabled                                                       |                    | 1                    |         | ms    | 5000 Internal Precision<br>Oscillator cycles                                                          |  |

| T <sub>VBO</sub>  | Voltage Brownout Pulse<br>Rejection Period                                                                     | _                  | 10                   | -       | μs    | Period of time in which V <sub>DD</sub><br>< V <sub>VBO</sub> without generating<br>a Reset.          |  |

| T <sub>RAMP</sub> | Time for V <sub>DD</sub> to<br>transition from V <sub>SS</sub> to<br>V <sub>POR</sub> to ensure valid<br>Reset | 0.10               | -                    | 100     | ms    |                                                                                                       |  |

| T <sub>SMP</sub>  | Stop Mode Recovery pin pulse rejection period                                                                  |                    | 20                   |         | ns    | For any SMR pin or for the Reset pin when it is asserted in STOP mode.                                |  |

only and are not tested in production.

### Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

zilog <sub>247</sub>

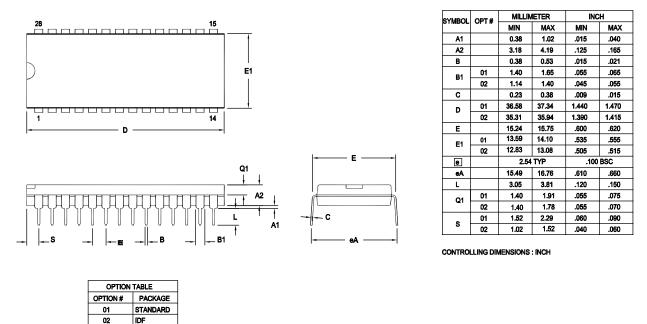

Note: ZILOG supplies both options for production. Component layout PCB design should cover bigger option 01.

#### Figure 45. 28-Pin Plastic Dual Inline Package (PDIP)

Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

# **z**ilog<sup>°</sup>

253

| Part Number                              | Flash    | RAM     | SQVN  | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|------------------------------------------|----------|---------|-------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F0824         |          |         |       | sn, 1     | 0-Bit      | Ana                 | log-t               | o-Dig          | ital C     | onv                | verter              |

| Standard Temperature                     |          |         |       |           |            |                     |                     |                |            |                    |                     |

| Z8F042APB020SC                           | 4 KB     | 1 KB    | 128 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F042AQB020SC                           | 4 KB     | 1 KB    | 128 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F042ASB020SC                           | 4 KB     | 1 KB    | 128 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F042ASH020SC                           | 4 KB     | 1 KB    | 128 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F042AHH020SC                           | 4 KB     | 1 KB    | 128 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F042APH020SC                           | 4 KB     | 1 KB    | 128 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F042ASJ020SC                           | 4 KB     | 1 KB    | 128 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F042AHJ020SC                           | 4 KB     | 1 KB    | 128 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F042APJ020SC                           | 4 KB     | 1 KB    | 128 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperatur                      | e: -40 ° | C to 10 | 5 °C  |           |            |                     |                     |                |            |                    |                     |

| Z8F042APB020EC                           | 4 KB     | 1 KB    | 128 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F042AQB020EC                           | 4 KB     | 1 KB    | 128 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F042ASB020EC                           | 4 KB     | 1 KB    | 128 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F042ASH020EC                           | 4 KB     | 1 KB    | 128 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F042AHH020EC                           | 4 KB     | 1 KB    | 128 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F042APH020EC                           | 4 KB     | 1 KB    | 128 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F042ASJ020EC                           | 4 KB     | 1 KB    | 128 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F042AHJ020EC                           | 4 KB     | 1 KB    | 128 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F042APJ020EC                           | 4 KB     | 1 KB    | 128 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging |          |         |       |           |            |                     |                     |                |            |                    |                     |

Z8 Encore! XP<sup>®</sup> F082A Series | **Product Specification**

| 25 |

|----|

| Part Number                              | Flash     | RAM      | SUVN   | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|------------------------------------------|-----------|----------|--------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082          | A Serie   | s with 1 | KB Fla | ish       |            |                     |                     |                |            |                    |                     |

| Standard Temperature: 0 °C to 70 °C      |           |          |        |           |            |                     |                     |                |            |                    |                     |

| Z8F011APB020SC                           | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F011AQB020SC                           | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F011ASB020SC                           | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F011ASH020SC                           | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F011AHH020SC                           | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F011APH020SC                           | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F011ASJ020SC                           | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F011AHJ020SC                           | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F011APJ020SC                           | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperatur                      | re: -40 ° | C to 10  | 5 °C   |           |            |                     |                     |                |            |                    |                     |

| Z8F011APB020EC                           | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F011AQB020EC                           | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F011ASB020EC                           | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F011ASH020EC                           | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F011AHH020EC                           | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F011APH020EC                           | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F011ASJ020EC                           | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F011AHJ020EC                           | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F011APJ020EC                           | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging |           |          |        |           |            |                     |                     |                |            |                    |                     |

Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

262

compare 85 compare - extended addressing 203 COMPARE mode 85 compare with carry 203 compare with carry - extended addressing 203 complement 205 complement carry flag 204 condition code 201 continuous conversion (ADC) 124 CONTINUOUS mode 84 control register definition, UART 108 Control Registers 15, 19 **COUNTER modes 84** CP 203 **CPC 203 CPCX 203** CPU and peripheral overview 5 CPU control instructions 204 **CPX 203** Customer Feedback Form 271

### D

DA 201, 203 data memory 17 DC characteristics 222 debugger, on-chip 173 **DEC 203** decimal adjust 203 decrement 203 decrement and jump non-zero 206 decrement word 203 **DECW 203** destination operand 202 device, port availability 37 DI 204 direct address 201 disable interrupts 204 **DJNZ 206** dst 202

### Ε

EI 204

electrical characteristics 221 ADC 231 flash memory and timing 230 GPIO input data sample timing 234 Watchdog Timer 230, 233 enable interrupt 204 ER 201 extended addressing register 201 external pin reset 27 eZ8 CPU features 5 eZ8 CPU instruction classes 202 eZ8 CPU instruction notation 200 eZ8 CPU instruction set 199 eZ8 CPU instruction summary 207

### F

FCTL register 149, 155, 156 features, Z8 Encore! 1 first opcode map 218 FLAGS 202 flags register 202 flash controller 7 option bit address space 156 option bit configuration - reset 153 program memory address 0000H 156 program memory address 0001H 158 flash memory 141 arrangement 142 byte programming 147 code protection 145 configurations 141 control register definitions 149, 155 controller bypass 148 electrical characteristics and timing 230 flash control register 149, 155, 156 flash option bits 146 flash status register 150 flow chart 144 frequency high and low byte registers 152 mass erase 147 operation 143 operation timing 145