Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 16 x 8                                                    |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f011asb020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Watchdog Timer Time-Out Response       92         Watchdog Timer Reload Unlock Sequence       93         Watchdog Timer Calibration       93         Watchdog Timer Calibration       93                                                                                       | 3<br>3                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Watchdog Timer Control Register Definitions       94         Watchdog Timer Control Register       94         Watchdog Timer Reload Upper, High and Low Byte Registers       94                                                                                                | 4                               |

| Universal Asynchronous Receiver/Transmitter                                                                                                                                                                                                                                    | 7                               |

| Architecture       97         Operation       98         Data Format       98         Transmitting Data using the Polled Method       98                                                                                                                                       | 8<br>8                          |

| Transmitting Data using the Interrupt-Driven Method       100         Receiving Data using the Polled Method       100                                                                                                                                                         | 0<br>1                          |

| Receiving Data using the Interrupt-Driven Method       102         Clear To Send (CTS) Operation       103         MULTIPROCESSOR (9-bit) Mode       103         External Driver Enable       104         UART Interrupts       104         UART Baud Rate Generator       105 | 3<br>3<br>4<br>5                |

| UART Control Register Definitions108UART Control 0 and Control 1 Registers108UART Status 0 Register112UART Status 1 Register112UART Transmit Data Register113UART Receive Data Register113UART Address Compare Register114UART Baud Rate High and Low Byte Registers114        | 8<br>8<br>1<br>2<br>3<br>3<br>4 |

| Infrared Encoder/Decoder 112                                                                                                                                                                                                                                                   | 7                               |

| Architecture       117         Operation       117         Transmitting IrDA Data       118         Receiving IrDA Data       119         Infrared Encoder Control Decistor Definitions       120                                                                              | 7<br>8<br>9                     |

| Infrared Encoder/Decoder Control Register Definitions                                                                                                                                                                                                                          |                                 |

| Analog-to-Digital Converter                                                                                                                                                                                                                                                    |                                 |

| Architecture         12           Operation         122           Data Format         122                                                                                                                                                                                      | 2                               |

vii

## **Interrupt Controller**

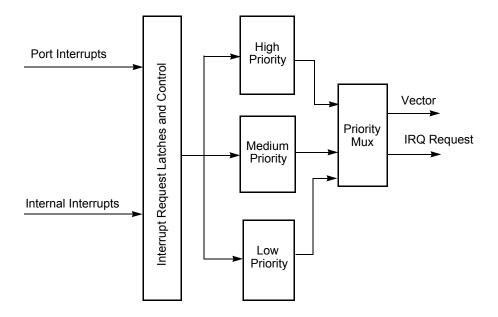

The Z8 Encore! XP<sup>®</sup> F082A Series products support up to 20 interrupts. These interrupts consist of 8 internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

## **Reset Controller**

The Z8 Encore! XP F082A Series products can be reset using the  $\overline{\text{RESET}}$  pin, Power-On Reset, Watchdog Timer (WDT) time-out, STOP mode exit, or Voltage Brownout (VBO) warning signal. The  $\overline{\text{RESET}}$  pin is bi-directional, that is, it functions as reset source as well as a reset indicator.

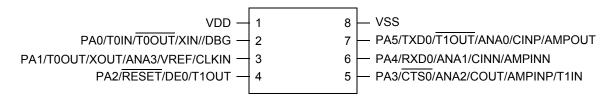

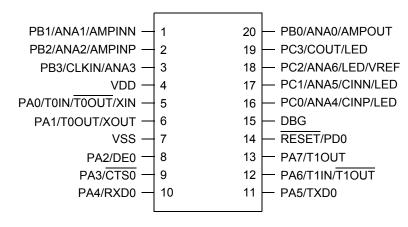

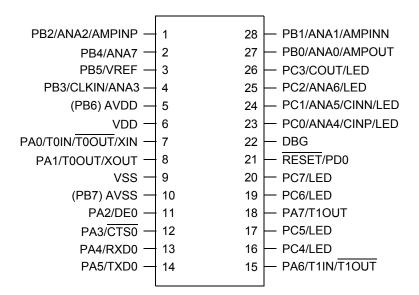

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

Figure 2. Z8F08xA, Z8F04xA, Z8F02xA, and Z8F01xA in 8-Pin SOIC, QFN/MLF-S, or PDIP Package

Figure 3. Z8F08xA, Z8F04xA, Z8F02xA, and Z8F01xA in 20-Pin SOIC, SSOP or PDIP Package

Figure 4. Z8F08xA, Z8F04xA, Z8F02xA, and Z8F01xA in 28-Pin SOIC, SSOP or PDIP Package

# Zilog <sub>19</sub>

## **Register Map**

Table 7 provides the address map for the Register File of the Z8 Encore! XP<sup>®</sup> F082A Series devices. Not all devices and package styles in the Z8 Encore! XP F082A Series support the ADC, or all of the GPIO Ports. Consider registers for unimplemented peripherals as Reserved.

#### Table 7. Register File Address Map

| Address (Hex) | Register Description              | Mnemonic      | Reset (Hex) | Page No |

|---------------|-----------------------------------|---------------|-------------|---------|

| General-Purpo | se RAM                            |               |             |         |

| Z8F082A/Z8F0  | 81A Devices                       |               |             |         |

| 000–3FF       | General-Purpose Register File RAM | _             | XX          |         |

| 400–EFF       | Reserved                          | —             | XX          |         |

| Z8F042A/Z8F0  | 41A Devices                       |               |             |         |

| 000–3FF       | General-Purpose Register File RAM | _             | XX          |         |

| 400–EFF       | Reserved                          | _             | XX          |         |

| Z8F022A/Z8F0  | 21A Devices                       |               |             |         |

| 000–1FF       | General-Purpose Register File RAM | _             | XX          |         |

| 200–EFF       | Reserved                          | —             | XX          |         |

| Z8F012A/Z8F0  | 11A Devices                       |               |             |         |

| 000–0FF       | General-Purpose Register File RAM | _             | XX          |         |

| 100–EFF       | Reserved                          | —             | XX          |         |

| Timer 0       |                                   |               |             |         |

| F00           | Timer 0 High Byte                 | T0H           | 00          | 87      |

| F01           | Timer 0 Low Byte                  | TOL           | 01          | 87      |

| F02           | Timer 0 Reload High Byte          | T0RH          | FF          | 88      |

| F03           | Timer 0 Reload Low Byte           | T0RL          | FF          | 88      |

| F04           | Timer 0 PWM High Byte             | T0PWMH        | 00          | 88      |

| F05           | Timer 0 PWM Low Byte              | <b>T0PWML</b> | 00          | 89      |

| F06           | Timer 0 Control 0                 | TOCTLO        | 00          | 83      |

| F07           | Timer 0 Control 1                 | T0CTL1        | 00          | 84      |

| Timer 1       |                                   |               |             |         |

| F08           | Timer 1 High Byte                 | T1H           | 00          | 87      |

| F09           | Timer 1 Low Byte                  | T1L           | 01          | 87      |

| F0A           | Timer 1 Reload High Byte          | T1RH          | FF          | 88      |

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source       |

|----------|-------------------------------------|--------------------------------|

|          | 0034H                               | Port C Pin 1, both input edges |

| Lowest   | 0036H                               | Port C Pin 0, both input edges |

|          | 0038H                               | Reserved                       |

#### Table 32. Trap and Interrupt Vectors in Order of Priority (Continued)

## Architecture

Figure 8 displays the interrupt controller block diagram.

Figure 8. Interrupt Controller Block Diagram

## Operation

## **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control register globally enables and disables interrupts.

U0RXI—UART 0 Receiver Interrupt Request

0 = No interrupt request is pending for the UART 0 receiver.

1 = An interrupt request from the UART 0 receiver is awaiting service.

U0TXI-UART 0 Transmitter Interrupt Request

0 = No interrupt request is pending for the UART 0 transmitter.

1 = An interrupt request from the UART 0 transmitter is awaiting service.

ADCI—ADC Interrupt Request

0 = No interrupt request is pending for the analog-to-digital Converter.

1 = An interrupt request from the Analog-to-Digital Converter is awaiting service.

## **Interrupt Request 1 Register**

The Interrupt Request 1 (IRQ1) register (Table 34) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ1 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 1 register to determine if any interrupt requests are pending.

| BITS  | 7     | 6     | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |

|-------|-------|-------|------|------|------|------|------|------|--|--|--|

| FIELD | PA7VI | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |  |  |  |

| RESET | 0     | 0     | 0    | 0    | 0    | 0    | 0    | 0    |  |  |  |

| R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |  |  |

| ADDR  |       | FC3H  |      |      |      |      |      |      |  |  |  |

Table 34. Interrupt Request 1 Register (IRQ1)

PA7*V*I—Port A Pin 7 or LVD Interrupt Request

0 = No interrupt request is pending for GPIO Port A or LVD.

1 = An interrupt request from GPIO Port A or LVD.

PA6CI—Port A Pin 6 or Comparator Interrupt Request

0 = No interrupt request is pending for GPIO Port A or Comparator.

1 = An interrupt request from GPIO Port A or Comparator.

PAxI—Port A Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port A pin *x*.

1 = An interrupt request from GPIO Port A pin x is awaiting service.

where x indicates the specific GPIO Port pin number (0–5).

62

## Interrupt Request 2 Register

The Interrupt Request 2 (IRQ2) register (Table 35) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 register to determine if any interrupt requests are pending.

#### Table 35. Interrupt Request 2 Register (IRQ2)

| BITS  | 7   | 6    | 5     | 4   | 3    | 2    | 1    | 0    |

|-------|-----|------|-------|-----|------|------|------|------|

| FIELD |     | Rese | erved |     | PC3I | PC2I | PC1I | PC0I |

| RESET | 0   | 0    | 0     | 0   | 0    | 0    | 0    | 0    |

| R/W   | R/W | R/W  | R/W   | R/W | R/W  | R/W  | R/W  | R/W  |

| ADDR  |     |      |       | FC  | 6H   |      |      |      |

Reserved—Must be 0.

PCxI—Port C Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port C pin x.

1 = An interrupt request from GPIO Port C pin x is awaiting service.

where x indicates the specific GPIO Port C pin number (0-3).

## **IRQ0 Enable High and Low Bit Registers**

Table 36 describes the priority control for IRQ0. The IRQ0 Enable High and Low Bit registers (Table 37 and Table 38) form a priority encoded enabling for interrupts in the Interrupt Request 0 register.

#### Table 36. IRQ0 Enable and Priority Encoding

| IRQ0ENH[x] | IRQ0ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Medium      |

| 1          | 1          | Level 3  | High        |

where x indicates the register bits from 0–7.

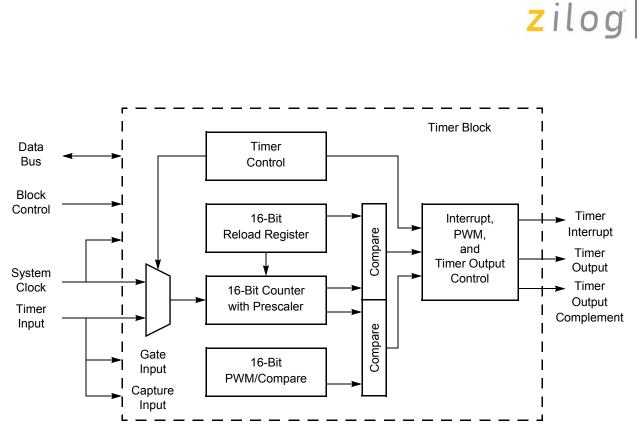

Figure 9. Timer Block Diagram

## Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

## **Timer Operating Modes**

The timers can be configured to operate in the following modes:

#### **ONE-SHOT Mode**

In ONE-SHOT mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. The timer is automatically disabled and stops counting.

70

Z8 Encore! XP<sup>®</sup> F082A Series

**Product Specification**

zilog<sup>°</sup>

duration of the negative phase of the PWM signal (as defined by the difference between the PWM registers and the Timer Reload registers).

- 5. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM period). The Reload value must be greater than the PWM value.

- 6. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 7. Configure the associated GPIO port pin for the Timer Output and Timer Output Complement alternate functions. The Timer Output Complement function is shared with the Timer Input function for both timers. Setting the timer mode to Dual PWM automatically switches the function from Timer In to Timer Out Complement.

- 8. Write to the Timer Control register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

PWM Period (s) = Reload Value xPrescale System Clock Frequency (Hz)

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT mode equation determines the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{PWM Value}}{\text{Reload Value}} \times 100$

#### **CAPTURE Mode**

In CAPTURE mode, the current timer count value is recorded when the appropriate external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte Registers. The timer input is the system clock. The TPOL bit in the Timer Control register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in TxCTL0 register is set to indicate the timer interrupt is because of an input capture event.

The timer continues counting up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt and continues counting. The INPCAP bit in TxCTL0 register clears indicating the timer interrupt is not because of an input capture event.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In CAPTURE/COMPARE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

### **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte register is read, the contents of the Timer Low Byte register are placed in a holding register. A subsequent read from the Timer Low Byte register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte register returns the actual value in the counter.

## **Timer Pin Signal Operation**

Timer Output is a GPIO Port pin alternate function. The Timer Output is toggled every time the counter is reloaded.

The Timer Input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function Registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

110 = 64 cycles delay 111 = 128 cycles delay

INPCAP—Input Capture Event

This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.

0 = Previous timer interrupt is not a result of Timer Input Capture Event

1 = Previous timer interrupt is a result of Timer Input Capture Event

#### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode (Table 49).

Table 49. Timer 0–1 Control Register 1 (TxCTL1)

| BITS  | 7   | 6    | 5   | 4     | 3    | 2           | 1 | 0 |  |  |

|-------|-----|------|-----|-------|------|-------------|---|---|--|--|

| FIELD | TEN | TPOL |     | PRES  |      | TMODE       |   |   |  |  |

| RESET | 0   | 0    | 0   | 0     | 0    | 0           | 0 | 0 |  |  |

| R/W   | R/W | R/W  | R/W | R/W   | R/W  | R/W R/W R/W |   |   |  |  |

| ADDR  |     |      |     | F07H, | F0FH |             |   |   |  |  |

TEN-Timer Enable

0 = Timer is disabled.

1 = Timer enabled to count.

TPOL—Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer.

#### **ONE-SHOT mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **CONTINUOUS mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### COUNTER mode

If the timer is enabled the Timer Output signal is complemented after timer reload.

0 = Count occurs on the rising edge of the Timer Input signal.

1 = Count occurs on the falling edge of the Timer Input signal.

## **Analog-to-Digital Converter**

The analog-to-digital converter (ADC) converts an analog input signal to its digital representation. The features of this sigma-delta ADC include:

- 11-bit resolution in DIFFERENTIAL mode.

- 10-bit resolution in SINGLE-ENDED mode.

- Eight single-ended analog input sources are multiplexed with general-purpose I/O ports.

- 9<sup>th</sup> analog input obtained from temperature sensor peripheral.

- 11 pairs of differential inputs also multiplexed with general-purpose I/O ports.

- Low-power operational amplifier (LPO).

- Interrupt on conversion complete.

- Bandgap generated internal voltage reference with two selectable levels.

- Manual in-circuit calibration is possible employing user code (offset calibration).

- Factory calibrated for in-circuit error compensation.

## Architecture

Figure 19 displays the major functional blocks of the ADC. An analog multiplexer network selects the ADC input from the available analog pins, ANA0 through ANA7.

The input stage of the ADC allows both differential gain and buffering. The following input options are available:

- Unbuffered input (SINGLE-ENDED and DIFFERENTIAL modes).

- Buffered input with unity gain (SINGLE-ENDED and DIFFERENTIAL modes).

- LPO output with full pin access to the feedback path.

zilog | 177

The Auto-Baud Detector/Generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous datastreams, the maximum recommended baud rate is the system clock frequency divided by 8. The maximum possible baud rate for asynchronous datastreams is the system clock frequency divided by 4, but this theoretical maximum is possible only for low noise designs with clean signals. Table 105 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock<br>Frequency (MHz) | Recommended Maximum<br>Baud Rate (Kbps) | Recommended<br>Standard PC<br>Baud Rate (bps) | Minimum Baud<br>Rate (Kbps) |

|---------------------------------|-----------------------------------------|-----------------------------------------------|-----------------------------|

| 20.0                            | 2500.0                                  | 1,843,200                                     | 39                          |

| 1.0                             | 125.0                                   | 115,200                                       | 1.95                        |

| 0.032768 (32 kHz)               | 4.096                                   | 2,400                                         | 0.064                       |

#### Table 105. OCD Baud-Rate Limits

If the OCD receives a Serial Break (nine or more continuous bits Low) the Auto-Baud Detector/Generator resets. Reconfigure the Auto-Baud Detector/Generator by sending 80H.

### **OCD Serial Errors**

The On-Chip Debugger can detect any of the following error conditions on the DBG pin:

- Serial Break (a minimum of nine continuous bits Low)

- Framing Error (received Stop bit is Low)

- Transmit Collision (OCD and host simultaneous transmission detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long Serial Break back to the host, and resets the Auto-Baud Detector/Generator. A Framing Error or Transmit Collision may be caused by the host sending a Serial Break to the OCD. Because of the open-drain nature of the interface, returning a Serial Break break back to the host only extends the length of the Serial Break if the host releases the Serial Break early.

The host transmits a Serial Break on the DBG pin when first connecting to the Z8 Encore! XP F082A Series devices or when recovering from an error. A Serial Break from the host resets the Auto-Baud Generator/Detector but does not reset the OCD Control register. A Serial Break leaves the device in DEBUG mode if that is the current mode. The OCD is held in Reset until the end of the Serial Break when the DBG pin returns

191

WDFEN-Watchdog Timer Oscillator Failure Detection Enable

1 = Failure detection of Watchdog Timer oscillator is enabled

0 = Failure detection of Watchdog Timer oscillator is disabled

SCKSEL—System Clock Oscillator Select

000 = Internal precision oscillator functions as system clock at 5.53 MHz

001 = Internal precision oscillator functions as system clock at 32 kHz

010 = Crystal oscillator or external RC oscillator functions as system clock

011 = Watchdog Timer oscillator functions as system

100 = External clock signal on PB3 functions as system clock

101 = Reserved

110 = Reserved

111 = Reserved

**z**ilog<sup>°</sup>

208

| Assembly             | Symbolic                                                                                  | Addres     | s Mode   | Opcode(s) | s) Flags |          |   |           |   |   | Fetch  | Instr. |

|----------------------|-------------------------------------------------------------------------------------------|------------|----------|-----------|----------|----------|---|-----------|---|---|--------|--------|

| Mnemonic             | Operation                                                                                 | dst        | src      | (Hex)     | С        | Ζ        | S | ۷         | D | Н | Cycles |        |

| AND dst, src         | $dst \gets dst \; AND \; src$                                                             | r          | r        | 52        | -        | *        | * | 0         | - | - | 2      | 3      |

|                      |                                                                                           | r          | Ir       | 53        | -        |          |   |           |   |   | 2      | 4      |

|                      |                                                                                           | R          | R        | 54        | -        |          |   |           |   |   | 3      | 3      |

|                      |                                                                                           | R          | IR       | 55        | -        |          |   |           |   |   | 3      | 4      |

|                      |                                                                                           | R          | IM       | 56        | -        |          |   |           |   |   | 3      | 3      |

|                      |                                                                                           | IR         | IM       | 57        | -        |          |   |           |   |   | 3      | 4      |

| ANDX dst, src        | $dst \gets dst \ AND \ src$                                                               | ER         | ER       | 58        | -        | *        | * | 0         | _ | - | 4      | 3      |

|                      |                                                                                           | ER         | IM       | 59        | -        |          |   |           |   |   | 4      | 3      |

| ATM                  | Block all interrupt and<br>DMA requests during<br>execution of the next 3<br>instructions |            |          | 2F        | -        | _        | _ | _         | _ | _ | 1      | 2      |

| BCLR bit, dst        | $dst[bit] \leftarrow 0$                                                                   | r          |          | E2        | -        | -        | _ | _         | - | - | 2      | 2      |

| BIT p, bit, dst      | $dst[bit] \leftarrow p$                                                                   | r          |          | E2        | -        | -        | - | _         | _ | _ | 2      | 2      |

| BRK                  | Debugger Break                                                                            |            |          | 00        | -        | -        | - | -         | - | - | 1      | 1      |

| BSET bit, dst        | $dst[bit] \leftarrow 1$                                                                   | r          |          | E2        | -        | -        | _ | _         | - | - | 2      | 2      |

| BSWAP dst            | $dst[7:0] \leftarrow dst[0:7]$                                                            | R          |          | D5        | Х        | *        | * | 0         | _ | - | 2      | 2      |

| BTJ p, bit, src, dst |                                                                                           |            | r        | F6        | -        | -        | - | -         | - | - | 3      | 3      |

|                      | $PC \gets PC + X$                                                                         |            | lr       | F7        | -        |          |   |           |   |   | 3      | 4      |

| BTJNZ bit, src, dst  |                                                                                           |            | r        | F6        | -        | -        | _ | _         | _ | - | 3      | 3      |

|                      | $PC \leftarrow PC + X$                                                                    |            | lr       | F7        | -        |          |   |           |   |   | 3      | 4      |

| BTJZ bit, src, dst   | if src[bit] = 0                                                                           |            | r        | F6        | -        | -        | - | -         | - | - | 3      | 3      |

|                      | $PC \leftarrow PC + X$                                                                    |            | lr       | F7        | -        |          |   |           |   |   | 3      | 4      |

| CALL dst             | $SP \leftarrow SP - 2$                                                                    | IRR        |          | D4        | -        | _        | _ | _         | _ | - | 2      | 6      |

|                      | $\begin{array}{l} @SP \leftarrow PC \\ PC \leftarrow dst \end{array}$                     | DA         |          | D6        | -        |          |   |           |   |   | 3      | 3      |

| CCF                  | $C \leftarrow \sim C$                                                                     |            |          | EF        | *        | _        | _ | _         | _ |   | 1      | 2      |

| CLR dst              | $dst \gets 00H$                                                                           | R          |          | B0        | -        | -        | _ | _         | - | - | 2      | 2      |

|                      |                                                                                           | IR         |          | B1        | -        |          |   |           |   |   | 2      | 3      |

| Flags Notation:      | * = Value is a function of<br>– = Unaffected<br>X = Undefined                             | the result | of the o | peration. |          | Re<br>Se |   | to (<br>1 | ) |   |        |        |

## Table 124. eZ8 CPU Instruction Summary (Continued)

223

|                   |                               |         | T <sub>A</sub> = -40 °C to +105 °C<br>(unless otherwise specified) |            |       |                                                                                 |

|-------------------|-------------------------------|---------|--------------------------------------------------------------------|------------|-------|---------------------------------------------------------------------------------|

| Symbol            | Parameter                     | Minimum | Typical                                                            | Maximum    | Units | Conditions                                                                      |

| V <sub>OL2</sub>  | Low Level Output<br>Voltage   | -       | -                                                                  | 0.6        | V     | I <sub>OL</sub> = 20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.  |

| V <sub>OH2</sub>  | High Level Output<br>Voltage  | 2.4     | _                                                                  | -          | V     | I <sub>OH</sub> = -20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled. |

| I <sub>IH</sub>   | Input Leakage<br>Current      | -       | <u>+</u> 0.002                                                     | <u>+</u> 5 | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V;$                                          |

| IIL               | Input Leakage<br>Current      | -       | <u>+</u> 0.007                                                     | <u>+</u> 5 | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3 V;$                                          |

| I <sub>TL</sub>   | Tristate Leakage<br>Current   | -       | _                                                                  | <u>+</u> 5 | μA    |                                                                                 |

| I <sub>LED</sub>  | Controlled Current            | 1.8     | 3                                                                  | 4.5        | mA    | {AFS2,AFS1} = {0,0}                                                             |

|                   | Drive                         | 2.8     | 7                                                                  | 10.5       | mA    | {AFS2,AFS1} = {0,1}                                                             |

|                   |                               | 7.8     | 13                                                                 | 19.5       | mA    | {AFS2,AFS1} = {1,0}                                                             |

|                   |                               | 12      | 20                                                                 | 30         | mA    | {AFS2,AFS1} = {1,1}                                                             |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance  | -       | 8.0 <sup>2</sup>                                                   | -          | pF    |                                                                                 |

| C <sub>XIN</sub>  | XIN Pad<br>Capacitance        | -       | 8.0 <sup>2</sup>                                                   | _          | pF    |                                                                                 |

| C <sub>XOUT</sub> | XOUT Pad<br>Capacitance       | -       | 9.5 <sup>2</sup>                                                   | _          | pF    |                                                                                 |

| I <sub>PU</sub>   | Weak Pull-up<br>Current       | 30      | 100                                                                | 350        | μA    | V <sub>DD</sub> = 3.0 V–3.6 V                                                   |

| V <sub>RAM</sub>  | RAM Data<br>Retention Voltage | TBD     |                                                                    |            | V     | Voltage at which RAM retains static values; no reading or writing is allowed.   |

|                   |                               |         | -                                                                  |            | -     |                                                                                 |

#### Table 127. DC Characteristics (Continued)

#### Notes

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

230

|                                               | $T_A = -$ | = 2.7 V to<br>40 °C to +<br>otherwis | 105 °C  |        |                                                                                                                                                                   |

|-----------------------------------------------|-----------|--------------------------------------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                     | Minimum   | Typical                              | Maximum | Units  | Notes                                                                                                                                                             |

| Flash Byte Read Time                          | 100       | -                                    | -       | ns     |                                                                                                                                                                   |

| Flash Byte Program Time                       | 20        | _                                    | 40      | μs     |                                                                                                                                                                   |

| Flash Page Erase Time                         | 10        | -                                    | -       | ms     |                                                                                                                                                                   |

| Flash Mass Erase Time                         | 200       | -                                    | -       | ms     |                                                                                                                                                                   |

| Writes to Single Address<br>Before Next Erase | -         | _                                    | 2       |        |                                                                                                                                                                   |

| Flash Row Program Time                        | -         | -                                    | 8       | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This<br>parameter is only an issue<br>when bypassing the Flash<br>Controller. |

| Data Retention                                | 100       | _                                    | _       | years  | 25 °C                                                                                                                                                             |

| Endurance                                     | 10,000    | _                                    | _       | cycles | Program/erase cycles                                                                                                                                              |

#### Table 132. Flash Memory Electrical Characteristics and Timing

#### Table 133. Watchdog Timer Electrical Characteristics and Timing

| V <sub>DD</sub> = 2.7 V to 3.6 V   |  |

|------------------------------------|--|

| T <sub>A</sub> = -40 °C to +105 °C |  |

| (unless otherwise stated)          |  |

| Symbol              | Parameter                | Minimum | Typical | Maximum     | Units | Conditions                                                      |

|---------------------|--------------------------|---------|---------|-------------|-------|-----------------------------------------------------------------|

| F <sub>WDT</sub>    | WDT Oscillator Frequency |         | 10      |             | kHz   |                                                                 |

| F <sub>WDT</sub>    | WDT Oscillator Error     |         |         | <u>+</u> 50 | %     |                                                                 |

| T <sub>WDTCAL</sub> | WDT Calibrated Timeout   | 0.98    | 1       | 1.02        | S     | V <sub>DD</sub> = 3.3 V;<br>T <sub>A</sub> = 30 °C              |

|                     |                          | 0.70    | 1       | 1.30        | S     | $V_{DD}$ = 2.7 V to 3.6 V<br>T <sub>A</sub> = 0 °C to 70 °C     |

|                     |                          | 0.50    | 1       | 1.50        | S     | $V_{DD}$ = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C |

zilog

232

|                |                                      | $T_A =$ | = 3.0 V to<br>0 °C to +<br>otherwis | 70 °C                |                           |                                                                                                                                                                                                                                |  |

|----------------|--------------------------------------|---------|-------------------------------------|----------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol         | Parameter                            | Minimum | Typical                             | Maximum              | Units                     | Conditions                                                                                                                                                                                                                     |  |

|                | Single-Shot Conversion<br>Time       | -       | 5129                                | -                    | System<br>clock<br>cycles | All measurements but temperature sensor                                                                                                                                                                                        |  |

|                |                                      |         | 10258                               |                      |                           | Temperature sensor<br>measurement                                                                                                                                                                                              |  |

|                | Continuous Conversion<br>Time        | _       | 256                                 | _                    | System<br>clock<br>cycles | All measurements but temperature sensor                                                                                                                                                                                        |  |

|                |                                      |         | 512                                 |                      |                           | Temperature sensor<br>measurement                                                                                                                                                                                              |  |

|                | Signal Input Bandwidth               | _       | 10                                  |                      | kHz                       | As defined by -3 dB point                                                                                                                                                                                                      |  |

| R <sub>S</sub> | Analog Source Impedance <sup>4</sup> | _       | _                                   | 10                   | kΩ                        | In unbuffered mode                                                                                                                                                                                                             |  |

|                |                                      |         |                                     | 500                  | kΩ                        | In buffered modes                                                                                                                                                                                                              |  |

| Zin            | Input Impedance                      | -       | 150                                 |                      | kΩ                        | In unbuffered mode at 20 $\rm MHz^5$                                                                                                                                                                                           |  |

|                |                                      | 10      | _                                   |                      | MΩ                        | In buffered modes                                                                                                                                                                                                              |  |

| Vin            | Input Voltage Range                  | 0       |                                     | V <sub>DD</sub>      | V                         | Unbuffered Mode                                                                                                                                                                                                                |  |

|                |                                      | 0.3     |                                     | V <sub>DD</sub> -1.1 | V                         | Buffered Modes                                                                                                                                                                                                                 |  |

|                |                                      |         |                                     | •                    | Note:                     | These values define the<br>range over which the<br>ADC performs within<br>spec; exceeding these<br>values does not cause<br>damage or instability; see<br>DC Characteristics on<br>page 222 for absolute pin<br>voltage limits |  |

#### Table 135. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

#### Notes

- 1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

- 2. Devices are factory calibrated at  $V_{DD}$  = 3.3 V and  $T_A$  = +30 °C, so the ADC is maximally accurate under these conditions.

- 3. LSBs are defined assuming 10-bit resolution.

- 4. This is the maximum recommended resistance seen by the ADC input pin.

- 5. The input impedance is inversely proportional to the system clock frequency.

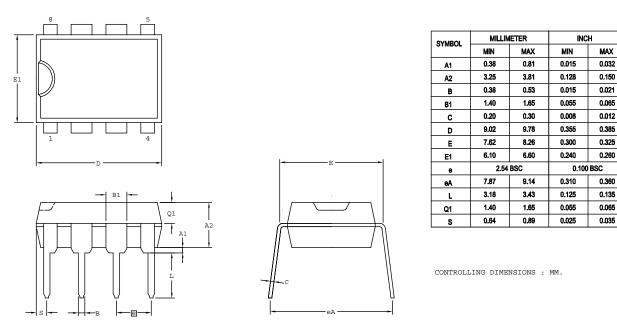

## Packaging

Figure 39 displays the 8-pin Plastic Dual Inline Package (PDIP) available for Z8 Encore!  $XP^{\textcircled{R}}$  F082A Series devices.

Figure 39. 8-Pin Plastic Dual Inline Package (PDIP)

zilog 257

| Part Number                     | Flash     | RAM      | SUVN   | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------|-----------|----------|--------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082 | A Serie   | s with 1 | KB Fla | ish, 1    | 0-Bit      | Ana                 | log-t               | o-Dig          | jital C    | Conv               | verter              |

| Standard Temperatu              | re: 0 °C  | to 70 °C | ;      |           |            |                     |                     |                |            |                    |                     |

| Z8F012APB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperatu              | re: -40 ° | C to 10  | 5 °C   |           |            |                     |                     |                |            |                    |                     |

| Z8F012APB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |