# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |  |  |  |

|----------------------------|-----------------------------------------------------------|--|--|--|

| Core Processor             | eZ8                                                       |  |  |  |

| Core Size                  | 8-Bit                                                     |  |  |  |

| Speed                      | 20MHz                                                     |  |  |  |

| Connectivity               | IrDA, UART/USART                                          |  |  |  |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |  |  |  |

| Number of I/O              | 17                                                        |  |  |  |

| Program Memory Size        | 1KB (1K x 8)                                              |  |  |  |

| Program Memory Type        | FLASH                                                     |  |  |  |

| EEPROM Size                | 16 x 8                                                    |  |  |  |

| RAM Size                   | 256 x 8                                                   |  |  |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |  |  |

| Data Converters            | -                                                         |  |  |  |

| Oscillator Type            | Internal                                                  |  |  |  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |  |  |  |

| Mounting Type              | Surface Mount                                             |  |  |  |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |  |  |  |

| Supplier Device Package    | -                                                         |  |  |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f011ash020sc |  |  |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# zilog <sub>3</sub>

| Part<br>Number | Flash<br>(KB) | RAM<br>(B) | NVDS <sup>1</sup><br>(B) | I/O  | Comparator | Advanced<br>Analog <sup>2</sup> | ADC<br>Inputs | Packages           |

|----------------|---------------|------------|--------------------------|------|------------|---------------------------------|---------------|--------------------|

| Z8F082A        | 8             | 1024       | 0                        | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F081A        | 8             | 1024       | 0                        | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F042A        | 4             | 1024       | 128                      | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F041A        | 4             | 1024       | 128                      | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F022A        | 2             | 512        | 64                       | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F021A        | 2             | 512        | 64                       | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F012A        | 1             | 256        | 16                       | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F011A        | 1             | 256        | 16                       | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pir |

Table 1. Z8 Encore! XP<sup>®</sup> F082A Series Family Part Selection Guide

<sup>1</sup>Non-volatile data storage.

<sup>2</sup>Advanced Analog includes ADC, temperature sensor, and low-power operational amplifier.

addresses outside the available Flash memory addresses returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 5 describes the Program Memory Maps for the Z8 Encore! XP F082A Series products.

| Program Memory Address (Hex) | Function                     |

|------------------------------|------------------------------|

| Z8F082A and Z8F081A Products |                              |

| 0000–0001                    | Flash Option Bits            |

| 0002–0003                    | Reset Vector                 |

| 0004–0005                    | WDT Interrupt Vector         |

| 0006–0007                    | Illegal Instruction Trap     |

| 0008–0037                    | Interrupt Vectors*           |

| 0038–0039                    | Reserved                     |

| 003A-003D                    | Oscillator Fail Trap Vectors |

| 003E-1FFF                    | Program Memory               |

| Z8F042A and Z8F041A Products |                              |

| 0000–0001                    | Flash Option Bits            |

| 0002–0003                    | Reset Vector                 |

| 0004–0005                    | WDT Interrupt Vector         |

| 0006–0007                    | Illegal Instruction Trap     |

| 0008–0037                    | Interrupt Vectors*           |

| 0038–0039                    | Reserved                     |

| 003A-003D                    | Oscillator Fail Trap Vectors |

| 003E-0FFF                    | Program Memory               |

Table 5. Z8 Encore! XP F082A Series Program Memory Maps

16

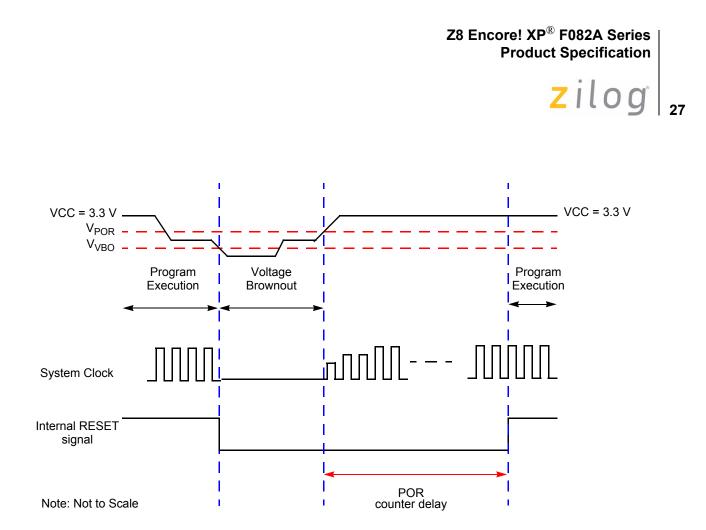

Figure 6. Voltage Brownout Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a Power-On Reset after recovering from a VBO condition.

# Watchdog Timer Reset

If the device is in NORMAL or HALT mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash Option Bit is programmed to 1. This is the unprogrammed state of the WDT\_RES Flash Option Bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT bit in the Reset Status (RSTSTAT) register is set to signify that the reset was initiated by the Watchdog Timer.

# **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system clock and reset signals, the required reset duration may be as short as three clock periods

PA0 and PA6 contain two different timer functions, a timer input and a complementary timer output. Both of these functions require the same GPIO configuration, the selection between the two is based on the timer mode. See Timers on page 69 for more details.

**Caution:** For pin with multiple alternate functions, it is recommended to write to the AFS1 and AFS2 sub-registers before enabling the alternate function via the AF sub-register. This prevents spurious transitions through unwanted alternate function modes.

# **Direct LED Drive**

The Port C pins provide a current sinked output capable of driving an LED without requiring an external resistor. The output sinks current at programmable levels of 3 mA, 7 mA, 13 mA and 20 mA. This mode is enabled through the Alternate Function sub-register AFS1 and is programmable through the LED control registers. The LED Drive Enable (LEDEN) register turns on the drivers. The LED Drive Level (LEDLVLH and LEDLVLL) registers select the sink current.

For correct function, the LED anode must be connected to  $V_{DD}$  and the cathode to the GPIO pin. Using all Port C pins in LED drive mode with maximum current may result in excessive total current. See Electrical Characteristics on page 221 for the maximum total current for the applicable package.

# **Shared Reset Pin**

On the 20- and 28-pin devices, the PD0 pin shares function with a bi-directional reset pin. Unlike all other I/O pins, this pin does not default to GPIO function on power-up. This pin acts as a bi-directional reset until the software re-configures it. The PD0 pin is output-only when in GPIO mode.

On the 8-pin product versions, the reset pin is shared with PA2, but the pin is not limited to output-only when in GPIO mode.

PS022825-0908

**Caution:** If PA2 on the 8-pin product is reconfigured as an input, ensure that no external stimulus drives the pin low during any reset sequence. Since PA2 returns to its RESET alternate function during system resets, driving it Low holds the chip in a reset state until the pin is released.

# **Shared Debug Pin**

On the 8-pin version of this device only, the Debug pin shares function with the PA0 GPIO pin. This pin performs as a general purpose input pin on power-up, but the debug logic monitors this pin during the reset sequence to determine if the unlock sequence occurs. If the unlock sequence is present, the debug function is unlocked and the pin no longer func-

zilog

50

during STOP mode do not initiate Stop Mode Recovery.

1 = The Port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP mode initiates Stop Mode Recovery.

### Port A–D Pull-up Enable Sub-Registers

The Port A–D Pull-up Enable sub-register (Table 24) is accessed through the Port A–D Control register by writing 06H to the Port A–D Address register. Setting the bits in the Port A–D Pull-up Enable sub-registers enables a weak internal resistive pull-up on the specified Port pins.

### Table 24. Port A–D Pull-Up Enable Sub-Registers (PxPUE)

| BITS  | 7        | 6                                                           | 5           | 4             | 3             | 2             | 1            | 0        |

|-------|----------|-------------------------------------------------------------|-------------|---------------|---------------|---------------|--------------|----------|

| FIELD | PPUE7    | PPUE6                                                       | PPUE5       | PPUE4         | PPUE3         | PPUE2         | PPUE1        | PPUE0    |

| RESET |          | 00H (Ports A-C); 01H (Port D); 04H (Port A of 8-pin device) |             |               |               |               |              |          |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W                                 |             |               |               |               |              |          |

| ADDR  | lf 06H i | n Port A–D /                                                | Address Reg | gister, acces | sible through | n the Port A- | -D Control F | Register |

PPUE[7:0]—Port Pull-up Enabled

0 = The weak pull-up on the Port pin is disabled.

1 = The weak pull-up on the Port pin is enabled.

### Port A–D Alternate Function Set 1 Sub-Registers

The Port A–D Alternate Function Set1 sub-register (Table 25) is accessed through the Port A–D Control register by writing 07H to the Port A–D Address register. The Alternate Function Set 1 sub-registers selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register are defined in GPIO Alternate Functions on page 38.

**Note:** Alternate function selection on port pins must also be enabled as described in Port A–D Alternate Function Sub-Registers on page 47.

### Table 25. Port A–D Alternate Function Set 1 Sub-Registers (PxAFS1)

| BITS  | 7                                                                                     | 6                           | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---------------------------------------------------------------------------------------|-----------------------------|--------|--------|--------|--------|--------|--------|

| FIELD | PAFS17                                                                                | PAFS16                      | PAFS15 | PAFS14 | PAFS13 | PAFS12 | PAFS11 | PAFS10 |

| RESET | 0                                                                                     | 0                           | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W   | R/W                                                                                   | R/W R/W R/W R/W R/W R/W R/W |        |        |        |        |        |        |

| ADDR  | If 07H in Port A–D Address Register, accessible through the Port A–D Control Register |                             |        |        |        |        |        |        |

# Table 46. Shared Interrupt Select Register (IRQSS)

| BITS  | 7     | 6     | 5                   | 4  | 3  | 2 | 1 | 0 |

|-------|-------|-------|---------------------|----|----|---|---|---|

| FIELD | PA7VS | PA6CS | Reserved            |    |    |   |   |   |

| RESET | 0     | 0     | 0 0 0 0 0 0         |    |    |   |   |   |

| R/W   | R/W   | R/W   | R/W R/W R/W R/W R/W |    |    |   |   |   |

| ADDR  |       |       |                     | FC | EH |   |   |   |

PA7VS—PA7/LVD Selection

0 = PA7 is used for the interrupt for PA7VS interrupt request.

1 = The LVD is used for the interrupt for PA7VS interrupt request.

PA6CS—PA6/Comparator Selection

0 = PA6 is used for the interrupt for PA6CS interrupt request.

1 = The Comparator is used for the interrupt for PA6CS interrupt request.

Reserved—Must be 0.

# **Interrupt Control Register**

The Interrupt Control (IRQCTL) register (Table 47) contains the master enable bit for all interrupts.

| Table 47. | Interrupt | Control | Register | (IRQCTL) |

|-----------|-----------|---------|----------|----------|

|-----------|-----------|---------|----------|----------|

| BITS  | 7    | 6        | 5             | 4  | 3  | 2 | 1 | 0 |

|-------|------|----------|---------------|----|----|---|---|---|

| FIELD | IRQE | Reserved |               |    |    |   |   |   |

| RESET | 0    | 0        | 0 0 0 0 0 0 0 |    |    |   |   |   |

| R/W   | R/W  | R        | R R R R R R R |    |    |   |   |   |

| ADDR  |      |          |               | FC | FH |   |   |   |

IRQE—Interrupt Request Enable

This bit is set to 1 by executing an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, Reset or by a direct register write of a 0 to this bit.

- 0 = Interrupts are disabled.

- 1 = Interrupts are enabled.

Reserved—Must be 0.

Follow the steps below for configuring a timer for COUNTER mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for COUNTER mode.

- Select either the rising edge or falling edge of the Timer Input signal for the count. This selection also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER mode. After the first timer Reload in COUNTER mode, counting always begins at the reset value of 0001H. In COUNTER mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer.

In COUNTER mode, the number of Timer Input transitions since the timer start is given by the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value-Start Value

### **COMPARATOR COUNTER Mode**

In COMPARATOR COUNTER mode, the timer counts input transitions from the analog comparator output. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the comparator output signal. In COMPAR-ATOR COUNTER mode, the prescaler is disabled.

**Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the comparator output signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

After reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

89

| BITS  | 7   | 6                           | 5 | 4     | 3    | 2 | 1 | 0 |  |

|-------|-----|-----------------------------|---|-------|------|---|---|---|--|

| FIELD |     | PWML                        |   |       |      |   |   |   |  |

| RESET | 0   | 0 0 0 0 0 0 0 0             |   |       |      |   |   |   |  |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |       |      |   |   |   |  |

| ADDR  |     |                             |   | F05H, | F0DH |   |   |   |  |

### Table 55. Timer 0–1 PWM Low Byte Register (TxPWML)

PWMH and PWML—Pulse-Width Modulator High and Low Bytes These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL1) register.

The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.

### WDT Reset in Normal Operation

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Reset Status (RSTSTAT) register is set to 1. For more information on system reset, see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23.

### WDT Reset in STOP Mode

If configured to generate a Reset when a time-out occurs and the device is in STOP mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Reset Status (RSTSTAT) register are set to 1 following WDT time-out in STOP mode.

## Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer (WDTCTL) Control register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers. Follow the steps below to unlock the Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte register (WDTU) with the desired time-out value.

- 4. Write the Watchdog Timer Reload High Byte register (WDTH) with the desired time-out value.

- 5. Write the Watchdog Timer Reload Low Byte register (WDTL) with the desired time-out value.

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

# Watchdog Timer Calibration

Due to its extremely low operating current, the Watchdog Timer oscillator is somewhat inaccurate. This variation can be corrected using the calibration data stored in the Flash Information Page (see Table 97 and Table 98 on page 165). Loading these values into the

# zilog

# Universal Asynchronous Receiver/Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. Features of the UART include:

- 8-bit asynchronous data transfer.

- Selectable even- and odd-parity generation and checking.

- Option of one or two STOP bits.

- Separate transmit and receive interrupts.

- Framing, parity, overrun and break detection.

- Separate transmit and receive enables.

- 16-bit baud rate generator (BRG).

- Selectable MULTIPROCESSOR (9-bit) mode with three configurable interrupt schemes.

- Baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

- Driver enable (DE) output for external bus transceivers.

# Architecture

The UART consists of three primary functional blocks: transmitter, receiver, and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 on page 98 displays the UART architecture.

- 3. Clears the UART Receiver interrupt in the applicable Interrupt Request register.

- 4. Executes the IRET instruction to return from the interrupt-service routine and await more data.

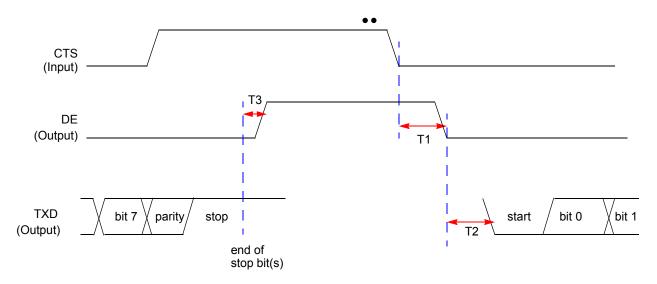

# Clear To Send (CTS) Operation

The CTS pin, if enabled by the CTSE bit of the UART Control 0 register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this action is typically performed during Stop Bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

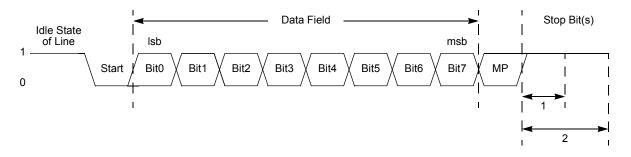

### MULTIPROCESSOR (9-bit) Mode

The UART has a MULTIPROCESSOR (9-bit) mode that uses an extra (9th) bit for selective communication when a number of processors share a common UART bus. In MULTI-PROCESSOR mode (also referred to as 9-bit mode), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 13. The character format is:

### Figure 13. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) mode, the Parity bit location (9th bit) becomes the Multiprocessor control bit. The UART Control 1 and Status 1 registers provide MULTI-PROCESSOR (9-bit) mode control and status information. If an automatic address matching scheme is enabled, the UART Address Compare register holds the network address of the device.

### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When MULTIPROCESSOR mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made in hardware, software or some combination of the two, depending on the multiprocessor

# zilog

134

# Low Power Operational Amplifier

# **Overview**

The LPO is a general-purpose low power operational amplifier. Each of the three ports of the amplifier is accessible from the package pins. The LPO contains only one pin configuration: ANA0 is the output/feedback node, ANA1 is the inverting input and ANA2 is the non-inverting input.

# Operation

To use the LPO, it must be enabled in the Power Control Register 0 (PWRCTL0). The default state of the LPO is OFF. To use the LPO, the LPO bit must be cleared, turning it ON (Power Control Register 0 (PWRCTL0) on page 35). When making normal ADC measurements on ANA0 (measurements not involving the LPO output), the LPO bit must be OFF. Turning the LPO bit ON interferes with normal ADC measurements.

**Warning:** The LPO bit enables the amplifier even in STOP mode. If the amplifier is not required in STOP mode, disable it. Failing to perform this results in STOP mode currents higher than necessary.

As with other ADC measurements, any pins used for analog purposes must be configured as such in the GPIO registers (see Port A–D Alternate Function Sub-Registers on page 47).

LPO output measurements are made on ANA0, as selected by the ANAIN[3:0] bits of ADC Control Register 0. It is also possible to make single-ended measurements on ANA1 and ANA2 while the amplifier is enabled, which is often useful for determining offset conditions. Differential measurements between ANA0 and ANA2 may be useful for noise cancellation purposes.

If the LPO output is routed to the ADC, then the BUFFMODE[2:0] bits of ADC Control/Status Register 1 must also be configured for unity-gain buffered operation. Sampling the LPO in an unbuffered mode is not recommended.

When either input is overdriven, the amplifier output saturates at the positive or negative supply voltage. No instability results.

| Info Page<br>Address | Memory<br>Address | Usage                                        |

|----------------------|-------------------|----------------------------------------------|

| 5C                   | FE5C              | Randomized Lot ID Byte 23                    |

| 5D                   | FE5D              | Randomized Lot ID Byte 22                    |

| 5E                   | FE5E              | Randomized Lot ID Byte 21                    |

| 5F                   | FE5F              | Randomized Lot ID Byte 20                    |

| 61                   | FE61              | Randomized Lot ID Byte 19                    |

| 62                   | FE62              | Randomized Lot ID Byte 18                    |

| 64                   | FE64              | Randomized Lot ID Byte 17                    |

| 65                   | FE65              | Randomized Lot ID Byte 16                    |

| 67                   | FE67              | Randomized Lot ID Byte 15                    |

| 68                   | FE68              | Randomized Lot ID Byte 14                    |

| 6A                   | FE6A              | Randomized Lot ID Byte 13                    |

| 6B                   | FE6B              | Randomized Lot ID Byte 12                    |

| 6D                   | FE6D              | Randomized Lot ID Byte 11                    |

| 6E                   | FE6E              | Randomized Lot ID Byte 10                    |

| 70                   | FE70              | Randomized Lot ID Byte 9                     |

| 71                   | FE71              | Randomized Lot ID Byte 8                     |

| 73                   | FE73              | Randomized Lot ID Byte 7                     |

| 74                   | FE74              | Randomized Lot ID Byte 6                     |

| 76                   | FE76              | Randomized Lot ID Byte 5                     |

| 77                   | FE77              | Randomized Lot ID Byte 4                     |

| 79                   | FE79              | Randomized Lot ID Byte 3                     |

| 7A                   | FE7A              | Randomized Lot ID Byte 2                     |

| 7C                   | FE7C              | Randomized Lot ID Byte 1                     |

| 7D                   | FE7D              | Randomized Lot ID Byte 0 (least significant) |

# Table 102. Randomized Lot ID Locations (Continued)

If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

DBG  $\leftarrow$  12H DBG  $\leftarrow$  1-5 byte opcode

# **On-Chip Debugger Control Register Definitions**

# **OCD Control Register**

The OCD Control register controls the state of the On-Chip Debugger. This register is used to enter or exit DEBUG mode and to enable the BRK instruction. It can also reset the Z8 Encore! XP<sup>®</sup> F082A Series device.

A reset and stop function can be achieved by writing \$1H to this register. A reset and go function can be achieved by writing \$1H to this register. If the device is in DEBUG mode, a run function can be implemented by writing \$0H to this register.

## Table 106. OCD Control Register (OCDCTL)

| BITS  | 7       | 6     | 5      | 4 | 3    | 2     | 1 | 0   |

|-------|---------|-------|--------|---|------|-------|---|-----|

| FIELD | DBGMODE | BRKEN | DBGACK |   | Rese | erved |   | RST |

| RESET | 0       | 0     | 0      | 0 | 0    | 0     | 0 | 0   |

| R/W   | R/W     | R/W   | R/W    | R | R    | R     | R | R/W |

### DBGMODE—DEBUG Mode

The device enters DEBUG mode when this bit is 1. When in DEBUG mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is automatically set when a BRK instruction is decoded and Breakpoints are enabled. If the Flash Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device. It cannot be written to 0.

0 = The Z8 Encore! XP F082A Series device is operating in NORMAL mode.

1 = The Z8 Encore! XP F082A Series device is in DEBUG mode.

### BRKEN—Breakpoint Enable

This bit controls the behavior of the BRK instruction (opcode 00H). By default, Breakpoints are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1, when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL register is automatically set to 1.

0 = Breakpoints are disabled.

1 = Breakpoints are enabled.

zilog

207

### Table 123. Rotate and Shift Instructions (Continued)

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| SRA      | dst      | Shift Right Arithmetic |

| SRL      | dst      | Shift Right Logical    |

| SWAP     | dst      | Swap Nibbles           |

# eZ8 CPU Instruction Summary

Table 124 summarizes the eZ8 CPU instructions. The table identifies the addressing modes employed by the instruction, the effect upon the Flags register, the number of CPU clock cycles required for the instruction fetch, and the number of CPU clock cycles required for the instruction.

| Assembly<br>Mnemonic | Symbolic<br>Operation                                      | Addres        | Address Mode Opco |           | Flags |          |   |           |   |   | Fetch | Instr. |

|----------------------|------------------------------------------------------------|---------------|-------------------|-----------|-------|----------|---|-----------|---|---|-------|--------|

|                      |                                                            | dst           | src               | (Hex)     | С     | Ζ        | S | ۷         | D | Н |       | Cycles |

| ADC dst, src         | $dst \gets dst + src + C$                                  | r             | r                 | 12        | *     | *        | * | *         | 0 | * | 2     | 3      |

|                      |                                                            | r             | lr                | 13        | -     |          |   |           |   |   | 2     | 4      |

|                      |                                                            | R             | R                 | 14        | -     |          |   |           |   |   | 3     | 3      |

|                      |                                                            | R             | IR                | 15        | -     |          |   |           |   |   | 3     | 4      |

|                      |                                                            | R             | IM                | 16        | -     |          |   |           |   |   | 3     | 3      |

|                      |                                                            | IR            | IM                | 17        | -     |          |   |           |   |   | 3     | 4      |

| ADCX dst, src        | $dst \gets dst + src + C$                                  | ER            | ER                | 18        | *     | *        | * | *         | 0 | * | 4     | 3      |

|                      |                                                            | ER            | IM                | 19        | -     |          |   |           |   |   | 4     | 3      |

| ADD dst, src         | $dst \gets dst + src$                                      | r             | r                 | 02        | *     | *        | * | *         | 0 | * | 2     | 3      |

|                      |                                                            | r             | lr                | 03        | _     |          |   |           |   |   | 2     | 4      |

|                      |                                                            | R             | R                 | 04        | -     |          |   |           |   |   | 3     | 3      |

|                      |                                                            | R             | IR                | 05        | -     |          |   |           |   |   | 3     | 4      |

|                      |                                                            | R             | IM                | 06        | _     |          |   |           |   |   | 3     | 3      |

|                      |                                                            | IR            | IM                | 07        | _     |          |   |           |   |   | 3     | 4      |

| ADDX dst, src        | $dst \gets dst + src$                                      | ER            | ER                | 08        | *     | *        | * | *         | 0 | * | 4     | 3      |

|                      |                                                            | ER            | IM                | 09        | -     |          |   |           |   |   | 4     | 3      |

| Flags Notation:      | * = Value is a function<br>– = Unaffected<br>X = Undefined | of the result | of the o          | peration. |       | Re<br>Se |   | to (<br>1 | ) |   |       |        |

Table 124. eZ8 CPU Instruction Summary

| 2 | n | ٥ |

|---|---|---|

| 4 | υ | 3 |

| Assembly        | Symbolic<br>Operation                                                                            | Addres        | Address Mode Opcode(s) |           |   |          | Fla | ags | Fetch | Instr. |   |        |

|-----------------|--------------------------------------------------------------------------------------------------|---------------|------------------------|-----------|---|----------|-----|-----|-------|--------|---|--------|

| Mnemonic        |                                                                                                  | dst           | src                    | (Hex)     | С | Ζ        | S   | ۷   | D     | Н      |   | Cycles |

| COM dst         | $dst \gets \simdst$                                                                              | R             |                        | 60        | - | *        | *   | 0   | -     | -      | 2 | 2      |

|                 |                                                                                                  | IR            |                        | 61        |   |          |     |     |       |        | 2 | 3      |

| CP dst, src     | dst - src                                                                                        | r             | r                      | A2        | * | *        | *   | *   | -     | -      | 2 | 3      |

|                 |                                                                                                  | r             | lr                     | A3        | - |          |     |     |       |        | 2 | 4      |

|                 |                                                                                                  | R             | R                      | A4        | - |          |     |     |       |        | 3 | 3      |

|                 |                                                                                                  | R             | IR                     | A5        | - |          |     |     |       |        | 3 | 4      |

|                 |                                                                                                  | R             | IM                     | A6        | - |          |     |     |       |        | 3 | 3      |

|                 |                                                                                                  | IR            | IM                     | A7        | - |          |     |     |       |        | 3 | 4      |

| CPC dst, src    | dst - src - C                                                                                    | r             | r                      | 1F A2     | * | *        | *   | *   | -     | -      | 3 | 3      |

|                 |                                                                                                  | r             | lr                     | 1F A3     | - |          |     |     |       |        | 3 | 4      |

|                 |                                                                                                  | R             | R                      | 1F A4     | - |          |     |     |       |        | 4 | 3      |

|                 |                                                                                                  | R             | IR                     | 1F A5     | - |          |     |     |       |        | 4 | 4      |

|                 |                                                                                                  | R             | IM                     | 1F A6     | - |          |     |     |       |        | 4 | 3      |

|                 |                                                                                                  | IR            | IM                     | 1F A7     | - |          |     |     |       |        | 4 | 4      |

| CPCX dst, src   | dst - src - C                                                                                    | ER            | ER                     | 1F A8     | * | *        | *   | *   | _     | _      | 5 | 3      |

|                 |                                                                                                  | ER            | IM                     | 1F A9     | - |          |     |     |       |        | 5 | 3      |

| CPX dst, src    | dst - src                                                                                        | ER            | ER                     | A8        | * | *        | *   | *   | _     | _      | 4 | 3      |

|                 |                                                                                                  | ER            | IM                     | A9        | - |          |     |     |       |        | 4 | 3      |

| DA dst          | $dst \gets DA(dst)$                                                                              | R             |                        | 40        | * | *        | *   | Х   | _     | _      | 2 | 2      |

|                 |                                                                                                  | IR            |                        | 41        | - |          |     |     |       |        | 2 | 3      |

| DEC dst         | $dst \gets dst \text{ - } 1$                                                                     | R             |                        | 30        | _ | *        | *   | *   | _     | _      | 2 | 2      |

|                 |                                                                                                  | IR            |                        | 31        | - |          |     |     |       |        | 2 | 3      |

| DECW dst        | $dst \gets dst \text{ - } 1$                                                                     | RR            |                        | 80        | _ | *        | *   | *   | _     | _      | 2 | 5      |

|                 |                                                                                                  | IRR           |                        | 81        | - |          |     |     |       |        | 2 | 6      |

| DI              | $IRQCTL[7] \leftarrow 0$                                                                         |               |                        | 8F        | _ | _        | _   | _   | _     | _      | 1 | 2      |

| DJNZ dst, RA    | $\begin{array}{l} dst \leftarrow dst - 1 \\ if \ dst \neq 0 \\ PC \leftarrow PC + X \end{array}$ | r             |                        | 0A-FA     | _ | _        | _   | _   | _     | _      | 2 | 3      |

| EI              | $IRQCTL[7] \leftarrow 1$                                                                         |               |                        | 9F        | _ | -        | _   | _   | -     | -      | 1 | 2      |

| Flags Notation: | * = Value is a function<br>– = Unaffected<br>X = Undefined                                       | of the result | of the o               | peration. |   | Re<br>Se |     |     | )     |        |   |        |

# Table 124. eZ8 CPU Instruction Summary (Continued)

zilog <sub>238</sub>

# **UART** Timing

Figure 37 and Table 142 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the transmit data register has been loaded with data prior to CTS assertion.

|                |                                                    | Delay (ns)        |                                |  |  |  |  |

|----------------|----------------------------------------------------|-------------------|--------------------------------|--|--|--|--|

| Parameter      | Abbreviation                                       | Minimum           | Maximum                        |  |  |  |  |

| UART           |                                                    |                   |                                |  |  |  |  |

| T <sub>1</sub> | CTS Fall to DE output delay                        | 2 * XIN<br>period | 2 * XIN period<br>+ 1 bit time |  |  |  |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) delay | / ± 5             |                                |  |  |  |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay         | ± 5               |                                |  |  |  |  |

### Table 142. UART Timing With CTS

266

timing 237 OCD commands execute instruction (12H) 183 read data memory (0DH) 183 read OCD control register (05H) 181 read OCD revision (00H) 180 read OCD status register (02H) 180 read program counter (07H) 181 read program memory (0BH) 182 read program memory CRC (0EH) 183 read register (09H) 182 read runtime counter (03H) 180 step instruction (10H) 183 stuff instruction (11H) 183 write data memory (0CH) 182 write OCD control register (04H) 181 write program counter (06H) 181 write program memory (0AH) 182 write register (08H) 181 on-chip debugger (OCD) 173 on-chip debugger signals 12 on-chip oscillator 193 **ONE-SHOT** mode 84 opcode map abbreviations 217 cell description 216 first 218 second after 1FH 219 Operational Description 23, 33, 37, 55, 69, 91, 97, 117, 121, 134, 135, 139, 141, 153, 169, 173, 187, 193, 197 OR 205 ordering information 251 **ORX 206** oscillator signals 12

## Ρ

p 201 packaging 20-pin PDIP 244, 245 20-pin SSOP 246, 249 28-pin PDIP 247 28-pin SOIC 248

8-pin PDIP 241 8-pin SOIC 242 PDIP 248, 249 part selection guide 2 PC 202 PDIP 248, 249 peripheral AC and DC electrical characteristics 229 pin characteristics 13 **Pin Descriptions 9** polarity 201 POP 205 pop using extended addressing 205 **POPX 205** port availability, device 37 port input timing (GPIO) 235 port output timing, GPIO 236 power supply signals 13 power-down, automatic (ADC) 122 Power-on and Voltage Brownout electrical characteristics and timing 229 Power-On Reset (POR) 25 program control instructions 206 program counter 202 program memory 15 **PUSH 205** push using extended addressing 205 PUSHX 205 PWM mode 85 PxADDR register 46 PxCTL register 47

# R

R 201 r 201 RA register address 201 RCF 204 receive IrDA data 119 receiving UART data-interrupt-driven method 102 receiving UART data-polled method 101

268

subtract with carry - extended addressing 203 SUBX 203 SWAP 207 swap nibbles 207 symbols, additional 202

# Т

TCM 204 **TCMX 204 Technical Support 271** test complement under mask 204 test complement under mask - extended addressing 204 test under mask 204 test under mask - extended addressing 204 timer signals 11 timers 69 architecture 69 block diagram 70 CAPTURE mode 77, 78, 85, 86 CAPTURE/COMPARE mode 81, 85 COMPARE mode 79.85 CONTINUOUS mode 71, 84 COUNTER mode 72, 73 COUNTER modes 84 GATED mode 80, 85 ONE-SHOT mode 70, 84 operating mode 70 PWM mode 74, 76, 85 reading the timer count values 82 reload high and low byte registers 87 timer control register definitions 83 timer output signal operation 82 timers 0-3 control registers 83, 84 high and low byte registers 87, 88 TM 204 TMX 204 transmit IrDA data 118 transmitting UART data-polled method 99 transmitting UART dat-interrupt-driven method 100

TRAP 206

# U

### UART 7

architecture 97 baud rate generator 107 baud rates table 115 control register definitions 108 controller signals 11 data format 98 interrupts 105 multiprocessor mode 103 receiving data using interrupt-driven method 102 receiving data using the polled method 101 transmitting data usin the interrupt-driven method 100 transmitting data using the polled method 99 x baud rate high and low registers 114 x control 0 and control 1 registers 108 x status 0 and status 1 registers 111, 112 UxBRH register 114 UxBRL register 114 UxCTL0 register 108, 114 UxCTL1 register 109 UxRXD register 113 UxSTAT0 register 111 UxSTAT1 register 112 UxTXD register 113

# V

vector 201 Voltage Brownout reset (VBR) 26

# W

Watchdog Timer approximate time-out delay 91 approximate time-out delays 135 CNTL 26 control register 94, 136, 190

269

electrical characteristics and timing 230, 233 interrupt in normal operation 92 interrupt in STOP mode 92 operation 135 refresh 92, 205 reload unlock sequence 93 reload upper, high and low registers 94 reset 27 reset in normal operation 93 reset in STOP mode 93 time-out response 92 WDTCTL register 31, 94, 136, 190 WDTH register 95 WDTL register 95 working register 201 working register pair 201 WTDU register 95

# Х

X 201 XOR 206 XORX 206

# Ζ

Z8 Encore! block diagram 4 features 1 part selection guide 2