Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                               |  |

|----------------------------|---------------------------------------------------------------|--|

| Product Status             | Obsolete                                                      |  |

| Core Processor             | eZ8                                                           |  |

| Core Size                  | 8-Bit                                                         |  |

| Speed                      | 20MHz                                                         |  |

| Connectivity               | IrDA, UART/USART                                              |  |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT               |  |

| Number of I/O              | 17                                                            |  |

| Program Memory Size        | 1KB (1K x 8)                                                  |  |

| Program Memory Type        | FLASH                                                         |  |

| EEPROM Size                | 16 x 8                                                        |  |

| RAM Size                   | 256 x 8                                                       |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |  |

| Data Converters            | -                                                             |  |

| Oscillator Type            | Internal                                                      |  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |  |

| Mounting Type              | Surface Mount                                                 |  |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                |  |

| Supplier Device Package    | -                                                             |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f011ash020sc00tr |  |

## Z8 Encore! XP® F082A Series **Product Specification**

| Hardware Overflow                                            | 123     |

|--------------------------------------------------------------|---------|

| Automatic Powerdown                                          |         |

| Single-Shot Conversion                                       |         |

| Continuous Conversion                                        |         |

| Interrupts                                                   |         |

| Calibration and Compensation                                 |         |

| ADC Compensation Details                                     |         |

| Input Buffer Stage                                           |         |

| ADC Control Register Definitions                             |         |

| ADC Control Register 0                                       |         |

| ADC Control/Status Register 1                                |         |

| ADC Data High Byte Register                                  |         |

| ADC Data Low Byte Register                                   |         |

| Low Power Operational Amplifier                              | 134     |

| Overview                                                     | 134     |

| Operation                                                    | 134     |

| Comparator                                                   |         |

| •                                                            |         |

| Operation                                                    |         |

| Comparator Control Register Definitions                      | 136     |

| Temperature Sensor                                           | 139     |

| Temperature Sensor Operation                                 | 139     |

| Flash Memory                                                 | 141     |

| Architecture                                                 | 141     |

| Flash Information Area                                       |         |

| Operation                                                    |         |

|                                                              |         |

| Flash Operation Timing Using the Flash Frequency Registers   |         |

| Flash Code Protection Against Accidental Program and Erasure |         |

| · · · · · · · · · · · · · · · · · · ·                        | 147     |

|                                                              | <br>147 |

|                                                              | <br>147 |

|                                                              | 148     |

| <b>71</b>                                                    | 148     |

|                                                              | 149     |

| <u> </u>                                                     | 149     |

| •                                                            | 150     |

|                                                              | 150     |

PS022825-0908 **Table of Contents**

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

| OCD Data Format                                         | 1/6 |

|---------------------------------------------------------|-----|

| OCD Auto-Baud Detector/Generator                        |     |

| OCD Serial Errors                                       |     |

| OCD Unlock Sequence (8-Pin Devices Only)                |     |

| Breakpoints                                             |     |

| Runtime Counter                                         |     |

| On-Chip Debugger Commands                               |     |

| On-Chip Debugger Control Register Definitions           |     |

| OCD Control Register                                    |     |

| OCD Status Register                                     |     |

| Oscillator Control                                      | 187 |

| Operation                                               | 187 |

| System Clock Selection                                  |     |

| Clock Failure Detection and Recovery                    |     |

| Oscillator Control Register Definitions                 | 190 |

| Crystal Oscillator                                      |     |

| Operating Modes                                         | 193 |

| Crystal Oscillator Operation                            |     |

| Oscillator Operation with an External RC Network        |     |

| Internal Precision Oscillator                           | 197 |

| Operation                                               | 197 |

| eZ8 CPU Instruction Set                                 | 199 |

| Assembly Language Programming Introduction              | 199 |

| Assembly Language Syntax                                |     |

| eZ8 CPU Instruction Notation                            |     |

| eZ8 CPU Instruction Classes                             |     |

| eZ8 CPU Instruction Summary                             |     |

| Opcode Maps                                             |     |

| Electrical Characteristics                              |     |

|                                                         |     |

| Absolute Maximum Ratings                                | 221 |

| DC Characteristics                                      | 222 |

| AC Characteristics                                      | 227 |

| On-Chip Peripheral AC and DC Electrical Characteristics | 229 |

| General Purpose I/O Port Input Data Sample Timing       | 234 |

PS022825-0908 Table of Contents

## **CPU and Peripheral Overview**

### eZ8 CPU Features

The eZ8 CPU, Zilog's latest 8-bit Central Processing Unit (CPU), meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original Z8<sup>®</sup> instruction set. The features of eZ8 CPU include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory.

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks.

- Compatible with existing Z8 code.

- Expanded internal Register File allows access of up to 4 KB.

- New instructions improve execution efficiency for code developed using higher-level programming languages, including C.

- Pipelined instruction fetch and execution.

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT, and SRL.

- New instructions support 12-bit linear addressing of the Register File.

- Up to 10 MIPS operation.

- C-Compiler friendly.

- 2 to 9 clock cycles per instruction.

For more information on eZ8 CPU, refer to eZ8 CPU Core User Manual (UM0128) available for download at www.zilog.com.

## 10-Bit Analog-to-Digital Converter

The optional analog-to-digital converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from eight different analog input pins in both single-ended and differential modes. The ADC also features a unity gain buffer when high input impedance is required.

PS022825-0908 Overview

## **Low-Power Operational Amplifier**

The optional low-power operational amplifier (LPO) is a general-purpose amplifier primarily targeted for current sense applications. The LPO output may be routed internally to the ADC or externally to a pin.

### Internal Precision Oscillator

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

## **Temperature Sensor**

The optional temperature sensor produces an analog output proportional to the device temperature. This signal can be sent to either the ADC or the analog comparator.

## **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

## **External Crystal Oscillator**

The crystal oscillator circuit provides highly accurate clock frequencies with the use of an external crystal, ceramic resonator or RC network.

## **Low Voltage Detector**

The low voltage detector (LVD) is able to generate an interrupt when the supply voltage drops below a user-programmable level. The LVD is available on 8-pin devices only.

## **On-Chip Debugger**

The Z8 Encore! XP<sup>®</sup> F082A Series products feature an integrated on-chip debugger (OCD) accessed via a single-pin interface. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints, and executing code.

PS022825-0908 Overview

**Table 2. Signal Descriptions (Continued)**

| Signal Mnemonic  | I/O | Description           |

|------------------|-----|-----------------------|

| Power Supply     |     |                       |

| $V_{DD}$         | I   | Digital Power Supply. |

| AV <sub>DD</sub> | I   | Analog Power Supply.  |

| V <sub>SS</sub>  | I   | Digital Ground.       |

| AV <sub>SS</sub> | I   | Analog Ground.        |

**Note:** The  $AV_{DD}$  and  $AV_{SS}$  signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

### **Pin Characteristics**

Table 3 describes the characteristics for each pin available on the Z8 Encore! XP F082A Series 20- and 28-pin devices. Data in Table 3 is sorted alphabetically by the pin symbol mnemonic.

Table 4 on page 14 provides detailed information about the characteristics for each pin available on the Z8 Encore! XP F082A Series 8-pin devices.

Note:

All six I/O pins on the 8-pin packages are 5 V-tolerant (unless the pull-up devices are enabled). The column in Table 3 below describes 5 V-tolerance for the 20- and 28-pin packages only.

Table 3. Pin Characteristics (20- and 28-pin Devices)

| Symbol<br>Mnemonic | Direction | Reset<br>Direction | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal Pull-<br>up<br>or Pull-down | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output | 5 V<br>Tolerance                        |

|--------------------|-----------|--------------------|---------------------------------------|--------------------|--------------------------------------|------------------------------|----------------------|-----------------------------------------|

| AVDD               | N/A       | N/A                | N/A                                   | N/A                | N/A                                  | N/A                          | N/A                  | N/A                                     |

| AVSS               | N/A       | N/A                | N/A                                   | N/A                | N/A                                  | N/A                          | N/A                  | NA                                      |

| DBG                | I/O       | 1                  | N/A                                   | Yes                | Yes                                  | Yes                          | Yes                  | No                                      |

| PA[7:0]            | I/O       | I                  | N/A                                   | Yes                | Programmable<br>Pull-up              | Yes                          | Yes,<br>Programmable | PA[7:2]<br>unless<br>pullups<br>enabled |

| PB[7:0]            | I/O       | I                  | N/A                                   | Yes                | Programmable<br>Pull-up              | Yes                          | Yes,<br>Programmable | PB[7:6]<br>unless<br>pullups<br>enabled |

PS022825-0908 Pin Description

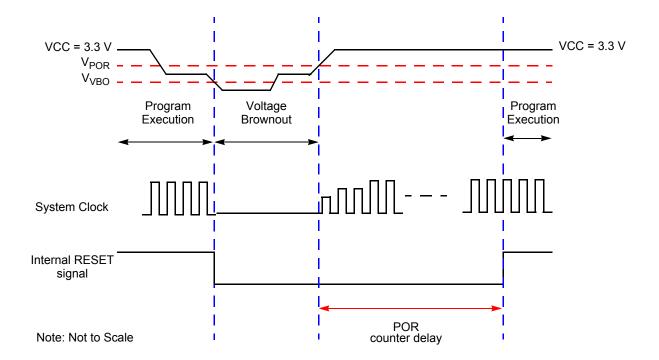

Figure 6. Voltage Brownout Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a Power-On Reset after recovering from a VBO condition.

## **Watchdog Timer Reset**

If the device is in NORMAL or HALT mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash Option Bit is programmed to 1. This is the unprogrammed state of the WDT\_RES Flash Option Bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT bit in the Reset Status (RSTSTAT) register is set to signify that the reset was initiated by the Watchdog Timer.

## **External Reset Input**

The RESET pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the RESET pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system clock and reset signals, the required reset duration may be as short as three clock periods

tions as a GPIO pin. If it is not present, the debug feature is disabled until/unless another reset event occurs. For more details, see On-Chip Debugger on page 173.

## **Crystal Oscillator Override**

For systems using a crystal oscillator, PA0 and PA1 are used to connect the crystal. When the crystal oscillator is enabled (see Oscillator Control Register Definitions on page 190), the GPIO settings are overridden and PA0 and PA1 are disabled.

### **5 V Tolerance**

All six I/O pins on the 8-pin devices are 5 V-tolerant, unless the programmable pull-ups are enabled. If the pull-ups are enabled and inputs higher than  $V_{DD}$  are applied to these parts, excessive current flows through those pull-up devices and can damage the chip.

Note:

In the 20- and 28-pin versions of this device, any pin which shares functionality with an ADC, crystal or comparator port is not 5 V-tolerant, including PA[1:0], PB[5:0] and PC[2:0]. All other signal pins are 5 V-tolerant, and can safely handle inputs higher than  $V_{DD}$  except when the programmable pull-ups are enabled.

## **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control (OSCCTL) register (see Oscillator Control Register Definitions on page 190) such that the external oscillator is selected as the system clock. For 8-pin devices use PA1 instead of PB3.

Table 32. Trap and Interrupt Vectors in Order of Priority

| Dui a uita . | Program<br>Memory       | Indonesia de Trom Course                                                                                                           |

|--------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Priority     | Vector Address<br>0002H | Interrupt or Trap Source  Reset (not an interrupt)                                                                                 |

| Highest      | 000211<br>0004H         | ·                                                                                                                                  |

|              |                         | Watchdog Timer (see Watchdog Timer on page 91)                                                                                     |

|              | 003AH                   | Primary Oscillator Fail Trap (not an interrupt)                                                                                    |

|              | 003CH                   | Watchdog Oscillator Fail Trap (not an interrupt)                                                                                   |

|              | 0006H                   | Illegal Instruction Trap (not an interrupt)                                                                                        |

|              | H8000                   | Reserved                                                                                                                           |

|              | 000AH                   | Timer 1                                                                                                                            |

|              | 000CH                   | Timer 0                                                                                                                            |

|              | 000EH                   | UART 0 receiver                                                                                                                    |

|              | 0010H                   | UART 0 transmitter                                                                                                                 |

|              | 0012H                   | Reserved                                                                                                                           |

|              | 0014H                   | Reserved                                                                                                                           |

|              | 0016H                   | ADC                                                                                                                                |

|              | 0018H                   | Port A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23) |

|              | 001AH                   | Port A Pin 6, selectable rising or falling input edge or Comparator Output                                                         |

|              | 001CH                   | Port A Pin 5, selectable rising or falling input edge                                                                              |

|              | 001EH                   | Port A Pin 4, selectable rising or falling input edge                                                                              |

|              | 0020H                   | Port A Pin 3, selectable rising or falling input edge                                                                              |

|              | 0022H                   | Port A Pin 2, selectable rising or falling input edge                                                                              |

|              | 0024H                   | Port A Pin 1, selectable rising or falling input edge                                                                              |

|              | 0026H                   | Port A Pin 0, selectable rising or falling input edge                                                                              |

|              | 0028H                   | Reserved                                                                                                                           |

|              | 002AH                   | Reserved                                                                                                                           |

|              | 002CH                   | Reserved                                                                                                                           |

|              | 002EH                   | Reserved                                                                                                                           |

|              | 0030H                   | Port C Pin 3, both input edges                                                                                                     |

|              | 0032H                   | Port C Pin 2, both input edges                                                                                                     |

PS022825-0908 Interrupt Controller

ner Output signal begins as

If the TPOL bit in the Timer Control register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

Follow the steps below for configuring a timer for PWM SINGLE OUTPUT mode and initiating the PWM operation:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for PWM SINGLE OUTPUT mode.

- Set the prescale value.

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM period). The Reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

$$PWM \ Period \ (s) \ = \ \frac{Reload \ Value \times Prescale}{System \ Clock \ Frequency \ (Hz)}$$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT mode equation to determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =

$$\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =

$$\frac{PWM \ Value}{Reload \ Value} \times 100$$

PS022825-0908 Timers

## **Timer Control Register Definitions**

## Timer 0–1 Control Registers

## Time 0-1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1) determine the timer operating mode (Table 48). It also includes a programmable PWM deadband delay, two bits to configure timer interrupt definition, and a status bit to identify if the most recent timer interrupt is caused by an input capture event.

Table 48. Timer 0–1 Control Register 0 (TxCTL0)

| BITS  | 7       | 6          | 5   | 4        | 3    | 2   | 1   | 0      |

|-------|---------|------------|-----|----------|------|-----|-----|--------|

| FIELD | TMODEHI | TICONFIG   |     | Reserved | PWMD |     |     | INPCAP |

| RESET | 0       | 0          | 0   | 0        | 0    | 0   | 0   | 0      |

| R/W   | R/W     | R/W        | R/W | R/W      | R/W  | R/W | R/W | R      |

| ADDR  |         | F06H, F0EH |     |          |      |     |     |        |

### TMODEHI—Timer Mode High Bit

This bit along with the TMODE field in TxCTL1 register determines the operating mode of the timer. This is the most significant bit of the Timer mode selection value. See the TxCTL1 register description for details of the full timer mode decoding.

### TICONFIG—Timer Interrupt Configuration

This field configures timer interrupt definition.

0x = Timer Interrupt occurs on all defined Reload, Compare and Input Events

10 = Timer Interrupt only on defined Input Capture/Deassertion Events

11 = Timer Interrupt only on defined Reload/Compare Events

Reserved—Must be 0.

### PWMD—PWM Delay value

This field is a programmable delay to control the number of system clock cycles delay before the Timer Output and the Timer Output Complement are forced to their active state.

000 = No delay

001 = 2 cycles delay

010 = 4 cycles delay

011 = 8 cycles delay

100 = 16 cycles delay

101 = 32 cycles delay

PS022825-0908 Timers

The 24-bit WDT Reload Value must not be set to a value less than 000004H.

Table 58. Watchdog Timer Reload Upper Byte Register (WDTU)

| BITS       | 7                                                                                         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|------------|-------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|--|

| FIELD      | WDTU                                                                                      |   |   |   |   |   |   |   |  |

| RESET      | 00H                                                                                       |   |   |   |   |   |   |   |  |

| R/W        | R/W*                                                                                      |   |   |   |   |   |   |   |  |

| ADDR       | FF1H                                                                                      |   |   |   |   |   |   |   |  |

| R/W* - Rea | R/W* - Read returns the current WDT count value. Write sets the appropriate Reload Value. |   |   |   |   |   |   |   |  |

WDTU—WDT Reload Upper Byte

Most-significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value.

Table 59. Watchdog Timer Reload High Byte Register (WDTH)

| BITS       | 7                                                                                         | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |

|------------|-------------------------------------------------------------------------------------------|------|---|---|---|---|---|---|--|

| FIELD      |                                                                                           | WDTH |   |   |   |   |   |   |  |

| RESET      |                                                                                           | 04H  |   |   |   |   |   |   |  |

| R/W        | R/W*                                                                                      |      |   |   |   |   |   |   |  |

| ADDR       | FF2H                                                                                      |      |   |   |   |   |   |   |  |

| R/W* - Rea | R/W* - Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |   |   |   |   |   |   |  |

WDTH—WDT Reload High Byte

Middle byte, Bits[15:8], of the 24-bit WDT reload value.

Table 60. Watchdog Timer Reload Low Byte Register (WDTL)

| BITS       | 7                                                                                         | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |

|------------|-------------------------------------------------------------------------------------------|------|---|---|---|---|---|---|--|

| FIELD      |                                                                                           | WDTL |   |   |   |   |   |   |  |

| RESET      | 00H                                                                                       |      |   |   |   |   |   |   |  |

| R/W        | R/W*                                                                                      |      |   |   |   |   |   |   |  |

| ADDR       | FF3H                                                                                      |      |   |   |   |   |   |   |  |

| R/W* - Rea | R/W* - Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |   |   |   |   |   |   |  |

WDTL-WDT Reload Low

Least significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value.

PS022825-0908 Watchdog Timer

### 139

## **Temperature Sensor**

The on-chip Temperature Sensor allows you to measure temperature on the die with either the on-board ADC or on-board comparator. This block is factory calibrated for in-circuit software correction. Uncalibrated accuracy is significantly worse, therefore the temperature sensor is not recommended for uncalibrated use.

## **Temperature Sensor Operation**

The on-chip temperature sensor is a Proportional to Absolute Temperature (PTAT) topology. A pair of Flash option bytes contain the calibration data. The temperature sensor can be disabled by a bit in the Power Control Register 0 on page 34 to reduce power consumption.

The temperature sensor can be directly read by the ADC to determine the absolute value of its output. The temperature sensor output is also available as an input to the comparator for threshold type measurement determination. The accuracy of the sensor when used with the comparator is substantially less than when measured by the ADC.

If the temperature sensor is routed to the ADC, the ADC must be configured in unity-gain buffered mode (see Input Buffer Stage on page 129) The value read back from the ADC is a signed number, although it is always positive.

The sensor is factory-trimmed through the ADC using the external 2.0 V reference. Unless the sensor is re-trimmed for use with a different reference, it is most accurate when used with the external 2.0 V reference.

Because this sensor is an on-chip sensor it is recommended that the user account for the difference between ambient and die temperature when inferring ambient temperature conditions.

During normal operation, the die undergoes heating that causes a mismatch between the ambient temperature and that measured by the sensor. For best results, the Z8 Encore! XP<sup>®</sup> device must be placed into STOP mode for sufficient time such that the die and ambient temperatures converge (this time is dependent on the thermal design of the system). The temperature sensor measurement must then be made immediately after recovery from STOP mode.

The following equation defines the transfer function between the temperature sensor output voltage and the die temperature. This is needed for comparator threshold measurements.

$V = 0.01 \times T + 0.65$

where, T is the temperature in °C; V is the sensor output in volts.

PS022825-0908 Temperature Sensor

163

**Table 94. ADC Calibration Data Location (Continued)**

| Info Page<br>Address | Memory<br>Address | Compensation Usage      | ADC Mode                 | Reference<br>Type |

|----------------------|-------------------|-------------------------|--------------------------|-------------------|

| 34                   | FE34              | Negative Gain High Byte | Differential Unbuffered  | External 2.0 V    |

| 35                   | FE35              | Negative Gain Low Byte  | Differential Unbuffered  | External 2.0 V    |

| 78                   | FE78              | Offset                  | Differential 1x Buffered | Internal 2.0 V    |

| 18                   | FE18              | Positive Gain High Byte | Differential 1x Buffered | Internal 2.0 V    |

| 19                   | FE19              | Positive Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V    |

| 36                   | FE36              | Negative Gain High Byte | Differential 1x Buffered | Internal 2.0 V    |

| 37                   | FE37              | Negative Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V    |

| 7B                   | FE7B              | Offset                  | Differential 1x Buffered | External 2.0 V    |

| 1A                   | FE1A              | Positive Gain High Byte | Differential 1x Buffered | External 2.0 V    |

| 1B                   | FE1B              | Positive Gain Low Byte  | Differential 1x Buffered | External 2.0 V    |

| 38                   | FE38              | Negative Gain High Byte | Differential 1x Buffered | External 2.0 V    |

| 39                   | FE39              | Negative Gain Low Byte  | Differential 1x Buffered | External 2.0 V    |

PS022825-0908 Flash Option Bits

```

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

• Read Data Memory (0DH)—The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode, this command returns FFH for the data.

```

DBG ← 0DH

DBG ← Data Memory Address[15:8]

DBG ← Data Memory Address[7:0]

DBG ← Size[15:8]

DBG ← Size[7:0]

DBG → 1-65536 data bytes

```

• Read Program Memory CRC (0EH)—The Read Program Memory CRC command computes and returns the Cyclic Redundancy Check (CRC) of Program Memory using the 16-bit CRC-CCITT polynomial. If the device is not in DEBUG mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program Memory, calculates the CRC value, and returns the result. The delay is a function of the Program Memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program Memory.

```

DBG \leftarrow 0EH

DBG \rightarrow CRC[15:8]

DBG \rightarrow CRC[7:0]

```

• Step Instruction (10H)—The Step Instruction command steps one assembly instruction at the current Program Counter (PC) location. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

```

DBG ← 10H

```

• Stuff Instruction (11H)—The Stuff Instruction command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0-4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

• Execute Instruction (12H)—The Execute Instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over Breakpoints. The number of bytes to send for the instruction depends on the opcode.

PS022825-0908 On-Chip Debugger

**z**ilog°

186

PS022825-0908 On-Chip Debugger

**Table 108. Oscillator Configuration and Selection**

| Clock Source                          | Characteristics                                                                                                                                 | Required Setup                                                                                                                                                                                                                                                                 |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Precision<br>RC Oscillator   | <ul><li>32.8 kHz or 5.53 MHz</li><li>High accuracy</li><li>No external components required</li></ul>                                            | <ul> <li>Unlock and write Oscillator Control<br/>Register (OSCCTL) to enable and<br/>select oscillator at either 5.53 MHz or<br/>32.8 kHz</li> </ul>                                                                                                                           |

| External Crystal/<br>Resonator        | <ul> <li>32 kHz to 20 MHz</li> <li>Very high accuracy (dependent on crystal or resonator used)</li> <li>Requires external components</li> </ul> | <ul> <li>Configure Flash option bits for correct external oscillator mode</li> <li>Unlock and write OSCCTL to enable crystal oscillator, wait for it to stabilize and select as system clock (if the XTLDIS option bit has been deasserted, no waiting is required)</li> </ul> |

| External RC<br>Oscillator             | <ul> <li>32 kHz to 4 MHz</li> <li>Accuracy dependent on external components</li> </ul>                                                          | <ul> <li>Configure Flash option bits for correct<br/>external oscillator mode</li> <li>Unlock and write OSCCTL to enable<br/>crystal oscillator and select as system<br/>clock</li> </ul>                                                                                      |

| External Clock<br>Drive               | <ul> <li>0 to 20 MHz</li> <li>Accuracy dependent on external clock<br/>source</li> </ul>                                                        | <ul> <li>Write GPIO registers to configure PB3 pin for external clock function</li> <li>Unlock and write OSCCTL to select external system clock</li> <li>Apply external clock signal to GPIO</li> </ul>                                                                        |

| Internal Watchdog<br>Timer Oscillator | <ul> <li>10 kHz nominal</li> <li>Low accuracy; no external components required</li> <li>Very low power consumption</li> </ul>                   | <ul> <li>Enable WDT if not enabled and wait<br/>until WDT Oscillator is operating.</li> <li>Unlock and write Oscillator Control<br/>Register (OSCCTL) to enable and<br/>select oscillator</li> </ul>                                                                           |

**Caution:** Unintentional accesses to the oscillator control register can actually stop the chip by switching to a non-functioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

### **OSC Control Register Unlocking/Locking**

To write the oscillator control register, unlock it by making two writes to the OSCCTL register with the values E7H followed by 18H. A third write to the OSCCTL register changes the value of the actual register and returns the register to a locked state. Any other sequence of oscillator control register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

PS022825-0908 Oscillator Control

## eZ8 CPU Instruction Set

## **Assembly Language Programming Introduction**

The eZ8 CPU assembly language provides a means for writing an application program without concern for actual memory addresses or machine instruction formats. A program written in assembly language is called a source program. Assembly language allows the use of symbolic addresses to identify memory locations. It also allows mnemonic codes (opcodes and operands) to represent the instructions themselves. The opcodes identify the instruction while the operands represent memory locations, registers, or immediate data values.

Each assembly language program consists of a series of symbolic commands called statements. Each statement can contain labels, operations, operands and comments.

Labels can be assigned to a particular instruction step in a source program. The label identifies that step in the program as an entry point for use by other instructions.

The assembly language also includes assembler directives that supplement the machine instruction. The assembler directives, or pseudo-ops, are not translated into a machine instruction. Rather, the pseudo-ops are interpreted as directives that control or assist the assembly process.

The source program is processed (assembled) by the assembler to obtain a machine language program called the object code. The object code is executed by the eZ8 CPU. An example segment of an assembly language program is detailed in the following example.

### **Assembly Language Source Program Example**

| JP START      | ; Everything after the semicolon is a comment.                                                                                                                                                                |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:        | ; A label called 'START'. The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs.                                 |

| LD R4, R7     | ; A Load (LD) instruction with two operands. The first operand, ; Working Register R4, is the destination. The second operand, ; Working Register R7, is the source. The contents of R7 is ; written into R4. |

| LD 234H, #%01 | ; Another Load (LD) instruction with two operands.<br>; The first operand, Extended Mode Register Address 234H,<br>; identifies the destination. The second operand, Immediate Data                           |

|               | ; value 01H, is the source. The value 01H is written into the ; Register at address 234H.                                                                                                                     |

PS022825-0908 eZ8 CPU Instruction Set

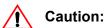

Figure 38 and Table 143 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the transmit data register has been written. DE remains asserted for multiple characters as long as the transmit data register is written with the next character before the current character has completed.

Figure 38. UART Timing Without CTS

**Table 143. UART Timing Without CTS**

|                |                                                                        | Delay (ns)        |            |  |  |

|----------------|------------------------------------------------------------------------|-------------------|------------|--|--|

| Parameter      | Abbreviation                                                           | Minimum           | Maximum    |  |  |

| UART           |                                                                        |                   |            |  |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * XIN<br>period | 1 bit time |  |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx data register is empty) | ± 5               |            |  |  |

PS022825-0908 Electrical Characteristics

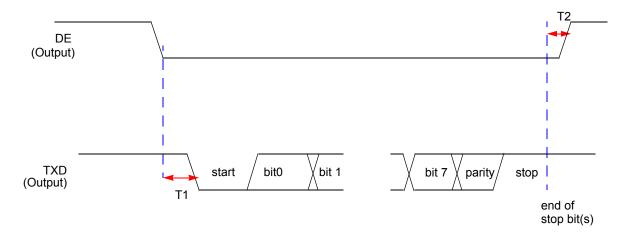

Figure 41 displays the 8-pin Quad Flat No-Lead package (QFN)/MLF-S available for the Z8 Encore! XP F082A Series devices. This package has a footprint identical to that of the 8-pin SOIC, but with a lower profile.

Figure 41. 8-Pin Quad Flat No-Lead Package (QFN)/MLF-S

PS022825-0908 Packaging

| Jage Encored XP® F0824                                                                                               | Flash | KAM<br>Water | SO O O O O O O O O O O O O O O O O O O | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|----------------------------------------------------------------------------------------------------------------------|-------|--------------|----------------------------------------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP® F082A Series with 4 KB Flash, 10-Bit Analog-to-Digital Converter  Standard Temperature: 0 °C to 70 °C |       |              |                                        |           |            |                     |                     |                |            |                    |                     |

| Z8F042APB020SC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F042AQB020SC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F042ASB020SC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F042ASH020SC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F042AHH020SC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F042APH020SC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F042ASJ020SC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F042AHJ020SC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F042APJ020SC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperature: -40 °C to 105 °C                                                                               |       |              |                                        |           |            |                     |                     |                |            |                    |                     |

| Z8F042APB020EC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F042AQB020EC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F042ASB020EC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F042ASH020EC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F042AHH020EC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F042APH020EC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F042ASJ020EC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F042AHJ020EC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F042APJ020EC                                                                                                       | 4 KB  | 1 KB         | 128 B                                  | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging                                                                             |       |              |                                        |           |            |                     |                     |                |            |                    |                     |

PS022825-0908 Ordering Information