Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 16 x 8                                                    |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f011asj020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Overview**

Zilog's Z8 Encore!<sup>®</sup> MCU family of products are the first in a line of Zilog<sup>®</sup> microcontroller products based upon the 8-bit eZ8 CPU. Zilog's Z8 Encore! XP<sup>®</sup> F082A Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8<sup>®</sup> instructions. The rich peripheral set of the Z8 Encore! XP F082A Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

## **Features**

The key features of Z8 Encore! XP F082A Series products include:

- 20 MHz eZ8 CPU

- 1 KB, 2 KB, 4 KB, or 8 KB Flash memory with in-circuit programming capability

- 256 B, 512 B, or 1 KB register RAM

- Up to 128 B non-volatile data storage (NVDS)

- Internal precision oscillator trimmed to  $\pm 1\%$  accuracy

- External crystal oscillator, operating up to 20 MHz

- Optional 8-channel, 10-bit analog-to-digital converter (ADC)

- Optional on-chip temperature sensor

- On-chip analog comparator

- Optional on-chip low-power operational amplifier (LPO)

- Full-duplex UART

- The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared Data Association (IrDA)-compliant infrared encoder/decoders, integrated with UART

- Two enhanced 16-bit timers with capture, compare, and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- Up to 20 vectored interrupts

- 6 to 25 I/O pins depending upon package

# Architecture

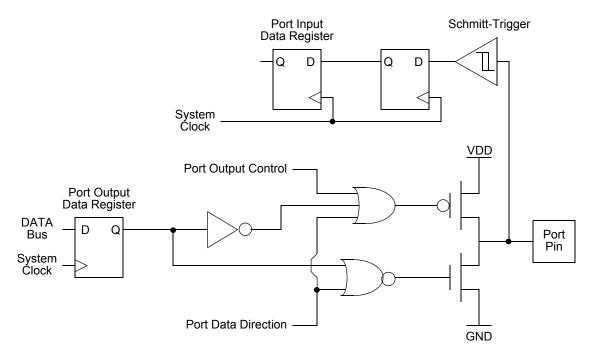

Figure 7 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

### Figure 7. GPIO Port Pin Block Diagram

# **GPIO Alternate Functions**

Many of the GPIO port pins can be used for general-purpose I/O and access to on-chip peripheral functions such as the timers and serial communication devices. The Port A–D Alternate Function sub-registers configure these pins for either General-Purpose I/O or alternate function operation. When a pin is configured for alternate function, control of the port pin direction (input/output) is passed from the Port A–D Data Direction registers to the alternate function assigned to this pin. Table 14 on page 41 lists the alternate functions possible with each port pin. For those pins with more one alternate function, the alternate function is defined through Alternate Function Sets sub-registers AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, those pins function as input and output for the crystal oscillator.

- Set the prescale value.

- If using the Timer Output alternate function, set the initial output level (High or Low).

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS mode. After the first timer Reload in CONTINUOUS mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the Timer Output function) for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In CONTINUOUS mode, the system clock always provides the timer input. The timer period is given by the following equation:

CONTINUOUS Mode Time-Out Period (s) =  $\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT mode equation to determine the first time-out period.

#### **COUNTER Mode**

In COUNTER mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO Port pin Timer Input alternate function. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the Timer Input signal. In COUNTER mode, the prescaler is disabled.

**Caution:** The input frequency of the Timer Input signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the input signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

Upon reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

**Caution:** *The 24-bit WDT Reload Value must not be set to a value less than* 000004H.

### Table 58. Watchdog Timer Reload Upper Byte Register (WDTU)

| BITS       | 7                                                                                  | 6    | 5 | 4  | 3  | 2 | 0 |  |  |  |  |  |  |  |

|------------|------------------------------------------------------------------------------------|------|---|----|----|---|---|--|--|--|--|--|--|--|

| FIELD      |                                                                                    | WDTU |   |    |    |   |   |  |  |  |  |  |  |  |

| RESET      |                                                                                    |      |   | 00 | Η  |   |   |  |  |  |  |  |  |  |

| R/W        |                                                                                    |      |   | R/ | N* |   |   |  |  |  |  |  |  |  |

| ADDR       | FF1H                                                                               |      |   |    |    |   |   |  |  |  |  |  |  |  |

| R/W* - Rea | Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |   |    |    |   |   |  |  |  |  |  |  |  |

R/W\* - Read returns the current WDT count value. Write sets the appropriate Reload Value.

WDTU—WDT Reload Upper Byte

Most-significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value.

### Table 59. Watchdog Timer Reload High Byte Register (WDTH)

| BITS       | 7                                                                                 | 6    | 5 | 4  | 3  | 2 1 0 |  |  |  |  |  |  |  |  |

|------------|-----------------------------------------------------------------------------------|------|---|----|----|-------|--|--|--|--|--|--|--|--|

| FIELD      |                                                                                   | WDTH |   |    |    |       |  |  |  |  |  |  |  |  |

| RESET      |                                                                                   | 04H  |   |    |    |       |  |  |  |  |  |  |  |  |

| R/W        |                                                                                   |      |   | R/ | N* |       |  |  |  |  |  |  |  |  |

| ADDR       |                                                                                   | FF2H |   |    |    |       |  |  |  |  |  |  |  |  |

| R/W* - Rea | ead returns the current WDT count value. Write sets the appropriate Reload Value. |      |   |    |    |       |  |  |  |  |  |  |  |  |

WDTH—WDT Reload High Byte

Middle byte, Bits[15:8], of the 24-bit WDT reload value.

### Table 60. Watchdog Timer Reload Low Byte Register (WDTL)

| BITS       | 7                                                                                 | 6    | 5 | 4  | 3  | 2 | 0 |  |  |  |  |  |  |  |

|------------|-----------------------------------------------------------------------------------|------|---|----|----|---|---|--|--|--|--|--|--|--|

| FIELD      |                                                                                   | WDTL |   |    |    |   |   |  |  |  |  |  |  |  |

| RESET      |                                                                                   | 00H  |   |    |    |   |   |  |  |  |  |  |  |  |

| R/W        |                                                                                   |      |   | R/ | W* |   |   |  |  |  |  |  |  |  |

| ADDR       |                                                                                   | FF3H |   |    |    |   |   |  |  |  |  |  |  |  |

| R/W* - Rea | ead returns the current WDT count value. Write sets the appropriate Reload Value. |      |   |    |    |   |   |  |  |  |  |  |  |  |

WDTL—WDT Reload Low

Least significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value.

# zilog

# Universal Asynchronous Receiver/Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. Features of the UART include:

- 8-bit asynchronous data transfer.

- Selectable even- and odd-parity generation and checking.

- Option of one or two STOP bits.

- Separate transmit and receive interrupts.

- Framing, parity, overrun and break detection.

- Separate transmit and receive enables.

- 16-bit baud rate generator (BRG).

- Selectable MULTIPROCESSOR (9-bit) mode with three configurable interrupt schemes.

- Baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

- Driver enable (DE) output for external bus transceivers.

## Architecture

The UART consists of three primary functional blocks: transmitter, receiver, and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 on page 98 displays the UART architecture.

### MPMD[1:0]—MULTIPROCESSOR Mode

If MULTIPROCESSOR (9-bit) mode is enabled,

00 = The UART generates an interrupt request on all received bytes (data and address).

01 = The UART generates an interrupt request only on received address bytes.

10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs.

11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register.

#### MPEN—MULTIPROCESSOR (9-bit) Enable

This bit is used to enable MULTIPROCESSOR (9-bit) mode.

0 = Disable MULTIPROCESSOR (9-bit) mode.

1 = Enable MULTIPROCESSOR (9-bit) mode.

#### MPBT—Multiprocessor Bit Transmit

This bit is applicable only when MULTIPROCESSOR (9-bit) mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.

0 = Send a 0 in the multiprocessor bit location of the data stream (data byte).

1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).

#### DEPOL—Driver Enable Polarity

0 = DE signal is Active High.

1 = DE signal is Active Low.

#### BRGCTL—Baud Rate Control

This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register.

When the UART receiver is **not** enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value 1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.

When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value. 1 = Reads from the Baud Rate High and Low Byte registers return the current BRG count value. Unlike the Timers, there is no mechanism to latch the Low Byte when the High Byte is read.

RDAIRQ—Receive Data Interrupt Enable

0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.

0 = No framing error occurred. 1 = A framing error occurred.

BRKD—Break Detect

This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data register clears this bit. 0 = No break occurred.

1 = A break occurred.

TDRE—Transmitter Data Register Empty

This bit indicates that the UART Transmit Data register is empty and ready for additional data. Writing to the UART Transmit Data register resets this bit.

0 = Do not write to the UART Transmit Data register.

1 = The UART Transmit Data register is ready to receive an additional byte to be transmitted.

TXE—Transmitter Empty

This bit indicates that the transmit shift register is empty and character transmission is finished.

0 = Data is currently transmitting.

1 = Transmission is complete.

$CTS - \overline{CTS}$  signal

When this bit is read it returns the level of the  $\overline{\text{CTS}}$  signal. This signal is active Low.

### **UART Status 1 Register**

This register contains multiprocessor control and status bits.

Table 64. UART Status 1 Register (U0STAT1)

| BITS  | 7 | 6 | 5    | 4    | 3   | 2   | 1      | 0    |

|-------|---|---|------|------|-----|-----|--------|------|

| FIELD |   |   | Rese | rved |     |     | NEWFRM | MPRX |

| RESET | 0 | 0 | 0    | 0    | 0   | 0   | 0      | 0    |

| R/W   | R | R | R    | R    | R/W | R/W | R      | R    |

| ADDR  |   |   |      | F4   | 4H  |     |        |      |

Reserved—Must be 0.

NEWFRM—Status bit denoting the start of a new frame. Reading the UART Receive Data register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame.

1 = The current byte is the first data byte of a new frame.

#### ANAIN[3:0]—Analog Input Select

These bits select the analog input for conversion. Not all Port pins in this list are available in all packages for the Z8 Encore! XP<sup>®</sup> F082A Series. For information on port pins available with each package style, see Pin Description on page 9. Do not enable unavailable analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.

For the reserved values, all input switches are disabled to avoid leakage or other undesirable operation. ADC samples taken with reserved bit settings are undefined.

SINGLE-ENDED:

- 0000 = ANA0 (transimpedance amp output when enabled)

- 0001 = ANA1 (transimpedance amp inverting input)

- 0010 = ANA2 (transimpedance amp non-inverting input)

- 0011 = ANA3

- 0100 = ANA4

- 0101 = ANA5

- 0110 = ANA6

- 0111 = ANA7

- 1000 = Reserved

- 1001 = Reserved

- 1010 = Reserved

- 1011 = Reserved

- 1100 = Hold transimpedance input nodes (ANA1 and ANA2) to ground.

- 1101 = Reserved

- 1110 = Temperature Sensor.

- 1111 = Reserved.

DIFFERENTIAL (non-inverting input and inverting input respectively):

- 0000 = ANA0 and ANA10001 = ANA2 and ANA30010 = ANA4 and ANA50011 = ANA1 and ANA00100 = ANA3 and ANA20101 = ANA5 and ANA40110 = ANA6 and ANA50111 = ANA0 and ANA50111 = ANA0 and ANA21000 = ANA0 and ANA31001 = ANA0 and ANA41010 = ANA0 and ANA51011 = Reserved1100 = Reserved1101 = Reserved1101 = Reserved1110 = Reserved

- 1111 = Manual Offset Calibration Mode

# zilog

134

# Low Power Operational Amplifier

## **Overview**

The LPO is a general-purpose low power operational amplifier. Each of the three ports of the amplifier is accessible from the package pins. The LPO contains only one pin configuration: ANA0 is the output/feedback node, ANA1 is the inverting input and ANA2 is the non-inverting input.

# Operation

To use the LPO, it must be enabled in the Power Control Register 0 (PWRCTL0). The default state of the LPO is OFF. To use the LPO, the LPO bit must be cleared, turning it ON (Power Control Register 0 (PWRCTL0) on page 35). When making normal ADC measurements on ANA0 (measurements not involving the LPO output), the LPO bit must be OFF. Turning the LPO bit ON interferes with normal ADC measurements.

**Warning:** The LPO bit enables the amplifier even in STOP mode. If the amplifier is not required in STOP mode, disable it. Failing to perform this results in STOP mode currents higher than necessary.

As with other ADC measurements, any pins used for analog purposes must be configured as such in the GPIO registers (see Port A–D Alternate Function Sub-Registers on page 47).

LPO output measurements are made on ANA0, as selected by the ANAIN[3:0] bits of ADC Control Register 0. It is also possible to make single-ended measurements on ANA1 and ANA2 while the amplifier is enabled, which is often useful for determining offset conditions. Differential measurements between ANA0 and ANA2 may be useful for noise cancellation purposes.

If the LPO output is routed to the ADC, then the BUFFMODE[2:0] bits of ADC Control/Status Register 1 must also be configured for unity-gain buffered operation. Sampling the LPO in an unbuffered mode is not recommended.

When either input is overdriven, the amplifier output saturates at the positive or negative supply voltage. No instability results.

1 = Watchdog Timer is enabled upon execution of the WDT instruction. Once enabled, the Watchdog Timer can only be disabled by a Reset or Stop Mode Recovery. This setting is the default for unprogrammed (erased) Flash.

OSC SEL[1:0]—Oscillator Mode Selection

00 = On-chip oscillator configured for use with external RC networks (<4 MHz).

01 = Minimum power for use with very low frequency crystals (32 kHz to 1.0 MHz).

10 = Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 5.0 MHz).

11 = Maximum power for use with high frequency crystals (5.0 MHz to 20.0 MHz). This setting is the default for unprogrammed (erased) Flash.

VBO AO-Voltage Brownout Protection Always On

0 = Voltage Brownout Protection can be disabled in STOP mode to reduce total power consumption. For the block to be disabled, the power control register bit must also be written (see Power Control Register Definitions on page 34).

1 = Voltage Brownout Protection is always enabled including during STOP mode. This setting is the default for unprogrammed (erased) Flash.

FRP—Flash Read Protect

0 = User program code is inaccessible. Limited control features are available through the On-Chip Debugger.

1 = User program code is accessible. All On-Chip Debugger commands are enabled. This setting is the default for unprogrammed (erased) Flash.

Reserved—Must be 1.

FWP—Flash Write Protect

This Option Bit provides Flash Program Memory protection:

0 = Programming and erasure disabled for all of Flash Program Memory. Programming,

Page Erase, and Mass Erase through User Code is disabled. Mass Erase is available using the On-Chip Debugger.

1 = Programming, Page Erase, and Mass Erase are enabled for all of Flash program memory.

zilog

162

| Info Page<br>Address | Memory<br>Address | Compensation Usage      | ADC Mode                 | Reference<br>Type |

|----------------------|-------------------|-------------------------|--------------------------|-------------------|

| 60                   | FE60              | Offset                  | Single-Ended Unbuffered  | Internal 2.0 V    |

| 08                   | FE08              | Gain High Byte          | Single-Ended Unbuffered  | Internal 2.0 V    |

| 09                   | FE09              | Gain Low Byte           | Single-Ended Unbuffered  | Internal 2.0 V    |

| 63                   | FE63              | Offset                  | Single-Ended Unbuffered  | Internal 1.0 V    |

| 0A                   | FE0A              | Gain High Byte          | Single-Ended Unbuffered  | Internal 1.0 V    |

| 0B                   | FE0B              | Gain Low Byte           | Single-Ended Unbuffered  | Internal 1.0 V    |

| 66                   | FE66              | Offset                  | Single-Ended Unbuffered  | External 2.0 V    |

| 0C                   | FE0C              | Gain High Byte          | Single-Ended Unbuffered  | External 2.0 V    |

| 0D                   | FE0D              | Gain Low Byte           | Single-Ended Unbuffered  | External 2.0 V    |

| 69                   | FE69              | Offset                  | Single-Ended 1x Buffered | Internal 2.0 V    |

| 0E                   | FE0E              | Gain High Byte          | Single-Ended 1x Buffered | Internal 2.0 V    |

| 0F                   | FE0F              | Gain Low Byte           | Single-Ended 1x Buffered | Internal 2.0 V    |

| 6C                   | FE6C              | Offset                  | Single-Ended 1x Buffered | External 2.0 V    |

| 10                   | FE10              | Gain High Byte          | Single-Ended 1x Buffered | External 2.0 V    |

| 11                   | FE11              | Gain Low Byte           | Single-Ended 1x Buffered | External 2.0 V    |

| 6F                   | FE6F              | Offset                  | Differential Unbuffered  | Internal 2.0 V    |

| 12                   | FE12              | Positive Gain High Byte | Differential Unbuffered  | Internal 2.0 V    |

| 13                   | FE13              | Positive Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V    |

| 30                   | FE30              | Negative Gain High Byte | Differential Unbuffered  | Internal 2.0 V    |

| 31                   | FE31              | Negative Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V    |

| 72                   | FE72              | Offset                  | Differential Unbuffered  | Internal 1.0 V    |

| 14                   | FE14              | Positive Gain High Byte | Differential Unbuffered  | Internal 1.0 V    |

| 15                   | FE15              | Positive Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V    |

| 32                   | FE32              | Negative Gain High Byte | Differential Unbuffered  | Internal 1.0 V    |

| 33                   | FE33              | Negative Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V    |

| 75                   | FE75              | Offset                  | Differential Unbuffered  | External 2.0 V    |

| 16                   | FE16              | Positive Gain High Byte | Differential Unbuffered  | External 2.0 V    |

| 17                   | FE17              | Positive Gain Low Byte  | Differential Unbuffered  | External 2.0 V    |

|                      |                   |                         |                          |                   |

### Table 94. ADC Calibration Data Location

186

# zilog

#### 199

# eZ8 CPU Instruction Set

# **Assembly Language Programming Introduction**

The eZ8 CPU assembly language provides a means for writing an application program without concern for actual memory addresses or machine instruction formats. A program written in assembly language is called a source program. Assembly language allows the use of symbolic addresses to identify memory locations. It also allows mnemonic codes (opcodes and operands) to represent the instructions themselves. The opcodes identify the instruction while the operands represent memory locations, registers, or immediate data values.

Each assembly language program consists of a series of symbolic commands called statements. Each statement can contain labels, operations, operands and comments.

Labels can be assigned to a particular instruction step in a source program. The label identifies that step in the program as an entry point for use by other instructions.

The assembly language also includes assembler directives that supplement the machine instruction. The assembler directives, or pseudo-ops, are not translated into a machine instruction. Rather, the pseudo-ops are interpreted as directives that control or assist the assembly process.

The source program is processed (assembled) by the assembler to obtain a machine language program called the object code. The object code is executed by the eZ8 CPU. An example segment of an assembly language program is detailed in the following example.

#### Assembly Language Source Program Example

| JP START      | ; Everything after the semicolon is a comment.                                                                                                                                                                         |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:        | ; A label called 'START'. The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs.                                          |

| LD R4, R7     | ; A Load (LD) instruction with two operands. The first operand,<br>; Working Register R4, is the destination. The second operand,<br>; Working Register R7, is the source. The contents of R7 is<br>; written into R4. |

| LD 234H, #%01 | ; Another Load (LD) instruction with two operands.<br>; The first operand, Extended Mode Register Address 234H,<br>; identifies the destination. The second operand, Immediate Data                                    |

|               | ; value 01H, is the source. The value 01H is written into the ; Register at address 234H.                                                                                                                              |

| 2 | n | 0 |

|---|---|---|

| 4 | υ | 3 |

| Assembly        | Symbolic                                                                                         | Addres        | s Mode   | Opcode(s) |   |          | Fla | ags |   |   | Fetch  | Instr. |

|-----------------|--------------------------------------------------------------------------------------------------|---------------|----------|-----------|---|----------|-----|-----|---|---|--------|--------|

| Mnemonic        | Operation                                                                                        | dst           | src      | (Hex)     | С | Ζ        | S   | ۷   | D | Н | Cycles |        |

| COM dst         | $dst \gets \simdst$                                                                              | R             |          | 60        | - | *        | *   | 0   | - | - | 2      | 2      |

|                 |                                                                                                  | IR            |          | 61        | - |          |     |     |   |   | 2      | 3      |

| CP dst, src     | dst - src                                                                                        | r             | r        | A2        | * | *        | *   | *   | - | - | 2      | 3      |

|                 |                                                                                                  | r             | lr       | A3        | - |          |     |     |   |   | 2      | 4      |

|                 |                                                                                                  | R             | R        | A4        | - |          |     |     |   |   | 3      | 3      |

|                 |                                                                                                  | R             | IR       | A5        | - |          |     |     |   |   | 3      | 4      |

|                 |                                                                                                  | R             | IM       | A6        | - |          |     |     |   |   | 3      | 3      |

|                 |                                                                                                  | IR            | IM       | A7        | - |          |     |     |   |   | 3      | 4      |

| CPC dst, src    | dst - src - C                                                                                    | r             | r        | 1F A2     | * | *        | *   | *   | - | - | 3      | 3      |

|                 |                                                                                                  | r             | lr       | 1F A3     | - |          |     |     |   |   | 3      | 4      |

|                 |                                                                                                  | R             | R        | 1F A4     | - |          |     |     |   |   | 4      | 3      |

|                 |                                                                                                  | R             | IR       | 1F A5     | - |          |     |     |   |   | 4      | 4      |

|                 |                                                                                                  | R             | IM       | 1F A6     | - |          |     |     |   |   | 4      | 3      |

|                 |                                                                                                  | IR            | IM       | 1F A7     | - |          |     |     |   |   | 4      | 4      |

| CPCX dst, src   | dst - src - C                                                                                    | ER            | ER       | 1F A8     | * | *        | *   | *   | _ | _ | 5      | 3      |

|                 |                                                                                                  | ER            | IM       | 1F A9     | - |          |     |     |   |   | 5      | 3      |

| CPX dst, src    | dst - src                                                                                        | ER            | ER       | A8        | * | *        | *   | *   | _ | _ | 4      | 3      |

|                 |                                                                                                  | ER            | IM       | A9        | - |          |     |     |   |   | 4      | 3      |

| DA dst          | $dst \gets DA(dst)$                                                                              | R             |          | 40        | * | *        | *   | Х   | _ | _ | 2      | 2      |

|                 |                                                                                                  | IR            |          | 41        | - |          |     |     |   |   | 2      | 3      |

| DEC dst         | $dst \gets dst \text{ - } 1$                                                                     | R             |          | 30        | _ | *        | *   | *   | _ | _ | 2      | 2      |

|                 |                                                                                                  | IR            |          | 31        | - |          |     |     |   |   | 2      | 3      |

| DECW dst        | $dst \gets dst \text{ - } 1$                                                                     | RR            |          | 80        | _ | *        | *   | *   | _ | _ | 2      | 5      |

|                 |                                                                                                  | IRR           |          | 81        | - |          |     |     |   |   | 2      | 6      |

| DI              | $IRQCTL[7] \leftarrow 0$                                                                         |               |          | 8F        | _ | _        | _   | _   | _ | _ | 1      | 2      |

| DJNZ dst, RA    | $\begin{array}{l} dst \leftarrow dst - 1 \\ if \ dst \neq 0 \\ PC \leftarrow PC + X \end{array}$ | r             |          | 0A-FA     | _ | _        | _   | _   | _ | _ | 2      | 3      |

| EI              | $IRQCTL[7] \leftarrow 1$                                                                         |               |          | 9F        | _ | -        | -   | _   | - | - | 1      | 2      |

| Flags Notation: | * = Value is a function<br>– = Unaffected<br>X = Undefined                                       | of the result | of the o | peration. |   | Re<br>Se |     |     | ) |   |        |        |

## Table 124. eZ8 CPU Instruction Summary (Continued)

# 210

| Assembly        | Symbolic                                                                                                          | Addres        | s Mode   | Opcode(s) |   |              | Fla | ags |   |   | _ Fetch | Instr. |

|-----------------|-------------------------------------------------------------------------------------------------------------------|---------------|----------|-----------|---|--------------|-----|-----|---|---|---------|--------|

| Mnemonic        | Operation                                                                                                         | dst           | src      | (Hex)     | С | Ζ            | S   | ۷   | D | Н | Cycles  |        |

| HALT            | Halt Mode                                                                                                         |               |          | 7F        | - | -            | -   | -   | - | - | 1       | 2      |

| INC dst         | $dst \gets dst + 1$                                                                                               | R             |          | 20        | _ | *            | *   | _   | - | _ | 2       | 2      |

|                 |                                                                                                                   | IR            |          | 21        | - |              |     |     |   |   | 2       | 3      |

|                 |                                                                                                                   | r             |          | 0E-FE     | - |              |     |     |   |   | 1       | 2      |

| INCW dst        | $dst \gets dst + 1$                                                                                               | RR            |          | A0        | - | *            | *   | *   | - | - | 2       | 5      |

|                 |                                                                                                                   | IRR           |          | A1        | - |              |     |     |   |   | 2       | 6      |

| IRET            | $FLAGS \leftarrow @SP$ $SP \leftarrow SP + 1$ $PC \leftarrow @SP$ $SP \leftarrow SP + 2$ $IRQCTL[7] \leftarrow 1$ |               |          | BF        | * | *            | *   | *   | * | * | 1       | 5      |

| JP dst          | $PC \gets dst$                                                                                                    | DA            |          | 8D        | - | _            | _   | _   | - | - | 3       | 2      |

|                 |                                                                                                                   | IRR           |          | C4        | - |              |     |     |   |   | 2       | 3      |

| JP cc, dst      | if cc is true $PC \leftarrow dst$                                                                                 | DA            |          | 0D-FD     | - | -            | _   | -   | - | - | 3       | 2      |

| JR dst          | $PC \gets PC + X$                                                                                                 | DA            |          | 8B        | - | -            | -   | -   | - | - | 2       | 2      |

| JR cc, dst      | if cc is true<br>PC $\leftarrow$ PC + X                                                                           | DA            |          | 0B-FB     | _ | _            | _   | _   | _ | _ | 2       | 2      |

| LD dst, rc      | $dst \gets src$                                                                                                   | r             | IM       | 0C-FC     | - | _            | _   | _   | - | - | 2       | 2      |

|                 |                                                                                                                   | r             | X(r)     | C7        | - |              |     |     |   |   | 3       | 3      |

|                 |                                                                                                                   | X(r)          | r        | D7        | - |              |     |     |   |   | 3       | 4      |

|                 |                                                                                                                   | r             | lr       | E3        | - |              |     |     |   |   | 2       | 3      |

|                 |                                                                                                                   | R             | R        | E4        | - |              |     |     |   |   | 3       | 2      |

|                 |                                                                                                                   | R             | IR       | E5        | - |              |     |     |   |   | 3       | 4      |

|                 |                                                                                                                   | R             | IM       | E6        | - |              |     |     |   |   | 3       | 2      |

|                 |                                                                                                                   | IR            | IM       | E7        | - |              |     |     |   |   | 3       | 3      |

|                 |                                                                                                                   | lr            | r        | F3        | - |              |     |     |   |   | 2       | 3      |

|                 |                                                                                                                   | IR            | R        | F5        | - |              |     |     |   |   | 3       | 3      |

| Flags Notation: | * = Value is a function<br>– = Unaffected<br>X = Undefined                                                        | of the result | of the o | peration. |   | ⊧ Re<br>⊧ Se |     |     | ) |   |         |        |

## Table 124. eZ8 CPU Instruction Summary (Continued)

# 215

| Assembly        | Symbolic                                                      | Addres     | s Mode   | Opcode(s) |   |              | FI | ags       |   |   | Fetch | Instr. |

|-----------------|---------------------------------------------------------------|------------|----------|-----------|---|--------------|----|-----------|---|---|-------|--------|

| Mnemonic        | Operation                                                     | dst        | src      | (Hex)     | С | Ζ            | S  | ۷         | D | Н |       | Cycles |

| XOR dst, src    | $dst \gets dst \ XOR \ src$                                   | r          | r        | B2        | _ | *            | *  | 0         | _ | - | 2     | 3      |

|                 |                                                               | r          | lr       | B3        | - |              |    |           |   |   | 2     | 4      |

|                 |                                                               | R          | R        | B4        | - |              |    |           |   |   | 3     | 3      |

|                 |                                                               | R          | IR       | B5        | - |              |    |           |   |   | 3     | 4      |

|                 |                                                               | R          | IM       | B6        | - |              |    |           |   |   | 3     | 3      |

|                 |                                                               | IR         | IM       | B7        | - |              |    |           |   |   | 3     | 4      |

| XORX dst, src   | $dst \gets dst \ XOR \ src$                                   | ER         | ER       | B8        | - | *            | *  | 0         | _ | - | 4     | 3      |

|                 |                                                               | ER         | IM       | B9        | - |              |    |           |   |   | 4     | 3      |

| Flags Notation: | * = Value is a function of<br>– = Unaffected<br>X = Undefined | the result | of the o | peration. | - | : Re<br>: Se |    | to (<br>1 | C |   |       |        |

## Table 124. eZ8 CPU Instruction Summary (Continued)

# Packaging

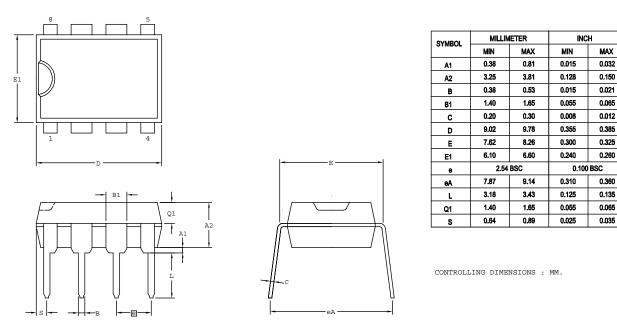

Figure 39 displays the 8-pin Plastic Dual Inline Package (PDIP) available for Z8 Encore!  $XP^{\textcircled{R}}$  F082A Series devices.

Figure 39. 8-Pin Plastic Dual Inline Package (PDIP)

Zilog 244

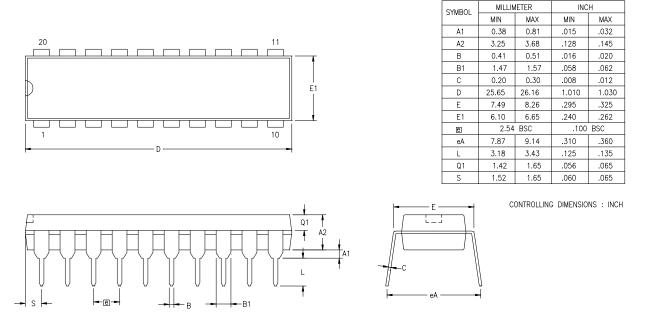

Figure 42 displays the 20-pin Plastic Dual Inline Package (PDIP) available for the Z8 Encore! XP F082A Series devices.

Figure 42. 20-Pin Plastic Dual Inline Package (PDIP)

**z**ilog<sup>°</sup>

## 251

# **Ordering Information**

Order the Z8 Encore! XP<sup>®</sup> F082A Series from Zilog<sup>®</sup>, using the following part numbers. For more information on ordering, please consult your local Zilog sales office. The Zilog website (<u>www.zilog.com</u>) lists all regional offices and provides additional Z8 Encore! XP product information.

| Part Number                                              | Flash    | RAM      | NVDS | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|----------------------------------------------------------|----------|----------|------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082/<br>Standard Temperature |          |          |      | asn, 1    | 0-ЫІ       | Ana                 | iog-t               | טום-ס          |            | Jony               | verter              |

| Z8F082APB020SC                                           | 8 KB     | 1 KB     | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082AQB020SC                                           | 8 KB     | 1 KB     | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020SC                                           | 8 KB     | 1 KB     | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020SC                                           | 8 KB     | 1 KB     | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020SC                                           | 8 KB     | 1 KB     | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020SC                                           | 8 KB     | 1 KB     | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F082ASJ020SC                                           | 8 KB     | 1 KB     | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020SC                                           | 8 KB     | 1 KB     | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020SC                                           | 8 KB     | 1 KB     | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperatur                                      | e: -40 ° | C to 10  | 5 °C |           |            |                     |                     |                |            |                    |                     |

| Z8F082APB020EC                                           | 8 KB     | 1 KB     | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082AQB020EC                                           | 8 KB     | 1 KB     | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020EC                                           | 8 KB     | 1 KB     | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020EC                                           | 8 KB     | 1 KB     | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020EC                                           | 8 KB     | 1 KB     | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020EC                                           | 8 KB     | 1 KB     | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F082ASJ020EC                                           | 8 KB     | 1 KB     | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020EC                                           | 8 KB     | 1 KB     | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020EC                                           | 8 KB     | 1 KB     | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Replace C with G for Lead                                | d-Free P | ackaging |      |           |            |                     |                     |                |            |                    |                     |

zilog 257

| Part Number                     | Flash     | RAM      | SUVN   | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------|-----------|----------|--------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082 | A Serie   | s with 1 | KB Fla | ish, 1    | 0-Bit      | Ana                 | log-t               | o-Dig          | jital C    | Conv               | verter              |

| Standard Temperatu              | re: 0 °C  | to 70 °C | ;      |           |            |                     |                     |                |            |                    |                     |

| Z8F012APB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperatu              | re: -40 ° | C to 10  | 5 °C   |           |            |                     |                     |                |            |                    |                     |

| Z8F012APB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |