# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | IrDA, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT               |

| Number of I/O              | 25                                                            |

| Program Memory Size        | 1KB (1K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | 16 x 8                                                        |

| RAM Size                   | 256 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | -                                                             |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f011asj020ec00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Zilog <sub>42</sub>

| Port   | Pin | Mnemonic    | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------|--------------------------------|-----------------------------------------|

| Port B | PB0 | Reserved    |                                | AFS1[0]: 0                              |

|        |     | ANA0/AMPOUT | ADC Analog Input/LPO Output    | AFS1[0]: 1                              |

|        | PB1 | Reserved    |                                | AFS1[1]: 0                              |

|        |     | ANA1/AMPINN | AFS1[1]: 1                     |                                         |

|        | PB2 | Reserved    |                                | AFS1[2]: 0                              |

|        |     | ANA2/AMPINP | AFS1[2]: 1                     |                                         |

| F      | PB3 | CLKIN       | External Clock Input           | AFS1[3]: 0                              |

|        |     | ANA3        | ADC Analog Input               | AFS1[3]: 1                              |

|        | PB4 | Reserved    |                                | AFS1[4]: 0                              |

|        |     | ANA7        | ADC Analog Input               | AFS1[4]: 1                              |

|        | PB5 | Reserved    |                                | AFS1[5]: 0                              |

|        |     | VREF*       | ADC Voltage Reference          | AFS1[5]: 1                              |

|        | PB6 | Reserved    |                                | AFS1[6]: 0                              |

|        |     | Reserved    |                                | AFS1[6]: 1                              |

|        | PB7 | Reserved    |                                | AFS1[7]: 0                              |

|        |     | Reserved    |                                | AFS1[7]: 1                              |

#### Table 14. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Note: Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set register AFS2 is not used to select the function. Also, alternate function selection as described in Port A-D Alternate Function Sub-Registers on page 47 must also be enabled.

\* VREF is available on PB5 in 28-pin products only.

zilog<sup>®</sup>

Set 1 Sub-Registers on page 50, GPIO Alternate Functions on page 38, and Port A–D Alternate Function Set 2 Sub-Registers on page 51. See GPIO Alternate Functions on page 38 to determine the alternate function associated with each port pin.

Caution:

Do not enable alternate functions for GPIO port pins for which there is no associated alternate function. Failure to follow this guideline can result in unpredictable operation.

| Table 20. Port A–D Alternate Function Sub-Registers | (PxAF) |  |

|-----------------------------------------------------|--------|--|

|                                                     |        |  |

| BITS  | 7        | 6                                                           | 5           | 4             | 3            | 2             | 1            | 0        |  |  |  |  |

|-------|----------|-------------------------------------------------------------|-------------|---------------|--------------|---------------|--------------|----------|--|--|--|--|

| FIELD | AF7      | AF6                                                         | AF5         | AF4           | AF4 AF3      |               | AF1          | AF0      |  |  |  |  |

| RESET |          | 00H (Ports A–C); 01H (Port D); 04H (Port A of 8-pin device) |             |               |              |               |              |          |  |  |  |  |

| R/W   |          | R/W                                                         |             |               |              |               |              |          |  |  |  |  |

| ADDR  | lf 02H i | n Port A–D /                                                | Address Reg | gister, acces | sible throug | n the Port A- | –D Control F | Register |  |  |  |  |

AF[7:0]—Port Alternate Function enabled

0 = The port pin is in normal mode and the DDx bit in the Port A–D Data Direction sub-register determines the direction of the pin.

1 = The alternate function selected through Alternate Function Set sub-registers is enabled. Port pin operation is controlled by the alternate function.

## Port A–D Output Control Sub-Registers

The Port A–D Output Control sub-register (Table 21) is accessed through the Port A–D Control register by writing 03H to the Port A–D Address register. Setting the bits in the Port A–D Output Control sub-registers to 1 configures the specified port pins for opendrain operation. These sub-registers affect the pins directly and, as a result, alternate functions are also affected.

#### Table 21. Port A–D Output Control Sub-Registers (PxOC)

| BITS  | 7        | 6                       | 5           | 4             | 3             | 2             | 1            | 0        |  |  |  |  |

|-------|----------|-------------------------|-------------|---------------|---------------|---------------|--------------|----------|--|--|--|--|

| FIELD | POC7     | POC6                    | POC5        | POC4          | POC3          | POC2          | POC1         | POC0     |  |  |  |  |

| RESET |          |                         | 001         | H (Ports A-C  | c); 01H (Port | D)            |              |          |  |  |  |  |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W |             |               |               |               |              |          |  |  |  |  |

| ADDR  | lf 03H i | n Port A–D              | Address Reg | gister, acces | sible throug  | n the Port A- | -D Control F | Register |  |  |  |  |

POC[7:0]—Port Output Control

These bits function independently of the alternate function bit and always disable the drains if set to 1.

0 = The source current is enabled for any output mode (unless overridden by the alternate

function). (Push-pull output)

1 = The source current for the associated pin is disabled (open-drain mode).

#### Port A–D High Drive Enable Sub-Registers

The Port A–D High Drive Enable sub-register (Table 22) is accessed through the Port A–D Control register by writing 04H to the Port A–D Address register. Setting the bits in the Port A–D High Drive Enable sub-registers to 1 configures the specified port pins for high current output drive operation. The Port A–D High Drive Enable sub-register affects the pins directly and, as a result, alternate functions are also affected.

Table 22. Port A–D High Drive Enable Sub-Registers (PxHDE)

| BITS  | 7        | 6                           | 5           | 4             | 3             | 2             | 1            | 0        |  |  |  |  |

|-------|----------|-----------------------------|-------------|---------------|---------------|---------------|--------------|----------|--|--|--|--|

| FIELD | PHDE7    | PHDE6                       | PHDE5       | PHDE4         | PHDE3         | PHDE2         | PHDE1        | PHDE0    |  |  |  |  |

| RESET | 0        | 0                           | 0           | 0             | 0             | 0             | 0            | 0        |  |  |  |  |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W |             |               |               |               |              |          |  |  |  |  |

| ADDR  | lf 04H i | n Port A–D /                | Address Reg | gister, acces | sible through | n the Port A- | -D Control F | Register |  |  |  |  |

PHDE[7:0]—Port High Drive Enabled

0 = The Port pin is configured for standard output current drive.

1 = The Port pin is configured for high output current drive.

#### Port A–D Stop Mode Recovery Source Enable Sub-Registers

The Port A–D Stop Mode Recovery Source Enable sub-register (Table 23) is accessed through the Port A–D Control register by writing 05H to the Port A–D Address register. Setting the bits in the Port A–D Stop Mode Recovery Source Enable sub-registers to 1 configures the specified Port pins as a Stop Mode Recovery source. During STOP mode, any logic transition on a Port pin enabled as a Stop Mode Recovery source initiates Stop Mode Recovery.

| BITS  | 7        | 6                           | 5           | 4             | 3            | 2             | 1            | 0        |  |  |  |  |

|-------|----------|-----------------------------|-------------|---------------|--------------|---------------|--------------|----------|--|--|--|--|

| FIELD | PSMRE7   | PSMRE6                      | PSMRE5      | PSMRE4        | PSMRE3       | PSMRE2        | PSMRE1       | PSMRE0   |  |  |  |  |

| RESET | 0        | 0                           | 0           | 0             | 0            | 0             | 0            | 0        |  |  |  |  |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W |             |               |              |               |              |          |  |  |  |  |

| ADDR  | lf 05H i | n Port A–D                  | Address Reg | gister, acces | sible throug | h the Port A- | -D Control F | Register |  |  |  |  |

PSMRE[7:0]—Port Stop Mode Recovery Source Enabled

0 = The Port pin is not configured as a Stop Mode Recovery source. Transitions on this pin

Interrupts are globally enabled by any of the following actions:

- Execution of an EI (Enable Interrupt) instruction

- Execution of an IRET (Return from Interrupt) instruction

- Writing a 1 to the IRQE bit in the Interrupt Control register

Interrupts are globally disabled by any of the following actions:

- Execution of a DI (Disable Interrupt) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller

- Writing a 0 to the IRQE bit in the Interrupt Control register

- Reset

- Execution of a Trap instruction

- Illegal Instruction Trap

- Primary Oscillator Fail Trap

- Watchdog Oscillator Fail Trap

## **Interrupt Vectors and Priority**

The interrupt controller supports three levels of interrupt priority. Level 3 is the highest priority, Level 2 is the second highest priority, and Level 1 is the lowest priority. If all of the interrupts are enabled with identical interrupt priority (all as Level 2 interrupts, for example), the interrupt priority is assigned from highest to lowest as specified in Table 32 on page 56. Level 3 interrupts are always assigned higher priority than Level 2 interrupts which, in turn, always are assigned higher priority than Level 1 interrupts. Within each interrupt priority level (Level 1, Level 2, or Level 3), priority is assigned as specified in Table 32, above. Reset, Watchdog Timer interrupt (if enabled), Primary Oscillator Fail Trap, Watchdog Oscillator Fail Trap, and Illegal Instruction Trap always have highest (level 3) priority.

#### **Interrupt Assertion**

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the Interrupt Request register is cleared until the next interrupt occurs. Writing a 0 to the corresponding bit in the Interrupt Request register likewise clears the interrupt request.

62

## Interrupt Request 2 Register

The Interrupt Request 2 (IRQ2) register (Table 35) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 register to determine if any interrupt requests are pending.

#### Table 35. Interrupt Request 2 Register (IRQ2)

| BITS  | 7   | 6    | 5     | 4   | 3    | 2    | 1    | 0    |

|-------|-----|------|-------|-----|------|------|------|------|

| FIELD |     | Rese | erved |     | PC3I | PC2I | PC1I | PC0I |

| RESET | 0   | 0    | 0     | 0   | 0    | 0    | 0    | 0    |

| R/W   | R/W | R/W  | R/W   | R/W | R/W  | R/W  | R/W  | R/W  |

| ADDR  |     |      |       | FC  | 6H   |      |      |      |

Reserved—Must be 0.

PCxI—Port C Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port C pin x.

1 = An interrupt request from GPIO Port C pin x is awaiting service.

where x indicates the specific GPIO Port C pin number (0-3).

## **IRQ0 Enable High and Low Bit Registers**

Table 36 describes the priority control for IRQ0. The IRQ0 Enable High and Low Bit registers (Table 37 and Table 38) form a priority encoded enabling for interrupts in the Interrupt Request 0 register.

#### Table 36. IRQ0 Enable and Priority Encoding

| IRQ0ENH[x] | IRQ0ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Medium      |

| 1          | 1          | Level 3  | High        |

where x indicates the register bits from 0–7.

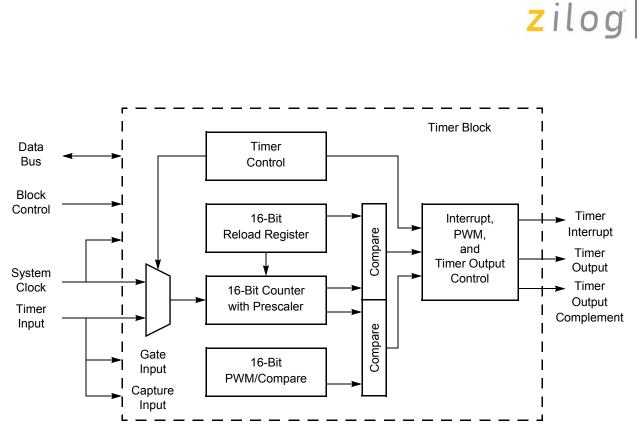

Figure 9. Timer Block Diagram

## Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

## **Timer Operating Modes**

The timers can be configured to operate in the following modes:

#### **ONE-SHOT Mode**

In ONE-SHOT mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. The timer is automatically disabled and stops counting.

70

Z8 Encore! XP<sup>®</sup> F082A Series

**Product Specification**

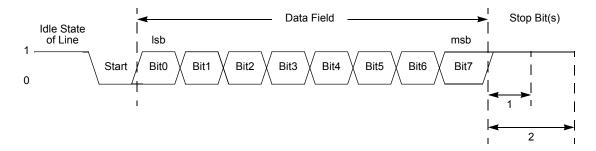

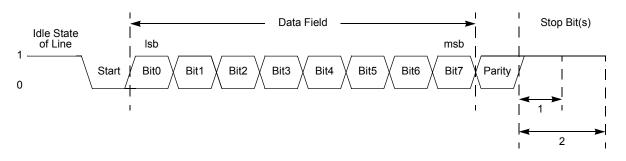

Figure 11. UART Asynchronous Data Format without Parity

Figure 12. UART Asynchronous Data Format with Parity

## Transmitting Data using the Polled Method

Follow the steps below to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Write to the UART Control 1 register, if MULTIPROCESSOR mode is appropriate, to enable MULTIPROCESSOR (9-bit) mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR mode.

- 5. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR mode is not enabled, and select either even or odd parity (PSEL).

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin.

zilog 1

- If the internal voltage reference must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- Set CEN to 1 to start the conversion.

- 4. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered-down state, the ADC uses 40 additional clock cycles to power up before beginning the 5129 cycle conversion.

- 5. When the conversion is complete, the ADC control logic performs the following operations:

- 13-bit two's-complement result written to {ADCD\_H[7:0], ADCD\_L[7:3]}.

- Sends an interrupt request to the Interrupt Controller denoting conversion complete.

- CEN resets to 0 to indicate the conversion is complete.

- 6. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered-down.

## **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analog-to-digital conversion on the selected analog input. Each new data value over-writes the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS mode, ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not immediately detected at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Follow the steps below for setting up the ADC and initiating continuous conversion:

- 1. Enable the desired analog input by configuring the general-purpose I/O pins for alternate function. This action disables the digital input and output driver.

- 2. Write the ADC Control/Status Register 1 to configure the ADC.

- Write to BUFMODE[2:0] to select SINGLE-ENDED or DIFFERENTIAL mode, as well as unbuffered or buffered mode.

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in the ADC Control Register 0.

zilog

##

**Caution:** Although the ADC can be used without the gain and offset compensation, it does exhibit non-unity gain. Designing the ADC with sub-unity gain reduces noise across the ADC range but requires the ADC results to be scaled by a factor of 8/7.

## **ADC Compensation Details**

High efficiency assembly code that performs this compensation is available for download on <u>www.zilog.com</u>. The following is a bit-specific description of the ADC compensation process used by this code.

The following data bit definitions are used:

0-9, a-f = bit indices in hexadecimal

s = sign bit

v = overflow bit

- = unused

#### Input Data

| MS             | βB           |     |   |     |     | LS | В |   |   |             |                                                   |

|----------------|--------------|-----|---|-----|-----|----|---|---|---|-------------|---------------------------------------------------|

| sba9           | 876          | 5 5 | 4 | 3 2 | 2 1 | 0  | - | - | v | (ADC)       | ADC Output Word; if $v = 1$ , the data is invalid |

|                |              |     | S | 6 5 | 54  | 3  | 2 | 1 | 0 |             | Offset Correction Byte                            |

| <u>s s s s</u> | <u>s 7 6</u> | 5 5 | 4 | 3 2 | 2 1 | 0  | 0 | 0 | 0 | (Offset)    | Offset Byte shifted to align with ADC data        |

| sedc           | b a S        | 98  | 7 | 6 5 | 54  | 3  | 2 | 1 | 0 | (Gain)<br>] | Gain Correction Word                              |

|                |              |     |   |     |     |    |   |   |   | ]           |                                                   |

| [              |              |     |   |     |     |    |   |   |   | 1           |                                                   |

Zilog 14

the OCD or via the Flash Controller Bypass mode are unaffected. After a bit of the Sector Protect Register has been set, it cannot be cleared except by powering down the device.

## **Byte Programming**

The Flash Memory is enabled for byte programming after unlocking the Flash Controller and successfully enabling either Mass Erase or Page Erase. When the Flash Controller is unlocked and Mass Erase is successfully completed, all Program Memory locations are available for byte programming. In contrast, when the Flash Controller is unlocked and Page Erase is successfully completed, only the locations of the selected page are available for byte programming. An erased Flash byte contains all 1's (FFH). The programming operation can only be used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from 0 to 1 requires execution of either the Page Erase or Mass Erase commands.

Byte Programming can be accomplished using the On-Chip Debugger's Write Memory command or eZ8 CPU execution of the LDC or LDCI instructions. Refer to the *eZ8 CPU User Manual* (available for download at <u>www.zilog.com</u>) for a description of the LDC and LDCI instructions. While the Flash Controller programs the Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. To exit programming mode and lock the Flash, write any value to the Flash Control register, except the Mass Erase or Page Erase commands.

**Caution:** The byte at each address of the Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs. Doing so may result in corrupted data at the target byte.

#### Page Erase

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

#### Mass Erase

The Flash memory can also be Mass Erased using the Flash Controller, but only by using the On-Chip Debugger. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the Mass Erase successfully enabled, writing the

**z**ilog<sup>°</sup>

## **Option Bit Types**

#### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. User access to these bits has been provided because these locations contain application-specific device configurations. The information contained here is lost when page 0 of the program memory is erased.

#### **Trim Option Bits**

The trim option bits are contained in the information page of the Flash memory. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered. Program Memory may be erased without endangering these values. It is possible to alter working values of these bits by accessing the Trim Bit Address and Data Registers, but these working values are lost after a power loss or any other reset event.

There are 32 bytes of trim data. To modify one of these values the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data register returns the working value of the target trim data byte.

The trim address range is from information address 20-3F only. The remainder of the information page is not accessible through the trim bit address and data registers.

#### **Calibration Option Bits**

The calibration option bits are also contained in the information page. These bits are factory programmed values intended for use in software correcting the device's analog performance. To read these values, the user code must employ the LDC instruction to access the information area of the address space as defined in See Flash Information Area on page 17.

#### **Serialization Bits**

As an optional feature, Zilog<sup>®</sup> is able to provide factory-programmed serialization. For serialized products, the individual devices are programmed with unique serial numbers. These serial numbers are binary values, four bytes in length. The numbers increase in size with each device, but gaps in the serial sequence may exist.

These serial numbers are stored in the Flash information page (see Reading the Flash Information Page on page 155 and Serialization Data on page 165 for more details) and are unaffected by mass erasure of the device's Flash memory.

Note:

#### 158

## Flash Program Memory Address 0001H

#### Table 87. Flash Options Bits at Program Memory Address 0001H

| BITS       | 7                    | 6           | 5            | 4        | 3        | 2   | 1   | 0   |  |  |  |

|------------|----------------------|-------------|--------------|----------|----------|-----|-----|-----|--|--|--|

| FIELD      |                      | Reserved    |              | XTLDIS   | Reserved |     |     |     |  |  |  |

| RESET      | U                    | U           | U            | U        | U U U U  |     |     |     |  |  |  |

| R/W        | R/W                  | R/W         | R/W          | R/W      | R/W      | R/W | R/W | R/W |  |  |  |

| ADDR       | Program Memory 0001H |             |              |          |          |     |     |     |  |  |  |

| Note:    = | Inchanged h          | v Reset R/W | = Read/Write | <u>د</u> |          |     |     |     |  |  |  |

**Note:** U = Unchanged by Reset. R/W = Read/Write.

Reserved—Must be 1.

XTLDIS—State of Crystal Oscillator at Reset.

- **Note:** *This bit only enables the crystal oscillator. Its selection as system clock must be done manually.*

- 0 = Crystal oscillator is enabled during reset, resulting in longer reset timing

- *I* = *Crystal oscillator is disabled during reset, resulting in shorter reset timing*

Warning: Programming the XTLDIS bit to zero on 8-pin versions of this device prevents any further communication via the debug pin. This is due to the fact that the XIN and DBG functions are shared on pin 2 of this package. Do not program this bit to zero on 8-pin devices unless no further debugging or Flash programming is required.

## **Trim Bit Address Space**

All available Trim bit addresses and their functions are listed in Table 88 through Table 92.

## Trim Bit Address 0000H

| Table 88. Trim Options | Bits at Address 0000H |

|------------------------|-----------------------|

|------------------------|-----------------------|

| BITS      | 7                             | 6               | 5 4 3 2 1 0  |     |     |     |     |     |  |  |  |  |  |

|-----------|-------------------------------|-----------------|--------------|-----|-----|-----|-----|-----|--|--|--|--|--|

| FIELD     |                               | Reserved        |              |     |     |     |     |     |  |  |  |  |  |

| RESET     | U                             | U U U U U U U U |              |     |     |     |     |     |  |  |  |  |  |

| R/W       | R/W                           | R/W             | R/W          | R/W | R/W | R/W | R/W | R/W |  |  |  |  |  |

| ADDR      | Information Page Memory 0020H |                 |              |     |     |     |     |     |  |  |  |  |  |

| Note: U = | Unchanged b                   | y Reset. R/W    | = Read/Write | ).  |     |     |     |     |  |  |  |  |  |

Reserved—Altering this register may result in incorrect device operation.

## Trim Bit Address 0004H

## Table 92. Trim Option Bits at 0004H

| BITS      | 7           | 6               | 5            | 4           | 3           | 2    | 1   | 0   |  |  |  |  |  |

|-----------|-------------|-----------------|--------------|-------------|-------------|------|-----|-----|--|--|--|--|--|

| FIELD     |             | Reserved        |              |             |             |      |     |     |  |  |  |  |  |

| RESET     | U           | U U U U U U U U |              |             |             |      |     |     |  |  |  |  |  |

| R/W       | R/W         | R/W             | R/W          | R/W         | R/W         | R/W  | R/W | R/W |  |  |  |  |  |

| ADDR      |             |                 | Infor        | mation Page | e Memory 00 | )24H |     |     |  |  |  |  |  |

| Note: U = | Jnchanged b | y Reset. R/W    | = Read/Write | <b>)</b> .  |             |      |     |     |  |  |  |  |  |

Reserved—Altering this register may result in incorrect device operation.

## Zilog Calibration Data

## ADC Calibration Data

## Table 93. ADC Calibration Bits

| BITS      | 7                                   | 6               | 5 4 3 2 1 0  |     |     |     |     |     |  |  |  |  |  |

|-----------|-------------------------------------|-----------------|--------------|-----|-----|-----|-----|-----|--|--|--|--|--|

| FIELD     |                                     | ADC_CAL         |              |     |     |     |     |     |  |  |  |  |  |

| RESET     | U                                   | U U U U U U U U |              |     |     |     |     |     |  |  |  |  |  |

| R/W       | R/W                                 | R/W             | R/W          | R/W | R/W | R/W | R/W | R/W |  |  |  |  |  |

| ADDR      | Information Page Memory 0060H–007DH |                 |              |     |     |     |     |     |  |  |  |  |  |

| Note: U = | Unchanged b                         | y Reset. R/W    | = Read/Write |     |     |     |     |     |  |  |  |  |  |

ADC\_CAL—Analog-to-Digital Converter Calibration Values

Contains factory calibrated values for ADC gain and offset compensation. Each of the ten supported modes has one byte of offset calibration and two bytes of gain calibration. These values are read by the software to compensate ADC measurements as described in Software Compensation Procedure Using Factory Calibration Data on page 126. The location of each calibration byte is provided in Table 94 on page 162.

# zilog

# **Internal Precision Oscillator**

The internal precision oscillator (IPO) is designed for use without external components. You can either manually trim the oscillator for a non-standard frequency or use the automatic factory-trimmed version to achieve a 5.53 MHz frequency. IPO features include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8 kHz (contains both a fast and a slow mode)

- Trimmed through Flash option bits with user override

- Elimination of crystals or ceramic resonators in applications where very high timing accuracy is not required

## Operation

An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed the oscillator frequency is stable and does not require subsequent calibration. Trimming is performed during manufacturing and is not necessary for you to repeat unless a frequency other than 5.53 MHz (fast mode) or 32.8 kHz (slow mode) is required. This trimming is done at +30 °C and a supply voltage of 3.3 V, so accuracy of this operating point is optimal.

If not used, the IPO can be disabled by the Oscillator Control register (see Oscillator Control Register Definitions on page 190).

By default, the oscillator frequency is set by the factory trim value stored in the write-protected Flash information page. However, the user code can override these trim values as described in Trim Bit Address Space on page 158.

Select one of two frequencies for the oscillator: 5.53 MHz and 32.8 kHz, using the OSCSEL bits in the Oscillator Control on page 187.

**z**ilog<sup>°</sup>

|   |                   |              |                     |                  |                     |               | Lo           | ower Ni       | bble (He        | x)             |              |            |             |             |           |           |

|---|-------------------|--------------|---------------------|------------------|---------------------|---------------|--------------|---------------|-----------------|----------------|--------------|------------|-------------|-------------|-----------|-----------|

|   | 0                 | 1            | 2                   | 3                | 4                   | 5             | 6            | 7             | 8               | 9              | А            | В          | С           | D           | Е         | F         |

| • | 1.1               | 2.2          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            | 2.3          | 2.2        | 2.2         | 3.2         | 1.2       | 1.2       |

| 0 | BRK               | SRP<br>IM    | <b>ADD</b><br>r1,r2 | ADD<br>r1,lr2    | <b>ADD</b><br>R2,R1 | ADD<br>IR2,R1 | ADD<br>R1,IM | ADD<br>IR1,IM | ADDX<br>ER2,ER1 | ADDX<br>IM,ER1 | DJNZ<br>r1,X | JR<br>cc,X | LD<br>r1,IM | JP<br>cc,DA | INC<br>r1 | NO        |

|   | 2.2               | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            | ,            |            | ,           | 00,271      | 1         | See       |

| 1 | RLC               | RLC          | ADC                 | ADC              | ADC                 | ADC           | ADC          | ADC           | ADCX            | ADCX           |              |            |             |             |           | Орсо      |

|   | R1                | IR1          | r1,r2               | r1,Ir2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           | Ma        |

|   | 2.2               | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1,        |

| 2 | INC<br>R1         | INC<br>IR1   | <b>SUB</b><br>r1,r2 | SUB<br>r1,lr2    | <b>SUB</b><br>R2,R1 | SUB<br>IR2,R1 | SUB<br>R1,IM | SUB<br>IR1,IM | SUBX<br>ER2,ER1 | SUBX<br>IM,ER1 |              |            |             |             |           | AT        |

|   | 2.2               | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           |           |

| 3 | DEC               | DEC          | SBC                 | SBC              | SBC                 | SBC           | SBC          | SBC           | SBCX            | SBCX           |              |            |             |             |           |           |

| - | R1                | IR1          | r1,r2               | r1,lr2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2               | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           |           |

| 4 | DA                | DA           | OR                  | OR               | OR                  | OR            | OR           | OR            | ORX             | ORX            |              |            |             |             |           |           |

|   | R1                | IR1          | r1,r2               | r1,Ir2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| 5 | 2.2<br><b>POP</b> | 2.3<br>POP   | 2.3<br>AND          | 2.4<br>AND       | 3.3<br>AND          | 3.4<br>AND    | 3.3<br>AND   | 3.4<br>AND    | 4.3<br>ANDX     | 4.3<br>ANDX    |              |            |             |             |           | 1.:<br>WE |

| 5 | R1                | IR1          | r1,r2               | r1,lr2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           | VVL       |

|   | 2.2               | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.3       |

| 6 | СОМ               | COM          | ТСМ                 | ТСМ              | TCM                 | TCM           | тсм          | TCM           | тсмх            | тсмх           |              |            |             |             |           | STO       |

|   | R1                | IR1          | r1,r2               | r1,lr2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2               | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.2       |

| 7 | PUSH              | PUSH         | ТМ                  | TM               | TM                  | TM            | ТМ           | TM            | TMX             | TMX            |              |            |             |             |           | HA        |

|   | R2                | IR2          | r1,r2               | r1,lr2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| 8 | 2.5<br>DECW       | 2.6<br>DECW  | 2.5<br>LDE          | 2.9<br>LDEI      | 3.2<br>LDX          | 3.3<br>LDX    | 3.4<br>LDX   | 3.5<br>LDX    | 3.4<br>LDX      | 3.4<br>LDX     |              |            |             |             |           | 1.:<br>D  |

| 0 | RR1               | IRR1         | r1,Irr2             | lr1,lrr2         | r1,ER2              | Ir1,ER2       | IRR2,R1      | IRR2,IR1      | r1,rr2,X        | rr1,r2,X       |              |            |             |             |           | -         |

|   | 2.2               | 2.3          | 2.5                 | 2.9              | 3.2                 | 3.3           | 3.4          | 3.5           | 3.3             | 3.5            |              |            |             |             |           | 1.2       |

| 9 | RL                | RL           | LDE                 | LDEI             | LDX                 | LDX           | LDX          | LDX           | LEA             | LEA            |              |            |             |             |           | E         |

|   | R1                | IR1          | r2,Irr1             | lr2,Irr1         | r2,ER1              | lr2,ER1       | R2,IRR1      | IR2,IRR1      | r1,r2,X         | rr1,rr2,X      |              |            |             |             |           |           |

|   | 2.5               | 2.6          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.4       |

| A | INCW<br>RR1       | INCW<br>IRR1 | CP                  | CP<br>r1,lr2     | CP<br>D2 D1         | CP            |              |               | CPX<br>ER2,ER1  |                |              |            |             |             |           | RE        |

|   | 2.2               |              | r1,r2<br>2.3        | 2.4              | R2,R1<br>3.3        | IR2,R1<br>3.4 | R1,IM<br>3.3 | IR1,IM<br>3.4 | 4.3             | IM,ER1<br>4.3  |              |            |             |             |           | 1.3       |

| в | CLR               | 2.3<br>CLR   | XOR                 | XOR              | XOR                 | XOR           | XOR          | XOR           | XORX            | XORX           |              |            |             |             |           | IRE       |

|   | R1                | IR1          | r1,r2               | r1,lr2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2               | 2.3          | 2.5                 | 2.9              | 2.3                 | 2.9           |              | 3.4           | 3.2             |                |              |            |             |             |           | 1.2       |

| С | RRC               | RRC          | LDC                 | LDCI             | JP                  | LDC           |              | LD            | PUSHX           |                |              |            |             |             |           | RC        |

|   | R1                | IR1          | r1,Irr2             | lr1,lrr2         | IRR1                | lr1,lrr2      |              | r1,r2,X       | ER2             |                |              |            |             |             |           |           |

| D | 2.2               | 2.3          | 2.5                 | 2.9              | 2.6                 | 2.2           | 3.3          | 3.4<br>LD     | 3.2<br>POPX     |                |              |            |             |             |           | 1.2<br>SC |

| J | SRA<br>R1         | IR1          | LDC<br>r2,Irr1      | LDCI<br>lr2,lrr1 | IRR1                | BSWAP<br>R1   | DA           | r2,r1,X       | ER1             |                |              |            |             |             |           | 30        |

|   | 2.2               | 2.3          | 2.2                 | 2.3              | 3.2                 | 3.3           | 3.2          | 3.3           | 4.2             | 4.2            |              |            |             |             |           | 1.2       |

| Е | RR                | RR           | BIT                 | LD               | LD                  | LD            | LD           | LD            | LDX             | LDX            |              |            |             |             |           | cc        |

|   | R1                | IR1          | p,b,r1              | r1,Ir2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2               | 2.3          | 2.6                 | 2.3              | 2.8                 | 3.3           | 3.3          | 3.4           |                 |                |              | T          |             |             |           |           |

| F | SWAP              | SWAP         | TRAP                | LD               | MULT                | LD            | BTJ          | BTJ           |                 |                |              | V          |             |             |           |           |

|   | R1                | IR1          | Vector              | lr1,r2           | RR1                 | R2,IR1        | p,b,r1,X     | p,b,lr1,X     |                 |                | 1            | 1          | Ţ           | 1           | 7         | 1         |

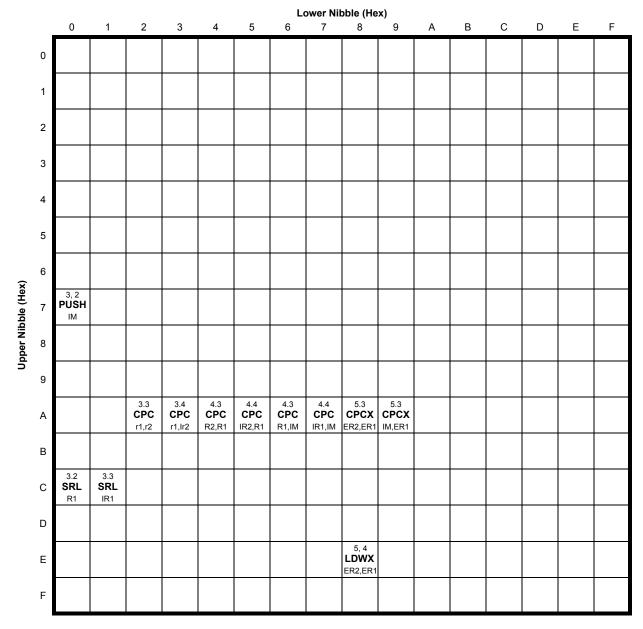

Figure 31. First Opcode Map

Upper Nibble (Hex)

218

zilog

232

|                |                                      | $T_A =$ | = 3.0 V to<br>0 °C to +<br>otherwis | 70 °C                |                           |                                                                                                                                                                                                                                |  |  |

|----------------|--------------------------------------|---------|-------------------------------------|----------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol         | Parameter                            | Minimum | Typical                             | Maximum              | Units                     | Conditions                                                                                                                                                                                                                     |  |  |

|                | Single-Shot Conversion<br>Time       | -       | 5129                                | -                    | System<br>clock<br>cycles | All measurements but temperature sensor                                                                                                                                                                                        |  |  |

|                |                                      |         | 10258                               |                      |                           | Temperature sensor<br>measurement                                                                                                                                                                                              |  |  |

|                | Continuous Conversion<br>Time        | -       | 256                                 | _                    | System<br>clock<br>cycles | All measurements but temperature sensor                                                                                                                                                                                        |  |  |

|                |                                      |         | 512                                 |                      |                           | Temperature sensor<br>measurement                                                                                                                                                                                              |  |  |

|                | Signal Input Bandwidth               | _       | 10                                  |                      | kHz                       | As defined by -3 dB point                                                                                                                                                                                                      |  |  |

| R <sub>S</sub> | Analog Source Impedance <sup>4</sup> | _       | _                                   | 10                   | kΩ                        | In unbuffered mode                                                                                                                                                                                                             |  |  |

|                |                                      |         |                                     | 500                  | kΩ                        | In buffered modes                                                                                                                                                                                                              |  |  |

| Zin            | Input Impedance                      | -       | 150                                 |                      | kΩ                        | In unbuffered mode at 20 $\rm MHz^5$                                                                                                                                                                                           |  |  |

|                |                                      | 10      | _                                   |                      | MΩ                        | In buffered modes                                                                                                                                                                                                              |  |  |

| Vin            | Input Voltage Range                  | 0       |                                     | V <sub>DD</sub>      | V                         | Unbuffered Mode                                                                                                                                                                                                                |  |  |

|                |                                      | 0.3     |                                     | V <sub>DD</sub> -1.1 | V                         | Buffered Modes                                                                                                                                                                                                                 |  |  |

|                |                                      |         |                                     | •                    | Note:                     | These values define the<br>range over which the<br>ADC performs within<br>spec; exceeding these<br>values does not cause<br>damage or instability; see<br>DC Characteristics on<br>page 222 for absolute pin<br>voltage limits |  |  |

#### Table 135. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

#### Notes

- 1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

- 2. Devices are factory calibrated at  $V_{DD}$  = 3.3 V and  $T_A$  = +30 °C, so the ADC is maximally accurate under these conditions.

- 3. LSBs are defined assuming 10-bit resolution.

- 4. This is the maximum recommended resistance seen by the ADC input pin.

- 5. The input impedance is inversely proportional to the system clock frequency.

| Part Number                     | Flash      | RAM     | SUVD  | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | <b>Temperature Sensor</b> | Description         |

|---------------------------------|------------|---------|-------|-----------|------------|---------------------|---------------------|----------------|------------|---------------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082 |            |         |       | sh        |            |                     |                     |                |            |                           |                     |

| Standard Temperatur             | re: 0 °C 1 |         |       |           |            |                     |                     |                |            |                           |                     |

| Z8F041APB020SC                  | 4 KB       | 1 KB    | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 8-pin package  |

| Z8F041AQB020SC                  | 4 KB       | 1 KB    | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | QFN 8-pin package   |

| Z8F041ASB020SC                  | 4 KB       | 1 KB    | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 8-pin package  |

| Z8F041ASH020SC                  | 4 KB       | 1 KB    | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 20-pin package |

| Z8F041AHH020SC                  | 4 KB       | 1 KB    | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SSOP 20-pin package |

| Z8F041APH020SC                  | 4 KB       | 1 KB    | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 20-pin package |

| Z8F041ASJ020SC                  | 4 KB       | 1 KB    | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 28-pin package |

| Z8F041AHJ020SC                  | 4 KB       | 1 KB    | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SSOP 28-pin package |

| Z8F041APJ020SC                  | 4 KB       | 1 KB    | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 28-pin package |

| Extended Temperatu              | re: -40 °  | C to 10 | 5 °C  |           |            |                     |                     |                |            |                           |                     |

| Z8F041APB020EC                  | 4 KB       | 1 KB    | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 8-pin package  |

| Z8F041AQB020EC                  | 4 KB       | 1 KB    | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | QFN 8-pin package   |

| Z8F041ASB020EC                  | 4 KB       | 1 KB    | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 8-pin package  |

| Z8F041ASH020EC                  | 4 KB       | 1 KB    | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 20-pin package |

| Z8F041AHH020EC                  | 4 KB       | 1 KB    | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SSOP 20-pin package |

| Z8F041APH020EC                  | 4 KB       | 1 KB    | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 20-pin package |

| Z8F041ASJ020EC                  | 4 KB       | 1 KB    | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 28-pin package |

| Z8F041AHJ020EC                  | 4 KB       | 1 KB    | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SSOP 28-pin package |

| Z8F041APJ020EC                  | 4 KB       | 1 KB    | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 28-pin package |

| Replace C with G for Lea        | ad-Free P  | ackagin | g     |           |            |                     |                     |                |            |                           |                     |

zilog 257

| Part Number                     | Flash     | RAM      | SUVN   | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------|-----------|----------|--------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082 | A Serie   | s with 1 | KB Fla | ish, 1    | 0-Bit      | Ana                 | log-t               | o-Dig          | jital C    | Conv               | verter              |

| Standard Temperatu              | re: 0 °C  | to 70 °C | ;      |           |            |                     |                     |                |            |                    |                     |

| Z8F012APB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperatu              | re: -40 ° | C to 10  | 5 °C   |           |            |                     |                     |                |            |                    |                     |

| Z8F012APB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

# **Customer Support**

For answers to technical questions about the product, documentation, or any other issues with Zilog's offerings, please visit Zilog's Knowledge Base at <a href="http://www.zilog.com/kb">http://www.zilog.com/kb</a>.

For any comments, detail technical questions, or reporting problems, please visit Zilog's Technical Support at <u>http://support.zilog.com</u>.