Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Obsolete                                                     |

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 1KB (1K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 16 x 8                                                       |

| RAM Size                   | 256 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f012ahh020ec    |

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

| Reset, Stop Mode Recovery, and Low Voltage Detection | 23 |

|------------------------------------------------------|----|

| Reset Types                                          | 23 |

| Reset Sources                                        |    |

| Power-On Reset                                       |    |

| Voltage Brownout Reset                               |    |

| Watchdog Timer Reset                                 |    |

| External Reset Input External Reset Indicator        |    |

| On-Chip Debugger Initiated Reset                     |    |

| Stop Mode Recovery                                   |    |

| Stop Mode Recovery Using Watchdog Timer Time-Out     |    |

| Stop Mode Recovery Using a GPIO Port Pin Transition  | 29 |

| Stop Mode Recovery Using the External RESET Pin      | 30 |

| Low Voltage Detection                                | 30 |

| Reset Register Definitions                           | 30 |

| Low-Power Modes                                      | 33 |

| STOP Mode                                            | 33 |

| HALT Mode                                            | 34 |

| Peripheral-Level Power Control                       | 34 |

| Power Control Register Definitions                   | 34 |

| General-Purpose Input/Output                         | 37 |

| GPIO Port Availability By Device                     | 37 |

| Architecture                                         | 38 |

| GPIO Alternate Functions                             | 38 |

| Direct LED Drive                                     | 39 |

| Shared Reset Pin                                     | 39 |

| Shared Debug Pin                                     | 39 |

| Crystal Oscillator Override                          | 40 |

| 5 V Tolerance                                        | 40 |

| External Clock Setup                                 | 40 |

| GPIO Interrupts                                      | 45 |

| GPIO Control Register Definitions                    | 45 |

| Port A–D Address Registers                           | 46 |

| Port A–D Control Registers                           |    |

| Port A–D Data Direction Sub-Registers                |    |

| Port A–D Alternate Function Sub-Registers            | 47 |

PS022825-0908 Table of Contents

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

zilog',

| v | ıi, |  |

|---|-----|--|

| Port A–C Input Data Registers5Port A–D Output Data Register5LED Drive Enable Register5LED Drive Level High Register5LED Drive Level Low Register5                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt Controller 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Interrupt Vector Listing         5           Architecture         5           Operation         5           Master Interrupt Enable         5           Interrupt Vectors and Priority         5           Interrupt Assertion         5           Software Interrupt Assertion         5           Watchdog Timer Interrupt Assertion         5           Interrupt Control Register Definitions         6           Interrupt Request 0 Register         6           Interrupt Request 1 Register         6           Interrupt Request 2 Register         6 |

| IRQ0 Enable High and Low Bit Registers 6 IRQ1 Enable High and Low Bit Registers 6 IRQ2 Enable High and Low Bit Registers 6 Interrupt Edge Select Register 6 Shared Interrupt Select Register 6 Interrupt Control Register 6 Timers 6                                                                                                                                                                                                                                                                                                                           |

| Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Timer Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Timer Control Register Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Watchdog Timer 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

PS022825-0908 Table of Contents

PAFS1[7:0]—Port Alternate Function Set 1

0 = Port Alternate Function selected as defined in Table 14 and Table 15 on page 44.

1 = Port Alternate Function selected as defined in Table 14 and Table 15 on page 44.

#### Port A-D Alternate Function Set 2 Sub-Registers

The Port A–D Alternate Function Set 2 sub-register (Table 26) is accessed through the Port A–D Control register by writing 08H to the Port A–D Address register. The Alternate Function Set 2 sub-registers selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register is defined in Table 15.

Note:

Alternate function selection on port pins must also be enabled as described in Port A–D Alternate Function Sub-Registers on page 47.

Table 26. Port A–D Alternate Function Set 2 Sub-Registers (PxAFS2)

| BITS  | 7                                                                  | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|

| FIELD | PAFS27                                                             | PAFS26                                                                                | PAFS25 | PAFS24 | PAFS23 | PAFS22 | PAFS21 | PAFS20 |

| RESET | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device) |                                                                                       |        |        |        |        |        |        |

| R/W   | R/W                                                                | R/W         R/W         R/W         R/W         R/W         R/W         R/W           |        |        |        |        |        |        |

| ADDR  | If 08H i                                                           | If 08H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |        |

PAFS2[7:0]—Port Alternate Function Set 2

0 = Port Alternate Function selected as defined in Table 15.

1 = Port Alternate Function selected as defined in Table 15.

### Port A-C Input Data Registers

Reading from the Port A–C Input Data registers (Table 27) returns the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those missing on the 8- and 28-pin packages, as well as those missing on the ADC-enabled 28-pin packages.

Table 27. Port A-C Input Data Registers (PxIN)

| BITS      | 7                | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----------|------------------|------|------|------|------|------|------|------|

| FIELD     | PIN7             | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |

| RESET     | Х                | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| R/W       | R                | R    | R    | R    | R    | R    | R    | R    |

| ADDR      | FD2H, FD6H, FDAH |      |      |      |      |      |      |      |

| X = Undef | ined.            |      |      |      |      |      |      |      |

Interrupts are globally enabled by any of the following actions:

- Execution of an EI (Enable Interrupt) instruction

- Execution of an IRET (Return from Interrupt) instruction

- Writing a 1 to the IRQE bit in the Interrupt Control register

Interrupts are globally disabled by any of the following actions:

- Execution of a DI (Disable Interrupt) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller

- Writing a 0 to the IRQE bit in the Interrupt Control register

- Reset

- Execution of a Trap instruction

- Illegal Instruction Trap

- Primary Oscillator Fail Trap

- Watchdog Oscillator Fail Trap

#### **Interrupt Vectors and Priority**

The interrupt controller supports three levels of interrupt priority. Level 3 is the highest priority, Level 2 is the second highest priority, and Level 1 is the lowest priority. If all of the interrupts are enabled with identical interrupt priority (all as Level 2 interrupts, for example), the interrupt priority is assigned from highest to lowest as specified in Table 32 on page 56. Level 3 interrupts are always assigned higher priority than Level 2 interrupts which, in turn, always are assigned higher priority than Level 1 interrupts. Within each interrupt priority level (Level 1, Level 2, or Level 3), priority is assigned as specified in Table 32, above. Reset, Watchdog Timer interrupt (if enabled), Primary Oscillator Fail Trap, Watchdog Oscillator Fail Trap, and Illegal Instruction Trap always have highest (level 3) priority.

# Interrupt Assertion

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the Interrupt Request register is cleared until the next interrupt occurs. Writing a 0 to the corresponding bit in the Interrupt Request register likewise clears the interrupt request.

PS022825-0908 Interrupt Controller

Table 37. IRQ0 Enable High Bit Register (IRQ0ENH)

| BITS  | 7        | 6                           | 5     | 4      | 3      | 2        | 1        | 0      |

|-------|----------|-----------------------------|-------|--------|--------|----------|----------|--------|

| FIELD | Reserved | T1ENH                       | T0ENH | U0RENH | U0TENH | Reserved | Reserved | ADCENH |

| RESET | 0        | 0                           | 0     | 0      | 0      | 0        | 0        | 0      |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W |       |        |        |          |          |        |

| ADDR  |          | FC1H                        |       |        |        |          |          |        |

Reserved—Must be 0.

T1ENH—Timer 1 Interrupt Request Enable High Bit

T0ENH—Timer 0 Interrupt Request Enable High Bit

U0RENH—UART 0 Receive Interrupt Request Enable High Bit

U0TENH—UART 0 Transmit Interrupt Request Enable High Bit

ADCENH—ADC Interrupt Request Enable High Bit

Table 38. IRQ0 Enable Low Bit Register (IRQ0ENL)

| BITS  | 7        | 6     | 5     | 4      | 3      | 2        | 1        | 0      |

|-------|----------|-------|-------|--------|--------|----------|----------|--------|

| FIELD | Reserved | T1ENL | T0ENL | U0RENL | U0TENL | Reserved | Reserved | ADCENL |

| RESET | 0        | 0     | 0     | 0      | 0      | 0        | 0        | 0      |

| R/W   | R        | R/W   | R/W   | R/W    | R/W    | R        | R        | R/W    |

| ADDR  |          | FC2H  |       |        |        |          |          |        |

Reserved—Must be 0.

T1ENL—Timer 1 Interrupt Request Enable Low Bit

T0ENL—Timer 0 Interrupt Request Enable Low Bit

U0RENL—UART 0 Receive Interrupt Request Enable Low Bit

U0TENL—UART 0 Transmit Interrupt Request Enable Low Bit

ADCENL—ADC Interrupt Request Enable Low Bit

# IRQ1 Enable High and Low Bit Registers

Table 39 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers (Table 40 and Table 41) form a priority encoded enabling for interrupts in the Interrupt Request 1 register.

PS022825-0908 Interrupt Controller

# **Watchdog Timer**

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which may place the Z8 Encore! XP® F082A Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator.

- A selectable time-out response: reset or interrupt.

- 24-bit programmable time-out value.

#### **Operation**

The Watchdog Timer is a one-shot timer that resets or interrupts the Z8 Encore! XP F082A Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash Option Bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =

$$\frac{\text{WDT Reload Value}}{10}$$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10 kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 56 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

Table 56. Watchdog Timer Approximate Time-Out Delays

| WDT Reload Value WDT Reload Va |            |            | oximate Time-Out Delay<br>opical WDT oscillator frequency) |  |  |

|--------------------------------|------------|------------|------------------------------------------------------------|--|--|

| (Hex)                          | (Decimal)  | Typical    | Description                                                |  |  |

| 000004                         | 4          | 400 μs     | Minimum time-out delay                                     |  |  |

| FFFFFF                         | 16,777,215 | 28 minutes | Maximum time-out delay                                     |  |  |

PS022825-0908 Watchdog Timer

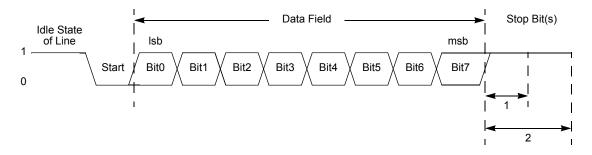

Figure 11. UART Asynchronous Data Format without Parity

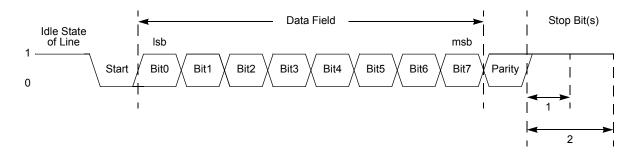

Figure 12. UART Asynchronous Data Format with Parity

#### Transmitting Data using the Polled Method

Follow the steps below to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Write to the UART Control 1 register, if MULTIPROCESSOR mode is appropriate, to enable MULTIPROCESSOR (9-bit) mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR mode.

- 5. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR mode is not enabled, and select either even or odd parity (PSEL).

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin.

- 3. Clears the UART Receiver interrupt in the applicable Interrupt Request register.

- 4. Executes the IRET instruction to return from the interrupt-service routine and await more data.

### Clear To Send (CTS) Operation

The CTS pin, if enabled by the CTSE bit of the UART Control 0 register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this action is typically performed during Stop Bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

#### **MULTIPROCESSOR (9-bit) Mode**

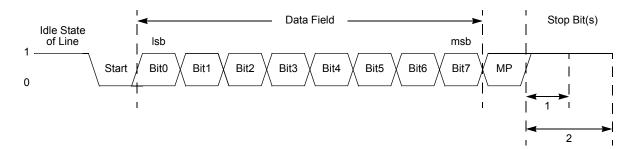

The UART has a MULTIPROCESSOR (9-bit) mode that uses an extra (9th) bit for selective communication when a number of processors share a common UART bus. In MULTIPROCESSOR mode (also referred to as 9-bit mode), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 13. The character format is:

Figure 13. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) mode, the Parity bit location (9th bit) becomes the Multiprocessor control bit. The UART Control 1 and Status 1 registers provide MULTI-PROCESSOR (9-bit) mode control and status information. If an automatic address matching scheme is enabled, the UART Address Compare register holds the network address of the device.

#### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When MULTIPROCESSOR mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made in hardware, software or some combination of the two, depending on the multiprocessor

configuration bits. In general, the address compare feature reduces the load on the CPU, because it does not require access to the UART when it receives data directed to other devices on the multi-node network. The following three MULTIPROCESSOR modes are available in hardware:

- 1. Interrupt on all address bytes.

- 2. Interrupt on matched address bytes and correctly framed data bytes.

- 3. Interrupt only on correctly framed data bytes.

These modes are selected with MPMD [1:0] in the UART Control 1 Register. For all multiprocessor modes, bit MPEN of the UART Control 1 Register must be set to 1.

The first scheme is enabled by writing 01b to MPMD[1:0]. In this mode, all incoming address bytes cause an interrupt, while data bytes never cause an interrupt. The interrupt service routine must manually check the address byte that caused triggered the interrupt. If it matches the UART address, the software clears MPMD[0]. Each new incoming byte interrupts the CPU. The software is responsible for determining the end of the frame. It checks for the end-of-frame by reading the MPRX bit of the UART Status 1 Register for each incoming byte. If MPRX=1, a new frame has begun. If the address of this new frame is different from the UART's address, MPMD[0] must be set to 1 causing the UART interrupts to go inactive until the next address byte. If the new frame's address matches the UART's, the data in the new frame is processed as well.

The second scheme requires the following: set MPMD[1:0] to 10B and write the UART's address into the UART Address Compare Register. This mode introduces additional hardware control, interrupting only on frames that match the UART's address. When an incoming address byte does not match the UART's address, it is ignored. All successive data bytes in this frame are also ignored. When a matching address byte occurs, an interrupt is issued and further interrupts now occur on each successive data byte. When the first data byte in the frame is read, the NEWFRM bit of the UART Status 1 Register is asserted. All successive data bytes have NEWFRM=0. When the next address byte occurs, the hardware compares it to the UART's address. If there is a match, the interrupts continues and the NEWFRM bit is set for the first byte of the new frame. If there is no match, the UART ignores all incoming bytes until the next address match.

The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second scheme, except that there are no interrupts on address bytes. The first data byte of each frame remains accompanied by a NEWFRM assertion.

#### **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

zilog

baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal, allowing the Endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

# Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined in Universal Asynchronous Receiver/Transmitter on page 97.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the *UART Control 1 register to 1 to enable the Infrared Encoder/Decoder before enabling* the GPIO Port alternate function for the corresponding pin.

PS022825-0908 Infrared Encoder/Decoder

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control register may be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in ADC Control/Status Register 1.

- Set CEN to 1 to start the conversions.

- 4. When the first conversion in continuous operation is complete (after 5129 system clock cycles, plus the 40 cycles for power-up, if necessary), the ADC control logic performs the following operations:

- CEN resets to 0 to indicate the first conversion is complete. CEN remains 0 for all subsequent conversions in continuous operation.

- An interrupt request is sent to the Interrupt Controller to indicate the conversion is complete.

- 5. The ADC writes a new data result every 256 system clock cycles. For each completed conversion, the ADC control logic performs the following operations:

- Writes the 13-bit two's complement result to {ADCD\_H[7:0], ADCD\_L[7:3]}.

- Sends an interrupt request to the Interrupt Controller denoting conversion complete.

- 6. To disable continuous conversion, clear the CONT bit in the ADC Control Register to 0.

#### Interrupts

The ADC is able to interrupt the CPU when a conversion has been completed. When the ADC is disabled, no new interrupts are asserted; however, an interrupt pending when the ADC is disabled is not cleared.

# Calibration and Compensation

The Z8 Encore!  $XP^{\circledR}$  F082A Series ADC is factory calibrated for offset error and gain error, with the compensation data stored in Flash memory. Alternatively, you can perform your own calibration, storing the values into Flash themselves. Thirdly, the user code can perform a manual offset calibration during DIFFERENTIAL mode operation.

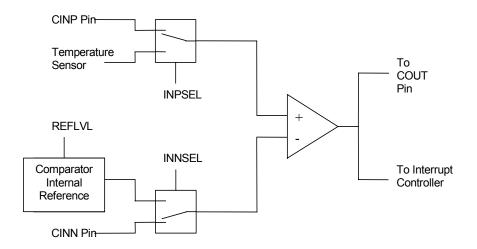

# Comparator

The Z8 Encore! XP® F082A Series devices feature a general purpose comparator that compares two analog input signals. These analog signals may be external stimulus from a pin (CINP and/or CINN) or internally generated signals. Both a programmable voltage reference and the temperature sensor output voltage are available internally. The output is available as an interrupt source or can be routed to an external pin.

Figure 20. Comparator Block Diagram

# **Operation**

When the positive comparator input exceeds the negative input by more than the specified hysteresis, the output is a logic HIGH. When the negative input exceeds the positive by more than the hysteresis, the output is a logic LOW. Otherwise, the comparator output retains its present value. See Table 137 on page 233 for details.

The comparator may be powered down to reduce supply current. See Power Control Register 0 on page 34 for details.

**Caution:** Because of the propagation delay of the comparator, it is not recommended to enable or reconfigure the comparator without first disabling interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts. The following example describes how to safely enable the comparator:

```

di

ld cmp0, r0; load some new configuration

nop

```

PS022825-0908 Comparator

```

nop     ; wait for output to settle

clr irq0 ; clear any spurious interrupts pending

ei

```

### **Comparator Control Register Definitions**

#### **Comparator Control Register**

The Comparator Control Register (CMP0) configures the comparator inputs and sets the value of the internal voltage reference.

Table 75. Comparator Control Register (CMP0)

| BITS  | 7      | 6      | 5   | 4   | 3   | 2   | 1                    | 0                        |

|-------|--------|--------|-----|-----|-----|-----|----------------------|--------------------------|

| FIELD | INPSEL | INNSEL |     | REF | LVL |     | Reserved (<br>REFLVI | 20-/28-pin)<br>_ (8-pin) |

| RESET | 0      | 0      | 0   | 1   | 0   | 1   | 0                    | 0                        |

| R/W   | R/W    | R/W    | R/W | R/W | R/W | R/W | R/W                  | R/W                      |

| ADDR  |        |        |     | F9  | 0H  |     |                      |                          |

INPSEL—Signal Select for Positive Input

0 = GPIO pin used as positive comparator input

1 = temperature sensor used as positive comparator input

INNSEL—Signal Select for Negative Input

0 = internal reference disabled, GPIO pin used as negative comparator input

1 = internal reference enabled as negative comparator input

REFLVL—Internal Reference Voltage Level (this reference is independent of the ADC voltage reference). Note that the 8-pin devices contain two additional LSBs for increased resolution.

For 20-/28-pin devices:

```

0000 = 0.0 V

0001 = 0.2 V

0010 = 0.4 V

0011 = 0.6 V

0100 = 0.8 V

0101 = 1.0 V (Default)

0110 = 1.2 V

0111 = 1.4 V

1000 = 1.6 V

```

PS022825-0908 Comparator

162

**Table 94. ADC Calibration Data Location**

| AddressAddressCompensation UsageADC ModeType60FE60OffsetSingle-Ended UnbufferedInternal 2.0 V08FE08Gain High ByteSingle-Ended UnbufferedInternal 2.0 V09FE09Gain Low ByteSingle-Ended UnbufferedInternal 1.0 V63FE63OffsetSingle-Ended UnbufferedInternal 1.0 V0AFE0AGain High ByteSingle-Ended UnbufferedInternal 1.0 V0BFE0BGain Low ByteSingle-Ended UnbufferedExternal 2.0 V0CFE66OffsetSingle-Ended UnbufferedExternal 2.0 V0CFE0CGain High ByteSingle-Ended UnbufferedExternal 2.0 V0DFE0DGain Low ByteSingle-Ended UnbufferedExternal 2.0 V0BFE69OffsetSingle-Ended 1x BufferedInternal 2.0 V0BFE0BGain High ByteSingle-Ended 1x BufferedInternal 2.0 V0CFE0CGain Low ByteSingle-Ended 1x BufferedExternal 2.0 V0FFE0FGain Low ByteSingle-Ended 1x BufferedExternal 2.0 V10FE10Gain High ByteSingle-Ended 1x BufferedExternal 2.0 V11FE11Gain Low ByteSingle-Ended 1x BufferedExternal 2.0 V12FE12Positive Gain Low ByteDifferential UnbufferedInternal 2.0 V13FE13Positive Gain Low ByteDifferential UnbufferedInternal 2.0 V14FE14Positive Gain Low ByteDiffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Info Page | Memory  |                         |                          | Reference      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|-------------------------|--------------------------|----------------|

| FE08 Gain High Byte Single-Ended Unbuffered Internal 2.0 V  99 FE09 Gain Low Byte Single-Ended Unbuffered Internal 2.0 V  63 FE63 Offset Single-Ended Unbuffered Internal 1.0 V  0A FE0A Gain High Byte Single-Ended Unbuffered Internal 1.0 V  0B FE0B Gain Low Byte Single-Ended Unbuffered Internal 1.0 V  0B FE0B Gain Low Byte Single-Ended Unbuffered Internal 1.0 V  0C FE0C Gain High Byte Single-Ended Unbuffered External 2.0 V  0D FE0D Gain Low Byte Single-Ended Unbuffered External 2.0 V  0D FE0D Gain Low Byte Single-Ended Unbuffered Internal 2.0 V  0D FE0B Gain High Byte Single-Ended 1x Buffered Internal 2.0 V  0D FE0B Gain High Byte Single-Ended 1x Buffered Internal 2.0 V  0F FE0F Gain Low Byte Single-Ended 1x Buffered External 2.0 V  0F FE0C Gain High Byte Single-Ended 1x Buffered External 2.0 V  10 FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V  11 FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V  12 FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V  13 FE13 Positive Gain High Byte Differential Unbuffered Internal 2.0 V  14 FE31 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V  15 FE72 Offset Differential Unbuffered Internal 2.0 V  16 FE61 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V  17 FE72 Offset Differential Unbuffered Internal 2.0 V  18 FE31 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V  19 FE75 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  19 FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  19 FE33 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  19 FE34 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  19 FE35 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  19 FE36 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  19 FE36 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  19 FE36 Negative Gain High Byte Differential Unbuffered Internal 1.0 V                                                                         | Address   | Address | Compensation Usage      | ADC Mode                 | Туре           |

| FE09 Gain Low Byte Single-Ended Unbuffered Internal 2.0 V G3 FE63 Offset Single-Ended Unbuffered Internal 1.0 V G4 FE0A Gain High Byte Single-Ended Unbuffered Internal 1.0 V G5 FE0B Gain Low Byte Single-Ended Unbuffered Internal 1.0 V G6 FE66 Offset Single-Ended Unbuffered External 2.0 V G7 FE0C Gain High Byte Single-Ended Unbuffered External 2.0 V G8 FE0B Gain Low Byte Single-Ended Unbuffered External 2.0 V G8 FE0B Gain Low Byte Single-Ended Unbuffered External 2.0 V G8 FE69 Offset Single-Ended 1x Buffered Internal 2.0 V G9 FE0B Gain High Byte Single-Ended 1x Buffered Internal 2.0 V G6 FE0C Gain High Byte Single-Ended 1x Buffered Internal 2.0 V G6 FE6C Offset Single-Ended 1x Buffered External 2.0 V G7 FE0B Gain Low Byte Single-Ended 1x Buffered External 2.0 V G8 FE6B Offset Single-Ended 1x Buffered External 2.0 V G8 FE6C Offset Single-Ended 1x Buffered External 2.0 V G8 FE10 Gain High Byte Single-Ended 1x Buffered Internal 2.0 V G8 FE6B Offset Differential Unbuffered Internal 2.0 V G8 FE6B Offset Differential Unbuffered Internal 2.0 V G9 FE6B Offset Differential Unbuffered Internal 2.0 V C9 FE7D Offset Differe | 60        | FE60    | Offset                  | Single-Ended Unbuffered  | Internal 2.0 V |

| FE63 Offset Single-Ended Unbuffered Internal 1.0 V  OA FE0A Gain High Byte Single-Ended Unbuffered Internal 1.0 V  OB FE0B Gain Low Byte Single-Ended Unbuffered Internal 1.0 V  66 FE66 Offset Single-Ended Unbuffered External 2.0 V  OC FE0C Gain High Byte Single-Ended Unbuffered External 2.0 V  OD FE0D Gain Low Byte Single-Ended Unbuffered External 2.0 V  OD FE0D Gain High Byte Single-Ended Unbuffered External 2.0 V  OF FE69 Offset Single-Ended 1x Buffered Internal 2.0 V  OF FE0E Gain High Byte Single-Ended 1x Buffered Internal 2.0 V  OF FE0F Gain Low Byte Single-Ended 1x Buffered Internal 2.0 V  OF FE6C Offset Single-Ended 1x Buffered External 2.0 V  OF FE6C Offset Single-Ended 1x Buffered External 2.0 V  OF FE6C Offset Single-Ended 1x Buffered External 2.0 V  OF FE6C Offset Single-Ended 1x Buffered External 2.0 V  OF FE6C Offset Differential Unbuffered Internal 2.0 V  OF FE6F Offset Differential Unbuffered Internal 1.0 V  OF FE7F Offset Differential Unbuffered Internal 1.0 V                                                                                                                                                                                                                                        | 08        | FE08    | Gain High Byte          | Single-Ended Unbuffered  | Internal 2.0 V |

| FEOA Gain High Byte Single-Ended Unbuffered Internal 1.0 V  B FEOB Gain Low Byte Single-Ended Unbuffered Internal 1.0 V  GEOFECC Gain High Byte Single-Ended Unbuffered External 2.0 V  CEOFECC Gain High Byte Single-Ended Unbuffered External 2.0 V  DEOFECC Gain High Byte Single-Ended Unbuffered External 2.0 V  DEOFECC Gain High Byte Single-Ended Unbuffered External 2.0 V  GEOFECC Gain High Byte Single-Ended Unbuffered Internal 2.0 V  GEOFECC Gain High Byte Single-Ended 1x Buffered Internal 2.0 V  GEOFECC Gain High Byte Single-Ended 1x Buffered Internal 2.0 V  GEOFECC Offset Single-Ended 1x Buffered External 2.0 V  GEOFECC Offset Differential Unbuffered Internal 1.0 V  GEOFECC Offset Differential Unbuffered Internal 2.0 V  GEOFECC Offset Differential Unbuffered External 2.0 V                                                                                                         | 09        | FE09    | Gain Low Byte           | Single-Ended Unbuffered  | Internal 2.0 V |

| Gain Low Byte Single-Ended Unbuffered External 2.0 V GENEROR Gain High Byte Single-Ended Unbuffered External 2.0 V CENTRO GENEROR Gain High Byte Single-Ended Unbuffered External 2.0 V CENTRO GENEROR | 63        | FE63    | Offset                  | Single-Ended Unbuffered  | Internal 1.0 V |

| FE66 Offset Single-Ended Unbuffered External 2.0 V  OC FEOC Gain High Byte Single-Ended Unbuffered External 2.0 V  OD FEOD Gain Low Byte Single-Ended Unbuffered External 2.0 V  69 FE69 Offset Single-Ended 1x Buffered Internal 2.0 V  OE FE0E Gain High Byte Single-Ended 1x Buffered Internal 2.0 V  OF FE0F Gain Low Byte Single-Ended 1x Buffered Internal 2.0 V  OF FE0C Offset Single-Ended 1x Buffered External 2.0 V  OF FE0C Offset Single-Ended 1x Buffered External 2.0 V  10 FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V  11 FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V  OF FE6F Offset Differential Unbuffered Internal 2.0 V  12 FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V  13 FE13 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V  30 FE30 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V  14 FE14 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V  15 FE72 Offset Differential Unbuffered Internal 1.0 V  16 FE15 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  17 FE15 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  18 FE33 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  19 FE75 Offset Differential Unbuffered Internal 1.0 V  10 FE16 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  10 FE175 Offset Differential Unbuffered Internal 1.0 V  11 FE18 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  11 FE19 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  12 FE75 Offset Differential Unbuffered Internal 1.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0A        | FE0A    | Gain High Byte          | Single-Ended Unbuffered  | Internal 1.0 V |

| OC FEOC Gain High Byte Single-Ended Unbuffered External 2.0 V  DD FEOD Gain Low Byte Single-Ended Unbuffered External 2.0 V  FEOF Gain High Byte Single-Ended 1x Buffered Internal 2.0 V  FEOF Gain Low Byte Single-Ended 1x Buffered Internal 2.0 V  FEOF Gain Low Byte Single-Ended 1x Buffered Internal 2.0 V  FEOF Gain Low Byte Single-Ended 1x Buffered External 2.0 V  GC FEGC Offset Single-Ended 1x Buffered External 2.0 V  GC FEOF Gain High Byte Single-Ended 1x Buffered External 2.0 V  FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V  FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V  FEOF FEOF Offset Differential Unbuffered Internal 2.0 V  FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V  FE13 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V  FE30 Negative Gain High Byte Differential Unbuffered Internal 2.0 V  FE31 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V  FE31 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V  FE31 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  FE32 FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V  FE33 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  FE33 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V  FE35 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  FE55 Offset Differential Unbuffered Internal 1.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0B        | FE0B    | Gain Low Byte           | Single-Ended Unbuffered  | Internal 1.0 V |

| OD FEOD Gain Low Byte Single-Ended Unbuffered External 2.0 V 69 FE69 Offset Single-Ended 1x Buffered Internal 2.0 V 0E FEOE Gain High Byte Single-Ended 1x Buffered Internal 2.0 V 0F FEOF Gain Low Byte Single-Ended 1x Buffered Internal 2.0 V 0F FE6C Offset Single-Ended 1x Buffered External 2.0 V 10 FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V 11 FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V 12 FE6C Offset Differential Unbuffered Internal 2.0 V 13 FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V 14 FE31 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V 15 FE70 Offset Differential Unbuffered Internal 2.0 V 16 FE71 Negative Gain High Byte Differential Unbuffered Internal 2.0 V 17 FE71 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V 18 FE71 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V 19 FE72 Offset Differential Unbuffered Internal 2.0 V 19 FE72 Offset Differential Unbuffered Internal 1.0 V 19 FE73 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE73 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE75 Offset Differential Unbuffered Internal 1.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66        | FE66    | Offset                  | Single-Ended Unbuffered  | External 2.0 V |

| FE69 Offset Single-Ended 1x Buffered Internal 2.0 V  DE FE0E Gain High Byte Single-Ended 1x Buffered Internal 2.0 V  DF FE0F Gain Low Byte Single-Ended 1x Buffered Internal 2.0 V  DF FE6C Offset Single-Ended 1x Buffered External 2.0 V  DF FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V  DF FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V  DF FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V  DF FE6F Offset Differential Unbuffered Internal 2.0 V  DF FE6F Offset Differential Unbuffered Internal 2.0 V  DF FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V  DF FE30 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V  DF FE72 Offset Differential Unbuffered Internal 2.0 V  DF FE72 Offset Differential Unbuffered Internal 1.0 V  DF FE15 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  DF FE31 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  DF FE73 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  DF FE75 Offset Differential Unbuffered Internal 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0C        | FE0C    | Gain High Byte          | Single-Ended Unbuffered  | External 2.0 V |

| OE FE0E Gain High Byte Single-Ended 1x Buffered Internal 2.0 V OF FE0F Gain Low Byte Single-Ended 1x Buffered Internal 2.0 V 6C FE6C Offset Single-Ended 1x Buffered External 2.0 V 10 FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V 11 FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V 12 FE6F Offset Differential Unbuffered Internal 2.0 V 13 FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V 14 FE30 Negative Gain High Byte Differential Unbuffered Internal 2.0 V 15 FE70 Offset Differential Unbuffered Internal 2.0 V 16 FE71 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V 17 FE72 Offset Differential Unbuffered Internal 2.0 V 18 FE73 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE70 Offset Differential Unbuffered Internal 1.0 V 19 FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE31 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE15 Positive Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE30 Offset Differential Unbuffered Internal 1.0 V 19 FE30 Offset Differential Unbuffered Internal 1.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0D        | FE0D    | Gain Low Byte           | Single-Ended Unbuffered  | External 2.0 V |

| OF FE0F Gain Low Byte Single-Ended 1x Buffered External 2.0 V 6C FE6C Offset Single-Ended 1x Buffered External 2.0 V 10 FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V 11 FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V 12 FE6F Offset Differential Unbuffered Internal 2.0 V 13 FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V 14 FE30 Negative Gain High Byte Differential Unbuffered Internal 2.0 V 15 FE70 Offset Differential Unbuffered Internal 2.0 V 16 FE71 Positive Gain High Byte Differential Unbuffered Internal 2.0 V 17 FE30 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V 18 FE31 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V 19 FE72 Offset Differential Unbuffered Internal 1.0 V 19 FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE31 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 69        | FE69    | Offset                  | Single-Ended 1x Buffered | Internal 2.0 V |

| FE6C Offset Single-Ended 1x Buffered External 2.0 V  FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V  FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V  FE6F Offset Differential Unbuffered Internal 2.0 V  FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V  FE13 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V  Negative Gain High Byte Differential Unbuffered Internal 2.0 V  RE30 Negative Gain High Byte Differential Unbuffered Internal 2.0 V  FE7 Offset Differential Unbuffered Internal 2.0 V  FE7 Diffset Differential Unbuffered Internal 1.0 V  FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V  FE7 FE7 Offset Differential Unbuffered Internal 1.0 V  FE7 FE7 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  FE30 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  FE7 FE7 Offset Differential Unbuffered Internal 1.0 V  FE7 FE7 Offset Differential Unbuffered Internal 1.0 V  FE7 FE7 Offset Differential Unbuffered Internal 1.0 V  FE7 FE75 Offset Differential Unbuffered External 2.0 V  FE7 FE75 Offset Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0E        | FE0E    | Gain High Byte          | Single-Ended 1x Buffered | Internal 2.0 V |

| FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V  FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V  FE6F Offset Differential Unbuffered Internal 2.0 V  FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V  FE13 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V  Negative Gain High Byte Differential Unbuffered Internal 2.0 V  Negative Gain Low Byte Differential Unbuffered Internal 2.0 V  FE30 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V  FE31 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V  FE72 Offset Differential Unbuffered Internal 1.0 V  FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V  FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V  FE75 FE75 Offset Differential Unbuffered External 2.0 V  FE76 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0F        | FE0F    | Gain Low Byte           | Single-Ended 1x Buffered | Internal 2.0 V |

| FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V  FE6F Offset Differential Unbuffered Internal 2.0 V  FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V  RE13 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V  Negative Gain High Byte Differential Unbuffered Internal 2.0 V  RE30 Negative Gain High Byte Differential Unbuffered Internal 2.0 V  RE31 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V  FE72 Offset Differential Unbuffered Internal 1.0 V  FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V  RE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  RE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V  FE75 Offset Differential Unbuffered Internal 1.0 V  FE75 Offset Differential Unbuffered External 2.0 V  Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6C        | FE6C    | Offset                  | Single-Ended 1x Buffered | External 2.0 V |

| FE6F Offset Differential Unbuffered Internal 2.0 V FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V FE13 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V Negative Gain High Byte Differential Unbuffered Internal 2.0 V Negative Gain Low Byte Differential Unbuffered Internal 2.0 V FE31 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V FE72 Offset Differential Unbuffered Internal 1.0 V FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V FE34 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V FE35 Diffset Differential Unbuffered Internal 1.0 V FE75 FE75 Offset Differential Unbuffered External 2.0 V FE16 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10        | FE10    | Gain High Byte          | Single-Ended 1x Buffered | External 2.0 V |

| 12 FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V 13 FE13 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V 14 FE30 Negative Gain High Byte Differential Unbuffered Internal 2.0 V 15 FE72 Offset Differential Unbuffered Internal 1.0 V 16 FE15 Positive Gain High Byte Differential Unbuffered Internal 1.0 V 17 FE32 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 18 FE33 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE31 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE32 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Offset Differential Unbuffered Internal 1.0 V 19 FE30 Offset Differential Unbuffered Internal 1.0 V 19 FE31 Differential Unbuffered Internal 1.0 V 19 FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 20 FE31 Differential Unbuffered Internal 1.0 V 21 FE32 Differential Unbuffered Internal 1.0 V 22 FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 23 FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 24 FE35 Differential Unbuffered Internal 1.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11        | FE11    | Gain Low Byte           | Single-Ended 1x Buffered | External 2.0 V |

| FE13 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V Negative Gain High Byte Differential Unbuffered Internal 2.0 V Negative Gain Low Byte Differential Unbuffered Internal 2.0 V FE31 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V FE72 Offset Differential Unbuffered Internal 1.0 V FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V FE75 Offset Differential Unbuffered External 2.0 V FE76 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6F        | FE6F    | Offset                  | Differential Unbuffered  | Internal 2.0 V |

| 30 FE30 Negative Gain High Byte Differential Unbuffered Internal 2.0 V 31 FE31 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V 72 FE72 Offset Differential Unbuffered Internal 1.0 V 14 FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V 15 FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V 32 FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 33 FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 75 FE75 Offset Differential Unbuffered External 2.0 V 16 FE16 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12        | FE12    | Positive Gain High Byte | Differential Unbuffered  | Internal 2.0 V |

| 31 FE31 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V 72 FE72 Offset Differential Unbuffered Internal 1.0 V 14 FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V 15 FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V 32 FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 33 FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 75 FE75 Offset Differential Unbuffered External 2.0 V 16 FE16 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13        | FE13    | Positive Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V |

| FE72 Offset Differential Unbuffered Internal 1.0 V  FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V  RE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  RE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V  FE75 Offset Differential Unbuffered External 2.0 V  FE76 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30        | FE30    | Negative Gain High Byte | Differential Unbuffered  | Internal 2.0 V |

| 14 FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V 15 FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V 32 FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 33 FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 75 FE75 Offset Differential Unbuffered External 2.0 V 16 FE16 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31        | FE31    | Negative Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V |