# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 1KB (1K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 16 x 8                                                       |

| RAM Size                   | 256 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f012ahh020sc    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Interrupt Controller

The Z8 Encore! X<sup>P</sup> F082A Series products support up to 20 interrupts. These interrupts consist of 8 internal periphe**irat**errupts and 12 general-purpose I/O pin interrupt sources. The interrupts have threelbeof programmable interrupt priority.

# **Reset Controller**

The Z8 Encore! XP F082A Seriesophucts can be reset using the RESpirit, Power-On Reset, Watchdorgmer (WDT) time-out, STOP mode exit, or Voltage Brownout (VBO) warning signal. The RESpirit is bi-directional, that is, it functions as reset source as well as a reset indicator.

|                                                       | Reset Characteristics and Latency                      |            |                                                               |  |  |  |

|-------------------------------------------------------|--------------------------------------------------------|------------|---------------------------------------------------------------|--|--|--|

| Reset Type                                            | Control Registers                                      | eZ8<br>CPU | Reset Latency (Delay)                                         |  |  |  |

| System Reset                                          | Reset (as applicable)                                  | Reset      | 66 Internal Precision Oscillator Cycles                       |  |  |  |

| System Reset with Crystal<br>Oscillator Enabled       | Reset (as applicable)                                  | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |

| Stop Mode Recovery                                    | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |  |

| Stop Mode Recovery with<br>Crystal Oscillator Enabled | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |

#### Table 8. Reset and Stop Mode Recovery Characteristics and Latency

During a System Reset or Stop Mode Recovering Internal Precision Oscillator requires 4 µs to start up. Then the Z8 Encore! XP F08224 ries device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the the set oscillator is enabled in the Flash option bits, this reset period is increase **500**0 IPO cycles. When a reset occurs because of a low voltage condition or Recer-On Reset (POR), this delies measured from the time that the supply voltage first exceeds the RPIE vel. If the external pin reset remains asserted at the end of the reset period device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are figured as inputs with pull-up resistor disabled, except PD0 (or PA2 on 8-pin devices) of this shared with the reset pin. On reset, the PD0 is configured as a bidirectional operative reset. The pin is internally driven low during port reset, after which the user contexy reconfigure this pin as a general purpose output.

During Reset, the eZ8 CPU and on-chip periphseare idle; however, the on-chip crystal oscillator and Watchdog Timescillator continue to run.

Upon Reset, control registersithin the Register File that have a defined Reset value are loaded with their reset values. Other contegisters (including the Stack Pointer, Register Pointer, and Flags) and generationse RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addressesand0003H and loads that value into the Program GeurProgram execution begins at the Reset vector address.

As the control registers are matialized by a system reset, etsystem clock after reset is always the IPO. The software must reconfigure oscillator controllock, such that the correct system clock source is enabled and selected.

PAFS1[7:0]—Port Alternate Function Set 1 0 = Port Alternate Function selected as define Dainle 14and Table 15on page 44. 1 = Port Alternate Function selected as define Dainle 14and Table 15on page 44.

Port A–D Alternate Function Set 2 Sub-Registers

The Port A–D Alternate Function Set 2 sub-register to the Port A–D Address register. The Alternate Function Set 2 sub-registers selects the alter function available at a port pin. Alternate Functions selected by setting or clearbings of this register is defined if able 15

Note: Alternate function selection on port pins must also be enabled as described in D Alternate Function Sub-Registeors page 47

| BITS  | 7                                                                                     | 6                                                               | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------|--------|--------|--------|--------|--------|

| FIELD | PAFS27                                                                                | PAFS26                                                          | PAFS25 | PAFS24 | PAFS23 | PAFS22 | PAFS21 | PAFS20 |

| RESET | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device)                    |                                                                 |        |        |        |        |        |        |

| R/W   | R/W                                                                                   | R/W         R/W         R/W         R/W         R/W         R/W |        |        |        |        |        |        |

| ADDR  | If 08H in Port A–D Address Register, accessible through the Port A–D Control Register |                                                                 |        |        |        |        |        |        |

Table 26. Port A–D Alternate Function Set 2 Sub-Registers (PxAFS2)

PAFS2[7:0]—Port Alternate Function Set 2

0 = Port Alternate Function selected as definedable 15

1 = Port Alternate Function selected as define Daiole 15

# Port A–C Input Data Registers

Reading from the Port A–Coput Data registers (able 27) returns the sampled values from the corresponding portrys. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those missing on the 8- and 28-pin packages, as well as those missing the ADC-enabled 28-pin packages.

| BITS                  | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----------------------|------|------|------|------|------|------|------|------|

| FIELD                 | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |

| RESET                 | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| R/W                   | R    | R    | R    | R    | R    | R    | R    | R    |

| ADDR FD2H, FD6H, FDAH |      |      |      |      |      |      |      |      |

| X = Undefined.        |      |      |      |      |      |      |      |      |

| Table 32. Trap and Interrupt Vectors in Order of Priority |

|-----------------------------------------------------------|

| Priority       Vector Address       Interrupt or Trap Source         Highest       0002H       Reset (not an interrupt)         0004H       Watchdog Timer (see Watchdog Timer on page 91)         003AH       Primary Oscillator Fail Trap (not an interrupt)         003CH       Watchdog Oscillator Fail Trap (not an interrupt)         003CH       Watchdog Oscillator Fail Trap (not an interrupt)         0008H       Reserved         0000CH       Timer 1         000CH       UART 0 receiver         0010H       UART 0 receiver         0012H       Reserved         0012H       Reserved         0012H       Reserved         0012H       Reserved         0012H       Reserved         0012H       Reserved         0016H       ADC         0016H       ADC         0018H       Port A Pin 7, selectable rising or falling input edge or Comparator Output         001CH       Port A Pin 5, selectable rising or falling input edge         001CH       Port A Pin 7, selectable rising or falling input edge         0012H       Port A Pin 3, selectable rising or falling input edge         0012H       Port A Pin 3, selectable rising or falling input edge         0020H       Port A Pin 1, selectable ri                                                                                  |          | Program<br>Memory |                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------|----------------------------------------------------------------------------|

| 0004H       Watchdog Timer (see Watchdog Timer on page 91)         003AH       Primary Oscillator Fail Trap (not an interrupt)         003CH       Watchdog Oscillator Fail Trap (not an interrupt)         0006H       Illegal Instruction Trap (not an interrupt)         0008H       Reserved         0000H       Timer 1         000CH       Timer 0         000EH       UART 0 receiver         0010H       UART 0 transmitter         0012H       Reserved         0014H       Reserved         0014H       Reserved         0014H       Reserved         0014H       Reserved         0014H       Reserved         0018H       Port A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23)         001AH       Port A Pin 5, selectable rising or falling input edge         001CH       Port A Pin 5, selectable rising or falling input edge         002DH       Port A Pin 5, selectable rising or falling input edge         002DH       Port A Pin 5, selectable rising or falling input edge         002DH       Port A Pin 3, selectable rising or falling input edge         002DH       Port A Pin 4, selectable rising or falling input edge         002DH       Port A Pin 1, selectable ri                             | Priority | Vector Address    | Interrupt or Trap Source                                                   |

| 003AH       Primary Oscillator Fail Trap (not an interrupt)         003CH       Watchdog Oscillator Fail Trap (not an interrupt)         0006H       Illegal Instruction Trap (not an interrupt)         0008H       Reserved         0000CH       Timer 1         000CH       Timer 0         000EH       UART 0 receiver         0010H       UART 0 transmitter         0012H       Reserved         0014H       Reserved         0012H       Reserved         0014H       Reserved         0014H       Reserved         0014H       Reserved         0018H       Port A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23)         001AH       Port A Pin 6, selectable rising or falling input edge         001CH       Port A Pin 5, selectable rising or falling input edge         001CH       Port A Pin 5, selectable rising or falling input edge         002DH       Port A Pin 1, selectable rising or falling input edge         002H       Port A Pin 2, selectable rising or falling input edge         002H       Port A Pin 1, selectable rising or falling input edge         002H       Port A Pin 0, selectable rising or falling input edge         002H       Port A Pin 0, selectabl                             | Highest  | 0002H             | Reset (not an interrupt)                                                   |

| 003CH       Watchdog Oscillator Fail Trap (not an interrupt)         0006H       Illegal Instruction Trap (not an interrupt)         0008H       Reserved         0000AH       Timer 1         000CH       Timer 0         000EH       UART 0 receiver         0010H       UART 0 transmitter         0012H       Reserved         0014H       Reserved         0016H       ADC         0018H       Port A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23)         001AH       Port A Pin 6, selectable rising or falling input edge         001CH       Port A Pin 5, selectable rising or falling input edge         001EH       Port A Pin 5, selectable rising or falling input edge         002H       Port A Pin 4, selectable rising or falling input edge         002H       Port A Pin 2, selectable rising or falling input edge         002H       Port A Pin 1, selectable rising or falling input edge         002H       Port A Pin 0, selectable rising or falling input edge         002H       Port A Pin 0, selectable rising or falling input edge         002H       Port A Pin 1, selectable rising or falling input edge         002H       Port A Pin 0, selectable rising or falling input edge         002H |          | 0004H             | Watchdog Timer (see Watchdog Timer on page 91)                             |

| 0006H       Illegal Instruction Trap (not an interrupt)         0008H       Reserved         000AH       Timer 1         000CH       Timer 0         000EH       UART 0 receiver         0010H       UART 0 transmitter         0012H       Reserved         0014H       Reserved         0016H       ADC         0018H       Port A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23)         001AH       Port A Pin 6, selectable rising or falling input edge         001CH       Port A Pin 5, selectable rising or falling input edge         001CH       Port A Pin 5, selectable rising or falling input edge         001CH       Port A Pin 3, selectable rising or falling input edge         0020H       Port A Pin 3, selectable rising or falling input edge         0022H       Port A Pin 1, selectable rising or falling input edge         0022H       Port A Pin 0, selectable rising or falling input edge         0028H       Reserved         0022H       Port A Pin 0, selectable rising or falling input edge         0022H       Reserved         0022H       Reserved         0022H       Reserved         0022H       Reserved         0022H                                                                  |          | 003AH             | Primary Oscillator Fail Trap (not an interrupt)                            |

| 0008H       Reserved         000AH       Timer 1         000CH       Timer 0         000EH       UART 0 receiver         0010H       UART 0 transmitter         0012H       Reserved         0016H       ADC         0016H       ADC         0018H       Port A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23)         001AH       Port A Pin 6, selectable rising or falling input edge         001CH       Port A Pin 5, selectable rising or falling input edge         001EH       Port A Pin 5, selectable rising or falling input edge         0020H       Port A Pin 4, selectable rising or falling input edge         0020H       Port A Pin 3, selectable rising or falling input edge         0022H       Port A Pin 2, selectable rising or falling input edge         0022H       Port A Pin 1, selectable rising or falling input edge         0022H       Port A Pin 0, selectable rising or falling input edge         0028H       Reserved         002AH       Reserved         002CH       Reserved         002CH       Reserved         002CH       Reserved         002CH       Reserved         002CH       Reserved                                                                                           |          | 003CH             | Watchdog Oscillator Fail Trap (not an interrupt)                           |

| 000AH       Timer 1         000CH       Timer 0         000EH       UART 0 receiver         0010H       UART 0 transmitter         0012H       Reserved         0014H       Reserved         0016H       ADC         0018H       Port A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23)         001AH       Port A Pin 6, selectable rising or falling input edge         001CH       Port A Pin 5, selectable rising or falling input edge         001EH       Port A Pin 5, selectable rising or falling input edge         001EH       Port A Pin 4, selectable rising or falling input edge         0020H       Port A Pin 3, selectable rising or falling input edge         0022H       Port A Pin 1, selectable rising or falling input edge         0022H       Port A Pin 1, selectable rising or falling input edge         0022H       Port A Pin 0, selectable rising or falling input edge         0026H       Port A Pin 0, selectable rising or falling input edge         0028H       Reserved         002CH       Reserved         002CH       Reserved         002EH       Reserved         002EH       Reserved         002EH       Reserved         0030H<                                                       |          | 0006H             | Illegal Instruction Trap (not an interrupt)                                |

| 000CH       Timer 0         000EH       UART 0 receiver         0010H       UART 0 transmitter         0012H       Reserved         0014H       Reserved         0016H       ADC         0018H       Port A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23)         001AH       Port A Pin 6, selectable rising or falling input edge or Comparator Output         001CH       Port A Pin 5, selectable rising or falling input edge         001EH       Port A Pin 3, selectable rising or falling input edge         0020H       Port A Pin 3, selectable rising or falling input edge         0022H       Port A Pin 1, selectable rising or falling input edge         0026H       Port A Pin 0, selectable rising or falling input edge         0026H       Port A Pin 0, selectable rising or falling input edge         0028H       Reserved         002CH       Reserved         002CH       Reserved         002EH       Reserved         002EH       Reserved         002EH       Reserved         002EH       Reserved         002EH       Reserved         0030H       Port C Pin 3, both input edges                                                                                                                    |          | 0008H             | Reserved                                                                   |

| 000EHUART 0 receiver0010HUART 0 transmitter0012HReserved0014HReserved0016HADC0018HPort A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop<br>Mode Recovery, and Low Voltage Detection on page 23)001AHPort A Pin 6, selectable rising or falling input edge or Comparator Output001CHPort A Pin 5, selectable rising or falling input edge001EHPort A Pin 4, selectable rising or falling input edge0020HPort A Pin 3, selectable rising or falling input edge0022HPort A Pin 1, selectable rising or falling input edge0026HPort A Pin 1, selectable rising or falling input edge0028HReserved0020HPort A Pin 0, selectable rising or falling input edge0028HReserved0028HReserved002EHReserved002EHReserved0030HPort C Pin 3, both input edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | 000AH             | Timer 1                                                                    |

| 0010H       UART 0 transmitter         0012H       Reserved         0014H       Reserved         0016H       ADC         0018H       Port A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23)         001AH       Port A Pin 6, selectable rising or falling input edge or Comparator Output         001CH       Port A Pin 5, selectable rising or falling input edge         001EH       Port A Pin 3, selectable rising or falling input edge         0020H       Port A Pin 3, selectable rising or falling input edge         0022H       Port A Pin 2, selectable rising or falling input edge         0026H       Port A Pin 1, selectable rising or falling input edge         0026H       Port A Pin 0, selectable rising or falling input edge         0026H       Port A Pin 0, selectable rising or falling input edge         0026H       Reserved         0028H       Reserved         002CH       Reserved         002CH       Reserved         002EH       Reserved         002EH       Reserved         0030H       Port C Pin 3, both input edges                                                                                                                                                                    |          | 000CH             | Timer 0                                                                    |

| 0012H       Reserved         0014H       Reserved         0016H       ADC         0018H       Port A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23)         001AH       Port A Pin 6, selectable rising or falling input edge or Comparator Output         001CH       Port A Pin 5, selectable rising or falling input edge         001EH       Port A Pin 3, selectable rising or falling input edge         0020H       Port A Pin 3, selectable rising or falling input edge         0022H       Port A Pin 2, selectable rising or falling input edge         0026H       Port A Pin 1, selectable rising or falling input edge         0026H       Port A Pin 0, selectable rising or falling input edge         0028H       Reserved         002CH       Reserved         002CH       Reserved         002CH       Reserved         002CH       Reserved         002CH       Reserved         002EH       Reserved         0030H       Port C Pin 3, both input edges                                                                                                                                                                                                                                                        |          | 000EH             | UART 0 receiver                                                            |

| 0014HReserved0016HADC0018HPort A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop<br>Mode Recovery, and Low Voltage Detection on page 23)001AHPort A Pin 6, selectable rising or falling input edge or Comparator Output001CHPort A Pin 5, selectable rising or falling input edge001EHPort A Pin 4, selectable rising or falling input edge0020HPort A Pin 3, selectable rising or falling input edge0022HPort A Pin 2, selectable rising or falling input edge0026HPort A Pin 1, selectable rising or falling input edge0028HReserved0028HReserved002CHReserved002CHReserved002CHReserved002CHReserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          | 0010H             | UART 0 transmitter                                                         |

| 0016HADC0018HPort A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop<br>Mode Recovery, and Low Voltage Detection on page 23)001AHPort A Pin 6, selectable rising or falling input edge or Comparator Output001CHPort A Pin 5, selectable rising or falling input edge001EHPort A Pin 4, selectable rising or falling input edge0020HPort A Pin 3, selectable rising or falling input edge0022HPort A Pin 2, selectable rising or falling input edge0026HPort A Pin 1, selectable rising or falling input edge0028HReserved002AHReserved002CHReserved002CHReserved002CHReserved002CHReserved002CHReserved002CHReserved002CHReserved002CHReserved002CHReserved002CHReserved002CHReserved002CHReserved0030HPort C Pin 3, both input edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | 0012H             | Reserved                                                                   |

| 0018HPort A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop<br>Mode Recovery, and Low Voltage Detection on page 23)001AHPort A Pin 6, selectable rising or falling input edge or Comparator Output001CHPort A Pin 5, selectable rising or falling input edge001EHPort A Pin 4, selectable rising or falling input edge0020HPort A Pin 3, selectable rising or falling input edge0022HPort A Pin 2, selectable rising or falling input edge0024HPort A Pin 1, selectable rising or falling input edge0026HPort A Pin 0, selectable rising or falling input edge0028HReserved002CHReserved002CHReserved002CHReserved002CHReserved002CHReserved002CHReserved0030HPort C Pin 3, both input edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | 0014H             | Reserved                                                                   |

| Mode Recovery, and Low Voltage Detection on page 23)001AHPort A Pin 6, selectable rising or falling input edge or Comparator Output001CHPort A Pin 5, selectable rising or falling input edge001EHPort A Pin 4, selectable rising or falling input edge0020HPort A Pin 3, selectable rising or falling input edge0022HPort A Pin 2, selectable rising or falling input edge0024HPort A Pin 1, selectable rising or falling input edge0026HPort A Pin 0, selectable rising or falling input edge0028HReserved002AHReserved002CHReserved002EHReserved002EHReserved0030HPort C Pin 3, both input edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | 0016H             | ADC                                                                        |

| 001CHPort A Pin 5, selectable rising or falling input edge001EHPort A Pin 4, selectable rising or falling input edge0020HPort A Pin 3, selectable rising or falling input edge0022HPort A Pin 2, selectable rising or falling input edge0024HPort A Pin 1, selectable rising or falling input edge0026HPort A Pin 0, selectable rising or falling input edge0028HReserved0028HReserved002CHReserved002CHReserved002CHReserved002CHReserved002CHReserved002EHReserved0030HPort C Pin 3, both input edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | 0018H             |                                                                            |

| 001EHPort A Pin 4, selectable rising or falling input edge0020HPort A Pin 3, selectable rising or falling input edge0022HPort A Pin 2, selectable rising or falling input edge0024HPort A Pin 1, selectable rising or falling input edge0026HPort A Pin 0, selectable rising or falling input edge0028HReserved002AHReserved002CHReserved002CHReserved002CHReserved002CHReserved002CHReserved002CHReserved002CHReserved002CHReserved002CHReserved002CHReserved0030HPort C Pin 3, both input edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | 001AH             | Port A Pin 6, selectable rising or falling input edge or Comparator Output |

| 0020HPort A Pin 3, selectable rising or falling input edge0022HPort A Pin 2, selectable rising or falling input edge0024HPort A Pin 1, selectable rising or falling input edge0026HPort A Pin 0, selectable rising or falling input edge0028HReserved002AHReserved002CHReserved002EHReserved002EHReserved0030HPort C Pin 3, both input edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | 001CH             | Port A Pin 5, selectable rising or falling input edge                      |

| 0022HPort A Pin 2, selectable rising or falling input edge0024HPort A Pin 1, selectable rising or falling input edge0026HPort A Pin 0, selectable rising or falling input edge0028HReserved002AHReserved002CHReserved002EHReserved002EHReserved0030HPort C Pin 3, both input edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | 001EH             | Port A Pin 4, selectable rising or falling input edge                      |

| 0024HPort A Pin 1, selectable rising or falling input edge0026HPort A Pin 0, selectable rising or falling input edge0028HReserved002AHReserved002CHReserved002EHReserved0030HPort C Pin 3, both input edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | 0020H             | Port A Pin 3, selectable rising or falling input edge                      |

| 0026H       Port A Pin 0, selectable rising or falling input edge         0028H       Reserved         002AH       Reserved         002CH       Reserved         002EH       Reserved         0030H       Port C Pin 3, both input edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | 0022H             | Port A Pin 2, selectable rising or falling input edge                      |

| 0028H     Reserved       002AH     Reserved       002CH     Reserved       002EH     Reserved       0030H     Port C Pin 3, both input edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | 0024H             | Port A Pin 1, selectable rising or falling input edge                      |

| 002AHReserved002CHReserved002EHReserved0030HPort C Pin 3, both input edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | 0026H             | Port A Pin 0, selectable rising or falling input edge                      |

| 002CHReserved002EHReserved0030HPort C Pin 3, both input edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          | 0028H             | Reserved                                                                   |

| 002EH     Reserved       0030H     Port C Pin 3, both input edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | 002AH             | Reserved                                                                   |

| 0030H Port C Pin 3, both input edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | 002CH             | Reserved                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | 002EH             | Reserved                                                                   |

| 0032H Port C Pin 2, both input edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | 0030H             | Port C Pin 3, both input edges                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | 0032H             | Port C Pin 2, both input edges                                             |

#### **CAPTURE RESTART mode**

0 = Count is captured on the risiedge of the Timer Input signal.

1 = Count is captured on the fabinedge of the Timer Input signal.

#### **COMPARATOR COUNTER mode**

When the timer is disabled, the Timer Outpignal is set to the value of this bit. When the timer is enabled, the Timer Outpignal is complemented upon timer Reload. Also:

0 = Count is captured on the rising edge of the comparator output.

1 = Count is captured on the fablinedge of the comparator output.

Caution: When the Timer Output alternate function OUT on a GPIO port pin is enabled, TxOUT changes to whatever state the TPOL bit. The timer does not need to be enabled for that to happen. Also, the Port dataection sub register is not needed to be set to output on TxOUT. Changing the TPIONL with the timer enabled and running does not immediately change the TxOUT.

#### PRES—Prescale value

The timer input clock is divided by  $P2^{ES}$ , where PRES can be set from 0 to 7. The prescaler is reset each time the Timer is disabled. This reset ensures proper clock division each time the Timer is restarted.

000 = Divide by 1 001 = Divide by 2 010 = Divide by 4 011 = Divide by 8 100 = Divide by 16 101 = Divide by 32 110 = Divide by 64111 = Divide by 128

#### TMODE—Timer mode

This field along with the TMODEHI bit in xCTL0 register determines the operating mode of the timer. TMODEHI is the most paificant bit of the Timer mode selection value. The entire operating mode bite expressed as {TMODEHI, TMODE[2:0]}. The TMODEHI is bit 7 of the TxCTL0 register vile TMODE[2:0] is the lower 3 bits of the TxCTL1 register.

0000 = ONE-SHOT mode 0001 = CONTINUOUS mode 0010 = COUNTER mode 0011 = PWM SINGLE OUTPUT mode 0100 = CAPTURE mode 0101 = COMPARE mode 0110 = GATED mode 0111 = CAPTURE/COMPARE mode

WDT Reset in Normal Operation

If configured to generate a Reset when aetimat occurs, the Watchdog Timer forces the device into the System Reset state. The TVsDatus bit in the Reset Status (RSTSTAT) register is set to 1. For more information on system reset, Stop Mode Recovery, and Low Voltage Detection page 23.

#### WDT Reset in STOP Mode

If configured to generate a Reset when a **time** eccurs and the device is in STOP mode, the Watchdog Timer initiates Stop Mode Recovery. Bothe WDT status bit and the STOP bit in the Reset Status (RSTSTAT) registare set to 1 following WDT time-out in STOP mode.

# Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence **to**e Watchdog Timer (WDTCTLC ontrol register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These e operations to the WDTCTL register address produce no effect on the bitshie WDTCTL register. The locking mechanism prevents spurious writes the Reload registers. Followet below to unlock the Watchdog Timer Reload Byte registe **(WDTU, WDTH)** for write access.

- 1. Write 55H to the Watchdog Timer Control register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upperte register (WDTU) with the desired time-out value.

- 4. Write the Watchdog Timer Reload Highyte register (WDTH) with the desired time-out value.

- 5. Write the Watchdog Timer Reload Low Byregister (WDTL) with the desired time-out value.

All three Watchdog Timer Reload registers moust written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and **rtbefu** writes can occur unless the sequence is restarted. The value in the Watchdog Timelo Red registers is loaded into the counter when the Watchdog Timer **fis**st enabled and every time a WDT instruction is executed.

# Watchdog Timer Calibration

Due to its extremely low opæting current, the Watchdog Timer oscillator is somewhat inaccurate. This variation can be corrected gushe calibration data stored in the Flash Information Page (setable 97 and Table 98 on page 165). Loading these values into the

Receiving Data using the Interrupt-Driven Method

The UART Receiver interruphdicates the availability of new data (as well as error conditions). Follow the steps below to counting the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Lobyte registers to set the acceptable baud rate.

- 2. Enable the UART pin functions by confiring the associated GPIO Port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registersenable the UART Receiver interrupt and set the acceptable priority.

- 5. Clear the UART Receiver interrupt inethapplicable InterrupRequest register.

- 6. Write to the UART Control 1 Regist**tor** enable Multiprocessor (9-bit) mode functions, if appropriate.

- Set the Multiprocessor Mode Selexap(EN) to Enable MULTIPROCESSOR mode.

- Set the Multiprocessor Mode Bits, MPMD[1;0] o select the acceptable address matching scheme.

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encondevices without a DMA block)

- 7. Write the device address to the Address pare Register (automatic MULTIPRO-CESSOR modes only).

- 8. Write to the UART Control 0 register to:

- Set the receive enable bitte(n) to enable the UARTor data reception

- Enable parity, if appropriate and if multipressor mode is nethabled, and select either even or odd parity.

- 9. Execute an El instrtion to enable interrupts.

The UART is now configure for interrupt-driven dataeception. When the UART Receiver interrupt is detected, the assectianterrupt service roline (ISR) performs the following:

- 1. Checks the UART Status 0 register to **dete**e the source of the interrupt error, break, or received data.

- 2. Reads the data from the UART Receive Data register if the interrupt was because of data available. If operating in MULTIPROCESSOR (9-bit) mode, further actions may be required depending on the MUPROCESSOR mode bits MPMD[1:0].

send. This action provides 7 bit periods **défacy** to load the Transmit Data register before the Transmit shift register comple**stati**fting the current character. Writing to the UART Transmit Data register clears the TDRE bit to 0.

#### Receiver Interrupts

The receiver generates an interruptien any of the following occurs:

- A data byte is received and is available in the UART Receive Data register. This interrupt can be disabled independently the other receiver interrupt sources. The received data interrupt occurs after the receive character has been received and placed in the Receive Data register. To avoid are run error, software must respond to this received data available condition before the next character is completely received.

- Note: In MULTIPROCESSOR mod  $\mathfrak{B}\mathfrak{P}(EN = 1)$ , the receive data interrupts are dependent on the multiprocess **o** on figuration and the **nso** recent address byte.

- A break is received.

- An overrun is detected.

- A data framing error is detected.

## UART Overrun Errors

When an overrun error condition ccurs the UART prevents verwriting of the valid data currently in the Receive Data register. The Br Detect and Overrun status bits are not displayed until after the **vial** data has been read.

After the valid data has been read, the UARatust 0 register is updated to indicate the overrun condition (and Break Detect, if applicable). The bit is set to 1 to indicate that the Receive Data register contains a data byte. However, because the overrun error occurred, this byte may not contain validadand must be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status byte indicating an overrun errothe Receive Data register must be read again to clear the error bits is the UART Status 0 register. Update the Receive Data register occur only when the next data word is received.

## UART Data and Error Handling Procedure

Figure 15 displays the recommended procedure for use in UART receiver interrupt service routines.

Endec, and passed to the UART. Com**ination** is half-duplex, which means simultaneous data transmissigned reception is not allowed.

The baud rate is set by the UART's Baud Ratenerator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled se the Infrared Endec Endec be Infrared Endec data rate is calculated ing the following equation:

Infrared Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

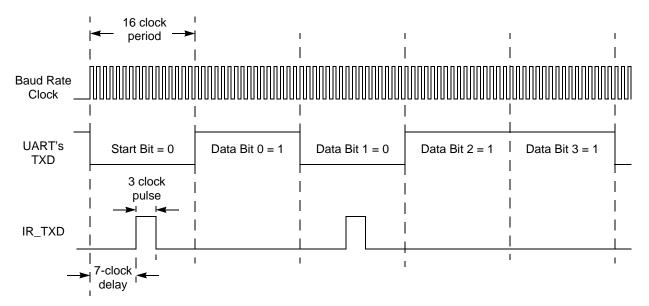

# Transmitting IrDA Data

The data to be transmitted using the infrared sceiver is first **ste** to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drivest hinfrared transceiver. Each UART/Infrared data bit is 16 clocks wide. If the datable transmitted is 1, the IR\_TXD signal remains low for the full 16 clock period. If the datable transmitted is 0, the transmitter first outputs a 7 clock low period, followed by a 3 clock high pulse. Finally, a 6 clock low pulse is output to complete the **I**Iu16 clock data periodFigure 17displays IrDA data transmission. When the Infrared Endec is enabled, UART's TXD signal is internal to the Z8 Encore! XIP F082A Series product while the IR\_TXD signals output through the TXD pin.

Figure 17. Infrared Data Transmission

baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse detected inside this windowish process is repeated. If the incoming data is a logical 1 (no pulse), the endec returns to the itial state and waits for the next falling edge. As each falling edge detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming datastre the errors in the incoming datastre the errors in the incoming datastre the data. The UART is only synchronized to the incoming data star when a Start bit is received.

# Infrared Encoder/Decoder C ontrol Register Definitions

All Infrared Endec configuration and stations ormation is set by the UART control registers as defined Indiversal Asynchronou Receiver/Transmittee page 97.

Caution: To prevent spurious signals during IrDA dataransmission, set the IREN bit in the UART Control 1 register to 1 to enable the fore enabling the GPIO Port alternate furtion for the corresponding pin.

- 3. Write to the ADC Control Register to configure the ADC focontinuous conversion. The bit fields in the ADC Control gester may be written simultaneously:

- Write to theANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- SetCONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the EXT bit to 1. The internal voltage reference refue enabled in this case.

- Write therefsell bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level ordisable the internal reference. The REFSELH bit is contained in ADC Control/Status Register 1

- SetCEN to 1 to start the conversions.

- 4. When the first conversion in continuous eration is complete (after 5129 system clock cycles, plus the 40 cycles for power, if necessary), the ADC control logic performs the following operations:

- CEN resets to 0 to indicate the st conversion is completeen remains 0 for all subsequent conversions in continuous operation.

- An interrupt request is sent to the conversion is complete.

- 5. The ADC writes a new data result every 256 system clock cycles. For each completed conversion, the ADC control logizerforms the following operations:

- Writes the 13-bit two's complement result to {ADCD\_H[7:0], ADCD\_L[7:3]}.

- Sends an interrupt request to the **trupt** Controller denoting conversion complete.

- 6. To disable continuous conversion, clear the T bit in the ADC Control Register to 0.

## Interrupts

The ADC is able to interrupt the CPU whenconversion has been mpleted. When the ADC is disabled, no new interrupts are assetted vever, an interrupt pending when the ADC is disabled is not cleared.

# Calibration and Compensation

The Z8 Encore! X<sup>P</sup> F082A Series ADC is factory calibrated for offset error and gain error, with the compensation data store familiansh memory. Alternately, you can perform your own calibration, storing the values in the selves. Thirdly, the user code can perform a manual offset calibration during DIFFERENTIAL mode operation.

Factory Calibration

Devices that have been factory calibrated **aimn8**0 bytes of calibration data in the Flash option bit space. This data civests of 3 bytes for each inpunode, one for offset and two for gain correction. For last of input modes for while calibration data exists, see Og Calibration Dataon page 161.

User Calibration

If you have precision references availalitie own external calibration can be performed using any input modes. This calibration **data** into account buffer offset and non-linearity, so it is recommended that this calibora be performed separately for each of the ADC input modes planned for use.

## Manual Offset Calibration

When uncalibrated, the ADC has significant offset (**Sade** 135on page 231). Subsequently, manual offset calibrition capability is built ito the block. When the ADC Control Register (Sets the input mode.t(AIN [2:0]) to MANUAL OFFSET CALIBRATION mode, the differential inputs the ADC are shorted together by an internal switch. Reading the ADC value at this interproduces 0 in an east system. The value actually read is the ADC offset. This values are stored in non-volatile memory (see Non-Volatile Data Storagen page 169) and accessed by user code to compensate for the input offset error. There is no purision for manual gain calibration.

Software Compensation Procedure Using Factory Calibration Data

The value read from the ADC high and lowteby egisters is uncompensated. The user mode software must apply gain and of fiscent rection to this uncompensated value for maximum accuracy. The following equation yields the compensated value:

$ADC_{comp} = (ADC_{uncomp} - OFFCAL) + ((ADC_{uncomp} - OFFCAL) \times GAINCAL)/2^{16}$

where GAINCAL is the gain calibration valueFFCAL is the offset calibration value and ADC<sub>uncomp</sub> is the uncompensated value read fither ADC. All values are in two's complement format.

Note: The offset compensation is performed fifstlowed by the gain compensation. One bit of resolution is lost because of rounding both the offset and gain computations. As a result the ADC registers read back 1t3:b1 sign bit, two calibration bits lost to rounding and 10 data bits.

Also note that in the second term, the tiplication must be performed before the division by  $2^6$ . Otherwise, the second term correctly evaluates to zero.

# Z8 Encore! XP <sup>®</sup> F082A Series Product Specification

128

Compensation Steps:

1. Correct for Offset

| ADC MSB    | ADC LSB    |

|------------|------------|

| 7,20 1102  | 100 200    |

| -          |            |

| Offset MSB | Offset LSB |

| =          |            |

| #1 MSB     | #1 LSB     |

2. Take absolute value of the offset corrected ADC via huegative—the gain correction factor is computed assuming positive nuemes with sign restoration afterward.

| #2 MSB #2 | LSB |

|-----------|-----|

|-----------|-----|

Also take absolute value drie gain correction world negative

| AGain MSB | AGain LSB |

|-----------|-----------|

|-----------|-----------|

3. Multiply by Gain Correction Word. If inDIFFERENTIAL mode, there are two gain correction values: one for positive ADClwes, another for negative ADC values. Based on the sign of #2, use the propriate Gain Correction Word.

| #2 MSB    | #2 LSB    |

|-----------|-----------|

| *         |           |

| AGain MSB | AGain LSB |

| =         |           |

| #3 #3 | #3 | #3 |

|-------|----|----|

|-------|----|----|

Round the result and discard the leastificities two bytes (this is equivalent to dividing by 2<sup>16</sup>).

| #3   | #3   | #3   | #3   |  |  |  |  |

|------|------|------|------|--|--|--|--|

|      |      |      |      |  |  |  |  |

| 0x00 | 0x00 | 0x80 | 0x00 |  |  |  |  |

| =    |      |      |      |  |  |  |  |

|      |      | 7    |      |  |  |  |  |

- #4 MSB #4 LSB

- 5. Determine sign of the gain cortient factor using the sign bits frontee 2 If the offset corrected ADC value AND the gain correction word have the same sign, then the factor is positive and is left unchangle they have differing signs, then the factor is negative and must be multiplied by -1.

#### ANAIN[3:0]—Analog Input Select

These bits select the analog infor conversion. Not all Port pins in this list are available in all packages for the Z8 Encore! RF082A Series. For information on port pins available with each package style, see Description page 9. Do not enable unavailable analog inputs. Usage of these bits chards and on the buffer mode selected DC Control/Status Register 1

For the reserved values, all intrestrictes are disabled to avoid leakage or other undesirable operation. ADC samples taken wites erved bit settings are undefined.

SINGLE-ENDED:

- 0000 = ANA0 (transimpedance amp output when enabled)

- 0001 = ANA1 (transimpedance amp inverting input)

- 0010 = ANA2 (transimpedance amp non-inverting input)

- 0011 = ANA3

- 0100 = ANA4

- 0101 = ANA5

- 0110 = ANA6

- 0111 = ANA7

- 1000 = Reserved

- 1001 = Reserved

- 1010 = Reserved

- 1011 = Reserved

- 1100 = Hold transimpedance input des (ANA1 and ANA2) to ground.

- 1101 = Reserved

- 1110 = Temperature Sensor.

- 1111 = Reserved.

DIFFERENTIAL (non-inverting input an inverting input respectively):

0000 = ANA0 and ANA1 0001 = ANA2 and ANA3 0010 = ANA4 and ANA50011 = ANA1 and ANA00100 = ANA3 and ANA2 0101 = ANA5 and ANA4 0110 = ANA6 and ANA5 0111 = ANA0 and ANA21000 = ANA0 and ANA3 1001 = ANA0 and ANA4 1010 = ANA0 and ANA5 1011 = Reserved1100 = Reserved1101 = Reserved1110 = Reserved1111 = Manual Offset Calibration Mode

| Info Page<br>Address | Memory<br>Address | Compensation Usage      | ADC Mode                 | Reference<br>Type |

|----------------------|-------------------|-------------------------|--------------------------|-------------------|

| 60                   | FE60              | Offset                  | Single-Ended Unbuffered  | Internal 2.0 V    |

| 08                   | FE08              | Gain High Byte          | Single-Ended Unbuffered  | Internal 2.0 V    |

| 09                   | FE09              | Gain Low Byte           | Single-Ended Unbuffered  | Internal 2.0 V    |

| 63                   | FE63              | Offset                  | Single-Ended Unbuffered  | Internal 1.0 V    |

| 0A                   | FE0A              | Gain High Byte          | Single-Ended Unbuffered  | Internal 1.0 V    |

| 0B                   | FE0B              | Gain Low Byte           | Single-Ended Unbuffered  | Internal 1.0 V    |

| 66                   | FE66              | Offset                  | Single-Ended Unbuffered  | External 2.0 V    |

| 0C                   | FE0C              | Gain High Byte          | Single-Ended Unbuffered  | External 2.0 V    |

| 0D                   | FE0D              | Gain Low Byte           | Single-Ended Unbuffered  | External 2.0 V    |

| 69                   | FE69              | Offset                  | Single-Ended 1x Buffered | Internal 2.0 V    |

| 0E                   | FE0E              | Gain High Byte          | Single-Ended 1x Buffered | Internal 2.0 V    |

| 0F                   | FE0F              | Gain Low Byte           | Single-Ended 1x Buffered | Internal 2.0 V    |

| 6C                   | FE6C              | Offset                  | Single-Ended 1x Buffered | External 2.0 V    |

| 10                   | FE10              | Gain High Byte          | Single-Ended 1x Buffered | External 2.0 V    |

| 11                   | FE11              | Gain Low Byte           | Single-Ended 1x Buffered | External 2.0 V    |

| 6F                   | FE6F              | Offset                  | Differential Unbuffered  | Internal 2.0 V    |

| 12                   | FE12              | Positive Gain High Byte | Differential Unbuffered  | Internal 2.0 V    |

| 13                   | FE13              | Positive Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V    |

| 30                   | FE30              | Negative Gain High Byte | Differential Unbuffered  | Internal 2.0 V    |

| 31                   | FE31              | Negative Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V    |

| 72                   | FE72              | Offset                  | Differential Unbuffered  | Internal 1.0 V    |

| 14                   | FE14              | Positive Gain High Byte | Differential Unbuffered  | Internal 1.0 V    |

| 15                   | FE15              | Positive Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V    |

| 32                   | FE32              | Negative Gain High Byte | Differential Unbuffered  | Internal 1.0 V    |

| 33                   | FE33              | Negative Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V    |

| 75                   | FE75              | Offset                  | Differential Unbuffered  | External 2.0 V    |

| 16                   | FE16              | Positive Gain High Byte | Differential Unbuffered  | External 2.0 V    |

| 17                   | FE17              | Positive Gain Low Byte  | Differential Unbuffered  | External 2.0 V    |

# Table 94. ADC Calibration Data Location

resides in working register R0. The bit **de**lof this status byte are defined **Tim**ble 103. The contents of the status byte are underfifor write operations illegal addresses. Also, user code must pop the **aetss** and data bytes off the stack.

The write routine uses 13 bytefsstack space in addition to the two bytes of address and data pushed by the user.ffsuient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS writes exhibit a non-uniform execution time. In general, a write takes 253 (assuming a 20 MHz system clock). Every 400 to 500 writes, however, a maintence operation is necessary. In this rare occurrence, the write takes up to 61 ms to complete. Slowgestem clock speeds result in proportionally higher execution times.

NVDS byte writes to invalid addresses (thexeeeding the NVDS array size) have no effect. Illegal write operations have all execution time.

Table 103. Write Status Byte

| BITS             | 7        | 6 | 5 | 4 | 3    | 2  | 1   | 0 |

|------------------|----------|---|---|---|------|----|-----|---|

| FIELD            | Reserved |   |   |   | RCPY | PF | DWE |   |

| DEFAULT<br>VALUE | 0        | 0 | 0 | 0 | 0    | 0  | 0   | 0 |

Reserved-Must be 0.

RCPY—Recopy Subroutine Executed

A recopy subroutine was executed. These adjuents take significantly longer than a normal write operation.

PF—Power Failure Indicator

A power failure or system reset occurred **dgri**he most recent attempted write to the NVDS array.

AW—Address Write Error

An address byte failure occurred during **the**st recent attempted write to the NVDS array.

DWE—Data Write Error

A data byte failure occurred during the **sho**ecent attempted write to the NVDS array.

# Byte Read

To read a byte from the NVDS array, used const first push the address onto the stack. User code issues CALL instruction to the address of etbyte-read routine (0x1000). At the return from the sub-routine read byte resides in working register R0, and the read status byte resides in working register R1. Tobaetents of the status byte are undefined for

High. Because of the open-drain nature of DBG pin, the host can send a Serial Break to the OCD even if the OCB transmitting a character.

OCD Unlock Sequence (8-Pin Devices Only)

Because of pin-sharing on the 8-pin device, an unlock sequence must be performed to access the DBG pin. If this sequence is control pleted during a system reset, then the PA0/DBG pin functions only as a GPIO pin.

The following sequence unlocks the DBG pin:

- 1. Hold PA2/RESETLow.

- 2. Wait 5ms for the internal reset sequence to complete.

- 3. Send the following bytes serially to the debug pin:

```

DBG \leftarrow 80H (autobaud)

DBG \leftarrow EBH

DBG \leftarrow 5AH

DBG \leftarrow 70H

DBG \leftarrow CDH (32-bit unlock key)

```

- 4. Release PA2/RESEThe PA0/DBG pin is now identical function to that of the DBG pin on the 20-/28-pin device. Toten DEBUG mode, re-autobaud and write 80H to the OCD control register (see-Chip Debugger Commands page 179).

- Caution: BetweerStep 3andStep 4 there is an interval during with the 8-pin device is neither in RESET nor DEBUG mode. If a devices were erased or has not yet been programmed, all program memory bytes contain. The CPU interprets this as an illegal instruction, so somieregular behavior can occubefore entering DEBUG mode, and the register values after entering BUEG mode differs from their specified reset values. However, none of these irreguties prevent programming the Flash memory. Before beginning system debug, iteisommended that some legal code be programmed into the 8-pin device, and that a RESET occurs.

## Breakpoints

Execution Breakpoints are generated using the BRK instruction (opcodeWhen the eZ8 CPU decodes a BRK instruction, it signtale On-Chip Debugger. If Breakpoints are enabled, the OCD enters DEBUG mode antesidhe eZ8 CPU. If Breakpoints are not enabled, the OCD ignores the BRK signal and attace instruction operates as an NOP instruction.

Read Register (09H)—The Read Register command reads data from the Register File. Data can be read 1–256 bytes at æ (256 bytes can be read by setting size to 0). If the device is not in DEBUG mode othic Flash Read Protect Option bit is enabled, this command returns H for all the data values.

```

DBG \leftarrow 09H

DBG \leftarrow {4'h0,Register Address[11:8]

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-256 data bytes

```

• Write Program Memory (0AH)—The Write Program Memory command writes data to Program Memory. This is equivalent the LDC and LDCI instructions. Data can be written 1–65536 bytes take (65536 bytes can be written by setting size to 0). The on-chip Flash Controlleust be written to and unlocked for the programming operation to occur. If the Flassontroller is not unlocked, the data is discarded. If the device is not in DEBUG decor if the Flash Read Protect Option bit is enabled, the data is discarded.

```

DBG \leftarrow 0AH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```