# E·XFL

#### Zilog - Z8F012AHJ020EC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | IrDA, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT  |

| Number of I/O              | 23                                                            |

| Program Memory Size        | 1KB (1K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | 16 x 8                                                        |

| RAM Size                   | 256 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | A/D 8x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                                |

| Supplier Device Package    |                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f012ahj020ec00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

zilog |

## **Revision History**

Each instance in Revision History reflects a change to this document from its previous revision. For more details, refer to the corresponding pages and appropriate links in the table below.

|                   | Revision |                                                                                                                                                                                           |                          |

|-------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Date              | Level    | Description                                                                                                                                                                               | Page Number              |

| September<br>2008 | 25       | Added the references to F042A series back<br>in Table 1, Available Packages, Table 5,<br>Table 7, Table 13, Ordering Information<br>sections.                                             | 3, 9, 16, 19, 37,<br>251 |

| May 2008          | 24       | Changed title to Z8 Encore! XP F082A<br>Series and removed references to F042A<br>series in Table 1, Available Packages,<br>Table 5, Table 7, Table 13, Ordering<br>Information sections. | All                      |

| December<br>2007  | 23       | Updated Figure 3, Table 14, Table 58 through Table 60.                                                                                                                                    | 10, 41, and 95           |

| July 2007         | 22       | Updated Table 15 and Table 128. Updated<br>Power consumption in Electrical<br>Characteristics chapter.                                                                                    | 44, 221                  |

| June 2007         | 21       | Revision number update.                                                                                                                                                                   | All                      |

| Watchdog Timer Time-Out Response       92         Watchdog Timer Reload Unlock Sequence       93         Watchdog Timer Calibration       93         Watchdog Timer Calibration       93                                                                                       | 3<br>3                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Watchdog Timer Control Register Definitions       94         Watchdog Timer Control Register       94         Watchdog Timer Reload Upper, High and Low Byte Registers       94                                                                                                | 4                               |

| Universal Asynchronous Receiver/Transmitter                                                                                                                                                                                                                                    | 7                               |

| Architecture       97         Operation       98         Data Format       98         Transmitting Data using the Polled Method       98                                                                                                                                       | 8<br>8                          |

| Transmitting Data using the Interrupt-Driven Method       100         Receiving Data using the Polled Method       100                                                                                                                                                         | 0<br>1                          |

| Receiving Data using the Interrupt-Driven Method       102         Clear To Send (CTS) Operation       103         MULTIPROCESSOR (9-bit) Mode       103         External Driver Enable       104         UART Interrupts       104         UART Baud Rate Generator       105 | 3<br>3<br>4<br>5                |

| UART Control Register Definitions108UART Control 0 and Control 1 Registers108UART Status 0 Register112UART Status 1 Register112UART Transmit Data Register113UART Receive Data Register113UART Address Compare Register114UART Baud Rate High and Low Byte Registers114        | 8<br>8<br>1<br>2<br>3<br>3<br>4 |

| Infrared Encoder/Decoder 112                                                                                                                                                                                                                                                   | 7                               |

| Architecture       117         Operation       117         Transmitting IrDA Data       118         Receiving IrDA Data       119         Infrared Encoder Control Decistor Definitions       120                                                                              | 7<br>8<br>9                     |

| Infrared Encoder/Decoder Control Register Definitions                                                                                                                                                                                                                          |                                 |

| Analog-to-Digital Converter                                                                                                                                                                                                                                                    |                                 |

| Architecture         12           Operation         122           Data Format         122                                                                                                                                                                                      | 2                               |

vii

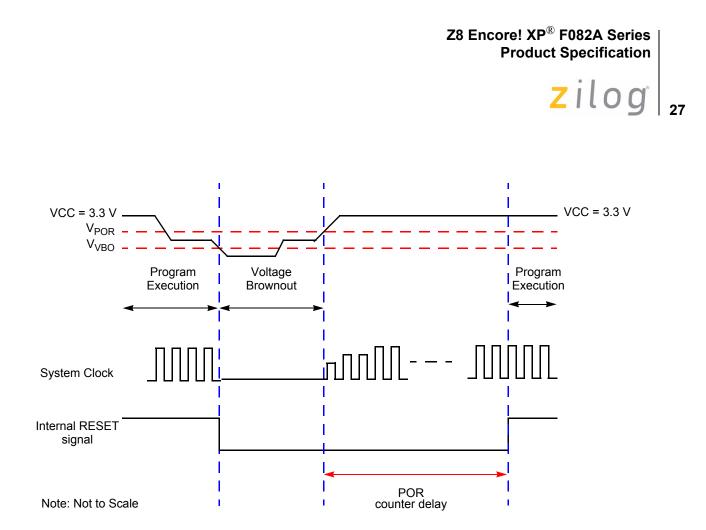

Figure 6. Voltage Brownout Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a Power-On Reset after recovering from a VBO condition.

## Watchdog Timer Reset

If the device is in NORMAL or HALT mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash Option Bit is programmed to 1. This is the unprogrammed state of the WDT\_RES Flash Option Bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT bit in the Reset Status (RSTSTAT) register is set to signify that the reset was initiated by the Watchdog Timer.

### **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system clock and reset signals, the required reset duration may be as short as three clock periods

# zilog <sub>37</sub>

## **General-Purpose Input/Output**

The Z8 Encore! XP<sup>®</sup> F082A Series products support a maximum of 25 port pins (Ports A– D) for general-purpose input/output (GPIO) operations. Each port contains control and data registers. The GPIO control registers determine data direction, open-drain, output drive current, programmable pull-ups, Stop Mode Recovery functionality, and alternate pin functions. Each port pin is individually programmable. In addition, the Port C pins are capable of direct LED drive at programmable drive strengths.

## **GPIO Port Availability By Device**

Table 13 lists the port pins available with each device and package type.

| Devices                         | Package | ADC | Port A | Port B | Port C | Port D | Total I/O |

|---------------------------------|---------|-----|--------|--------|--------|--------|-----------|

| Z8F082ASB, Z8F082APB, Z8F082AQB | 8-pin   | Yes | [5:0]  | No     | No     | No     | 6         |

| Z8F042ASB, Z8F042APB, Z8F042AQB |         |     |        |        |        |        |           |

| Z8F022ASB, Z8F022APB, Z8F022AQB |         |     |        |        |        |        |           |

| Z8F012ASB, Z8F012APB, Z8F012AQB |         |     |        |        |        |        |           |

| Z8F081ASB, Z8F081APB, Z8F081AQB | 8-pin   | No  | [5:0]  | No     | No     | No     | 6         |

| Z8F041ASB, Z8F041APB, Z8F041AQB |         |     |        |        |        |        |           |

| Z8F021ASB, Z8F021APB, Z8F021AQB |         |     |        |        |        |        |           |

| Z8F011ASB, Z8F011APB, Z8F011AQB |         |     |        |        |        |        |           |

| Z8F082APH, Z8F082AHH, Z8F082ASH | 20-pin  | Yes | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F042APH, Z8F042AHH, Z8F042ASH |         |     |        |        |        |        |           |

| Z8F022APH, Z8F022AHH, Z8F022ASH |         |     |        |        |        |        |           |

| Z8F012APH, Z8F012AHH, Z8F012ASH |         |     |        |        |        |        |           |

| Z8F081APH, Z8F081AHH, Z8F081ASH | 20-pin  | No  | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F041APH, Z8F041AHH, Z8F041ASH | •       |     |        |        |        |        |           |

| Z8F021APH, Z8F021AHH, Z8F021ASH |         |     |        |        |        |        |           |

| Z8F011APH, Z8F011AHH, Z8F011ASH |         |     |        |        |        |        |           |

| Z8F082APJ, Z8F082ASJ, Z8F082AHJ | 28-pin  | Yes | [7:0]  | [5:0]  | [7:0]  | [0]    | 23        |

| Z8F042APJ, Z8F042ASJ, Z8F042AHJ | •       |     |        |        |        |        |           |

| Z8F022APJ, Z8F022ASJ, Z8F022AHJ |         |     |        |        |        |        |           |

| Z8F012APJ, Z8F012ASJ, Z8F012AHJ |         |     |        |        |        |        |           |

| Z8F081APJ, Z8F081ASJ, Z8F081AHJ | 28-pin  | No  | [7:0]  | [7:0]  | [7:0]  | [0]    | 25        |

| Z8F041APJ, Z8F041ASJ, Z8F041AHJ | •       |     |        |        |        |        |           |

| Z8F021APJ, Z8F021ASJ, Z8F021AHJ |         |     |        |        |        |        |           |

| Z8F011APJ, Z8F011ASJ, Z8F011AHJ |         |     |        |        |        |        |           |

#### Table 13. Port Availability by Device and Package Type

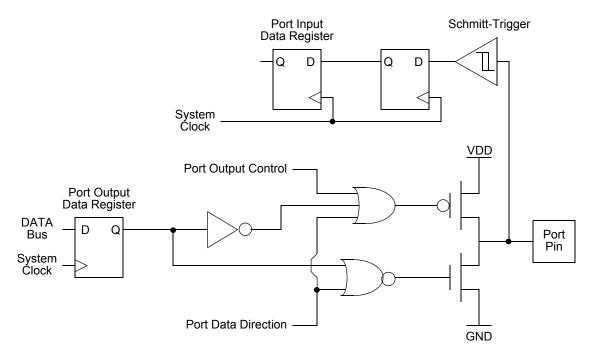

## Architecture

Figure 7 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

#### Figure 7. GPIO Port Pin Block Diagram

## **GPIO Alternate Functions**

Many of the GPIO port pins can be used for general-purpose I/O and access to on-chip peripheral functions such as the timers and serial communication devices. The Port A–D Alternate Function sub-registers configure these pins for either General-Purpose I/O or alternate function operation. When a pin is configured for alternate function, control of the port pin direction (input/output) is passed from the Port A–D Data Direction registers to the alternate function assigned to this pin. Table 14 on page 41 lists the alternate functions possible with each port pin. For those pins with more one alternate function, the alternate function is defined through Alternate Function Sets sub-registers AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, those pins function as input and output for the crystal oscillator.

PIN[7:0]—Port Input Data

Sampled data from the corresponding port pin input.

0 = Input data is logical 0 (Low).

1 = Input data is logical 1 (High).

## Port A–D Output Data Register

The Port A–D Output Data register (Table 28) controls the output data to the pins.

| BITS  | 7     | 6                      | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|------------------------|-------|-------|-------|-------|-------|-------|

| FIELD | POUT7 | POUT6                  | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |

| RESET | 0     | 0                      | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W   | R/W   | R/W                    | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| ADDR  |       | FD3H, FD7H, FDBH, FDFH |       |       |       |       |       |       |

#### Table 28. Port A–D Output Data Register (PxOUT)

POUT[7:0]—Port Output Data

These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 = Drive a logical 0 (Low).

1= Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control register bit to 1.

## LED Drive Enable Register

The LED Drive Enable register (Table 29) activates the controlled current drive. The Port C pin must first be enabled by setting the Alternate Function register to select the LED function.

| BITS  | 7          | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------------|------|-----|-----|-----|-----|-----|-----|

| FIELD | LEDEN[7:0] |      |     |     |     |     |     |     |

| RESET | 0          | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W        | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  |            | F82H |     |     |     |     |     |     |

#### Table 29. LED Drive Enable (LEDEN)

zilog<sup>°</sup>

duration of the negative phase of the PWM signal (as defined by the difference between the PWM registers and the Timer Reload registers).

- 5. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM period). The Reload value must be greater than the PWM value.

- 6. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 7. Configure the associated GPIO port pin for the Timer Output and Timer Output Complement alternate functions. The Timer Output Complement function is shared with the Timer Input function for both timers. Setting the timer mode to Dual PWM automatically switches the function from Timer In to Timer Out Complement.

- 8. Write to the Timer Control register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

PWM Period (s) = Reload Value xPrescale System Clock Frequency (Hz)

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT mode equation determines the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{PWM Value}}{\text{Reload Value}} \times 100$

#### **CAPTURE Mode**

In CAPTURE mode, the current timer count value is recorded when the appropriate external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte Registers. The timer input is the system clock. The TPOL bit in the Timer Control register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in TxCTL0 register is set to indicate the timer interrupt is because of an input capture event.

The timer continues counting up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt and continues counting. The INPCAP bit in TxCTL0 register clears indicating the timer interrupt is not because of an input capture event.

110 = 64 cycles delay 111 = 128 cycles delay

INPCAP—Input Capture Event

This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.

0 = Previous timer interrupt is not a result of Timer Input Capture Event

1 = Previous timer interrupt is a result of Timer Input Capture Event

#### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode (Table 49).

Table 49. Timer 0–1 Control Register 1 (TxCTL1)

| BITS  | 7   | 6          | 5    | 4   | 3   | 2     | 1   | 0   |

|-------|-----|------------|------|-----|-----|-------|-----|-----|

| FIELD | TEN | TPOL       | PRES |     |     | TMODE |     |     |

| RESET | 0   | 0          | 0    | 0   | 0   | 0     | 0   | 0   |

| R/W   | R/W | R/W        | R/W  | R/W | R/W | R/W   | R/W | R/W |

| ADDR  |     | F07H, F0FH |      |     |     |       |     |     |

TEN-Timer Enable

0 = Timer is disabled.

1 = Timer enabled to count.

TPOL—Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer.

#### **ONE-SHOT mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **CONTINUOUS mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### COUNTER mode

If the timer is enabled the Timer Output signal is complemented after timer reload.

0 = Count occurs on the rising edge of the Timer Input signal.

1 = Count occurs on the falling edge of the Timer Input signal.

#### 85

#### **PWM SINGLE OUTPUT mode**

0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload.

1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload.

#### **CAPTURE mode**

0 = Count is captured on the rising edge of the Timer Input signal.

1 = Count is captured on the falling edge of the Timer Input signal.

#### **COMPARE mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **GATED** mode

0 = Timer counts when the Timer Input signal is High (1) and interrupts are generated on the falling edge of the Timer Input.

1 = Timer counts when the Timer Input signal is Low (0) and interrupts are generated on the rising edge of the Timer Input.

#### **CAPTURE/COMPARE mode**

0 = Counting is started on the first rising edge of the Timer Input signal. The current count is captured on subsequent rising edges of the Timer Input signal.

1 = Counting is started on the first falling edge of the Timer Input signal. The current count is captured on subsequent falling edges of the Timer Input signal.

#### **PWM DUAL OUTPUT mode**

0 = Timer Output is forced Low (0) and Timer Output Complement is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload. When enabled, the Timer Output Complement is forced Low (0) upon PWM count match and forced High (1) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to High (1).

1 = Timer Output is forced High (1) and Timer Output Complement is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced Low (0) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to Low (0).

## Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which may place the Z8 Encore! XP<sup>®</sup> F082A Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator.

- A selectable time-out response: reset or interrupt.

- 24-bit programmable time-out value.

## Operation

The Watchdog Timer is a one-shot timer that resets or interrupts the Z8 Encore! XP F082A Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash Option Bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10 kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 56 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

#### Table 56. Watchdog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value – | Approximate Time-Out Delay<br>(with 10 kHz typical WDT oscillator frequency) |                        |  |  |  |

|------------------|--------------------|------------------------------------------------------------------------------|------------------------|--|--|--|

| (Hex)            | (Decimal)          | Typical                                                                      | Description            |  |  |  |

| 000004           | 4                  | 400 μs                                                                       | Minimum time-out delay |  |  |  |

| FFFFF            | 16,777,215         | 28 minutes                                                                   | Maximum time-out delay |  |  |  |

zilog<sup>°</sup>

- 3. Clears the UART Receiver interrupt in the applicable Interrupt Request register.

- 4. Executes the IRET instruction to return from the interrupt-service routine and await more data.

## Clear To Send (CTS) Operation

The CTS pin, if enabled by the CTSE bit of the UART Control 0 register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this action is typically performed during Stop Bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

#### MULTIPROCESSOR (9-bit) Mode

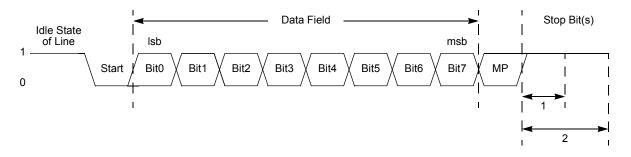

The UART has a MULTIPROCESSOR (9-bit) mode that uses an extra (9th) bit for selective communication when a number of processors share a common UART bus. In MULTI-PROCESSOR mode (also referred to as 9-bit mode), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 13. The character format is:

#### Figure 13. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) mode, the Parity bit location (9th bit) becomes the Multiprocessor control bit. The UART Control 1 and Status 1 registers provide MULTI-PROCESSOR (9-bit) mode control and status information. If an automatic address matching scheme is enabled, the UART Address Compare register holds the network address of the device.

#### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When MULTIPROCESSOR mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made in hardware, software or some combination of the two, depending on the multiprocessor

## 116

|                          | z System Clo             | -                    |              |

|--------------------------|--------------------------|----------------------|--------------|

| Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) |

| 1250.0                   | N/A                      | N/A                  | N/A          |

| 625.0                    | N/A                      | N/A                  | N/A          |

| 250.0                    | 1                        | 223.72               | -10.51       |

| 115.2                    | 2                        | 111.9                | -2.90        |

| 57.6                     | 4                        | 55.9                 | -2.90        |

| 38.4                     | 6                        | 37.3                 | -2.90        |

| 19.2                     | 12                       | 18.6                 | -2.90        |

| 9.60                     | 23                       | 9.73                 | 1.32         |

| 4.80                     | 47                       | 4.76                 | -0.83        |

| 2.40                     | 93                       | 2.41                 | 0.23         |

| 1.20                     | 186                      | 1.20                 | 0.23         |

| 0.60                     | 373                      | 0.60                 | -0.04        |

| 0.30                     | 746                      | 0.30                 | -0.04        |

### Table 70. UART Baud Rates (Continued)

| 1.8432 MHz \$            | System Clock             |                      |              |

|--------------------------|--------------------------|----------------------|--------------|

| Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) |

| 1250.0                   | N/A                      | N/A                  | N/A          |

| 625.0                    | N/A                      | N/A                  | N/A          |

| 250.0                    | N/A                      | N/A                  | N/A          |

| 115.2                    | 1                        | 115.2                | 0.00         |

| 57.6                     | 2                        | 57.6                 | 0.00         |

| 38.4                     | 3                        | 38.4                 | 0.00         |

| 19.2                     | 6                        | 19.2                 | 0.00         |

| 9.60                     | 12                       | 9.60                 | 0.00         |

| 4.80                     | 24                       | 4.80                 | 0.00         |

| 2.40                     | 48                       | 2.40                 | 0.00         |

| 1.20                     | 96                       | 1.20                 | 0.00         |

| 0.60                     | 192                      | 0.60                 | 0.00         |

| 0.30                     | 384                      | 0.30                 | 0.00         |

|                          |                          |                      |              |

## **ADC Control/Status Register 1**

The ADC Control/Status Register 1 (ADCCTL1) configures the input buffer stage, enables the threshold interrupts and contains the status of both threshold triggers. It is also used to select the voltage reference configuration.

#### Table 72. ADC Control/Status Register 1 (ADCCTL1)

| BITS  | 7       | 6    | 5    | 4     | 3   | 2         | 1   | 0   |

|-------|---------|------|------|-------|-----|-----------|-----|-----|

| FIELD | REFSELH |      | Rese | erved | В   | UFMODE[2: | 0]  |     |

| RESET | 1       | 0    | 0    | 0     | 0   | 0         | 0   | 0   |

| R/W   | R/W     | R/W  | R/W  | R/W   | R/W | R/W       | R/W | R/W |

| ADDR  |         | F71H |      |       |     |           |     |     |

REFSELH—Voltage Reference Level Select High Bit; in conjunction with the Low bit (REFSELL) in ADC Control Register 0, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL}; this reference is independent of the Comparator reference.

00= Internal Reference Disabled, reference comes from external pin

01= Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

11= Reserved

BUFMODE[2:0] - Input Buffer Mode Select

000 =Single-ended, unbuffered input

- 001 = Single-ended, buffered input with unity gain

- 010 = Reserved

- 011 = Reserved

- 100 = Differential, unbuffered input

- 101 = Differential, buffered input with unity gain

- 110 = Reserved

- 111 = Reserved

## ADC Data High Byte Register

The ADC Data High Byte (ADCD\_H) register contains the upper eight bits of the ADC output. The output is an 13-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

High. Because of the open-drain nature of the DBG pin, the host can send a Serial Break to the OCD even if the OCD is transmitting a character.

### OCD Unlock Sequence (8-Pin Devices Only)

Because of pin-sharing on the 8-pin device, an unlock sequence must be performed to access the DBG pin. If this sequence is not completed during a system reset, then the PA0/DBG pin functions only as a GPIO pin.

The following sequence unlocks the DBG pin:

- 1. Hold PA2/RESET Low.

- 2. Wait 5ms for the internal reset sequence to complete.

- 3. Send the following bytes serially to the debug pin:

```

DBG \leftarrow 80H (autobaud)

DBG \leftarrow EBH

DBG \leftarrow 5AH

DBG \leftarrow 70H

DBG \leftarrow CDH (32-bit unlock key)

```

4. Release PA2/RESET. The PA0/DBG pin is now identical in function to that of the DBG pin on the 20-/28-pin device. To enter DEBUG mode, re-autobaud and write 80H to the OCD control register (see On-Chip Debugger Commands on page 179).

**Caution:** Between Step 3 and Step 4, there is an interval during which the 8-pin device is neither in RESET nor DEBUG mode. If a device has been erased or has not yet been programmed, all program memory bytes contain FFH. The CPU interprets this as an illegal instruction, so some irregular behavior can occur before entering DEBUG mode, and the register values after entering DEBUG mode differs from their specified reset values. However, none of these irregularities prevent programming the Flash memory. Before beginning system debug, it is recommended that some legal code be programmed into the 8-pin device, and that a RESET occurs.

#### **Breakpoints**

Execution Breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the On-Chip Debugger. If Breakpoints are enabled, the OCD enters DEBUG mode and idles the eZ8 CPU. If Breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

186

zilog

196

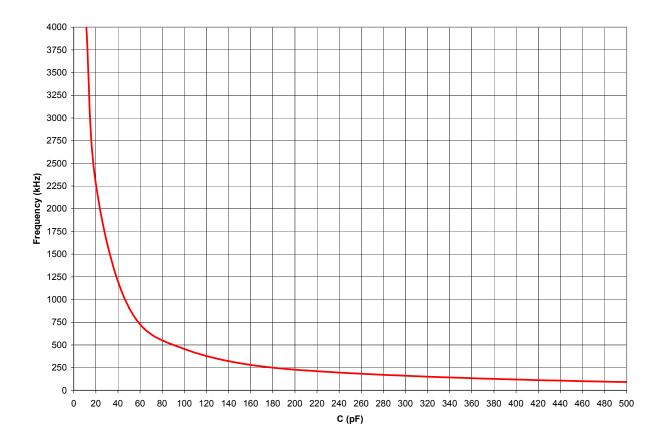

Figure 29 displays the typical (3.3 V and 25 °C) oscillator frequency as a function of the capacitor (C in pF) employed in the RC network assuming a 45 K $\Omega$  external resistor. For very small values of C, the parasitic capacitance of the oscillator XIN pin and the printed circuit board must be included in the estimation of the oscillator frequency.

It is possible to operate the RC oscillator using only the parasitic capacitance of the package and printed circuit board. To minimize sensitivity to external parasitics, external capacitance values in excess of 20 pF are recommended.

## Figure 29. Typical RC Oscillator Frequency as a Function of the External Capacitance with a 45 k $\Omega$ Resistor

**Caution**:

When using the external RC oscillator mode, the oscillator can stop oscillating if the power supply drops below 2.7 V, but before the power supply drops to the Voltage Brownout threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7 V.

#### 200

## Assembly Language Syntax

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed if manual program coding is preferred or if you intend to implement your own assembler.

**Example 1**: If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Table 112. Assembly Language Syntax Example 1

| Assembly Language<br>Code | ADD | 43H, | 08H | (ADD dst, src) |

|---------------------------|-----|------|-----|----------------|

| Object Code               | 04  | 08   | 43  | (OPC src, dst) |

**Example 2**: In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Table 113. Assembly Language Syntax Example 2

| Assembly Language<br>Code | ADD | 43H, | R8 | (ADD dst, src) |

|---------------------------|-----|------|----|----------------|

| Object Code               | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

## eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is described in Table 114.

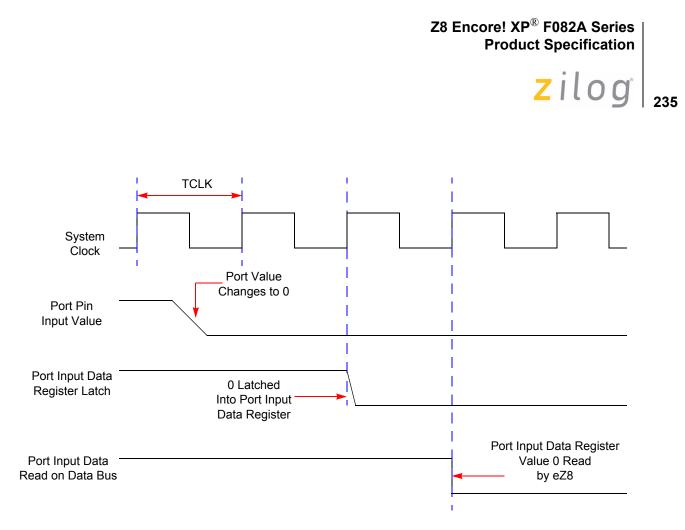

Figure 34. Port Input Sample Timing

|                     |                                                                                                          | Delay (ns) |         |

|---------------------|----------------------------------------------------------------------------------------------------------|------------|---------|

| Parameter           | Abbreviation                                                                                             | Minimum    | Maximum |

| T <sub>S_PORT</sub> | Port Input Transition to XIN Rise Setup Time (Not pictured)                                              | 5          | _       |

| T <sub>H_PORT</sub> | XIN Rise to Port Input Transition Hold Time (Not pictured)                                               | 0          | -       |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to ensure Stop Mode<br>Recovery<br>(for GPIO Port Pins enabled as SMR sources) | 1 µs       |         |

Zilog 239

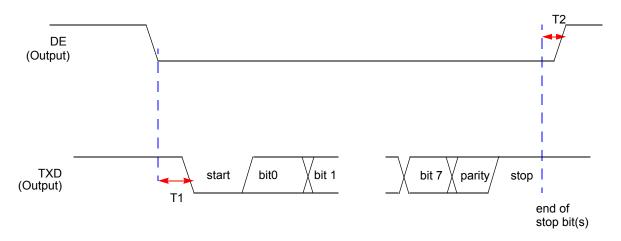

Figure 38 and Table 143 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the transmit data register has been written. DE remains asserted for multiple characters as long as the transmit data register is written with the next character before the current character has completed.

Figure 38. UART Timing Without CTS

| Table | 143. | UART | Timing | Without CTS |

|-------|------|------|--------|-------------|

|-------|------|------|--------|-------------|

|                |                                                                        | Delay (ns)        |            |  |

|----------------|------------------------------------------------------------------------|-------------------|------------|--|

| Parameter      | Abbreviation                                                           | Minimum           | Maximum    |  |

| UART           |                                                                        |                   |            |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * XIN<br>period | 1 bit time |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx data register is empty) | ± 5               |            |  |

250