# E·XFL

#### Zilog - Z8F012ASH020EC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | IrDA, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT  |

| Number of I/O              | 17                                                            |

| Program Memory Size        | 1KB (1K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | 16 x 8                                                        |

| RAM Size                   | 256 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | A/D 7x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f012ash020ec00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| Overview                                            |

|-----------------------------------------------------|

| Features                                            |

| Part Selection Guide                                |

| Block Diagram                                       |

| CPU and Peripheral Overview                         |

| eZ8 CPU Features 5                                  |

| 10-Bit Analog-to-Digital Converter 5                |

| Low-Power Operational Amplifier                     |

| Internal Precision Oscillator                       |

| Temperature Sensor    6      Analog Comparator    6 |

| External Crystal Oscillator                         |

| Low Voltage Detector                                |

| On-Chip Debugger                                    |

| Universal Asynchronous Receiver/Transmitter         |

| Timers                                              |

| General-Purpose Input/Output                        |

| Direct LED Drive                                    |

| Non-Volatile Data Storage                           |

| Interrupt Controller                                |

| Reset Controller                                    |

| Pin Description                                     |

| Available Packages                                  |

| Pin Configurations                                  |

| Signal Descriptions                                 |

| Pin Characteristics                                 |

| Address Space                                       |

|                                                     |

| Register File                                       |

| Program Memory                                      |

| Data Memory                                         |

| Flash Information Area 17                           |

| Register Map                                        |

zilog | 3

initiate Stop Mode Recovery without being written to the Port Input Data register or without initiating an interrupt (if enabled for that pin).

# Stop Mode Recovery Using the External RESET Pin

When the Z8 Encore! XP F082A Series device is in STOP mode and the external <u>RESET</u> pin is driven Low, a system reset occurs. Because of a glitch filter operating on the <u>RESET</u> pin, the Low pulse must be greater than the minimum width specified, or it is ignored. See Electrical Characteristics on page 221 for details.

# Low Voltage Detection

In addition to the Voltage Brownout (VBO) Reset described above, it is also possible to generate an interrupt when the supply voltage drops below a user-selected value. For details about configuring the Low Voltage Detection (LVD) and the threshold levels available, see Trim Bit Address 0003H on page 159. The LVD function is available on the 8-pin product versions only.

When the supply voltage drops below the LVD threshold, the LVD bit of the Reset Status (RSTSTAT) register is set to one. This bit remains one until the low-voltage condition goes away. Reading or writing this bit does not clear it. The LVD circuit can also generate an interrupt when so enabled, see Interrupt Vectors and Priority on page 58. The LVD bit is NOT latched, so enabling the interrupt is the only way to guarantee detection of a transient low voltage event.

The LVD functionality depends on circuitry shared with the VBO block; therefore, disabling the VBO also disables the LVD.

# **Reset Register Definitions**

The following sections define the Reset registers.

### **Reset Status Register**

The Reset Status (RSTSTAT) register is a read-only register that indicates the source of the most recent Reset event, indicates a Stop Mode Recovery event, and indicates a Watchdog Timer time-out. Reading this register resets the upper four bits to 0.

This register shares its address with the Watchdog Timer control register, which is write-only (see Table 11 on page 31).

<mark>z</mark>ilog<sup>°</sup>

| Port   | Pin | Mnemonic                | Alternate Function Description        | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------------------|---------------------------------------|-----------------------------------------|

| Port C | PC0 | Reserved                |                                       | AFS1[0]: 0                              |

|        |     | ANA4/CINP/LED<br>Drive  | ADC or Comparator Input, or LED drive | AFS1[0]: 1                              |

|        | PC1 | Reserved                |                                       | AFS1[1]: 0                              |

|        |     | ANA5/CINN/ LED<br>Drive | ADC or Comparator Input, or LED drive | AFS1[1]: 1                              |

#### Table 14. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

|     | Drive              | ADC or Comparator Input, or LED drive                  | AFSI[I]: I |

|-----|--------------------|--------------------------------------------------------|------------|

| PC2 | Reserved           | AFS1[2]: 0                                             |            |

|     | ANA6/LED/<br>VREF* | ADC Analog Input or LED Drive or ADC Voltage Reference | AFS1[2]: 1 |

| PC3 | COUT               | Comparator Output                                      | AFS1[3]: 0 |

|     | LED                | LED drive                                              | AFS1[3]: 1 |

| PC4 | Reserved           |                                                        | AFS1[4]: 0 |

|     | LED                | LED Drive                                              | AFS1[4]: 1 |

| PC5 | Reserved           |                                                        | AFS1[5]: 0 |

|     | LED                | LED Drive                                              | AFS1[5]: 1 |

| PC6 | Reserved           |                                                        | AFS1[6]: 0 |

|     | LED                | LED Drive                                              | AFS1[6]: 1 |

| PC7 | Reserved           |                                                        | AFS1[7]: 0 |

|     | LED                | LED Drive                                              | AFS1[7]: 1 |

|     |                    |                                                        |            |

Note: Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set register AFS2 is not used to select the function. Also, alternate function selection as described in Port A–D Alternate Function Sub-Registers on page 47 must also be enabled. \*VREF is available on PC2 in 20-pin parts only.

PS022825-0908

43

# **Timer Control Register Definitions**

# Timer 0–1 Control Registers

## Time 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1) determine the timer operating mode (Table 48). It also includes a programmable PWM deadband delay, two bits to configure timer interrupt definition, and a status bit to identify if the most recent timer interrupt is caused by an input capture event.

Table 48. Timer 0–1 Control Register 0 (TxCTL0)

| BITS  | 7       | 6    | 5    | 4        | 3    | 2    | 1   | 0      |

|-------|---------|------|------|----------|------|------|-----|--------|

| FIELD | TMODEHI | TICO | NFIG | Reserved |      | PWMD |     | INPCAP |

| RESET | 0       | 0    | 0    | 0        | 0    | 0    | 0   | 0      |

| R/W   | R/W     | R/W  | R/W  | R/W      | R/W  | R/W  | R/W | R      |

| ADDR  |         |      |      | F06H,    | F0EH |      |     |        |

TMODEHI—Timer Mode High Bit

This bit along with the TMODE field in TxCTL1 register determines the operating mode of the timer. This is the most significant bit of the Timer mode selection value. See the TxCTL1 register description for details of the full timer mode decoding.

TICONFIG—Timer Interrupt Configuration

This field configures timer interrupt definition.

- 0x = Timer Interrupt occurs on all defined Reload, Compare and Input Events

- 10 = Timer Interrupt only on defined Input Capture/Deassertion Events

- 11 = Timer Interrupt only on defined Reload/Compare Events

Reserved—Must be 0.

PWMD—PWM Delay value

This field is a programmable delay to control the number of system clock cycles delay before the Timer Output and the Timer Output Complement are forced to their active state.

- 000 = No delay

- 001 = 2 cycles delay

- 010 = 4 cycles delay

- 011 = 8 cycles delay

- 100 = 16 cycles delay

- 101 = 32 cycles delay

# Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which may place the Z8 Encore! XP<sup>®</sup> F082A Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator.

- A selectable time-out response: reset or interrupt.

- 24-bit programmable time-out value.

# Operation

The Watchdog Timer is a one-shot timer that resets or interrupts the Z8 Encore! XP F082A Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash Option Bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10 kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 56 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

#### Table 56. Watchdog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value – | Approximate Time-Out Delay<br>(with 10 kHz typical WDT oscillator frequency |                        |  |  |

|------------------|--------------------|-----------------------------------------------------------------------------|------------------------|--|--|

| (Hex)            | (Decimal)          | Typical                                                                     | Description            |  |  |

| 000004           | 4                  | 400 μs                                                                      | Minimum time-out delay |  |  |

| FFFFF            | 16,777,215         | 28 minutes                                                                  | Maximum time-out delay |  |  |

**Caution:** *The 24-bit WDT Reload Value must not be set to a value less than* 000004H.

### Table 58. Watchdog Timer Reload Upper Byte Register (WDTU)

| BITS       | 7             | 6          | 5             | 4             | 3             | 2            | 1   | 0 |  |  |

|------------|---------------|------------|---------------|---------------|---------------|--------------|-----|---|--|--|

| FIELD      |               | WDTU       |               |               |               |              |     |   |  |  |

| RESET      |               | 00H        |               |               |               |              |     |   |  |  |

| R/W        |               | R/W*       |               |               |               |              |     |   |  |  |

| ADDR       |               | FF1H       |               |               |               |              |     |   |  |  |

| R/W* - Rea | d returns the | current WD | C count value | Write sets th | ne appropriat | e Reload Val | ue. |   |  |  |

R/W\* - Read returns the current WDT count value. Write sets the appropriate Reload Value.

WDTU—WDT Reload Upper Byte

Most-significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value.

#### Table 59. Watchdog Timer Reload High Byte Register (WDTH)

| BITS       | 7              | 6           | 5            | 4              | 3           | 2            | 1 | 0 |  |  |

|------------|----------------|-------------|--------------|----------------|-------------|--------------|---|---|--|--|

| FIELD      |                | WDTH        |              |                |             |              |   |   |  |  |

| RESET      |                | 04H         |              |                |             |              |   |   |  |  |

| R/W        |                | R/W*        |              |                |             |              |   |   |  |  |

| ADDR       |                | FF2H        |              |                |             |              |   |   |  |  |

| R/W* - Rea | ad returns the | current WDT | count value. | Write sets the | appropriate | Reload Value |   |   |  |  |

WDTH—WDT Reload High Byte

Middle byte, Bits[15:8], of the 24-bit WDT reload value.

#### Table 60. Watchdog Timer Reload Low Byte Register (WDTL)

| BITS       | 7             | 6           | 5            | 4             | 3             | 2           | 1  | 0 |  |  |

|------------|---------------|-------------|--------------|---------------|---------------|-------------|----|---|--|--|

| FIELD      |               | WDTL        |              |               |               |             |    |   |  |  |

| RESET      |               | 00H         |              |               |               |             |    |   |  |  |

| R/W        |               | R/W*        |              |               |               |             |    |   |  |  |

| ADDR       |               | FF3H        |              |               |               |             |    |   |  |  |

| R/W* - Rea | d returns the | current WDT | count value. | Write sets th | e appropriate | Reload Valu | e. |   |  |  |

WDTL—WDT Reload Low

Least significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value.

Zilog

# **Receiving IrDA Data**

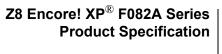

Data received from the infrared transceiver using the IR\_RXD signal through the RXD pin is decoded by the Infrared Endec and passed to the UART. The UART's baud rate clock is used by the Infrared Endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 18 displays data reception. When the Infrared Endec is enabled, the UART's RXD signal is internal to the Z8 Encore! XP<sup>®</sup> F082A Series products while the IR\_RXD signal is received through the RXD pin.

Figure 18. IrDA Data Reception

#### **Infrared Data Reception**

**Caution:** The system clock frequency must be at least 1.0 MHz to ensure proper reception of the  $1.4 \,\mu s$  minimum width pulses allowed by the IrDA standard.

#### **Endec Receiver Synchronization**

The IrDA receiver uses a local baud rate clock counter (0 to 15 clock periods) to generate an input stream for the UART and to create a sampling window for detection of incoming pulses. The generated UART input (UART RXD) is delayed by 8 baud rate clock periods with respect to the incoming IrDA data stream. When a falling edge in the input data stream is detected, the Endec counter is reset. When the count reaches a value of 8, the UART RXD value is updated to reflect the value of the decoded data. When the count reaches 12 baud clock periods, the sampling window for the next incoming pulse opens. The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the Endec a sampling window of minus four

zilog

baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal, allowing the Endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

# Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined in Universal Asynchronous Receiver/Transmitter on page 97.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO Port alternate function for the corresponding pin.

| İ | l | 0 | g | 133 |

|---|---|---|---|-----|

|   |   |   |   | 133 |

| BITS      | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----------|----------------|---|---|---|---|---|---|---|--|

| FIELD     | ADCDH          |   |   |   |   |   |   |   |  |

| RESET     | Х              | Х | Х | Х | Х | Х | Х | Х |  |

| R/W       | R              | R | R | R | R | R | R | R |  |

| ADDR      | F72H           |   |   |   |   |   |   |   |  |

| X = Undef | X = Undefined. |   |   |   |   |   |   |   |  |

#### Table 73. ADC Data High Byte Register (ADCD\_H)

ADCDH—ADC Data High Byte

This byte contains the upper eight bits of the ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the most recent conversion output is held in this register. These bits are undefined after a Reset.

# ADC Data Low Byte Register

The ADC Data Low Byte (ADCD\_L) register contains the lower bits of the ADC output as well as an overflow status bit. The output is a 13-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data Low Byte register is read-only. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

Table 74. ADC Data Low Byte Register (ADCD\_L)

| BITS      | 7              | 6 | 5     | 4    | 3     | 2   | 1 | 0 |

|-----------|----------------|---|-------|------|-------|-----|---|---|

| FIELD     |                |   | ADCDL | Rese | erved | OVF |   |   |

| RESET     | Х              | Х | Х     | Х    | Х     | Х   | Х | Х |

| R/W       | R              | R | R     | R    | R     | R   | R | R |

| ADDR      | F73H           |   |       |      |       |     |   |   |

| X = Undef | X = Undefined. |   |       |      |       |     |   |   |

ADCDL—ADC Data Low Bits

These bits are the least significant five bits of the 13-bits of the ADC output. These bits are undefined after a Reset.

Reserved—Must be undefined.

OVF—Overflow Status

0= A hardware overflow did not occur in the ADC for the current sample. 1= A hardware overflow did occur in the ADC for the current sample, therefore the current sample is invalid.

138

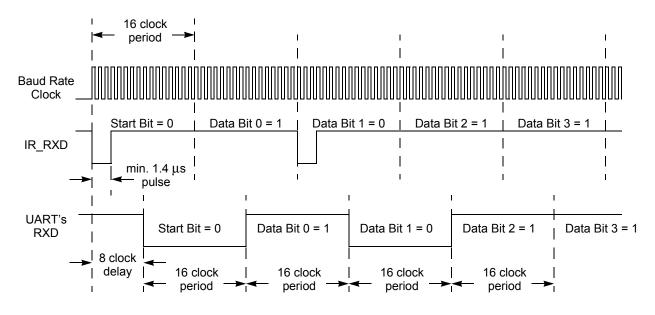

Figure 22. Flash Controller Operation Flow Chart

# **Trim Bit Data Register**

The Trim Bid Data (TRMDR) register contains the read or write data for access to the trim option bits (Table 85).

## Table 85. Trim Bit Data Register (TRMDR)

| BITS  | 7   | 6   | 5   | 4         | 3            | 2   | 1   | 0   |

|-------|-----|-----|-----|-----------|--------------|-----|-----|-----|

| FIELD |     |     |     | TRMDR - T | rim Bit Data |     |     |     |

| RESET | 0   | 0   | 0   | 0         | 0            | 0   | 0   | 0   |

| R/W   | R/W | R/W | R/W | R/W       | R/W          | R/W | R/W | R/W |

| ADDR  |     |     |     | FF        | 7H           |     | ·   |     |

# Flash Option Bit Address Space

The first two bytes of Flash program memory at addresses 0000H and 0001H are reserved for the user-programmable Flash option bits.

# Flash Program Memory Address 0000H

Table 86. Flash Option Bits at Program Memory Address 0000H

| BITS                                            | 7                    | 6      | 5            | 4   | 3      | 2   | 1        | 0   |

|-------------------------------------------------|----------------------|--------|--------------|-----|--------|-----|----------|-----|

| FIELD                                           | WDT_RES              | WDT_AO | OSC_SEL[1:0] |     | VBO_AO | FRP | Reserved | FWP |

| RESET                                           | U                    | U      | U            | U   | U      | U   | U        | U   |

| R/W                                             | R/W                  | R/W    | R/W          | R/W | R/W    | R/W | R/W      | R/W |

| ADDR                                            | Program Memory 0000H |        |              |     |        |     |          |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                      |        |              |     |        |     |          |     |

WDT\_RES—Watchdog Timer Reset

0 = Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.

1 = Watchdog Timer time-out causes a system reset. This setting is the default for unprogrammed (erased) Flash.

WDT\_AO—Watchdog Timer Always On

0 = Watchdog Timer is automatically enabled upon application of system power. Watchdog Timer can not be disabled.

zilog |

Write Memory, Read Memory, Write Register, Read Register, Read Memory CRC, Step Instruction, Stuff Instruction, and Execute Instruction commands.

DBG  $\leftarrow$  03H DBG  $\rightarrow$  RuntimeCounter[15:8] DBG  $\rightarrow$  RuntimeCounter[7:0]

• Write OCD Control Register (04H)—The Write OCD Control Register command writes the data that follows to the OCDCTL register. When the Flash Read Protect Option Bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0 and the only method of returning the device to normal operating mode is to reset the device.

DBG  $\leftarrow$  04H DBG  $\leftarrow$  OCDCTL[7:0]

• **Read OCD Control Register (05H)**—The Read OCD Control Register command reads the value of the OCDCTL register.

```

DBG \leftarrow 05H

DBG \rightarrow OCDCTL[7:0]

```

• Write Program Counter (06H)—The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter (PC). If the device is not in DE-BUG mode or if the Flash Read Protect Option bit is enabled, the Program Counter (PC) values are discarded.

```

DBG ← 06H

DBG ← ProgramCounter[15:8]

DBG ← ProgramCounter[7:0]

```

• **Read Program Counter (07H)**—The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

• Write Register (08H)—The Write Register command writes data to the Register File. Data can be written 1–256 bytes at a time (256 bytes can be written by setting size to 0). If the device is not in DEBUG mode, the address and data values are discarded. If the Flash Read Protect Option bit is enabled, only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

**z**ilog<sup>®</sup>

| Mode         | Crystal<br>Frequency Range | Function                            | Use  | sconduo<br>(mA/V)<br>this ran<br>alculatio | ge for |

|--------------|----------------------------|-------------------------------------|------|--------------------------------------------|--------|

| Low Gain*    | 32 kHz–1 MHz               | Low Power/Frequency Applications    | 0.02 | 0.04                                       | 0.09   |

| Medium Gain* | 0.5 MHz–10 MHz             | Medium Power/Frequency Applications | 0.84 | 1.7                                        | 3.1    |

| High Gain*   | 8 MHz–20 MHz               | High Power/Frequency Applications   | 1.1  | 2.3                                        | 4.2    |

#### Table 111. Transconductance Values for Low, Medium, and High Gain Operating Modes

**Note:** \*Printed circuit board layout must not add more than 4 pF of stray capacitance to either XIN or XOUT pins. if no Oscillation occurs, reduce the values of the capacitors C1 and C2 to decrease the loading.

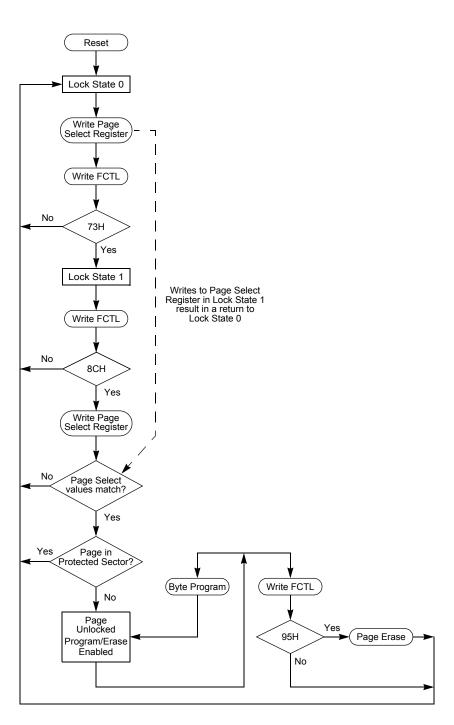

# **Oscillator Operation with an External RC Network**

Figure 28 displays a recommended configuration for connection with an external resistor-capacitor (RC) network.

#### Figure 28. Connecting the On-Chip Oscillator to an External RC Network

An external resistance value of 45 k $\Omega$  is recommended for oscillator operation with an external RC network. The minimum resistance value to ensure operation is 40 k $\Omega$ . The typical oscillator frequency can be estimated from the values of the resistor (*R* in k $\Omega$ ) and capacitor (*C* in pF) elements using the following equation:

Oscillator Frequency (kHz) =

$$\frac{1 \times 10^{6}}{(0.4 \times R \times C) + (4 \times C)}$$

195

# zilog

# **Internal Precision Oscillator**

The internal precision oscillator (IPO) is designed for use without external components. You can either manually trim the oscillator for a non-standard frequency or use the automatic factory-trimmed version to achieve a 5.53 MHz frequency. IPO features include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8 kHz (contains both a fast and a slow mode)

- Trimmed through Flash option bits with user override

- Elimination of crystals or ceramic resonators in applications where very high timing accuracy is not required

# Operation

An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed the oscillator frequency is stable and does not require subsequent calibration. Trimming is performed during manufacturing and is not necessary for you to repeat unless a frequency other than 5.53 MHz (fast mode) or 32.8 kHz (slow mode) is required. This trimming is done at +30 °C and a supply voltage of 3.3 V, so accuracy of this operating point is optimal.

If not used, the IPO can be disabled by the Oscillator Control register (see Oscillator Control Register Definitions on page 190).

By default, the oscillator frequency is set by the factory trim value stored in the write-protected Flash information page. However, the user code can override these trim values as described in Trim Bit Address Space on page 158.

Select one of two frequencies for the oscillator: 5.53 MHz and 32.8 kHz, using the OSCSEL bits in the Oscillator Control on page 187.

zilog <sub>201</sub>

### Table 114. Notational Shorthand

| Notation | Description                    | Operand | Range                                                                                                                        |

|----------|--------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------|

| b        | Bit                            | b       | b represents a value from 0 to 7 (000B to 111B)                                                                              |

| CC       | Condition Code                 | _       | Refer to Condition Codes section in the <i>eZ8 CPU Core User Manual (UM0128)</i> .                                           |

| DA       | Direct Address                 | Addrs   | Addrs. represents a number in the range of 0000H to FFFFH                                                                    |

| ER       | Extended Addressing Register   | Reg     | Reg. represents a number in the range of 000H to FFFH                                                                        |

| IM       | Immediate Data                 | #Data   | Data is a number between 00H to FFH                                                                                          |

| lr       | Indirect Working Register      | @Rn     | n = 0–15                                                                                                                     |

| IR       | Indirect Register              | @Reg    | Reg. represents a number in the range of 00H to FFH                                                                          |

| Irr      | Indirect Working Register Pair | @RRp    | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                             |

| IRR      | Indirect Register Pair         | @Reg    | Reg. represents an even number in the range 00H to FEH                                                                       |

| р        | Polarity                       | р       | Polarity is a single bit binary value of either 0B or 1B.                                                                    |

| r        | Working Register               | Rn      | n = 0 – 15                                                                                                                   |

| R        | Register                       | Reg     | Reg. represents a number in the range of 00H to FFH                                                                          |

| RA       | Relative Address               | Х       | X represents an index in the range of +127 to –<br>128 which is an offset relative to the address of<br>the next instruction |

| rr       | Working Register Pair          | RRp     | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                             |

| RR       | Register Pair Reg              |         | Reg. represents an even number in the range of 00H to FEH                                                                    |

| Vector   | Vector Address                 | Vector  | Vector represents a number in the range of 00H to FFH                                                                        |

| X        | Indexed                        | #Index  | The register or register pair to be indexed is<br>offset by the signed Index value (#Index) in a<br>+127 to<br>-128 range.   |

Table 115 lists additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

**z**ilog<sup>®</sup>

203

Table 116 through Table 123 lists the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| ADC      | dst, src | Add with Carry                                |

| ADCX     | dst, src | Add with Carry using Extended Addressing      |

| ADD      | dst, src | Add                                           |

| ADDX     | dst, src | Add using Extended Addressing                 |

| СР       | dst, src | Compare                                       |

| CPC      | dst, src | Compare with Carry                            |

| CPCX     | dst, src | Compare with Carry using Extended Addressing  |

| CPX      | dst, src | Compare using Extended Addressing             |

| DA       | dst      | Decimal Adjust                                |

| DEC      | dst      | Decrement                                     |

| DECW     | dst      | Decrement Word                                |

| INC      | dst      | Increment                                     |

| INCW     | dst      | Increment Word                                |

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

#### **Table 116. Arithmetic Instructions**