# E·XFL

#### Zilog - Z8F021AHH020EC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusObsoleteCore Processore38Core Size8-BitSpeed20MHzConnectivityIrDA, UART/USARTPeripheralsBrown-out Detect/Reset, LED, LVD, POR, PWM, WDTNumber of I/O17Program Memory SizeEASHProgram Memory TypeFLASHEEPROM Size64 x 8Nufface512 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Operating Temperature4.0°C ~ 105°C (TA)Monting TypeSufface MonthProkage / Case-Suppler Device Package-Prokage / Case-Suppler Device Package-Prokage URLMtps://www.exfl.com/product-detail/zilog/z8f021ahh020e00tr |                            |                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------|

| Core Size8-BitCore Size8-BitSpeed20MHzConnectivityIrDA, UART/USARTPeripheralsBrown-out Detect/Reset, LED, LVD, POR, PWM, WDTNumber of I/O17Program Memory Size2KB (2K × 8)Program Memory TypeFLASHEEPROM Size64 × 8RAM Size512 × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)Supplier Device Package-                                                                      | Product Status             | Obsolete                                                      |

| Speed20MHzConnectivityIrDA, UART/USARTPeripheralsBrown-out Detect/Reset, LED, LVD, POR, PWM, WDTNumber of I/O17Program Memory Size2KB (2K × 8)Program Memory TypeFLASHEEPROM Size64 × 8RAM Size512 × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case0-SSOP (0.209", 5.30mm Width)                                                                                                                            | Core Processor             | eZ8                                                           |

| ConnectivityIrDA, UART/USARTPeripheralsBrown-out Detect/Reset, LED, LVD, POR, PWM, WDTNumber of I/O17Program Memory Size2KB (2K × 8)Program Memory TypeELASHEEPROM Size64 × 8RAM Size512 × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Operating Temperature4.0°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case0.5SOP (0.209", 5.30mm Width)                                                                                                                                                            | Core Size                  | 8-Bit                                                         |

| PeripheralsBrown-out Detect/Reset, LED, LVD, POR, PWM, WDTNumber of I/O17Program Memory Size2KB (2K x 8)Program Memory TypeFLASHEEPROM Size64 x 8RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case0-SSOP (0.209", 5.30mm Width)                                                                                                                                                                 | Speed                      | 20MHz                                                         |

| Number of I/O17Program Memory Size2KB (2K × 8)Program Memory TypeFLASHEEPROM Size64 × 8RAM Size512 × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case0-SSOP (0.209", 5.30mm Width)Suppler Device Package.                                                                                                                                                                                                     | Connectivity               | IrDA, UART/USART                                              |

| Program Memory Size2KB (2K × 8)Program Memory TypeFLASHEEPROM Size64 × 8RAM Size512 × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case2.5SOP (0.209", 5.30mm Width)Suppler Device Package-                                                                                                                                                                                                                   | Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT               |

| Program Memory TypeFLASHEEPROM Size64 x 8RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)Supplier Device Package-                                                                                                                                                                                                                                                | Number of I/O              | 17                                                            |

| EEPROM Size64 x 8RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)Supplier Device Package-                                                                                                                                                                                                                                                                        | Program Memory Size        | 2KB (2K x 8)                                                  |

| RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)Supplier Device Package-                                                                                                                                                                                                                                                                                         | Program Memory Type        | FLASH                                                         |

| Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)Supplier Device Package-                                                                                                                                                                                                                                                                                                        | EEPROM Size                | 64 x 8                                                        |

| Data Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)Supplier Device Package-                                                                                                                                                                                                                                                                                                                                             | RAM Size                   | 512 x 8                                                       |

| Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)Supplier Device Package-                                                                                                                                                                                                                                                                                                                                                             | Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Operating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)Supplier Device Package-                                                                                                                                                                                                                                                                                                                                                                                    | Data Converters            | -                                                             |

| Mounting TypeSurface MountPackage / Case20-SSOP (0.209", 5.30mm Width)Supplier Device Package-                                                                                                                                                                                                                                                                                                                                                                                                                           | Oscillator Type            | Internal                                                      |

| Package / Case     20-SSOP (0.209", 5.30mm Width)       Supplier Device Package     -                                                                                                                                                                                                                                                                                                                                                                                                                                    | Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Supplier Device Package -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Mounting Type              | Surface Mount                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                |

| Purchase URL https://www.e-xfl.com/product-detail/zilog/z8f021ahh020ec00tr                                                                                                                                                                                                                                                                                                                                                                                                                                               | Supplier Device Package    | -                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f021ahh020ec00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

х

| OCD Data Format<br>OCD Auto-Baud Detector/Generator<br>OCD Serial Errors<br>OCD Unlock Sequence (8-Pin Devices Only)<br>Breakpoints<br>Runtime Counter                                                                        | 176<br>177<br>178<br>178<br>179 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| On-Chip Debugger Commands                                                                                                                                                                                                     | 184<br>184                      |

| Oscillator Control                                                                                                                                                                                                            | 187                             |

| Operation       System Clock Selection         Clock Failure Detection and Recovery       Oscillator Control Register Definitions                                                                                             | 187<br>189                      |

| Crystal Oscillator                                                                                                                                                                                                            | 193                             |

| Operating Modes       Crystal Oscillator Operation         Oscillator Operation with an External RC Network       Crystal Oscillator Operation                                                                                | 193                             |

| Internal Precision Oscillator                                                                                                                                                                                                 | 197                             |

| Operation                                                                                                                                                                                                                     | 197                             |

| eZ8 CPU Instruction Set                                                                                                                                                                                                       | 199                             |

| Assembly Language Programming IntroductionAssembly Language SyntaxeZ8 CPU Instruction NotationeZ8 CPU Instruction ClasseseZ8 CPU Instruction ClasseseZ8 CPU Instruction Summary                                               | 200<br>200<br>202               |

| Opcode Maps                                                                                                                                                                                                                   | 216                             |

| Electrical Characteristics                                                                                                                                                                                                    | 221                             |

| Absolute Maximum Ratings       DC Characteristics         DC Characteristics       AC Characteristics         On-Chip Peripheral AC and DC Electrical Characteristics       General Purpose I/O Port Input Data Sample Timing | 222<br>227<br>229               |

# **Interrupt Controller**

The Z8 Encore! XP<sup>®</sup> F082A Series products support up to 20 interrupts. These interrupts consist of 8 internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

#### **Reset Controller**

The Z8 Encore! XP F082A Series products can be reset using the  $\overline{\text{RESET}}$  pin, Power-On Reset, Watchdog Timer (WDT) time-out, STOP mode exit, or Voltage Brownout (VBO) warning signal. The  $\overline{\text{RESET}}$  pin is bi-directional, that is, it functions as reset source as well as a reset indicator.

zilog<sup>°</sup>.

#### **PWM DUAL OUTPUT Mode**

In PWM DUAL OUTPUT mode, the timer outputs a Pulse-Width Modulated (PWM) output signal pair (basic PWM signal and its complement) through two GPIO Port pins. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

If the TPOL bit in the Timer Control register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

The timer also generates a second PWM output signal Timer Output Complement. The Timer Output Complement is the complement of the Timer Output PWM signal. A programmable deadband delay can be configured to time delay (0 to 128 system clock cycles) PWM output transitions on these two pins from a low to a high (inactive to active). This ensures a time gap between the deassertion of one PWM output to the assertion of its complement.

Follow the steps below for configuring a timer for PWM DUAL OUTPUT mode and initiating the PWM operation:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for PWM DUAL OUTPUT mode by writing the TMODE bits in the TxCTL1 register and the TMODEHI bit in TxCTL0 register.

- Set the prescale value.

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the PWM Control register to set the PWM dead band delay value. The deadband delay must be less than the duration of the positive phase of the PWM signal (as defined by the PWM high and low byte registers). It must also be less than the

zilog

Timer Reload Low Byte register occurs, the temporary holding register value is written to the Timer High Byte register. This operation allows simultaneous updates of the 16-bit Timer Reload value.

In COMPARE mode, the Timer Reload High and Low Byte registers store the 16-bit Compare value.

#### Table 52. Timer 0–1 Reload High Byte Register (TxRH)

| BITS  | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|-------|-----|-----|-----|-------|------|-----|-----|-----|

| FIELD |     |     |     | TF    | RH   |     |     |     |

| RESET | 1   | 1   | 1   | 1     | 1    | 1   | 1   | 1   |

| R/W   | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| ADDR  |     |     |     | F02H, | F0AH |     |     |     |

Table 53. Timer 0–1 Reload Low Byte Register (TxRL)

| BITS  | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|-------|-----|-----|-----|-------|------|-----|-----|-----|

| FIELD |     |     |     | TF    | ٦L   |     |     |     |

| RESET | 1   | 1   | 1   | 1     | 1    | 1   | 1   | 1   |

| R/W   | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| ADDR  |     |     |     | F03H, | F0BH |     |     |     |

TRH and TRL—Timer Reload Register High and Low

These two bytes form the 16-bit Reload value, {TRH[7:0], TRL[7:0]}. This value sets the maximum count value which initiates a timer reload to 0001H. In COMPARE mode, these two bytes form the 16-bit Compare value.

## **Timer 0-1 PWM High and Low Byte Registers**

The Timer 0-1 PWM High and Low Byte (TxPWMH and TxPWML) registers (Table 54 and Table 55) control Pulse-Width Modulator (PWM) operations. These registers also store the Capture values for the CAPTURE and CAPTURE/COMPARE modes.

#### Table 54. Timer 0–1 PWM High Byte Register (TxPWMH)

| BITS  | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|-------|-----|-----|-----|-------|------|-----|-----|-----|

| FIELD |     |     |     | PW    | MH   |     |     |     |

| RESET | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 0   |

| R/W   | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| ADDR  |     |     |     | F04H, | F0CH |     |     |     |

zilog

baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal, allowing the Endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

# Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined in Universal Asynchronous Receiver/Transmitter on page 97.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO Port alternate function for the corresponding pin.

zilog<sup>°</sup>

#### ANAIN[3:0]—Analog Input Select

These bits select the analog input for conversion. Not all Port pins in this list are available in all packages for the Z8 Encore! XP<sup>®</sup> F082A Series. For information on port pins available with each package style, see Pin Description on page 9. Do not enable unavailable analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.

For the reserved values, all input switches are disabled to avoid leakage or other undesirable operation. ADC samples taken with reserved bit settings are undefined.

SINGLE-ENDED:

- 0000 = ANA0 (transimpedance amp output when enabled)

- 0001 = ANA1 (transimpedance amp inverting input)

- 0010 = ANA2 (transimpedance amp non-inverting input)

- 0011 = ANA3

- 0100 = ANA4

- 0101 = ANA5

- 0110 = ANA6

- 0111 = ANA7

- 1000 = Reserved

- 1001 = Reserved

- 1010 = Reserved

- 1011 = Reserved

- 1100 = Hold transimpedance input nodes (ANA1 and ANA2) to ground.

- 1101 = Reserved

- 1110 = Temperature Sensor.

- 1111 = Reserved.

DIFFERENTIAL (non-inverting input and inverting input respectively):

- 0000 = ANA0 and ANA10001 = ANA2 and ANA30010 = ANA4 and ANA50011 = ANA1 and ANA00100 = ANA3 and ANA20101 = ANA5 and ANA40110 = ANA6 and ANA50111 = ANA0 and ANA50111 = ANA0 and ANA21000 = ANA0 and ANA31001 = ANA0 and ANA41010 = ANA0 and ANA51011 = Reserved1100 = Reserved1101 = Reserved1101 = Reserved1110 = Reserved

- 1111 = Manual Offset Calibration Mode

Assuming a compensated ADC measurement, the following equation defines the relationship between the ADC reading and the die temperature:

$T = (25/128) \times (ADC - TSCAL[11:2]) + 30$

where, T is the temperature in C; ADC is the 10-bit compensated ADC value; and TSCAL is the temperature sensor calibration value, ignoring the two least significant bits of the 12-bit value.

See Temperature Sensor Calibration Data on page 164 for the location of TSCAL.

#### Calibration

The temperature sensor undergoes calibration during the manufacturing process and is maximally accurate at 30 °C. Accuracy decreases as measured temperatures move further from the calibration point.

**z**ilog<sup>®</sup>

# Flash Status Register

The Flash Status (FSTAT) register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status register shares its Register File address with the Write-only Flash Control register.

Table 79. Flash Status Register (FSTAT)

| BITS  | 7    | 6     | 5 | 4  | 3  | 2   | 1 | 0 |

|-------|------|-------|---|----|----|-----|---|---|

| FIELD | Rese | erved |   |    | FS | TAT |   |   |

| RESET | 0    | 0     | 0 | 0  | 0  | 0   | 0 | 0 |

| R/W   | R    | R     | R | R  | R  | R   | R | R |

| ADDR  |      |       |   | FF | 8H |     |   |   |

Reserved—Must be 0.

FSTAT—Flash Controller Status

000000 = Flash Controller locked

000001 = First unlock command received (73H written)

000010 = Second unlock command received (8CH written)

000011 = Flash Controller unlocked

000100 = Sector protect register selected

001xxx = Program operation in progress

010xxx = Page erase operation in progress

100xxx = Mass erase operation in progress

# Flash Page Select Register

The Flash Page Select (FPS) register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7 bits given by FPS[6:0] are chosen for program/erase operation.

zilog

163

| Info Page<br>Address | Memory<br>Address | Compensation Usage      | ADC Mode                 | Reference<br>Type |

|----------------------|-------------------|-------------------------|--------------------------|-------------------|

| 34                   | FE34              | Negative Gain High Byte | Differential Unbuffered  | External 2.0 V    |

| 35                   | FE35              | Negative Gain Low Byte  | Differential Unbuffered  | External 2.0 V    |

| 78                   | FE78              | Offset                  | Differential 1x Buffered | Internal 2.0 V    |

| 18                   | FE18              | Positive Gain High Byte | Differential 1x Buffered | Internal 2.0 V    |

| 19                   | FE19              | Positive Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V    |

| 36                   | FE36              | Negative Gain High Byte | Differential 1x Buffered | Internal 2.0 V    |

| 37                   | FE37              | Negative Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V    |

| 7B                   | FE7B              | Offset                  | Differential 1x Buffered | External 2.0 V    |

| 1A                   | FE1A              | Positive Gain High Byte | Differential 1x Buffered | External 2.0 V    |

| 1B                   | FE1B              | Positive Gain Low Byte  | Differential 1x Buffered | External 2.0 V    |

| 38                   | FE38              | Negative Gain High Byte | Differential 1x Buffered | External 2.0 V    |

| 39                   | FE39              | Negative Gain Low Byte  | Differential 1x Buffered | External 2.0 V    |

#### Table 94. ADC Calibration Data Location (Continued)

zilog <sub>17</sub>

resides in working register R0. The bit fields of this status byte are defined in Table 103. The contents of the status byte are undefined for write operations to illegal addresses. Also, user code must pop the address and data bytes off the stack.

The write routine uses 13 bytes of stack space in addition to the two bytes of address and data pushed by the user. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS writes exhibit a non-uniform execution time. In general, a write takes  $251 \,\mu s$  (assuming a 20 MHz system clock). Every 400 to 500 writes, however, a maintenance operation is necessary. In this rare occurrence, the write takes up to 61 ms to complete. Slower system clock speeds result in proportionally higher execution times.

NVDS byte writes to invalid addresses (those exceeding the NVDS array size) have no effect. Illegal write operations have a 2  $\mu$ s execution time.

#### Table 103. Write Status Byte

| BITS             | 7 | 6    | 5     | 4 | 3    | 2  | 1   | 0   |

|------------------|---|------|-------|---|------|----|-----|-----|

| FIELD            |   | Rese | erved |   | RCPY | PF | AWE | DWE |

| DEFAULT<br>VALUE | 0 | 0    | 0     | 0 | 0    | 0  | 0   | 0   |

Reserved—Must be 0.

**RCPY**—Recopy Subroutine Executed

A recopy subroutine was executed. These operations take significantly longer than a normal write operation.

PF—Power Failure Indicator

A power failure or system reset occurred during the most recent attempted write to the NVDS array.

AW-Address Write Error

An address byte failure occurred during the most recent attempted write to the NVDS array.

DWE—Data Write Error

A data byte failure occurred during the most recent attempted write to the NVDS array.

#### Byte Read

To read a byte from the NVDS array, user code must first push the address onto the stack. User code issues a CALL instruction to the address of the byte-read routine (0x1000). At the return from the sub-routine, the read byte resides in working register R0, and the read status byte resides in working register R1. The contents of the status byte are undefined for

202

#### Table 115. Additional Symbols

| Definition                   |

|------------------------------|

| Destination Operand          |

| Source Operand               |

| Indirect Address Prefix      |

| Stack Pointer                |

| Program Counter              |

| Flags Register               |

| Register Pointer             |

| Immediate Operand Prefix     |

| Binary Number Suffix         |

| Hexadecimal Number<br>Prefix |

| Hexadecimal Number<br>Suffix |

|                              |

Assignment of a value is indicated by an arrow. For example,

$dst \leftarrow dst + src$

indicates the source data is added to the destination data and the result is stored in the destination location.

# eZ8 CPU Instruction Classes

eZ8 CPU instructions can be divided functionally into the following groups:

- Arithmetic

- Bit Manipulation

- Block Transfer

- CPU Control

- Load

- Logical

- Program Control

- Rotate and Shift

**z**ilog<sup>®</sup>

203

Table 116 through Table 123 lists the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| ADC      | dst, src | Add with Carry                                |

| ADCX     | dst, src | Add with Carry using Extended Addressing      |

| ADD      | dst, src | Add                                           |

| ADDX     | dst, src | Add using Extended Addressing                 |

| CP       | dst, src | Compare                                       |

| CPC      | dst, src | Compare with Carry                            |

| CPCX     | dst, src | Compare with Carry using Extended Addressing  |

| CPX      | dst, src | Compare using Extended Addressing             |

| DA       | dst      | Decimal Adjust                                |

| DEC      | dst      | Decrement                                     |

| DECW     | dst      | Decrement Word                                |

| INC      | dst      | Increment                                     |

| INCW     | dst      | Increment Word                                |

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

#### **Table 116. Arithmetic Instructions**

**z**ilog<sup>°</sup>

205

#### Table 119. CPU Control Instructions (Continued)

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| SCF      | _        | Set Carry Flag         |

| SRP      | SIC      | Set Register Pointer   |

| STOP     | _        | STOP Mode              |

| WDT      | _        | Watchdog Timer Refresh |

#### Table 120. Load Instructions

| Mnemonic | Operands    | Instruction                                                             |

|----------|-------------|-------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                   |

| LD       | dst, src    | Load                                                                    |

| LDC      | dst, src    | Load Constant to/from Program Memory                                    |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                  |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                     |

| LDX      | dst, src    | Load using Extended Addressing                                          |

| LEA      | dst, X(src) | Load Effective Address                                                  |

| POP      | dst         | Рор                                                                     |

| POPX     | dst         | Pop using Extended Addressing                                           |

| PUSH     | src         | Push                                                                    |

| PUSHX    | src         | Push using Extended Addressing                                          |

|          |             |                                                                         |

### Table 121. Logical Instructions

| Mnemonic | Operands | Instruction                           |

|----------|----------|---------------------------------------|

| AND      | dst, src | Logical AND                           |

| ANDX     | dst, src | Logical AND using Extended Addressing |

| COM      | dst      | Complement                            |

| OR       | dst, src | Logical OR                            |

**z**ilog<sup>°</sup>

| 2 | n | ٥ |

|---|---|---|

| 4 | υ | 3 |

| Assembly<br>Mnemonic | Symbolic<br>Operation                                                                            | Addres        | Address Mode Opcode(s |           | Flags |              |   |   |   | Fetch | Instr. |   |

|----------------------|--------------------------------------------------------------------------------------------------|---------------|-----------------------|-----------|-------|--------------|---|---|---|-------|--------|---|

|                      |                                                                                                  | dst           | src                   | (Hex)     | С     | Ζ            | S | ۷ | D | Н     | Cycles |   |

| COM dst              | $dst \gets \simdst$                                                                              | R             |                       | 60        | -     | *            | * | 0 | - | -     | 2      | 2 |

|                      |                                                                                                  | IR            |                       | 61        | -     |              |   |   |   |       | 2      | 3 |

| CP dst, src          | dst - src                                                                                        | r             | r                     | A2        | *     | *            | * | * | - | -     | 2      | 3 |

|                      |                                                                                                  | r             | lr                    | A3        | _     |              |   |   |   |       | 2      | 4 |

|                      |                                                                                                  | R             | R                     | A4        | -     |              |   |   |   |       | 3      | 3 |

|                      |                                                                                                  | R             | IR                    | A5        | -     |              |   |   |   |       | 3      | 4 |

|                      |                                                                                                  | R             | IM                    | A6        | -     |              |   |   |   |       | 3      | 3 |

|                      |                                                                                                  | IR            | IM                    | A7        | -     |              |   |   |   |       | 3      | 4 |

| CPC dst, src         | dst - src - C                                                                                    | r             | r                     | 1F A2     | *     | *            | * | * | _ | -     | 3      | 3 |

|                      |                                                                                                  | r             | Ir                    | 1F A3     | -     |              |   |   |   |       | 3      | 4 |

|                      |                                                                                                  | R             | R                     | 1F A4     | -     |              |   |   |   |       | 4      | 3 |

|                      |                                                                                                  | R             | IR                    | 1F A5     | -     |              |   |   |   |       | 4      | 4 |

|                      |                                                                                                  | R             | IM                    | 1F A6     | -     |              |   |   |   |       | 4      | 3 |

|                      |                                                                                                  | IR            | IM                    | 1F A7     | -     |              |   |   |   |       | 4      | 4 |

| CPCX dst, src        | dst - src - C                                                                                    | ER            | ER                    | 1F A8     | *     | *            | * | * | - | -     | 5      | 3 |

|                      |                                                                                                  | ER            | IM                    | 1F A9     | -     |              |   |   |   |       | 5      | 3 |

| CPX dst, src         | dst - src                                                                                        | ER            | ER                    | A8        | *     | *            | * | * | _ | _     | 4      | 3 |

|                      |                                                                                                  | ER            | IM                    | A9        | -     |              |   |   |   |       | 4      | 3 |

| DA dst               | $dst \gets DA(dst)$                                                                              | R             |                       | 40        | *     | *            | * | Х | - | -     | 2      | 2 |

|                      |                                                                                                  | IR            |                       | 41        | -     |              |   |   |   |       | 2      | 3 |

| DEC dst              | $dst \gets dst \text{ - } 1$                                                                     | R             |                       | 30        | _     | *            | * | * | _ | _     | 2      | 2 |

|                      |                                                                                                  | IR            |                       | 31        | -     |              |   |   |   |       | 2      | 3 |

| DECW dst             | $dst \gets dst \text{ - } 1$                                                                     | RR            |                       | 80        | _     | *            | * | * | _ | _     | 2      | 5 |

|                      |                                                                                                  | IRR           |                       | 81        | -     |              |   |   |   |       | 2      | 6 |

| DI                   | $IRQCTL[7] \leftarrow 0$                                                                         |               |                       | 8F        | _     | _            | _ | _ | _ | _     | 1      | 2 |

| DJNZ dst, RA         | $\begin{array}{l} dst \leftarrow dst - 1 \\ if \ dst \neq 0 \\ PC \leftarrow PC + X \end{array}$ | r             |                       | 0A-FA     | _     | _            | _ | _ | _ | _     | 2      | 3 |

| EI                   | $IRQCTL[7] \leftarrow 1$                                                                         |               |                       | 9F        | _     | -            | _ | _ | - | -     | 1      | 2 |

| Flags Notation:      | * = Value is a function<br>– = Unaffected<br>X = Undefined                                       | of the result | of the o              | peration. |       | : Re<br>: Se |   |   | ) |       |        |   |

#### Table 124. eZ8 CPU Instruction Summary (Continued)

| V <sub>DD</sub> = 2.7 V to 3.6 V |                                                                               |                                           |          |          |       |                                                                  |  |  |

|----------------------------------|-------------------------------------------------------------------------------|-------------------------------------------|----------|----------|-------|------------------------------------------------------------------|--|--|

|                                  |                                                                               | Maximum <sup>2</sup> Maximum <sup>3</sup> |          |          |       |                                                                  |  |  |

| Symbol                           | Parameter                                                                     | Typical $^1$                              | Std Temp | Ext Temp | Units | Conditions                                                       |  |  |

| I <sub>DD</sub> Stop             | Supply Current in STOP<br>Mode                                                | 0.1                                       |          |          | μA    | No peripherals enabled. All pins driven to $V_{DD}$ or $V_{SS}.$ |  |  |

| I <sub>DD</sub> Halt             | Supply Current in HALT                                                        | 35                                        | 55       | 65       | μA    | 32 kHz                                                           |  |  |

|                                  | Mode (with all peripherals disabled)                                          | 520                                       |          |          | μA    | 5.5 MHz                                                          |  |  |

|                                  | penpinenaie aleaalea)                                                         | 2.1                                       | 2.85     | 2.85     | mA    | 20 MHz                                                           |  |  |

| I <sub>DD</sub>                  | Supply Current in                                                             | 2.8                                       |          |          | mA    | 32 kHz                                                           |  |  |

|                                  | ACTIVE Mode (with all peripherals disabled)                                   | 4.5                                       | 5.2      | 5.2      | mA    | 5.5 MHz                                                          |  |  |

|                                  |                                                                               | 5.5                                       | 6.5      | 6.5      | mA    | 10 MHz                                                           |  |  |

|                                  | -                                                                             | 7.9                                       | 11.5     | 11.5     | mA    | 20 MHz                                                           |  |  |

| I <sub>DD</sub> WDT              | Watchdog Timer Supply<br>Current                                              | 0.9                                       | 1.0      | 1.1      | μA    |                                                                  |  |  |

| I <sub>DD</sub>                  | Crystal Oscillator<br>Supply Current                                          | 40                                        |          |          | μA    | 32 kHz                                                           |  |  |

| XTAL                             |                                                                               | 230                                       |          |          | μA    | 4 MHz                                                            |  |  |

|                                  | -                                                                             | 760                                       |          |          | μA    | 20 MHz                                                           |  |  |

| I <sub>DD</sub> IPO              | Internal Precision<br>Oscillator Supply<br>Current                            | 350                                       | 500      | 550      | μA    |                                                                  |  |  |

| I <sub>DD</sub> VBO              | Voltage Brownout and<br>Low-Voltage Detect<br>Supply Current                  | 50                                        |          |          | μA    | For 20-/28-pin devices<br>(VBO only); See Notes 4                |  |  |

|                                  |                                                                               |                                           |          |          |       | For 8-pin devices; See<br>Notes 4                                |  |  |

| I <sub>DD</sub> ADC              | Analog to Digital<br>Converter Supply<br>Current (with External<br>Reference) | 2.8                                       | 3.1      | 3.2      | mA    | 32 kHz                                                           |  |  |

|                                  |                                                                               | 3.1                                       | 3.6      | 3.7      | mA    | 5.5 MHz                                                          |  |  |

|                                  |                                                                               | 3.3                                       | 3.7      | 3.8      | mA    | 10 MHz                                                           |  |  |

|                                  | -                                                                             | 3.7                                       | 4.2      | 4.3      | mA    | 20 MHz                                                           |  |  |

| I <sub>DD</sub><br>ADCRef        | ADC Internal Reference<br>Supply Current                                      | 0                                         |          |          | μA    | See Notes 4                                                      |  |  |

| I <sub>DD</sub> CMP              | Comparator supply<br>Current                                                  | 150                                       | 180      | 190      | μA    | See Notes 4                                                      |  |  |

# Table 128. Power Consumption

Zilog 239

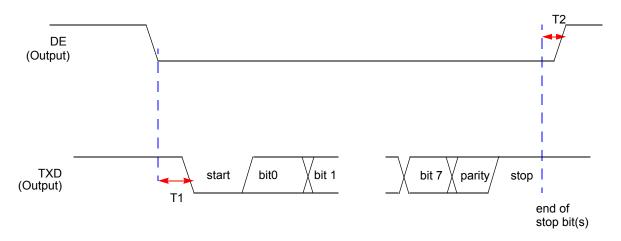

Figure 38 and Table 143 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the transmit data register has been written. DE remains asserted for multiple characters as long as the transmit data register is written with the next character before the current character has completed.

Figure 38. UART Timing Without CTS

| Table | 143. | UART | Timing | Without CTS |

|-------|------|------|--------|-------------|

|-------|------|------|--------|-------------|

|                |                                                                        | Delay (ns)        |            |  |  |

|----------------|------------------------------------------------------------------------|-------------------|------------|--|--|

| Parameter      | Abbreviation                                                           | Minimum           | Maximum    |  |  |

| UART           |                                                                        |                   |            |  |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * XIN<br>period | 1 bit time |  |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx data register is empty) | ± 5               |            |  |  |

265

L LD 205 LDC 205 LDCI 204, 205 LDE 205 LDEI 204, 205 LDX 205 LEA 205 load 205 load constant 204 load constant to/from program memory 205 load constant with auto-increment addresses 205 load effective address 205 load external data 205 load external data to/from data memory and auto-increment addresses 204 load external to/from data memory and auto-increment addresses 205 load using extended addressing 205 logical AND 205 logical AND/extended addressing 205 logical exclusive OR 206 logical exclusive OR/extended addressing 206 logical instructions 205 logical OR 205 logical OR/extended addressing 206 low power modes 33

# Μ

master interrupt enable 57 memory data 17 program 15 mode CAPTURE 85, 86 CAPTURE/COMPARE 85 CONTINUOUS 84 COUNTER 84 GATED 85 ONE-SHOT 84 PWM 85 modes 85 MULT 203 multiply 203 multiprocessor mode, UART 103

# Ν

NOP (no operation) 204 notation b 201 cc 201 DA 201 ER 201 IM 201 IR 201 Ir 201 IRR 201 Irr 201 p 201 R 201 r 201 RA 201 RR 201 rr 201 vector 201 X 201 notational shorthand 201

#### O OCD

architecture 173 auto-baud detector/generator 176 baud rate limits 177 block diagram 173 breakpoints 178 commands 179 control register 184 data format 176 DBG pin to RS-232 Interface 174 debug mode 175 debugger break 206 interface 174 serial errors 177 status register 185