Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Obsolete                                                  |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 20MHz                                                     |  |

| Connectivity               | IrDA, UART/USART                                          |  |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |  |

| Number of I/O              | 17                                                        |  |

| Program Memory Size        | 2KB (2K x 8)                                              |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | 64 x 8                                                    |  |

| RAM Size                   | 512 x 8                                                   |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | -                                                         |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |  |

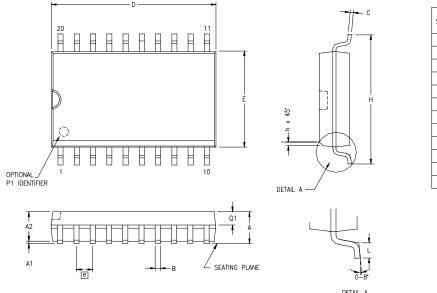

| Mounting Type              | Surface Mount                                             |  |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |  |

| Supplier Device Package    | -                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f021ahh020sc |  |

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

vii

| Watchdog Timer Time-Out Response                         |         |

|----------------------------------------------------------|---------|

| Watchdog Timer Reload Unlock Sequence                    |         |

| Watchdog Timer Calibration                               |         |

| Watchdog Timer Control Register Definitions              |         |

| Watchdog Timer Control Register                          |         |

| Watchdog Timer Reload Upper, High and Low Byte Registers |         |

| Universal Asynchronous Receiver/Transmitter              | 97      |

| Architecture                                             |         |

| Operation                                                | 98      |

| Data Format                                              | 98      |

| Transmitting Data using the Polled Method                |         |

| Transmitting Data using the Interrupt-Driven Method      |         |

| Receiving Data using the Polled Method                   |         |

| Receiving Data using the Interrupt-Driven Method         |         |

| Clear To Send (CTS) Operation                            |         |

| MULTIPROCESSOR (9-bit) Mode                              |         |

| External Driver Enable                                   |         |

| UART Interrupts                                          |         |

| UART Baud Rate Generator                                 |         |

| UART Control Register Definitions                        |         |

| UART Control 0 and Control 1 Registers                   |         |

| UART Status 0 Register                                   |         |

| UART Status 1 Register                                   |         |

| UART Transmit Data Register                              |         |

| UART Receive Data Register                               |         |

| UART Address Compare Register                            |         |

| UART Baud Rate High and Low Byte Registers               |         |

| Infrared Encoder/Decoder                                 | 117     |

| Architecture                                             | 117     |

| Operation                                                | 445     |

| Transmitting IrDA Data                                   |         |

| Receiving IrDA Data                                      |         |

| Infrared Encoder/Decoder Control Register Definitions    |         |

| Analog-to-Digital Converter                              | 121     |

| Architecture                                             |         |

| Operation                                                |         |

| Data Format                                              |         |

| =                                                        | · · · · |

PS022825-0908 Table of Contents

# Z8 Encore! XP® F082A Series **Product Specification**

| Hardware Overflow                                            | 123     |

|--------------------------------------------------------------|---------|

| Automatic Powerdown                                          |         |

| Single-Shot Conversion                                       |         |

| Continuous Conversion                                        |         |

| Interrupts                                                   |         |

| Calibration and Compensation                                 |         |

| ADC Compensation Details                                     |         |

| Input Buffer Stage                                           |         |

| ADC Control Register Definitions                             |         |

| ADC Control Register 0                                       |         |

| ADC Control/Status Register 1                                |         |

| ADC Data High Byte Register                                  |         |

| ADC Data Low Byte Register                                   |         |

| Low Power Operational Amplifier                              | 134     |

| Overview                                                     | 134     |

| Operation                                                    | 134     |

| Comparator                                                   |         |

| •                                                            |         |

| Operation                                                    |         |

| Comparator Control Register Definitions                      | 136     |

| Temperature Sensor                                           | 139     |

| Temperature Sensor Operation                                 | 139     |

| Flash Memory                                                 | 141     |

| Architecture                                                 | 141     |

| Flash Information Area                                       |         |

| Operation                                                    |         |

|                                                              |         |

| Flash Operation Timing Using the Flash Frequency Registers   |         |

| Flash Code Protection Against Accidental Program and Erasure |         |

| · · · · · · · · · · · · · · · · · · ·                        | 147     |

|                                                              | <br>147 |

|                                                              | <br>147 |

|                                                              | 148     |

| <b>71</b>                                                    | 148     |

|                                                              | 149     |

| · · · · · · · · · · · · · · · · · · ·                        | 149     |

| •                                                            | 150     |

|                                                              | 150     |

PS022825-0908 **Table of Contents**

Table 5. Z8 Encore! XP F082A Series Program Memory Maps (Continued)

| Program Memory Address (Hex)                | Function                     |

|---------------------------------------------|------------------------------|

| Z8F022A and Z8F021A Products                |                              |

| 0000–0001                                   | Flash Option Bits            |

| 0002–0003                                   | Reset Vector                 |

| 0004–0005                                   | WDT Interrupt Vector         |

| 0006–0007                                   | Illegal Instruction Trap     |

| 0008–0037                                   | Interrupt Vectors*           |

| 0038–0039                                   | Reserved                     |

| 003A-003D                                   | Oscillator Fail Trap Vectors |

| 003E-07FF                                   | Program Memory               |

| Z8F012A and Z8F011A Products                |                              |

| 0000–0001                                   | Flash Option Bits            |

| 0002–0003                                   | Reset Vector                 |

| 0004–0005                                   | WDT Interrupt Vector         |

| 0006–0007                                   | Illegal Instruction Trap     |

| 0008–0037                                   | Interrupt Vectors*           |

| 0038–0039                                   | Reserved                     |

| 003A-003D                                   | Oscillator Fail Trap Vectors |

| 003E-03FF                                   | Program Memory               |

| * See Table 32 on page 56 for a list of the | e interrupt vectors.         |

## **Data Memory**

The Z8 Encore! XP F082A Series does not use the eZ8 CPU's 64 KB Data Memory address space.

### Flash Information Area

Table 6 on page 18 describes the Z8 Encore! XP F082A Series Flash Information Area. This 128 B Information Area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash Information Area is mapped into the Program Memory and overlays the 128 bytes at addresses FEOOH to FF7FH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Infor-

PS022825-0908 Address Space and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the  $\overline{RESET}$  input pin is asserted Low, the Z8 Encore!  $XP^{\circledR}$  F082A Series devices remain in the Reset state. If the  $\overline{RESET}$  pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following  $\overline{RESET}$  pin deassertion. Following a System Reset initiated by the external  $\overline{RESET}$  pin, the EXT status bit in the Reset Status (RSTSTAT) register is set to 1.

### **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see Port A–D Control Registers on page 46), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows a Z8 Encore! XP F082A Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the RESET pin Low. The RESET pin is held Low by the internal circuitry until the appropriate delay listed in Table 8 has elapsed.

### **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control register. The On-Chip Debugger block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset the POR bit in the Reset Status (RSTSTAT) register is set.

# **Stop Mode Recovery**

STOP mode is entered by execution of a STOP instruction by the eZ8 CPU. See Low-Power Modes on page 33 for detailed STOP mode information. During Stop Mode Recovery (SMR), the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay (see Table 131 on page 229)  $T_{SMR}$ , also includes the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control register (WDTCTL) and the Oscillator Control register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset

**Table 14. Port Alternate Function Mapping (Non 8-Pin Parts)**

| Port   | Pin | Mnemonic    | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------|-----------------------------------------|-----------------------------------------|

| Port A | PA0 | T0IN/T0OUT* | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|        |     | Reserved    |                                         | -                                       |

|        | PA1 | T0OUT       | Timer 0 Output                          | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA2 | DE0         | UART 0 Driver Enable                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA3 | CTS0        | UART 0 Clear to Send                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA4 | RXD0/IRRX0  | UART 0/IrDA 0 Receive Data              | _                                       |

|        |     | Reserved    |                                         | _                                       |

|        | PA5 | TXD0/IRTX0  | UART 0/IrDA 0 Transmit Data             | _                                       |

|        |     | Reserved    |                                         | _                                       |

|        | PA6 | T1IN/T1OUT* | Timer 1 Input/Timer 1 Output Complement | _                                       |

|        |     | Reserved    |                                         | _                                       |

|        | PA7 | T1OUT       | Timer 1 Output                          | _                                       |

|        |     | Reserved    |                                         |                                         |

**Note:** Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in Port A–D Alternate Function Sub-Registers on page 47 automatically enables the associated alternate function.

<sup>\*</sup> Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in Timer Pin Signal Operation on page 82.

Set 1 Sub-Registers on page 50, GPIO Alternate Functions on page 38, and Port A–D Alternate Function Set 2 Sub-Registers on page 51. See GPIO Alternate Functions on page 38 to determine the alternate function associated with each port pin.

#### Caution:

Do not enable alternate functions for GPIO port pins for which there is no associated alternate function. Failure to follow this guideline can result in unpredictable operation.

Table 20. Port A–D Alternate Function Sub-Registers (PxAF)

| BITS  | 7                                                           | 6          | 5           | 4             | 3             | 2             | 1            | 0        |

|-------|-------------------------------------------------------------|------------|-------------|---------------|---------------|---------------|--------------|----------|

| FIELD | AF7                                                         | AF6        | AF5         | AF4           | AF3           | AF2           | AF1          | AF0      |

| RESET | 00H (Ports A–C); 01H (Port D); 04H (Port A of 8-pin device) |            |             |               |               |               |              |          |

| R/W   | R/W                                                         |            |             |               |               |               |              |          |

| ADDR  | If 02H i                                                    | n Port A–D | Address Reg | gister, acces | sible througl | n the Port A- | -D Control F | Register |

AF[7:0]—Port Alternate Function enabled

0 =The port pin is in normal mode and the DDx bit in the Port A–D Data Direction sub-register determines the direction of the pin.

1 = The alternate function selected through Alternate Function Set sub-registers is enabled. Port pin operation is controlled by the alternate function.

### Port A-D Output Control Sub-Registers

The Port A–D Output Control sub-register (Table 21) is accessed through the Port A–D Control register by writing 03H to the Port A–D Address register. Setting the bits in the Port A–D Output Control sub-registers to 1 configures the specified port pins for opendrain operation. These sub-registers affect the pins directly and, as a result, alternate functions are also affected.

Table 21. Port A–D Output Control Sub-Registers (PxOC)

| BITS  | 7                                                                                     | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|---------------------------------------------------------------------------------------|------|------|------|------|------|------|------|

| FIELD | POC7                                                                                  | POC6 | POC5 | POC4 | POC3 | POC2 | POC1 | POC0 |

| RESET | 00H (Ports A-C); 01H (Port D)                                                         |      |      |      |      |      |      |      |

| R/W   | R/W                                                                                   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| ADDR  | If 03H in Port A–D Address Register, accessible through the Port A–D Control Register |      |      |      |      |      |      |      |

POC[7:0]—Port Output Control

These bits function independently of the alternate function bit and always disable the drains if set to 1.

0 = The source current is enabled for any output mode (unless overridden by the alternate

### Receiving Data using the Interrupt-Driven Method

The UART Receiver interrupt indicates the availability of new data (as well as error conditions). Follow the steps below to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the acceptable baud rate

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Receiver interrupt and set the acceptable priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 6. Write to the UART Control 1 Register to enable Multiprocessor (9-bit) mode functions, if appropriate.

- Set the Multiprocessor Mode Select (MPEN) to Enable MULTIPROCESSOR mode.

- Set the Multiprocessor Mode Bits, MPMD[1:0], to select the acceptable address matching scheme.

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore!<sup>®</sup> devices without a DMA block)

- 7. Write the device address to the Address Compare Register (automatic MULTIPRO-CESSOR modes only).

- 8. Write to the UART Control 0 register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if multiprocessor mode is not enabled, and select either even or odd parity.

- 9. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine (ISR) performs the following:

- 1. Checks the UART Status 0 register to determine the source of the interrupt error, break, or received data.

- 2. Reads the data from the UART Receive Data register if the interrupt was because of data available. If operating in MULTIPROCESSOR (9-bit) mode, further actions may be required depending on the MULTIPROCESSOR mode bits MPMD[1:0].

128

Compensation Steps:

1. Correct for Offset

| ADC MSB    | ADC LSB    |  |  |

|------------|------------|--|--|

| -          |            |  |  |

| Offset MSB | Offset LSB |  |  |

| =          |            |  |  |

| #1 MSB     | #1 LSB     |  |  |

2. Take absolute value of the offset corrected ADC value *if negative*—the gain correction factor is computed assuming positive numbers, with sign restoration afterward.

| #2 MSB | #2 LSB |

|--------|--------|

Also take absolute value of the gain correction word if negative.

3. Multiply by Gain Correction Word. If in DIFFERENTIAL mode, there are two gain correction values: one for positive ADC values, another for negative ADC values. Based on the sign of #2, use the appropriate Gain Correction Word.

|   | #2 MSB    | #2 LSB    |    |    |

|---|-----------|-----------|----|----|

| * |           |           |    |    |

|   | AGain MSB | AGain LSB | ]  |    |

| = |           |           |    |    |

|   | #3        | #3        | #3 | #3 |

4. Round the result and discard the least significant two bytes (this is equivalent to dividing by  $2^{16}$ ).

| #3     | #3      | #3   | #3   |

|--------|---------|------|------|

| -      |         |      |      |

| 0x00   | 0x00    | 0x80 | 0x00 |

| =      |         |      |      |

| #4 MSB | #4 I SB |      |      |

5. Determine sign of the gain correction factor using the sign bits from Step 2. If the offset corrected ADC value AND the gain correction word have the same sign, then the factor is positive and is left unchanged. If they have differing signs, then the factor is negative and must be multiplied by -1.

162

**Table 94. ADC Calibration Data Location**

| AddressAddressCompensation UsageADC ModeType60FE60OffsetSingle-Ended UnbufferedInternal 2.0 V08FE08Gain High ByteSingle-Ended UnbufferedInternal 2.0 V09FE09Gain Low ByteSingle-Ended UnbufferedInternal 1.0 V63FE63OffsetSingle-Ended UnbufferedInternal 1.0 V0AFE0AGain High ByteSingle-Ended UnbufferedInternal 1.0 V0BFE0BGain Low ByteSingle-Ended UnbufferedExternal 2.0 V0CFE66OffsetSingle-Ended UnbufferedExternal 2.0 V0CFE0CGain High ByteSingle-Ended UnbufferedExternal 2.0 V0DFE0DGain Low ByteSingle-Ended UnbufferedExternal 2.0 V0BFE69OffsetSingle-Ended 1x BufferedInternal 2.0 V0BFE0BGain High ByteSingle-Ended 1x BufferedInternal 2.0 V0CFE0CGain Low ByteSingle-Ended 1x BufferedExternal 2.0 V0FFE0FGain Low ByteSingle-Ended 1x BufferedExternal 2.0 V10FE10Gain High ByteSingle-Ended 1x BufferedExternal 2.0 V11FE11Gain Low ByteSingle-Ended 1x BufferedExternal 2.0 V12FE12Positive Gain Low ByteDifferential UnbufferedInternal 2.0 V13FE13Positive Gain Low ByteDifferential UnbufferedInternal 2.0 V14FE14Positive Gain Low ByteDiffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Info Page | Memory  |                         |                          | Reference      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|-------------------------|--------------------------|----------------|

| FE08 Gain High Byte Single-Ended Unbuffered Internal 2.0 V  99 FE09 Gain Low Byte Single-Ended Unbuffered Internal 2.0 V  63 FE63 Offset Single-Ended Unbuffered Internal 1.0 V  0A FE0A Gain High Byte Single-Ended Unbuffered Internal 1.0 V  0B FE0B Gain Low Byte Single-Ended Unbuffered Internal 1.0 V  0B FE0B Gain Low Byte Single-Ended Unbuffered Internal 1.0 V  0C FE0C Gain High Byte Single-Ended Unbuffered External 2.0 V  0D FE0D Gain Low Byte Single-Ended Unbuffered External 2.0 V  0D FE0D Gain Low Byte Single-Ended Unbuffered Internal 2.0 V  0D FE0B Gain High Byte Single-Ended 1x Buffered Internal 2.0 V  0D FE0B Gain High Byte Single-Ended 1x Buffered Internal 2.0 V  0F FE0F Gain Low Byte Single-Ended 1x Buffered External 2.0 V  0F FE0C Gain High Byte Single-Ended 1x Buffered External 2.0 V  10 FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V  11 FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V  12 FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V  13 FE13 Positive Gain High Byte Differential Unbuffered Internal 2.0 V  14 FE31 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V  15 FE72 Offset Differential Unbuffered Internal 2.0 V  16 FE16 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V  17 FE17 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V  18 FE31 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V  19 FE15 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  19 FE30 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  19 FE31 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  19 FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  19 FE33 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  19 FE30 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  19 FE30 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  19 FE30 Negative Gain High Byte Differential Unbuffered Internal 1.0 V                                                         | Address   | Address | Compensation Usage      | ADC Mode                 | Туре           |

| FE09 Gain Low Byte Single-Ended Unbuffered Internal 2.0 V G3 FE63 Offset Single-Ended Unbuffered Internal 1.0 V G4 FE0A Gain High Byte Single-Ended Unbuffered Internal 1.0 V G5 FE0B Gain Low Byte Single-Ended Unbuffered Internal 1.0 V G6 FE66 Offset Single-Ended Unbuffered External 2.0 V G7 FE0C Gain High Byte Single-Ended Unbuffered External 2.0 V G8 FE0B Gain Low Byte Single-Ended Unbuffered External 2.0 V G8 FE0B Gain Low Byte Single-Ended Unbuffered External 2.0 V G8 FE69 Offset Single-Ended 1x Buffered Internal 2.0 V G9 FE0B Gain High Byte Single-Ended 1x Buffered Internal 2.0 V G6 FE0C Gain High Byte Single-Ended 1x Buffered Internal 2.0 V G6 FE6C Offset Single-Ended 1x Buffered External 2.0 V G7 FE0B Gain Low Byte Single-Ended 1x Buffered External 2.0 V G8 FE6B Offset Single-Ended 1x Buffered External 2.0 V G8 FE6C Offset Single-Ended 1x Buffered External 2.0 V G8 FE10 Gain High Byte Single-Ended 1x Buffered Internal 2.0 V G8 FE6B Offset Differential Unbuffered Internal 2.0 V G8 FE6B Offset Differential Unbuffered Internal 2.0 V G9 FE6B Offset Differential Unbuffered Internal 2.0 V C9 FE7D Offset Differe | 60        | FE60    | Offset                  | Single-Ended Unbuffered  | Internal 2.0 V |

| FE63 Offset Single-Ended Unbuffered Internal 1.0 V  OA FE0A Gain High Byte Single-Ended Unbuffered Internal 1.0 V  OB FE0B Gain Low Byte Single-Ended Unbuffered Internal 1.0 V  66 FE66 Offset Single-Ended Unbuffered External 2.0 V  OC FE0C Gain High Byte Single-Ended Unbuffered External 2.0 V  OD FE0D Gain Low Byte Single-Ended Unbuffered External 2.0 V  OD FE0D Gain High Byte Single-Ended Unbuffered External 2.0 V  OF FE69 Offset Single-Ended 1x Buffered Internal 2.0 V  OF FE0E Gain High Byte Single-Ended 1x Buffered Internal 2.0 V  OF FE0F Gain Low Byte Single-Ended 1x Buffered Internal 2.0 V  OF FE6C Offset Single-Ended 1x Buffered External 2.0 V  OF FE6C Offset Single-Ended 1x Buffered External 2.0 V  OF FE6C Offset Single-Ended 1x Buffered External 2.0 V  OF FE6C Offset Single-Ended 1x Buffered External 2.0 V  OF FE6C Offset Differential Unbuffered Internal 2.0 V  OF FE6F Offset Differential Unbuffered Internal 1.0 V  OF FE7F Offset Differential Unbuffered Internal 1.0 V                                                                                                                                                                                                                                        | 08        | FE08    | Gain High Byte          | Single-Ended Unbuffered  | Internal 2.0 V |

| FEOA Gain High Byte Single-Ended Unbuffered Internal 1.0 V  B FEOB Gain Low Byte Single-Ended Unbuffered Internal 1.0 V  GEOFECC Gain High Byte Single-Ended Unbuffered External 2.0 V  CEOFECC Gain High Byte Single-Ended Unbuffered External 2.0 V  DEOFECC Gain High Byte Single-Ended Unbuffered External 2.0 V  DEOFECC Gain High Byte Single-Ended Unbuffered External 2.0 V  GEOFECC Gain High Byte Single-Ended Unbuffered Internal 2.0 V  GEOFECC Gain High Byte Single-Ended 1x Buffered Internal 2.0 V  GEOFECC Gain High Byte Single-Ended 1x Buffered Internal 2.0 V  GEOFECC Offset Single-Ended 1x Buffered External 2.0 V  GEOFECC Offset Differential Unbuffered Internal 1.0 V  GEOFECC Offset Differential Unbuffered Internal 2.0 V  GEOFECC Offset Differential Unbuffered External 2.0 V                                                                                                         | 09        | FE09    | Gain Low Byte           | Single-Ended Unbuffered  | Internal 2.0 V |

| Gain Low Byte Single-Ended Unbuffered External 2.0 V GENEROR Gain High Byte Single-Ended Unbuffered External 2.0 V CENTRO GENEROR Gain High Byte Single-Ended Unbuffered External 2.0 V CENTRO GENEROR | 63        | FE63    | Offset                  | Single-Ended Unbuffered  | Internal 1.0 V |

| FE66 Offset Single-Ended Unbuffered External 2.0 V  OC FEOC Gain High Byte Single-Ended Unbuffered External 2.0 V  OD FEOD Gain Low Byte Single-Ended Unbuffered External 2.0 V  69 FE69 Offset Single-Ended 1x Buffered Internal 2.0 V  OE FE0E Gain High Byte Single-Ended 1x Buffered Internal 2.0 V  OF FE0F Gain Low Byte Single-Ended 1x Buffered Internal 2.0 V  OF FE0C Offset Single-Ended 1x Buffered External 2.0 V  10 FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V  11 FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V  12 FE6F Offset Differential Unbuffered Internal 2.0 V  13 FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V  14 FE13 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V  30 FE30 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V  15 FE72 Offset Differential Unbuffered Internal 2.0 V  16 FE14 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V  17 FE72 Offset Differential Unbuffered Internal 1.0 V  18 FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  19 FE75 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  19 FE75 Offset Differential Unbuffered Internal 1.0 V  10 FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V  10 FE16 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  11 FE17 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  12 FE75 Offset Differential Unbuffered Internal 1.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0A        | FE0A    | Gain High Byte          | Single-Ended Unbuffered  | Internal 1.0 V |

| OC FEOC Gain High Byte Single-Ended Unbuffered External 2.0 V  DD FEOD Gain Low Byte Single-Ended Unbuffered External 2.0 V  FEOF Gain High Byte Single-Ended 1x Buffered Internal 2.0 V  FEOF Gain Low Byte Single-Ended 1x Buffered Internal 2.0 V  FEOF Gain Low Byte Single-Ended 1x Buffered Internal 2.0 V  FEOF Gain Low Byte Single-Ended 1x Buffered External 2.0 V  GC FEGC Offset Single-Ended 1x Buffered External 2.0 V  DF FEOF Gain High Byte Single-Ended 1x Buffered External 2.0 V  GF FEOF Gain Low Byte Single-Ended 1x Buffered External 2.0 V  FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V  FE11 Gain Low Byte Single-Ended 1x Buffered Internal 2.0 V  FEOF FEOF Offset Differential Unbuffered Internal 2.0 V  FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V  FE13 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V  FE30 Negative Gain High Byte Differential Unbuffered Internal 2.0 V  FE31 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V  FE72 Offset Differential Unbuffered Internal 1.0 V  FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  FE15 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  FE15 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V  FE75 Offset Differential Unbuffered Internal 1.0 V  FE75 Offset Differential Unbuffered Internal 1.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0B        | FE0B    | Gain Low Byte           | Single-Ended Unbuffered  | Internal 1.0 V |

| OD FEOD Gain Low Byte Single-Ended Unbuffered External 2.0 V 69 FE69 Offset Single-Ended 1x Buffered Internal 2.0 V 0E FEOE Gain High Byte Single-Ended 1x Buffered Internal 2.0 V 0F FEOF Gain Low Byte Single-Ended 1x Buffered Internal 2.0 V 0F FE6C Offset Single-Ended 1x Buffered External 2.0 V 10 FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V 11 FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V 12 FE6C Offset Differential Unbuffered Internal 2.0 V 13 FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V 14 FE31 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V 15 FE70 Offset Differential Unbuffered Internal 2.0 V 16 FE71 Negative Gain High Byte Differential Unbuffered Internal 2.0 V 17 FE71 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V 18 FE71 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V 19 FE72 Offset Differential Unbuffered Internal 2.0 V 19 FE72 Offset Differential Unbuffered Internal 1.0 V 19 FE73 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE73 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE75 Offset Differential Unbuffered Internal 1.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66        | FE66    | Offset                  | Single-Ended Unbuffered  | External 2.0 V |

| FE69 Offset Single-Ended 1x Buffered Internal 2.0 V  DE FE0E Gain High Byte Single-Ended 1x Buffered Internal 2.0 V  DF FE0F Gain Low Byte Single-Ended 1x Buffered Internal 2.0 V  DF FE6C Offset Single-Ended 1x Buffered External 2.0 V  DF FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V  DF FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V  DF FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V  DF FE6F Offset Differential Unbuffered Internal 2.0 V  DF FE6F Offset Differential Unbuffered Internal 2.0 V  DF FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V  DF FE30 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V  DF FE72 Offset Differential Unbuffered Internal 2.0 V  DF FE72 Offset Differential Unbuffered Internal 1.0 V  DF FE15 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  DF FE31 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  DF FE73 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  DF FE75 Offset Differential Unbuffered Internal 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0C        | FE0C    | Gain High Byte          | Single-Ended Unbuffered  | External 2.0 V |

| OE FE0E Gain High Byte Single-Ended 1x Buffered Internal 2.0 V OF FE0F Gain Low Byte Single-Ended 1x Buffered Internal 2.0 V 6C FE6C Offset Single-Ended 1x Buffered External 2.0 V 10 FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V 11 FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V 12 FE6F Offset Differential Unbuffered Internal 2.0 V 13 FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V 14 FE30 Negative Gain High Byte Differential Unbuffered Internal 2.0 V 15 FE70 Offset Differential Unbuffered Internal 2.0 V 16 FE71 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V 17 FE72 Offset Differential Unbuffered Internal 2.0 V 18 FE73 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE70 Offset Differential Unbuffered Internal 1.0 V 19 FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE31 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE15 Positive Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE30 Offset Differential Unbuffered Internal 1.0 V 19 FE30 Offset Differential Unbuffered Internal 1.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0D        | FE0D    | Gain Low Byte           | Single-Ended Unbuffered  | External 2.0 V |

| OF FE0F Gain Low Byte Single-Ended 1x Buffered External 2.0 V 6C FE6C Offset Single-Ended 1x Buffered External 2.0 V 10 FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V 11 FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V 12 FE6F Offset Differential Unbuffered Internal 2.0 V 13 FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V 14 FE30 Negative Gain High Byte Differential Unbuffered Internal 2.0 V 15 FE70 Offset Differential Unbuffered Internal 2.0 V 16 FE71 Positive Gain High Byte Differential Unbuffered Internal 2.0 V 17 FE30 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V 18 FE31 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V 19 FE72 Offset Differential Unbuffered Internal 1.0 V 19 FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE31 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 69        | FE69    | Offset                  | Single-Ended 1x Buffered | Internal 2.0 V |

| FE6C Offset Single-Ended 1x Buffered External 2.0 V  FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V  FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V  FE6F Offset Differential Unbuffered Internal 2.0 V  FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V  FE13 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V  Negative Gain High Byte Differential Unbuffered Internal 2.0 V  RE30 Negative Gain High Byte Differential Unbuffered Internal 2.0 V  FE7 Offset Differential Unbuffered Internal 2.0 V  FE7 Diffset Differential Unbuffered Internal 1.0 V  FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V  FE7 FE7 Offset Differential Unbuffered Internal 1.0 V  FE7 FE7 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  FE30 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  FE7 FE7 Offset Differential Unbuffered Internal 1.0 V  FE7 FE7 Offset Differential Unbuffered Internal 1.0 V  FE7 FE7 Offset Differential Unbuffered Internal 1.0 V  FE7 FE75 Offset Differential Unbuffered External 2.0 V  FE7 FE75 Offset Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0E        | FE0E    | Gain High Byte          | Single-Ended 1x Buffered | Internal 2.0 V |

| FE10 Gain High Byte Single-Ended 1x Buffered External 2.0 V  FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V  FE6F Offset Differential Unbuffered Internal 2.0 V  FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V  FE13 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V  Negative Gain High Byte Differential Unbuffered Internal 2.0 V  Negative Gain Low Byte Differential Unbuffered Internal 2.0 V  FE30 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V  FE31 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V  FE72 Offset Differential Unbuffered Internal 1.0 V  FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V  FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V  FE75 FE75 Offset Differential Unbuffered External 2.0 V  FE76 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0F        | FE0F    | Gain Low Byte           | Single-Ended 1x Buffered | Internal 2.0 V |

| FE11 Gain Low Byte Single-Ended 1x Buffered External 2.0 V  FE6F Offset Differential Unbuffered Internal 2.0 V  FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V  RE13 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V  Negative Gain High Byte Differential Unbuffered Internal 2.0 V  RE30 Negative Gain High Byte Differential Unbuffered Internal 2.0 V  FE31 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V  FE72 Offset Differential Unbuffered Internal 1.0 V  FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V  FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  RE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V  FE75 Offset Differential Unbuffered Internal 1.0 V  FE75 Offset Differential Unbuffered External 2.0 V  Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6C        | FE6C    | Offset                  | Single-Ended 1x Buffered | External 2.0 V |

| FE6F Offset Differential Unbuffered Internal 2.0 V FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V FE13 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V Negative Gain High Byte Differential Unbuffered Internal 2.0 V Negative Gain Low Byte Differential Unbuffered Internal 2.0 V FE31 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V FE72 Offset Differential Unbuffered Internal 1.0 V FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V FE34 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V FE35 Diffset Differential Unbuffered Internal 1.0 V FE75 FE75 Offset Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10        | FE10    | Gain High Byte          | Single-Ended 1x Buffered | External 2.0 V |

| 12 FE12 Positive Gain High Byte Differential Unbuffered Internal 2.0 V 13 FE13 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V 14 FE30 Negative Gain High Byte Differential Unbuffered Internal 2.0 V 15 FE72 Offset Differential Unbuffered Internal 1.0 V 16 FE15 Positive Gain High Byte Differential Unbuffered Internal 1.0 V 17 FE32 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 18 FE33 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE30 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE31 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 19 FE32 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 19 FE30 Offset Differential Unbuffered External 2.0 V 19 FE30 Positive Gain High Byte Differential Unbuffered External 2.0 V 19 FE30 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11        | FE11    | Gain Low Byte           | Single-Ended 1x Buffered | External 2.0 V |

| FE13 Positive Gain Low Byte Differential Unbuffered Internal 2.0 V Negative Gain High Byte Differential Unbuffered Internal 2.0 V Negative Gain Low Byte Differential Unbuffered Internal 2.0 V FE31 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V FE72 Offset Differential Unbuffered Internal 1.0 V FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V FE75 Offset Differential Unbuffered External 2.0 V FE76 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6F        | FE6F    | Offset                  | Differential Unbuffered  | Internal 2.0 V |

| 30 FE30 Negative Gain High Byte Differential Unbuffered Internal 2.0 V 31 FE31 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V 72 FE72 Offset Differential Unbuffered Internal 1.0 V 14 FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V 15 FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V 32 FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 33 FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 75 FE75 Offset Differential Unbuffered External 2.0 V 16 FE16 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12        | FE12    | Positive Gain High Byte | Differential Unbuffered  | Internal 2.0 V |

| 31 FE31 Negative Gain Low Byte Differential Unbuffered Internal 2.0 V 72 FE72 Offset Differential Unbuffered Internal 1.0 V 14 FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V 15 FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V 32 FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 33 FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 75 FE75 Offset Differential Unbuffered External 2.0 V 16 FE16 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13        | FE13    | Positive Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V |

| FE72 Offset Differential Unbuffered Internal 1.0 V  FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V  FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V  RE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  RE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V  FE75 Offset Differential Unbuffered External 2.0 V  FE76 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30        | FE30    | Negative Gain High Byte | Differential Unbuffered  | Internal 2.0 V |

| 14 FE14 Positive Gain High Byte Differential Unbuffered Internal 1.0 V 15 FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V 32 FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 33 FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 75 FE75 Offset Differential Unbuffered External 2.0 V 16 FE16 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31        | FE31    | Negative Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V |

| 15 FE15 Positive Gain Low Byte Differential Unbuffered Internal 1.0 V  32 FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V  33 FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V  75 FE75 Offset Differential Unbuffered External 2.0 V  16 FE16 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 72        | FE72    | Offset                  | Differential Unbuffered  | Internal 1.0 V |

| 32 FE32 Negative Gain High Byte Differential Unbuffered Internal 1.0 V 33 FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 75 FE75 Offset Differential Unbuffered External 2.0 V 16 FE16 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14        | FE14    | Positive Gain High Byte | Differential Unbuffered  | Internal 1.0 V |

| 33 FE33 Negative Gain Low Byte Differential Unbuffered Internal 1.0 V 75 FE75 Offset Differential Unbuffered External 2.0 V 16 FE16 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15        | FE15    | Positive Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V |

| 75 FE75 Offset Differential Unbuffered External 2.0 V 16 FE16 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32        | FE32    | Negative Gain High Byte | Differential Unbuffered  | Internal 1.0 V |

| 16 FE16 Positive Gain High Byte Differential Unbuffered External 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33        | FE33    | Negative Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V |