Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 64 x 8                                                    |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            |                                                           |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f021apj020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Low-Power Operational Amplifier

The optional low-power operational amplifier (LPO) is a general-purpose amplifier primarily targeted for current sense applications. The LPO output may be routed internally to the ADC or externally to a pin.

## **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

## **Temperature Sensor**

The optional temperature sensor produces an analog output proportional to the device temperature. This signal can be sent to either the ADC or the analog comparator.

## **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

# **External Crystal Oscillator**

The crystal oscillator circuit provides highly accurate clock frequencies with the use of an external crystal, ceramic resonator or RC network.

## Low Voltage Detector

The low voltage detector (LVD) is able to generate an interrupt when the supply voltage drops below a user-programmable level. The LVD is available on 8-pin devices only.

## **On-Chip Debugger**

The Z8 Encore! XP<sup>®</sup> F082A Series products feature an integrated on-chip debugger (OCD) accessed via a single-pin interface. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints, and executing code.

# **Reset Sources**

Table 9 lists the possible sources of a system reset.

| Operating Mode       | Reset Source                                             | Special Conditions                                                                            |  |  |

|----------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|

| NORMAL or HALT modes | Power-On Reset/Voltage<br>Brownout                       | Reset delay begins after supply voltage exceeds POR level.                                    |  |  |

|                      | Watchdog Timer time-out when configured for Reset        | None.                                                                                         |  |  |

|                      | RESET pin assertion                                      | All reset pulses less than three system cloc in width are ignored.                            |  |  |

|                      | On-Chip Debugger initiated Reset<br>(OCDCTL[0] set to 1) | System Reset, except the On-Chip Debugger is unaffected by the reset.                         |  |  |

| STOP mode            | Power-On Reset/Voltage<br>Brownout                       | Reset delay begins after supply voltage exceeds POR level.                                    |  |  |

|                      | RESET pin assertion                                      | All reset pulses less than the specified analog delay are ignored. See Table 131 on page 229. |  |  |

|                      | DBG pin driven Low                                       | None.                                                                                         |  |  |

## Table 9. Reset Sources and Resulting Reset Type

# **Power-On Reset**

Z8 Encore! XP F082A Series devices contain an internal Power-On Reset circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the device is held in the Reset state until the POR Counter has timed out. If the crystal oscillator is enabled by the option bits, this timeout is longer.

After the Z8 Encore! XP F082A Series device exits the Power-On Reset state, the eZ8 CPU fetches the Reset vector. Following Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) register is set to 1.

Figure 5 displays Power-On Reset operation. See Electrical Characteristics on page 221 for the POR threshold voltage ( $V_{POR}$ ).

# Architecture

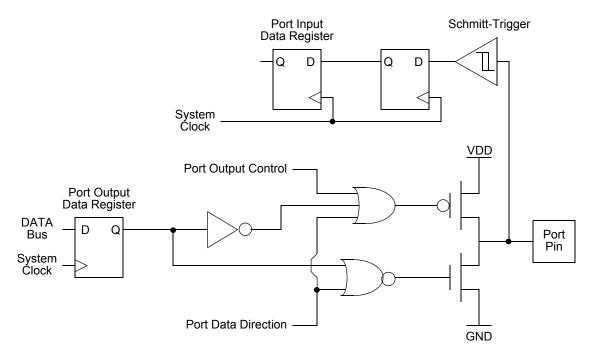

Figure 7 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

## Figure 7. GPIO Port Pin Block Diagram

# **GPIO Alternate Functions**

Many of the GPIO port pins can be used for general-purpose I/O and access to on-chip peripheral functions such as the timers and serial communication devices. The Port A–D Alternate Function sub-registers configure these pins for either General-Purpose I/O or alternate function operation. When a pin is configured for alternate function, control of the port pin direction (input/output) is passed from the Port A–D Data Direction registers to the alternate function assigned to this pin. Table 14 on page 41 lists the alternate functions possible with each port pin. For those pins with more one alternate function, the alternate function is defined through Alternate Function Sets sub-registers AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, those pins function as input and output for the crystal oscillator.

zilog /

tions as a GPIO pin. If it is not present, the debug feature is disabled until/unless another reset event occurs. For more details, see On-Chip Debugger on page 173.

# **Crystal Oscillator Override**

For systems using a crystal oscillator, PA0 and PA1 are used to connect the crystal. When the crystal oscillator is enabled (see Oscillator Control Register Definitions on page 190), the GPIO settings are overridden and PA0 and PA1 are disabled.

# **5 V Tolerance**

All six I/O pins on the 8-pin devices are 5 V-tolerant, unless the programmable pull-ups are enabled. If the pull-ups are enabled and inputs higher than  $V_{DD}$  are applied to these parts, excessive current flows through those pull-up devices and can damage the chip.

**Note:** In the 20- and 28-pin versions of this device, any pin which shares functionality with an ADC, crystal or comparator port is not 5 V-tolerant, including PA[1:0], PB[5:0] and PC[2:0]. All other signal pins are 5 V-tolerant, and can safely handle inputs higher than  $V_{DD}$  except when the programmable pull-ups are enabled.

# **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control (OSCCTL) register (see Oscillator Control Register Definitions on page 190) such that the external oscillator is selected as the system clock. For 8-pin devices use PA1 instead of PB3.

# Table 31. LED Drive Level Low Register (LEDLVLL)

| BITS  | 7            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|--------------|-----|-----|-----|-----|-----|-----|-----|--|

| FIELD | LEDLVLL[7:0] |     |     |     |     |     |     |     |  |

| RESET | 0            | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W   | R/W          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR  |              |     |     | F8  | 4H  |     |     |     |  |

LEDLVLL[7:0]—LED Level Low Bit

{LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin.

00 = 3 mA01 = 7 mA10 = 13 mA

11 = 20 mA

# 63

## Table 37. IRQ0 Enable High Bit Register (IRQ0ENH)

| BITS  | 7        | 6     | 5     | 4      | 3      | 2        | 1        | 0      |  |  |  |

|-------|----------|-------|-------|--------|--------|----------|----------|--------|--|--|--|

| FIELD | Reserved | T1ENH | T0ENH | U0RENH | U0TENH | Reserved | Reserved | ADCENH |  |  |  |

| RESET | 0        | 0     | 0     | 0      | 0      | 0        | 0        | 0      |  |  |  |

| R/W   | R/W      | R/W   | R/W   | R/W    | R/W    | R/W      | R/W      | R/W    |  |  |  |

| ADDR  |          | FC1H  |       |        |        |          |          |        |  |  |  |

Reserved—Must be 0.

T1ENH—Timer 1 Interrupt Request Enable High Bit T0ENH—Timer 0 Interrupt Request Enable High Bit U0RENH—UART 0 Receive Interrupt Request Enable High Bit U0TENH—UART 0 Transmit Interrupt Request Enable High Bit ADCENH—ADC Interrupt Request Enable High Bit

#### Table 38. IRQ0 Enable Low Bit Register (IRQ0ENL)

| BITS  | 7        | 6     | 5            | 4             | 3             | 2        | 1        | 0      |

|-------|----------|-------|--------------|---------------|---------------|----------|----------|--------|

| FIELD | Reserved | T1ENL | <b>T0ENL</b> | <b>U0RENL</b> | <b>U0TENL</b> | Reserved | Reserved | ADCENL |

| RESET | 0        | 0     | 0            | 0             | 0             | 0        | 0        | 0      |

| R/W   | R        | R/W   | R/W          | R/W           | R/W           | R        | R        | R/W    |

| ADDR  |          |       |              | FC            | 2H            |          |          |        |

Reserved—Must be 0.

T1ENL—Timer 1 Interrupt Request Enable Low Bit T0ENL—Timer 0 Interrupt Request Enable Low Bit U0RENL—UART 0 Receive Interrupt Request Enable Low Bit U0TENL—UART 0 Transmit Interrupt Request Enable Low Bit ADCENL—ADC Interrupt Request Enable Low Bit

# **IRQ1 Enable High and Low Bit Registers**

Table 39 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers (Table 40 and Table 41) form a priority encoded enabling for interrupts in the Interrupt Request 1 register.

#### Table 39. IRQ1 Enable and Priority Encoding

| IRQ1ENH[x] | IRQ1ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Medium      |

| 1          | 1          | Level 3  | High        |

|            |            |          |             |

where x indicates the register bits from 0–7.

#### Table 40. IRQ1 Enable High Bit Register (IRQ1ENH)

| BITS  | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |  |  |

|-------|---------|---------|--------|--------|---------------|--------|--------|--------|--|--|

| FIELD | PA7VENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |  |  |

| RESET | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |  |  |

| R/W   | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |  |  |

| ADDR  |         | FC4H    |        |        |               |        |        |        |  |  |

PA7VENH—Port A Bit[7] or LVD Interrupt Request Enable High Bit PA6CENH—Port A Bit[7] or Comparator Interrupt Request Enable High Bit PAxENH—Port A Bit[x] Interrupt Request Enable High Bit

See Shared Interrupt Select (IRQSS) register for selection of either the LVD or the comparator as the interrupt source.

#### Table 41. IRQ1 Enable Low Bit Register (IRQ1ENL)

| BITS  | 7       | 6       | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |

|-------|---------|---------|--------|--------|--------|--------|--------|--------|--|--|--|

| FIELD | PA7VENL | PA6CENL | PA5ENL | PA4ENL | PA3ENL | PA2ENL | PA1ENL | PA0ENL |  |  |  |

| RESET | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      |  |  |  |

| R/W   | R/W     | R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |  |

| ADDR  |         | FC5H    |        |        |        |        |        |        |  |  |  |

PA7VENL—Port A Bit[7] or LVD Interrupt Request Enable Low Bit PA6CENL—Port A Bit[6] or Comparator Interrupt Request Enable Low Bit PAxENL—Port A Bit[x] Interrupt Request Enable Low Bit

# Universal Asynchronous Receiver/Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. Features of the UART include:

- 8-bit asynchronous data transfer.

- Selectable even- and odd-parity generation and checking.

- Option of one or two STOP bits.

- Separate transmit and receive interrupts.

- Framing, parity, overrun and break detection.

- Separate transmit and receive enables.

- 16-bit baud rate generator (BRG).

- Selectable MULTIPROCESSOR (9-bit) mode with three configurable interrupt schemes.

- Baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

- Driver enable (DE) output for external bus transceivers.

# Architecture

The UART consists of three primary functional blocks: transmitter, receiver, and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 on page 98 displays the UART architecture.

#### MPMD[1:0]—MULTIPROCESSOR Mode

If MULTIPROCESSOR (9-bit) mode is enabled,

00 = The UART generates an interrupt request on all received bytes (data and address).

01 = The UART generates an interrupt request only on received address bytes.

10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs.

11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register.

#### MPEN—MULTIPROCESSOR (9-bit) Enable

This bit is used to enable MULTIPROCESSOR (9-bit) mode.

0 = Disable MULTIPROCESSOR (9-bit) mode.

1 = Enable MULTIPROCESSOR (9-bit) mode.

#### MPBT—Multiprocessor Bit Transmit

This bit is applicable only when MULTIPROCESSOR (9-bit) mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.

0 = Send a 0 in the multiprocessor bit location of the data stream (data byte).

1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).

#### DEPOL—Driver Enable Polarity

0 = DE signal is Active High.

1 = DE signal is Active Low.

#### BRGCTL—Baud Rate Control

This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register.

When the UART receiver is **not** enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value 1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.

When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value. 1 = Reads from the Baud Rate High and Low Byte registers return the current BRG count value. Unlike the Timers, there is no mechanism to latch the Low Byte when the High Byte is read.

RDAIRQ—Receive Data Interrupt Enable

0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.

# **ADC Control Register Definitions**

# ADC Control Register 0

The ADC Control Register 0 (ADCCTL0) selects the analog input channel and initiates the analog-to-digital conversion. It also selects the voltage reference configuration.

Table 71. ADC Control Register 0 (ADCCTL0)

| BITS  | 7   | 6       | 5      | 4    | 3          | 2   | 1   | 0   |  |  |

|-------|-----|---------|--------|------|------------|-----|-----|-----|--|--|

| FIELD | CEN | REFSELL | REFOUT | CONT | ANAIN[3:0] |     |     |     |  |  |

| RESET | 0   | 0       | 0      | 0    | 0          | 0   | 0   | 0   |  |  |

| R/W   | R/W | R/W     | R/W    | R/W  | R/W        | R/W | R/W | R/W |  |  |

| ADDR  |     | F70H    |        |      |            |     |     |     |  |  |

#### CEN—Conversion Enable

0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion is complete.

1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.

REFSELL—Voltage Reference Level Select Low Bit; in conjunction with the High bit (REFSELH) in ADC Control/Status Register 1, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL}; note that this reference is independent of the Comparator reference.

00= Internal Reference Disabled, reference comes from external pin

01= Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

11= Reserved

REFOUT—Internal Reference Output Enable

0 = Reference buffer is disabled; Vref pin is available for GPIO or analog functions

1 = The internal ADC reference is buffered and driven out to the Vref pin

<u>/</u>

**Warning:** When the ADC is used with an external reference ({REFSELH,REFSELL}=00), the REFOUT bit must be set to 0.

## CONT

0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles (measurements of the internal temperature sensor take twice as long) 1 = Continuous conversion. ADC data updated every 256 system clock cycles after an initial 5129 clock conversion (measurements of the internal temperature sensor take twice as long)

| İ | l | 0 | g | 133 |

|---|---|---|---|-----|

|   |   |   |   | 133 |

| BITS      | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------|----------------|---|---|---|---|---|---|---|--|--|

| FIELD     | ADCDH          |   |   |   |   |   |   |   |  |  |

| RESET     | Х              | Х | Х | Х | Х | Х | Х | Х |  |  |

| R/W       | R              | R | R | R | R | R | R | R |  |  |

| ADDR      | F72H           |   |   |   |   |   |   |   |  |  |

| X = Undef | X = Undefined. |   |   |   |   |   |   |   |  |  |

#### Table 73. ADC Data High Byte Register (ADCD\_H)

ADCDH—ADC Data High Byte

This byte contains the upper eight bits of the ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the most recent conversion output is held in this register. These bits are undefined after a Reset.

# ADC Data Low Byte Register

The ADC Data Low Byte (ADCD\_L) register contains the lower bits of the ADC output as well as an overflow status bit. The output is a 13-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data Low Byte register is read-only. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

Table 74. ADC Data Low Byte Register (ADCD\_L)

| BITS      | 7              | 6 | 5     | 4    | 3   | 2 | 1 | 0 |  |

|-----------|----------------|---|-------|------|-----|---|---|---|--|

| FIELD     |                |   | ADCDL | Rese | OVF |   |   |   |  |

| RESET     | Х              | Х | Х     | Х    | Х   | Х | Х | Х |  |

| R/W       | R              | R | R     | R    | R   | R | R | R |  |

| ADDR      | F73H           |   |       |      |     |   |   |   |  |

| X = Undef | X = Undefined. |   |       |      |     |   |   |   |  |

ADCDL—ADC Data Low Bits

These bits are the least significant five bits of the 13-bits of the ADC output. These bits are undefined after a Reset.

Reserved—Must be undefined.

OVF—Overflow Status

0= A hardware overflow did not occur in the ADC for the current sample. 1= A hardware overflow did occur in the ADC for the current sample, therefore the current sample is invalid.

Assuming a compensated ADC measurement, the following equation defines the relationship between the ADC reading and the die temperature:

$T = (25/128) \times (ADC - TSCAL[11:2]) + 30$

where, T is the temperature in C; ADC is the 10-bit compensated ADC value; and TSCAL is the temperature sensor calibration value, ignoring the two least significant bits of the 12-bit value.

See Temperature Sensor Calibration Data on page 164 for the location of TSCAL.

## Calibration

The temperature sensor undergoes calibration during the manufacturing process and is maximally accurate at 30 °C. Accuracy decreases as measured temperatures move further from the calibration point.

Zilog 14

the OCD or via the Flash Controller Bypass mode are unaffected. After a bit of the Sector Protect Register has been set, it cannot be cleared except by powering down the device.

# **Byte Programming**

The Flash Memory is enabled for byte programming after unlocking the Flash Controller and successfully enabling either Mass Erase or Page Erase. When the Flash Controller is unlocked and Mass Erase is successfully completed, all Program Memory locations are available for byte programming. In contrast, when the Flash Controller is unlocked and Page Erase is successfully completed, only the locations of the selected page are available for byte programming. An erased Flash byte contains all 1's (FFH). The programming operation can only be used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from 0 to 1 requires execution of either the Page Erase or Mass Erase commands.

Byte Programming can be accomplished using the On-Chip Debugger's Write Memory command or eZ8 CPU execution of the LDC or LDCI instructions. Refer to the *eZ8 CPU User Manual* (available for download at <u>www.zilog.com</u>) for a description of the LDC and LDCI instructions. While the Flash Controller programs the Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. To exit programming mode and lock the Flash, write any value to the Flash Control register, except the Mass Erase or Page Erase commands.

**Caution:** The byte at each address of the Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs. Doing so may result in corrupted data at the target byte.

## Page Erase

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

#### Mass Erase

The Flash memory can also be Mass Erased using the Flash Controller, but only by using the On-Chip Debugger. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the Mass Erase successfully enabled, writing the

185

DBGACK—Debug Acknowledge

This bit enables the debug acknowledge feature. If this bit is set to 1, the OCD sends a Debug Acknowledge character (FFH) to the host when a Breakpoint occurs.

0 = Debug Acknowledge is disabled.

1 = Debug Acknowledge is enabled.

Reserved—Must be 0.

RST—Reset

Setting this bit to 1 resets the Z8F04xA family device. The device goes through a normal Power-On Reset sequence with the exception that the On-Chip Debugger is not reset. This bit is automatically cleared to 0 at the end of reset.

0 = No effect.

1 = Reset the Flash Read Protect Option Bit device.

# **OCD Status Register**

The OCD Status register reports status information about the current state of the debugger and the system.

#### Table 107. OCD Status Register (OCDSTAT)

| BITS  | 7   | 6    | 5      | 4        | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|-----|------|--------|----------|---|---|---|---|--|--|--|--|

| FIELD | DBG | HALT | FRPENB | Reserved |   |   |   |   |  |  |  |  |

| RESET | 0   | 0    | 0      | 0        | 0 | 0 | 0 | 0 |  |  |  |  |

| R/W   | R   | R    | R      | R        | R | R | R | R |  |  |  |  |

DBG—Debug Status

0 = NORMAL mode

1 = DEBUG mode

HALT—HALT Mode

0 =Not in HALT mode

1 =In HALT mode

FRPENB—Flash Read Protect Option Bit Enable

0 = FRP bit enabled, that allows disabling of many OCD commands

1 = FRP bit has no effect

Reserved-Must be 0

189

When selecting a new clock source, the system clock oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If SOFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the OSCCTL register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it may be appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

# **Clock Failure Detection and Recovery**

#### System Clock Oscillator Failure

The Z8F04xA family devices can generate non-maskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function (see Watchdog Timer on page 91).

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below 1 kHz  $\pm$ 50%. If an external signal is selected as the system oscillator, it is possible that a very slow but non-failing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (SOFEN must be deasserted in the OSCCTL register).

#### Watchdog Timer Failure

In the event of a Watchdog Timer oscillator failure, a similar non-maskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the system clock oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while looking for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

220

#### 22

## Table 126. Absolute Maximum Ratings (Continued)

| Parameter                                        | Minimum Maximum | Units | Notes |  |

|--------------------------------------------------|-----------------|-------|-------|--|

| 28-pin Packages Maximum Ratings at 0 °C to 70 °C |                 |       |       |  |

| Total power dissipation                          | 450             | mW    |       |  |

| Maximum current into $V_{DD}$ or out of $V_{SS}$ | 125             | mA    |       |  |

|                                                  |                 |       |       |  |

Operating temperature is specified in DC Characteristics.

This voltage applies to all pins except the following: V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1). On the 8-pin packages, this applies to all pins but V<sub>DD</sub>.

2. This voltage applies to pins on the 20-/28-pin packages supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1).

# **DC Characteristics**

Table 127 lists the DC characteristics of the Z8 Encore!  $XP^{\mathbb{R}}$  F082A Series products. All voltages are referenced to  $V_{SS}$ , the primary system ground.

| Table 127. DC Characteristics |  |

|-------------------------------|--|

|-------------------------------|--|

|                  |                              |                     | 40 °C to +<br>therwise | 105 °C<br>specified) |       |                                                                                                                                                              |  |  |

|------------------|------------------------------|---------------------|------------------------|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol Parameter |                              | Minimum             | Typical                | Maximum              | Units | Conditions                                                                                                                                                   |  |  |

| V <sub>DD</sub>  | Supply Voltage               | 2.7                 | _                      | 3.6                  | V     |                                                                                                                                                              |  |  |

| V <sub>IL1</sub> | Low Level Input<br>Voltage   | -0.3                | _                      | 0.3*V <sub>DD</sub>  | V     |                                                                                                                                                              |  |  |

| V <sub>IH1</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | 5.5                  | V     | For all input pins without analog<br>or oscillator function. For all<br>signal pins on the 8-pin devices.<br>Programmable pull-ups must<br>also be disabled. |  |  |

| V <sub>IH2</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | V <sub>DD</sub> +0.3 | V     | For those pins with analog or<br>oscillator function (20-/28-pin<br>devices only), or when<br>programmable pull-ups are<br>enabled.                          |  |  |

| V <sub>OL1</sub> | Low Level Output<br>Voltage  | -                   | -                      | 0.4                  | V     | I <sub>OL</sub> = 2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                               |  |  |

| V <sub>OH1</sub> | High Level Output<br>Voltage | 2.4                 | -                      | _                    | V     | I <sub>OH</sub> = -2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                              |  |  |

232

|                |                                      | $T_A =$ | = 3.0 V to<br>0 °C to +<br>otherwis | 70 °C                |                           | Conditions                                                                                                                                                                                                                     |  |  |

|----------------|--------------------------------------|---------|-------------------------------------|----------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol         | Parameter                            | Minimum | Typical                             | Maximum              | Units                     |                                                                                                                                                                                                                                |  |  |

|                | Single-Shot Conversion<br>Time       | -       | 5129                                | -                    | System<br>clock<br>cycles | All measurements but temperature sensor                                                                                                                                                                                        |  |  |

|                |                                      |         | 10258                               |                      |                           | Temperature sensor<br>measurement                                                                                                                                                                                              |  |  |

|                | Continuous Conversion<br>Time        | _       | 256                                 | _                    | System<br>clock<br>cycles | All measurements but temperature sensor                                                                                                                                                                                        |  |  |

|                |                                      |         | 512                                 |                      |                           | Temperature sensor<br>measurement                                                                                                                                                                                              |  |  |

|                | Signal Input Bandwidth               | _       | 10                                  |                      | kHz                       | As defined by -3 dB point                                                                                                                                                                                                      |  |  |

| R <sub>S</sub> | Analog Source Impedance <sup>4</sup> | _       | _                                   | 10                   | kΩ                        | In unbuffered mode                                                                                                                                                                                                             |  |  |

|                |                                      |         |                                     | 500                  | kΩ                        | In buffered modes                                                                                                                                                                                                              |  |  |

| Zin            | Input Impedance                      | -       | 150                                 |                      | kΩ                        | In unbuffered mode at 20 $\rm MHz^5$                                                                                                                                                                                           |  |  |

|                |                                      | 10      | _                                   |                      | MΩ                        | In buffered modes                                                                                                                                                                                                              |  |  |

| Vin            | Input Voltage Range                  | 0       |                                     | V <sub>DD</sub>      | V                         | Unbuffered Mode                                                                                                                                                                                                                |  |  |

|                |                                      | 0.3     |                                     | V <sub>DD</sub> -1.1 | V                         | Buffered Modes                                                                                                                                                                                                                 |  |  |

|                |                                      |         |                                     | •                    | Note:                     | These values define the<br>range over which the<br>ADC performs within<br>spec; exceeding these<br>values does not cause<br>damage or instability; see<br>DC Characteristics on<br>page 222 for absolute pin<br>voltage limits |  |  |

#### Table 135. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

#### Notes

- 1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

- 2. Devices are factory calibrated at  $V_{DD}$  = 3.3 V and  $T_A$  = +30 °C, so the ADC is maximally accurate under these conditions.

- 3. LSBs are defined assuming 10-bit resolution.

- 4. This is the maximum recommended resistance seen by the ADC input pin.

- 5. The input impedance is inversely proportional to the system clock frequency.

| ג<br>ש<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק | Flash<br>Serie | S Devel                                           | SQ<br>NN<br>Opmen | t Kit | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description |  |

|-------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------|-------------------|-------|------------|---------------------|---------------------|----------------|------------|--------------------|-------------|--|

| Z8F08A28100KITG                                                                                       | •              |                                                   |                   |       |            |                     |                     |                |            |                    |             |  |

| Z8F04A28100KITG                                                                                       |                | Z8 Encore! XP F042A Series 28-Pin Development Kit |                   |       |            |                     |                     |                |            |                    |             |  |

| Z8F04A08100KITG                                                                                       |                | Z8 Encore! XP F042A Series 8-Pin Development Kit  |                   |       |            |                     |                     |                |            |                    |             |  |

| ZUSBSC00100ZACG                                                                                       |                | USB Smart Cable Accessory Kit                     |                   |       |            |                     |                     |                |            |                    |             |  |

| ZUSBOPTSC01ZACG                                                                                       |                | USB Opto-Isolated Smart Cable Accessory Kit       |                   |       |            |                     |                     |                |            |                    |             |  |

| ZENETSC0100ZACG                                                                                       |                | Ethernet Smart Cable Accessory Kit                |                   |       |            |                     |                     |                |            |                    |             |  |

|                                                                                                       |                |                                                   |                   |       |            |                     |                     |                |            |                    |             |  |