Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 64 x 8                                                    |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-VDFN Exposed Pad                                        |

| Supplier Device Package    | 8-QFN (5x6)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f021aqb020sc |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

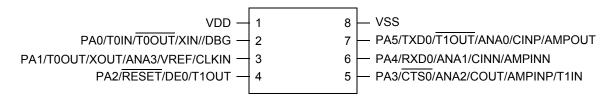

Figure 2. Z8F08xA, Z8F04xA, Z8F02xA, and Z8F01xA in 8-Pin SOIC, QFN/MLF-S, or PDIP Package

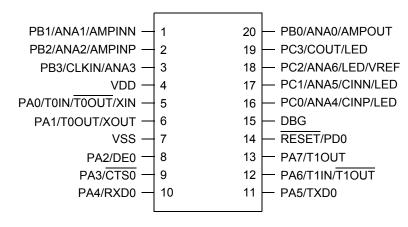

Figure 3. Z8F08xA, Z8F04xA, Z8F02xA, and Z8F01xA in 20-Pin SOIC, SSOP or PDIP Package

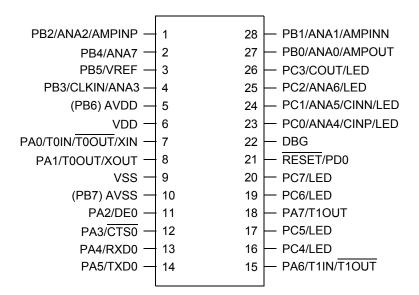

Figure 4. Z8F08xA, Z8F04xA, Z8F02xA, and Z8F01xA in 28-Pin SOIC, SSOP or PDIP Package

## **Signal Descriptions**

Table 2 describes the Z8 Encore! XP F082A Series signals. See Pin Configurations on page 9 to determine the signals available for the specific package styles.

| Signal Mnemonic                                     | I/O     | Description                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose I/                                  | O Ports | A–D                                                                                                                                                                                                                                                                                                     |

| PA[7:0]                                             | I/O     | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| PB[7:0]                                             | I/O     | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |

| PC[7:0]                                             | I/O     | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| PD[0]                                               | I/O     | Port D. This pin is used for general-purpose output only.                                                                                                                                                                                                                                               |

| Note: PB6 and PB7 ar<br>replaced by AV <sub>E</sub> |         | vailable in 28-pin packages without ADC. In 28-pin packages with ADC, they are $V_{\rm SS}.$                                                                                                                                                                                                            |

| UART Controllers                                    |         |                                                                                                                                                                                                                                                                                                         |

| TXD0                                                | 0       | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |

| RXD0                                                | Ι       | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |

| CTS0                                                | Ι       | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |

| DE                                                  | 0       | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 register. The DE signal may be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |

| Timers                                              |         |                                                                                                                                                                                                                                                                                                         |

| T0OUT/T1OUT                                         | 0       | Timer Output 0–1. These signals are outputs from the timers.                                                                                                                                                                                                                                            |

| T0OUT/T1OUT                                         | 0       | Timer Complement Output 0–1. These signals are output from the timers in PWM Dual Output mode.                                                                                                                                                                                                          |

| T0IN/T1IN                                           | Ι       | Timer Input 0–1. These signals are used as the capture, gating and counter inputs.                                                                                                                                                                                                                      |

| Comparator                                          |         |                                                                                                                                                                                                                                                                                                         |

| CINP/CINN                                           | Ι       | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |

| COUT                                                | 0       | Comparator Output.                                                                                                                                                                                                                                                                                      |

#### Table 2. Signal Descriptions

#### Table 2. Signal Descriptions (Continued)

| Signal Mnemonic     | I/O     | Description                                                                                                                                                                                                                                                                   |

|---------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog              |         |                                                                                                                                                                                                                                                                               |

| ANA[7:0]            | I       | Analog Port. These signals are used as inputs to the analog-to-digital converter (ADC).                                                                                                                                                                                       |

| VREF                | I/O     | Analog-to-digital converter reference voltage input, or buffered output for internal reference.                                                                                                                                                                               |

| Low-Power Operation | onal An | nplifier (LPO)                                                                                                                                                                                                                                                                |

| AMPINP/AMPINN       | Ι       | LPO inputs. If enabled, these pins drive the positive and negative amplifier inputs respectively.                                                                                                                                                                             |

| AMPOUT              | 0       | LPO output. If enabled, this pin is driven by the on-chip LPO.                                                                                                                                                                                                                |

| Oscillators         |         |                                                                                                                                                                                                                                                                               |

| XIN                 | I       | External Crystal Input. This is the input pin to the crystal oscillator. A crystal can be connected between it and the <b>XOUT</b> pin to form the oscillator. In addition, this pin is used with external RC networks or external clock drivers to provide the system clock. |

| XOUT                | 0       | External Crystal Output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the <b>XIN</b> pin to form the oscillator.                                                                                                               |

| Clock Input         |         |                                                                                                                                                                                                                                                                               |

| CLKIN               | I       | Clock Input Signal. This pin may be used to input a TTL-level signal to be used as the system clock.                                                                                                                                                                          |

| LED Drivers         |         |                                                                                                                                                                                                                                                                               |

| LED                 | 0       | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                                                                                   |

| On-Chip Debugger    |         |                                                                                                                                                                                                                                                                               |

| DBG                 | I/O     | Debug. This signal is the control and data input and output to and from the On-Chip Debugger.                                                                                                                                                                                 |

|                     |         | <b>Caution:</b> The DBG pin is open-drain and requires a pull-up resistor to ensure proper operation.                                                                                                                                                                         |

| Reset               |         |                                                                                                                                                                                                                                                                               |

| RESET               | I/O     | RESET. Generates a Reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin low when in reset. This pin is open-drain and features an enabled internal pull-up resistor.                                                         |

12

#### Table 2. Signal Descriptions (Continued)

| Signal Mnemonic  | I/O      | Description                                                                       |

|------------------|----------|-----------------------------------------------------------------------------------|

| Power Supply     |          |                                                                                   |

| V <sub>DD</sub>  | Ι        | Digital Power Supply.                                                             |

| AV <sub>DD</sub> | Ι        | Analog Power Supply.                                                              |

| V <sub>SS</sub>  | I        | Digital Ground.                                                                   |

| AV <sub>SS</sub> | Ι        | Analog Ground.                                                                    |

| Note: The AV     | Vee siar | nals are available only in 28-pin packages with ADC. They are replaced by PB6 and |

**Note:** The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

## **Pin Characteristics**

Table 3 describes the characteristics for each pin available on the Z8 Encore! XP F082A Series 20- and 28-pin devices. Data in Table 3 is sorted alphabetically by the pin symbol mnemonic.

Table 4 on page 14 provides detailed information about the characteristics for each pin available on the Z8 Encore! XP F082A Series 8-pin devices.

Note:

All six I/O pins on the 8-pin packages are 5 V-tolerant (unless the pull-up devices are enabled). The column in Table 3 below describes 5 V-tolerance for the 20- and 28-pin packages only.

#### Table 3. Pin Characteristics (20- and 28-pin Devices)

| Symbol<br>Mnemonic | Direction | Reset<br>Direction | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal Pull-<br>up<br>or Pull-down | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output | 5 V<br>Tolerance                        |

|--------------------|-----------|--------------------|---------------------------------------|--------------------|--------------------------------------|------------------------------|----------------------|-----------------------------------------|

| AVDD               | N/A       | N/A                | N/A                                   | N/A                | N/A                                  | N/A                          | N/A                  | N/A                                     |

| AVSS               | N/A       | N/A                | N/A                                   | N/A                | N/A                                  | N/A                          | N/A                  | NA                                      |

| DBG                | I/O       | I                  | N/A                                   | Yes                | Yes                                  | Yes                          | Yes                  | No                                      |

| PA[7:0]            | I/O       | I                  | N/A                                   | Yes                | Programmable<br>Pull-up              | Yes                          | Yes,<br>Programmable | PA[7:2]<br>unless<br>pullups<br>enabled |

| PB[7:0]            | I/O       | I                  | N/A                                   | Yes                | Programmable<br>Pull-up              | Yes                          | Yes,<br>Programmable | PB[7:6]<br>unless<br>pullups<br>enabled |

## **Address Space**

The eZ8 CPU can access the following three distinct address spaces:

- 1. The Register File contains addresses for the general-purpose registers and the eZ8 CPU, peripheral, and general-purpose I/O port control registers.

- 2. The Program Memory contains addresses for all memory locations having executable code and/or data.

- 3. The Data Memory contains addresses for all memory locations that contain data only.

These three address spaces are covered briefly in the following subsections. For more information on eZ8 CPU and its address space, refer to eZ8 CPU Core User Manual (UM0128) available for download at www.zilog.com.

## **Register File**

The Register File address space in the Z8 Encore!<sup>®</sup> MCU is 4 KB (4096 bytes). The Register File is composed of two sections: control registers and general-purpose registers. When instructions are executed, registers defined as sources are read, and registers defined as destinations are written. The architecture of the eZ8 CPU allows all general-purpose registers to function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

The upper 256 bytes of the 4 KB Register File address space are reserved for control of the eZ8 CPU, the on-chip peripherals, and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256 B control register section are reserved (unavailable). Reading from a reserved Register File address returns an undefined value. Writing to reserved Register File addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address 000H in the Register File address space. The Z8 Encore! XP<sup>®</sup> F082A Series devices contain 256 B to 1 KB of on-chip RAM. Reading from Register File addresses outside the available RAM addresses (and not within the control register address space) returns an undefined value. Writing to these Register File addresses produces no effect.

### **Program Memory**

The eZ8 CPU supports 64 KB of Program Memory address space. The Z8 Encore! XP F082A Series devices contain 1 KB to 8 KB of on-chip Flash memory in the Program Memory address space, depending on the device. Reading from Program Memory

|                                                       | Reset Characteristics and Latency                      |            |                                                               |  |  |  |

|-------------------------------------------------------|--------------------------------------------------------|------------|---------------------------------------------------------------|--|--|--|

| Reset Type                                            | Control Registers                                      | eZ8<br>CPU | Reset Latency (Delay)                                         |  |  |  |

| System Reset                                          | Reset (as applicable)                                  | Reset      | 66 Internal Precision Oscillator Cycles                       |  |  |  |

| System Reset with Crystal Oscillator Enabled          | Reset (as applicable)                                  | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |

| Stop Mode Recovery                                    | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |  |

| Stop Mode Recovery with<br>Crystal Oscillator Enabled | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |

#### Table 8. Reset and Stop Mode Recovery Characteristics and Latency

During a System Reset or Stop Mode Recovery, the Internal Precision Oscillator requires 4  $\mu$ s to start up. Then the Z8 Encore! XP F082A Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset (POR), this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled, except PD0 (or PA2 on 8-pin devices) which is shared with the reset pin. On reset, the PD0 is configured as a bidirectional open-drain reset. The pin is internally driven low during port reset, after which the user code may reconfigure this pin as a general purpose output.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

As the control registers are re-initialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

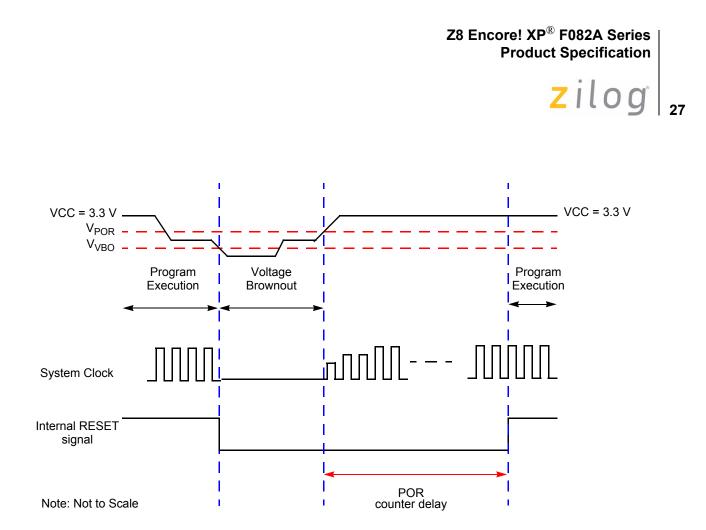

Figure 6. Voltage Brownout Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a Power-On Reset after recovering from a VBO condition.

#### Watchdog Timer Reset

If the device is in NORMAL or HALT mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash Option Bit is programmed to 1. This is the unprogrammed state of the WDT\_RES Flash Option Bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT bit in the Reset Status (RSTSTAT) register is set to signify that the reset was initiated by the Watchdog Timer.

#### External Reset Input

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system clock and reset signals, the required reset duration may be as short as three clock periods

Zilog <sub>42</sub>

| Port   | Pin | Mnemonic    | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------|--------------------------------|-----------------------------------------|

| Port B | PB0 | Reserved    |                                | AFS1[0]: 0                              |

|        |     | ANA0/AMPOUT | ADC Analog Input/LPO Output    | AFS1[0]: 1                              |

|        | PB1 | Reserved    |                                | AFS1[1]: 0                              |

|        |     | ANA1/AMPINN | ADC Analog Input/LPO Input (N) | AFS1[1]: 1                              |

|        | PB2 | Reserved    |                                | AFS1[2]: 0                              |

|        |     | ANA2/AMPINP | ADC Analog Input/LPO Input (P) | AFS1[2]: 1                              |

|        |     | CLKIN       | External Clock Input           | AFS1[3]: 0                              |

|        |     | ANA3        | ADC Analog Input               | AFS1[3]: 1                              |

|        | PB4 | Reserved    |                                | AFS1[4]: 0                              |

|        |     | ANA7        | ADC Analog Input               | AFS1[4]: 1                              |

|        | PB5 | Reserved    |                                | AFS1[5]: 0                              |

|        |     | VREF*       | ADC Voltage Reference          | AFS1[5]: 1                              |

|        | PB6 | Reserved    |                                | AFS1[6]: 0                              |

|        |     | Reserved    |                                | AFS1[6]: 1                              |

|        | PB7 | Reserved    |                                | AFS1[7]: 0                              |

|        |     | Reserved    |                                | AFS1[7]: 1                              |

#### Table 14. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Note: Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set register AFS2 is not used to select the function. Also, alternate function selection as described in Port A-D Alternate Function Sub-Registers on page 47 must also be enabled.

\* VREF is available on PB5 in 28-pin products only.

## **GPIO Interrupts**

Many of the GPIO port pins can be used as interrupt sources. Some port pins can be configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). See Interrupt Controller on page 55 for more information about interrupts using the GPIO pins.

## **GPIO Control Register Definitions**

Four registers for each Port provide access to GPIO control, input data, and output data. Table 16 lists these Port registers. Use the Port A–D Address and Control registers together to provide access to sub-registers for Port configuration and control.

| Port Register Mnemonic     | Port Register Name                                              |

|----------------------------|-----------------------------------------------------------------|

| PxADDR                     | Port A–D Address Register<br>(Selects sub-registers)            |

| PxCTL                      | Port A–D Control Register<br>(Provides access to sub-registers) |

| PxIN                       | Port A–D Input Data Register                                    |

| PxOUT                      | Port A–D Output Data Register                                   |

| Port Sub-Register Mnemonic | Port Register Name                                              |

| PxDD                       | Data Direction                                                  |

| PxAF                       | Alternate Function                                              |

| PxOC                       | Output Control (Open-Drain)                                     |

| PxHDE                      | High Drive Enable                                               |

| PxSMRE                     | Stop Mode Recovery Source Enable                                |

| PxPUE                      | Pull-up Enable                                                  |

| PxAFS1                     | Alternate Function Set 1                                        |

| PxAFS2                     | Alternate Function Set 2                                        |

|                            |                                                                 |

| Table 16. | <b>GPIO Por</b> | t Registers | and Sub-Registers |

|-----------|-----------------|-------------|-------------------|

|-----------|-----------------|-------------|-------------------|

# zilog

## **Flash Control Register Definitions**

## Flash Control Register

The Flash Controller must be unlocked using the Flash Control (FCTL) register before programming or erasing the Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control register unlocks the Flash Controller. When the Flash Controller is unlocked, the Flash memory can be enabled for Mass Erase or Page Erase by writing the appropriate enable command to the FCTL. Page Erase applies only to the active page selected in Flash Page Select register. Mass Erase is enabled only through the On-Chip Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its locked state. The Write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

| Table 78 | . Flash | Control | Register | (FCTL) |

|----------|---------|---------|----------|--------|

|----------|---------|---------|----------|--------|

| BITS  | 7 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|------|---|---|---|---|---|---|--|

| FIELD |   | FCMD |   |   |   |   |   |   |  |

| RESET | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 |  |

| R/W   | W | W    | W | W | W | W | W | W |  |

| ADDR  |   | FF8H |   |   |   |   |   |   |  |

FCMD—Flash Command

73H = First unlock command.

8CH = Second unlock command.

95H = Page Erase command (must be third command in sequence to initiate Page Erase).

63H = Mass Erase command (must be third command in sequence to initiate Mass Erase).

5EH = Enable Flash Sector Protect Register Access

## Trim Bit Address 0004H

#### Table 92. Trim Option Bits at 0004H

| BITS      | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| FIELD     | Reserved                                        |     |     |     |     |     |     |     |  |

| RESET     | U U U U U U U U                                 |     |     |     |     |     | U   |     |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR      | Information Page Memory 0024H                   |     |     |     |     |     |     |     |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |

Reserved—Altering this register may result in incorrect device operation.

## Zilog Calibration Data

## ADC Calibration Data

#### Table 93. ADC Calibration Bits

| BITS      | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

| FIELD     | ADC_CAL                                         |     |     |     |     |     |     |     |  |  |  |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |  |  |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| ADDR      | Information Page Memory 0060H–007DH             |     |     |     |     |     |     |     |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |  |

ADC\_CAL—Analog-to-Digital Converter Calibration Values

Contains factory calibrated values for ADC gain and offset compensation. Each of the ten supported modes has one byte of offset calibration and two bytes of gain calibration. These values are read by the software to compensate ADC measurements as described in Software Compensation Procedure Using Factory Calibration Data on page 126. The location of each calibration byte is provided in Table 94 on page 162.

**z**ilog<sup>°</sup>

### 166

**Table 100. Serialization Data Locations**

| Info Page Address | Memory Address | Usage                                   |  |  |  |  |  |

|-------------------|----------------|-----------------------------------------|--|--|--|--|--|

| 1C                | FE1C           | Serial Number Byte 3 (most significant) |  |  |  |  |  |

| 1D                | FE1D           | Serial Number Byte 2                    |  |  |  |  |  |

| 1E                | FE1E           | Serial Number Byte 1                    |  |  |  |  |  |

| 1F                | FE1F           | Serial Number Byte 0 (leas significant) |  |  |  |  |  |

#### **Randomized Lot Identifier**

| Table 101. | Lot Identification | Number | (RAND | LOT) |

|------------|--------------------|--------|-------|------|

|------------|--------------------|--------|-------|------|

| BITS      | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

| FIELD     | RAND_LOT                                        |     |     |     |     |     |     |     |  |  |  |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |  |  |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| ADDR      | Interspersed throughout Information Page Memory |     |     |     |     |     |     |     |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |  |

RAND LOT—Randomized Lot ID

The randomized lot ID is a 32 byte binary value that changes for each production lot.

#### Table 102. Randomized Lot ID Locations

| Info Page | Memory  |                                              |

|-----------|---------|----------------------------------------------|

| Address   | Address | Usage                                        |

| 3C        | FE3C    | Randomized Lot ID Byte 31 (most significant) |

| 3D        | FE3D    | Randomized Lot ID Byte 30                    |

| 3E        | FE3E    | Randomized Lot ID Byte 29                    |

| 3F        | FE3F    | Randomized Lot ID Byte 28                    |

| 58        | FE58    | Randomized Lot ID Byte 27                    |

| 59        | FE59    | Randomized Lot ID Byte 26                    |

| 5A        | FE5A    | Randomized Lot ID Byte 25                    |

| 5B        | FE5B    | Randomized Lot ID Byte 24                    |

## **On-Chip Debugger**

The Z8 Encore! XP<sup>®</sup> F082A Series devices contain an integrated On-Chip Debugger (OCD) that provides advanced debugging features including:

- Single pin interface.

- Reading and writing of the register file.

- Reading and writing of program and data memory.

- Setting of breakpoints and watchpoints.

- Executing eZ8 CPU instructions.

- Debug pin sharing with general-purpose input-output function to maximize pins available to the user (8-pin product only).

### Architecture

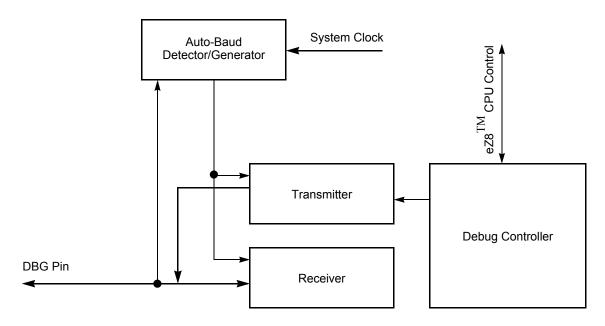

The on-chip debugger consists of four primary functional blocks: transmitter, receiver, auto-baud detector/generator, and debug controller. Figure 23 displays the architecture of the on-chip debugger.

Figure 23. On-Chip Debugger Block Diagram

zilog

196

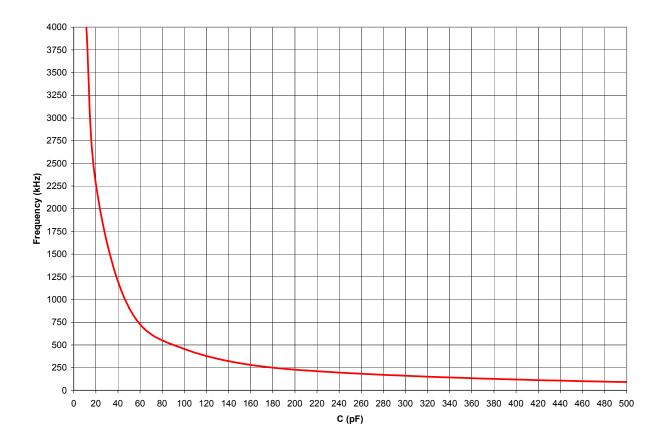

Figure 29 displays the typical (3.3 V and 25 °C) oscillator frequency as a function of the capacitor (C in pF) employed in the RC network assuming a 45 K $\Omega$  external resistor. For very small values of C, the parasitic capacitance of the oscillator XIN pin and the printed circuit board must be included in the estimation of the oscillator frequency.

It is possible to operate the RC oscillator using only the parasitic capacitance of the package and printed circuit board. To minimize sensitivity to external parasitics, external capacitance values in excess of 20 pF are recommended.

## Figure 29. Typical RC Oscillator Frequency as a Function of the External Capacitance with a 45 k $\Omega$ Resistor

**Caution**:

When using the external RC oscillator mode, the oscillator can stop oscillating if the power supply drops below 2.7 V, but before the power supply drops to the Voltage Brownout threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7 V.

204

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| ТСМ      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |

Table 118. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-Increment Addresses       |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

#### Table 119. CPU Control Instructions

| Mnemonic | Operands | Instruction           |

|----------|----------|-----------------------|

| ATM      | _        | Atomic Execution      |

| CCF      | _        | Complement Carry Flag |

| DI       | _        | Disable Interrupts    |

| EI       | _        | Enable Interrupts     |

| HALT     | _        | Halt Mode             |

| NOP      | _        | No Operation          |

| RCF      | _        | Reset Carry Flag      |

**z**ilog<sup>°</sup>

## 210

| Assembly        | Symbolic                                                                                                          | Addres        | s Mode   | Opcode(s) |   |              | Fla | ags |   |   | _ Fetch | Instr. |

|-----------------|-------------------------------------------------------------------------------------------------------------------|---------------|----------|-----------|---|--------------|-----|-----|---|---|---------|--------|

| Mnemonic        | Operation                                                                                                         | dst           | src      | (Hex)     | С | Ζ            | S   | ۷   | D | Н | Cycles  |        |

| HALT            | Halt Mode                                                                                                         |               |          | 7F        | - | -            | -   | -   | - | - | 1       | 2      |

| INC dst         | $dst \gets dst + 1$                                                                                               | R             |          | 20        | _ | *            | *   | _   | - | _ | 2       | 2      |

|                 |                                                                                                                   | IR            |          | 21        | - |              |     |     |   |   | 2       | 3      |

|                 |                                                                                                                   | r             |          | 0E-FE     | - |              |     |     |   |   | 1       | 2      |

| INCW dst        | $dst \gets dst + 1$                                                                                               | RR            |          | A0        | - | *            | *   | *   | - | - | 2       | 5      |

|                 |                                                                                                                   | IRR           |          | A1        | - |              |     |     |   |   | 2       | 6      |

| IRET            | $FLAGS \leftarrow @SP$ $SP \leftarrow SP + 1$ $PC \leftarrow @SP$ $SP \leftarrow SP + 2$ $IRQCTL[7] \leftarrow 1$ |               |          | BF        | * | *            | *   | *   | * | * | 1       | 5      |

| JP dst          | $PC \gets dst$                                                                                                    | DA            |          | 8D        | - | _            | _   | _   | - | - | 3       | 2      |

|                 |                                                                                                                   | IRR           |          | C4        | - |              |     |     |   |   | 2       | 3      |

| JP cc, dst      | if cc is true $PC \leftarrow dst$                                                                                 | DA            |          | 0D-FD     | - | -            | _   | -   | - | - | 3       | 2      |

| JR dst          | $PC \gets PC + X$                                                                                                 | DA            |          | 8B        | - | -            | -   | -   | - | - | 2       | 2      |

| JR cc, dst      | if cc is true<br>PC $\leftarrow$ PC + X                                                                           | DA            |          | 0B-FB     | _ | _            | _   | _   | _ | _ | 2       | 2      |

| LD dst, rc      | $dst \gets src$                                                                                                   | r             | IM       | 0C-FC     | - | _            | _   | _   | - | - | 2       | 2      |

|                 |                                                                                                                   | r             | X(r)     | C7        | - |              |     |     |   |   | 3       | 3      |

|                 |                                                                                                                   | X(r)          | r        | D7        | - |              |     |     |   |   | 3       | 4      |

|                 |                                                                                                                   | r             | lr       | E3        | - |              |     |     |   |   | 2       | 3      |

|                 |                                                                                                                   | R             | R        | E4        | - |              |     |     |   |   | 3       | 2      |

|                 |                                                                                                                   | R             | IR       | E5        | - |              |     |     |   |   | 3       | 4      |

|                 |                                                                                                                   | R             | IM       | E6        | - |              |     |     |   |   | 3       | 2      |

|                 |                                                                                                                   | IR            | IM       | E7        | - |              |     |     |   |   | 3       | 3      |

|                 |                                                                                                                   | lr            | r        | F3        | - |              |     |     |   |   | 2       | 3      |

|                 |                                                                                                                   | IR            | R        | F5        | - |              |     |     |   |   | 3       | 3      |

| Flags Notation: | * = Value is a function<br>– = Unaffected<br>X = Undefined                                                        | of the result | of the o | peration. |   | ⊧ Re<br>⊧ Se |     |     | ) |   |         |        |

#### Table 124. eZ8 CPU Instruction Summary (Continued)

# zilog

## **Electrical Characteristics**

The data in this chapter is pre-qualification and pre-characterization and is subject to change. Additional electrical characteristics may be found in the individual chapters.

## **Absolute Maximum Ratings**

Stresses greater than those listed in Table 126 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                                      | Minimum | Maximum | Units | Notes |

|----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                 | -40     | +105    | °C    |       |

| Storage temperature                                            | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>             | -0.3    | +5.5    | V     | 1     |

|                                                                | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$               | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin            | -5      | +5      | μA    |       |

| Maximum output current from active output pin                  | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0 °C to 70 °C                |         |         |       |       |

| Total power dissipation                                        |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$               |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0 °C to 70 °C               |         |         |       |       |

| Total power dissipation                                        |         | 430     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub> |         | 120     | mA    |       |

#### Table 126. Absolute Maximum Ratings

| Part Number                         | Flash     | RAM      | NVDS   | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|-------------------------------------|-----------|----------|--------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082/    | A Series  | s with 8 | KB Fla | ash       |            |                     |                     |                |            |                    |                     |

| Standard Temperature: 0 °C to 70 °C |           |          |        |           |            |                     |                     |                |            |                    |                     |

| Z8F081APB020SC                      | 8 KB      | 1 KB     | 0      | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F081AQB020SC                      | 8 KB      | 1 KB     | 0      | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F081ASB020SC                      | 8 KB      | 1 KB     | 0      | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F081ASH020SC                      | 8 KB      | 1 KB     | 0      | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F081AHH020SC                      | 8 KB      | 1 KB     | 0      | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F081APH020SC                      | 8 KB      | 1 KB     | 0      | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F081ASJ020SC                      | 8 KB      | 1 KB     | 0      | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F081AHJ020SC                      | 8 KB      | 1 KB     | 0      | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F081APJ020SC                      | 8 KB      | 1 KB     | 0      | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperatur                 | e: -40 °  | C to 105 | 5 °C   |           |            |                     |                     |                |            |                    |                     |

| Z8F081APB020EC                      | 8 KB      | 1 KB     | 0      | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F081AQB020EC                      | 8 KB      | 1 KB     | 0      | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F081ASB020EC                      | 8 KB      | 1 KB     | 0      | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F081ASH020EC                      | 8 KB      | 1 KB     | 0      | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F081AHH020EC                      | 8 KB      | 1 KB     | 0      | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F081APH020EC                      | 8 KB      | 1 KB     | 0      | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F081ASJ020EC                      | 8 KB      | 1 KB     | 0      | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F081AHJ020EC                      | 8 KB      | 1 KB     | 0      | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F081APJ020EC                      | 8 KB      | 1 KB     | 0      | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Replace C with G for Lead           | d-Free Pa | ackaging |        |           |            |                     |                     |                |            |                    |                     |

RL 206

Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

zilog | 267

register 201 ADC control (ADCCTL) 130, 132 ADC data high byte (ADCDH) 132 ADC data low bits (ADCDL) 133 flash control (FCTL) 149, 155, 156 flash high and low byte (FFREQH and FREEQL) 152 flash page select (FPS) 150, 151 flash status (FSTAT) 150 GPIO port A-H address (PxADDR) 46 GPIO port A-H alternate function sub-registers 48 GPIO port A-H control address (PxCTL) 47 GPIO port A-H data direction sub-registers 47 OCD control 184 OCD status 185 UARTx baud rate high byte (UxBRH) 114 UARTx baud rate low byte (UxBRL) 114 UARTx Control 0 (UxCTL0) 108, 114 UARTx control 1 (UxCTL1) 109 UARTx receive data (UxRXD) 113 UARTx status 0 (UxSTAT0) 111 UARTx status 1 (UxSTAT1) 112 UARTx transmit data (UxTXD) 113 Watchdog Timer control (WDTCTL) 31, 94, 136, 190 Watchdog Timer reload high byte (WDTH) 95 Watchdog Timer reload low byte (WDTL) 95 Watchdog Timer reload upper byte (WD-TU) 95 register file 15 register pair 201 register pointer 202 reset and stop mode characteristics 24 and Stop Mode Recovery 23 carry flag 204 sources 25 **RET 206** return 206

RLC 206 rotate and shift instuctions 206 rotate left 206 rotate left through carry 206 rotate right 206 rotate right through carry 206 RP 202 RR 201, 206 rr 201 RRC 206

## S

**SBC 203** SCF 204, 205 second opcode map after 1FH 219 set carry flag 204, 205 set register pointer 205 shift right arithmatic 207 shift right logical 207 signal descriptions 11 single-shot conversion (ADC) 123 software trap 206 source operand 202 SP 202 SRA 207 src 202 SRL 207 **SRP 205** stack pointer 202 **STOP 205** STOP mode 33 stop mode 205 Stop Mode Recovery sources 28 using a GPIO port pin transition 29 using Watchdog Timer time-out 29 stop mode recovery sources 30 using a GPIO port pin transition 30 SUB 203 subtract 203 subtract - extended addressing 203 subtract with carry 203