Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 64 x 8                                                    |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f021asb020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Z8 Encore! XP<sup>®</sup> F082A Series **Product Specification**

# zilog <sub>3</sub>

| Part<br>Number | Flash<br>(KB) | RAM<br>(B) | NVDS <sup>1</sup><br>(B) | I/O  | Comparator | Advanced<br>Analog <sup>2</sup> | ADC<br>Inputs | Packages           |

|----------------|---------------|------------|--------------------------|------|------------|---------------------------------|---------------|--------------------|

| Z8F082A        | 8             | 1024       | 0                        | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F081A        | 8             | 1024       | 0                        | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F042A        | 4             | 1024       | 128                      | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F041A        | 4             | 1024       | 128                      | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F022A        | 2             | 512        | 64                       | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F021A        | 2             | 512        | 64                       | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F012A        | 1             | 256        | 16                       | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F011A        | 1             | 256        | 16                       | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pir |

Table 1. Z8 Encore! XP<sup>®</sup> F082A Series Family Part Selection Guide

<sup>1</sup>Non-volatile data storage.

<sup>2</sup>Advanced Analog includes ADC, temperature sensor, and low-power operational amplifier.

**z**ilog<sup>°</sup>

addresses outside the available Flash memory addresses returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 5 describes the Program Memory Maps for the Z8 Encore! XP F082A Series products.

| Program Memory Address (Hex) | Function                     |

|------------------------------|------------------------------|

| Z8F082A and Z8F081A Products |                              |

| 0000–0001                    | Flash Option Bits            |

| 0002–0003                    | Reset Vector                 |

| 0004–0005                    | WDT Interrupt Vector         |

| 0006–0007                    | Illegal Instruction Trap     |

| 0008–0037                    | Interrupt Vectors*           |

| 0038–0039                    | Reserved                     |

| 003A-003D                    | Oscillator Fail Trap Vectors |

| 003E-1FFF                    | Program Memory               |

| Z8F042A and Z8F041A Products |                              |

| 0000–0001                    | Flash Option Bits            |

| 0002–0003                    | Reset Vector                 |

| 0004–0005                    | WDT Interrupt Vector         |

| 0006–0007                    | Illegal Instruction Trap     |

| 0008–0037                    | Interrupt Vectors*           |

| 0038–0039                    | Reserved                     |

| 003A-003D                    | Oscillator Fail Trap Vectors |

| 003E-0FFF                    | Program Memory               |

Table 5. Z8 Encore! XP F082A Series Program Memory Maps

16

operational amplifier (LPO) is OFF. To use the LPO, clear the LPO bit, turning it ON. Clearing this bit might interfere with normal ADC measurements on ANA0 (the LPO output). This bit enables the amplifier even in STOP mode. If the amplifier is not required in STOP mode, disable it. Failure to perform this results in STOP mode currents greater than specified.

**Note:** This register is only reset during a POR sequence. Other system reset events do not affect *it.*

### Table 12. Power Control Register 0 (PWRCTL0)

| BITS  | 7   | 6        | 5               | 4   | 3    | 2   | 1    | 0        |

|-------|-----|----------|-----------------|-----|------|-----|------|----------|

| FIELD | LPO | Reserved |                 | VBO | TEMP | ADC | COMP | Reserved |

| RESET | 1   | 0        | 0               | 0   | 0    | 0   | 0    | 0        |

| R/W   | R/W | R/W      | R/W R/W R/W R/W |     |      |     |      | R/W      |

| ADDR  |     |          |                 | F8  | 0H   |     |      |          |

LPO—Low-Power Operational Amplifier Disable

0 = LPO is enabled (this applies even in STOP mode).

1 = LPO is disabled.

Reserved—Must be 0.

VBO—Voltage Brownout Detector Disable

This bit and the VBO\_AO Flash option bit must both enable the VBO for the VBO to be active.

0 = VBO Enabled

1 = VBO Disabled

TEMP—Temperature Sensor Disable

0 = Temperature Sensor Enabled

1 = Temperature Sensor Disabled

ADC—Analog-to-Digital Converter Disable

- 0 = Analog-to-Digital Converter Enabled

- 1 = Analog-to-Digital Converter Disabled

COMP—Comparator Disable

- 0 =Comparator is Enabled

- 1 = Comparator is Disabled

Reserved—Must be 0.

Note: Asserting any power control bit disables the targeted block, regardless of any enable bits contained in the target block's control registers.

Zilog <sub>42</sub>

| Port   | Pin | Mnemonic    | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------|--------------------------------|-----------------------------------------|

| Port B | PB0 | Reserved    |                                | AFS1[0]: 0                              |

|        |     | ANA0/AMPOUT | ADC Analog Input/LPO Output    | AFS1[0]: 1                              |

|        | PB1 | Reserved    |                                | AFS1[1]: 0                              |

|        |     | ANA1/AMPINN | ADC Analog Input/LPO Input (N) | AFS1[1]: 1                              |

|        | PB2 | Reserved    |                                | AFS1[2]: 0                              |

|        |     | ANA2/AMPINP | ADC Analog Input/LPO Input (P) | AFS1[2]: 1                              |

|        | PB3 | CLKIN       | External Clock Input           | AFS1[3]: 0                              |

|        |     | ANA3        | ADC Analog Input               | AFS1[3]: 1                              |

|        | PB4 | Reserved    |                                | AFS1[4]: 0                              |

|        |     | ANA7        | ADC Analog Input               | AFS1[4]: 1                              |

|        | PB5 | Reserved    |                                | AFS1[5]: 0                              |

|        |     | VREF*       | ADC Voltage Reference          | AFS1[5]: 1                              |

|        | PB6 | Reserved    |                                | AFS1[6]: 0                              |

|        |     | Reserved    |                                | AFS1[6]: 1                              |

|        | PB7 | Reserved    |                                | AFS1[7]: 0                              |

|        |     | Reserved    |                                | AFS1[7]: 1                              |

#### Table 14. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Note: Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set register AFS2 is not used to select the function. Also, alternate function selection as described in Port A-D Alternate Function Sub-Registers on page 47 must also be enabled.

\* VREF is available on PB5 in 28-pin products only.

U0RXI—UART 0 Receiver Interrupt Request

0 = No interrupt request is pending for the UART 0 receiver.

1 = An interrupt request from the UART 0 receiver is awaiting service.

U0TXI-UART 0 Transmitter Interrupt Request

0 = No interrupt request is pending for the UART 0 transmitter.

1 = An interrupt request from the UART 0 transmitter is awaiting service.

ADCI—ADC Interrupt Request

0 = No interrupt request is pending for the analog-to-digital Converter.

1 = An interrupt request from the Analog-to-Digital Converter is awaiting service.

## **Interrupt Request 1 Register**

The Interrupt Request 1 (IRQ1) register (Table 34) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ1 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 1 register to determine if any interrupt requests are pending.

| BITS  | 7     | 6                           | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|-------|-----------------------------|------|------|------|------|------|------|

| FIELD | PA7VI | PA6CI                       | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |

| RESET | 0     | 0                           | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W   | R/W   | R/W R/W R/W R/W R/W R/W R/W |      |      |      |      |      |      |

| ADDR  |       | FC3H                        |      |      |      |      |      |      |

Table 34. Interrupt Request 1 Register (IRQ1)

PA7*V*I—Port A Pin 7 or LVD Interrupt Request

0 = No interrupt request is pending for GPIO Port A or LVD.

1 = An interrupt request from GPIO Port A or LVD.

PA6CI—Port A Pin 6 or Comparator Interrupt Request

0 = No interrupt request is pending for GPIO Port A or Comparator.

1 = An interrupt request from GPIO Port A or Comparator.

PAxI—Port A Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port A pin *x*.

1 = An interrupt request from GPIO Port A pin x is awaiting service.

where x indicates the specific GPIO Port pin number (0–5).

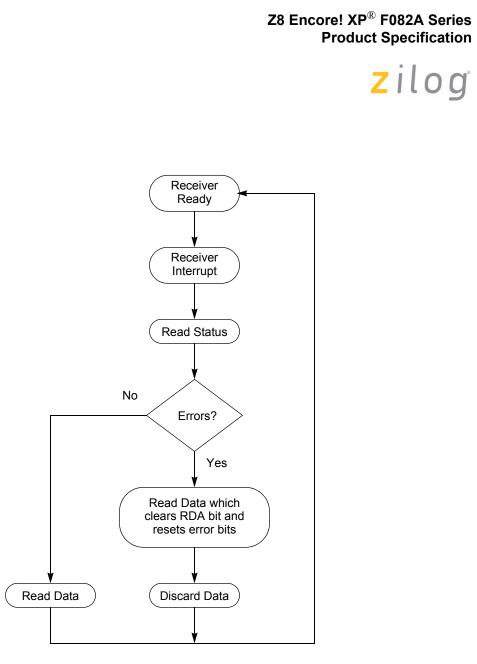

Figure 15. UART Receiver Interrupt Service Routine Flow

## **Baud Rate Generator Interrupts**

If the baud rate generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud Rate Generator to function as an additional counter if the UART functionality is not employed.

## **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value

107

MPRX—Multiprocessor Receive

Returns the value of the most recent multiprocessor bit received. Reading from the UART Receive Data register resets this bit to 0.

## **UART Transmit Data Register**

Data bytes written to the UART Transmit Data (UxTXD) register (Table 65) are shifted out on the TXDx pin. The Write-only UART Transmit Data register shares a Register File address with the read-only UART Receive Data register.

| BITS  | 7 | 6             | 5 | 4  | 3  | 2 | 1 | 0 |

|-------|---|---------------|---|----|----|---|---|---|

| FIELD |   | TXD           |   |    |    |   |   |   |

| RESET | Х | Х             | Х | Х  | Х  | Х | Х | Х |

| R/W   | W | w w w w w w w |   |    |    |   |   |   |

| ADDR  |   |               |   | F4 | 0H |   |   |   |

#### Table 65. UART Transmit Data Register (U0TXD)

TXD-Transmit Data

UART transmitter data byte to be shifted out through the TXDx pin.

## **UART Receive Data Register**

Data bytes received through the RXDx pin are stored in the UART Receive Data (UxRXD) register (Table 66). The read-only UART Receive Data register shares a Register File address with the Write-only UART Transmit Data register.

### Table 66. UART Receive Data Register (U0RXD)

| BITS      | 7              | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|----------------|-----|---|---|---|---|---|---|

| FIELD     |                | RXD |   |   |   |   |   |   |

| RESET     | Х              | Х   | Х | Х | Х | Х | Х | Х |

| R/W       | R              | R   | R | R | R | R | R | R |

| ADDR      | F40H           |     |   |   |   |   |   |   |

| X = Undef | < = Undefined. |     |   |   |   |   |   |   |

RXD—Receive Data

UART receiver data byte from the RXDx pin

## Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

zilog

### 126

## **Factory Calibration**

Devices that have been factory calibrated contain 30 bytes of calibration data in the Flash option bit space. This data consists of 3 bytes for each input mode, one for offset and two for gain correction. For a list of input modes for which calibration data exists, see Zilog Calibration Data on page 161.

#### **User Calibration**

If you have precision references available, its own external calibration can be performed using any input modes. This calibration data takes into account buffer offset and non-linearity, so it is recommended that this calibration be performed separately for each of the ADC input modes planned for use.

### **Manual Offset Calibration**

When uncalibrated, the ADC has significant offset (see Table 135 on page 231). Subsequently, manual offset calibration capability is built into the block. When the ADC Control Register 0 sets the input mode (ANAIN[2:0]) to MANUAL OFFSET CALIBRATION mode, the differential inputs to the ADC are shorted together by an internal switch. Reading the ADC value at this point produces 0 in an ideal system. The value actually read is the ADC offset. This value can be stored in non-volatile memory (see Non-Volatile Data Storage on page 169) and accessed by user code to compensate for the input offset error. There is no provision for manual gain calibration.

### Software Compensation Procedure Using Factory Calibration Data

The value read from the ADC high and low byte registers is uncompensated. The user mode software must apply gain and offset correction to this uncompensated value for maximum accuracy. The following equation yields the compensated value:

$ADC_{comp} = (ADC_{uncomp} - OFFCAL) + ((ADC_{uncomp} - OFFCAL) \times GAINCAL)/2^{16}$

where GAINCAL is the gain calibration value, OFFCAL is the offset calibration value and  $ADC_{uncomp}$  is the uncompensated value read from the ADC. All values are in two's complement format.

#### Note:

The offset compensation is performed first, followed by the gain compensation. One bit of resolution is lost because of rounding on both the offset and gain computations. As a result the ADC registers read back 13 bits: 1 sign bit, two calibration bits lost to rounding and 10 data bits.

Also note that in the second term, the multiplication must be performed before the division by  $2^{16}$ . Otherwise, the second term incorrectly evaluates to zero.

134

## Low Power Operational Amplifier

## **Overview**

The LPO is a general-purpose low power operational amplifier. Each of the three ports of the amplifier is accessible from the package pins. The LPO contains only one pin configuration: ANA0 is the output/feedback node, ANA1 is the inverting input and ANA2 is the non-inverting input.

## Operation

To use the LPO, it must be enabled in the Power Control Register 0 (PWRCTL0). The default state of the LPO is OFF. To use the LPO, the LPO bit must be cleared, turning it ON (Power Control Register 0 (PWRCTL0) on page 35). When making normal ADC measurements on ANA0 (measurements not involving the LPO output), the LPO bit must be OFF. Turning the LPO bit ON interferes with normal ADC measurements.

**Warning:** The LPO bit enables the amplifier even in STOP mode. If the amplifier is not required in STOP mode, disable it. Failing to perform this results in STOP mode currents higher than necessary.

As with other ADC measurements, any pins used for analog purposes must be configured as such in the GPIO registers (see Port A–D Alternate Function Sub-Registers on page 47).

LPO output measurements are made on ANA0, as selected by the ANAIN[3:0] bits of ADC Control Register 0. It is also possible to make single-ended measurements on ANA1 and ANA2 while the amplifier is enabled, which is often useful for determining offset conditions. Differential measurements between ANA0 and ANA2 may be useful for noise cancellation purposes.

If the LPO output is routed to the ADC, then the BUFFMODE[2:0] bits of ADC Control/Status Register 1 must also be configured for unity-gain buffered operation. Sampling the LPO in an unbuffered mode is not recommended.

When either input is overdriven, the amplifier output saturates at the positive or negative supply voltage. No instability results.

## Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

zilog

183

```

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

• **Read Data Memory (0DH)**—The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode, this command returns FFH for the data.

```

DBG \leftarrow 0DH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

• **Read Program Memory CRC (0EH)**—The Read Program Memory CRC command computes and returns the Cyclic Redundancy Check (CRC) of Program Memory using the 16-bit CRC-CCITT polynomial. If the device is not in DEBUG mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program Memory, calculates the CRC value, and returns the result. The delay is a function of the Program Memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program Memory.

DBG  $\leftarrow$  0EH DBG  $\rightarrow$  CRC[15:8] DBG  $\rightarrow$  CRC[7:0]

• Step Instruction (10H)—The Step Instruction command steps one assembly instruction at the current Program Counter (PC) location. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

DBG  $\leftarrow$  10H

• Stuff Instruction (11H)—The Stuff Instruction command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0-4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

• **Execute Instruction (12H)**—The Execute Instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over Breakpoints. The number of bytes to send for the instruction depends on the opcode.

If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

DBG  $\leftarrow$  12H DBG  $\leftarrow$  1-5 byte opcode

## **On-Chip Debugger Control Register Definitions**

## **OCD Control Register**

The OCD Control register controls the state of the On-Chip Debugger. This register is used to enter or exit DEBUG mode and to enable the BRK instruction. It can also reset the Z8 Encore! XP<sup>®</sup> F082A Series device.

A reset and stop function can be achieved by writing \$1H to this register. A reset and go function can be achieved by writing \$1H to this register. If the device is in DEBUG mode, a run function can be implemented by writing \$0H to this register.

## Table 106. OCD Control Register (OCDCTL)

| BITS  | 7       | 6     | 5      | 4 | 3    | 2     | 1 | 0   |

|-------|---------|-------|--------|---|------|-------|---|-----|

| FIELD | DBGMODE | BRKEN | DBGACK |   | Rese | erved |   | RST |

| RESET | 0       | 0     | 0      | 0 | 0    | 0     | 0 | 0   |

| R/W   | R/W     | R/W   | R/W    | R | R    | R     | R | R/W |

#### DBGMODE—DEBUG Mode

The device enters DEBUG mode when this bit is 1. When in DEBUG mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is automatically set when a BRK instruction is decoded and Breakpoints are enabled. If the Flash Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device. It cannot be written to 0.

0 = The Z8 Encore! XP F082A Series device is operating in NORMAL mode.

1 = The Z8 Encore! XP F082A Series device is in DEBUG mode.

### BRKEN—Breakpoint Enable

This bit controls the behavior of the BRK instruction (opcode 00H). By default, Breakpoints are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1, when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL register is automatically set to 1.

0 = Breakpoints are disabled.

1 = Breakpoints are enabled.

#### Table 108. Oscillator Configuration and Selection

| Clock Source                          | Characteristics                                                                                                                                 | Required Setup                                                                                                                                                                                                                                                                                       |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Internal Precision<br>RC Oscillator   | <ul> <li>32.8 kHz or 5.53 MHz</li> <li>High accuracy</li> <li>No external components required</li> </ul>                                        | Unlock and write Oscillator Control<br>Register (OSCCTL) to enable and<br>select oscillator at either 5.53 MHz or<br>32.8 kHz                                                                                                                                                                        |  |  |

| External Crystal/<br>Resonator        | <ul> <li>32 kHz to 20 MHz</li> <li>Very high accuracy (dependent on crystal or resonator used)</li> <li>Requires external components</li> </ul> | <ul> <li>Configure Flash option bits for correct<br/>external oscillator mode</li> <li>Unlock and write OSCCTL to enable<br/>crystal oscillator, wait for it to stabilize<br/>and select as system clock (if the<br/>XTLDIS option bit has been de-<br/>asserted, no waiting is required)</li> </ul> |  |  |

| External RC<br>Oscillator             | <ul> <li>32 kHz to 4 MHz</li> <li>Accuracy dependent on external components</li> </ul>                                                          | <ul> <li>Configure Flash option bits for correct<br/>external oscillator mode</li> <li>Unlock and write OSCCTL to enable<br/>crystal oscillator and select as system<br/>clock</li> </ul>                                                                                                            |  |  |

| External Clock<br>Drive               | <ul> <li>0 to 20 MHz</li> <li>Accuracy dependent on external clock source</li> </ul>                                                            | <ul> <li>Write GPIO registers to configure PB3<br/>pin for external clock function</li> <li>Unlock and write OSCCTL to select<br/>external system clock</li> <li>Apply external clock signal to GPIO</li> </ul>                                                                                      |  |  |

| Internal Watchdog<br>Timer Oscillator | <ul> <li>10 kHz nominal</li> <li>Low accuracy; no external components required</li> <li>Very low power consumption</li> </ul>                   | <ul> <li>Enable WDT if not enabled and wait<br/>until WDT Oscillator is operating.</li> <li>Unlock and write Oscillator Control<br/>Register (OSCCTL) to enable and<br/>select oscillator</li> </ul>                                                                                                 |  |  |

**Caution:** Unintentional accesses to the oscillator control register can actually stop the chip by switching to a non-functioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

### **OSC Control Register Unlocking/Locking**

To write the oscillator control register, unlock it by making two writes to the OSCCTL register with the values E7H followed by 18H. A third write to the OSCCTL register changes the value of the actual register and returns the register to a locked state. Any other sequence of oscillator control register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

189

When selecting a new clock source, the system clock oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If SOFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the OSCCTL register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it may be appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

## **Clock Failure Detection and Recovery**

#### System Clock Oscillator Failure

The Z8F04xA family devices can generate non-maskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function (see Watchdog Timer on page 91).

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below 1 kHz  $\pm$ 50%. If an external signal is selected as the system oscillator, it is possible that a very slow but non-failing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (SOFEN must be deasserted in the OSCCTL register).

#### Watchdog Timer Failure

In the event of a Watchdog Timer oscillator failure, a similar non-maskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the system clock oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while looking for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

196

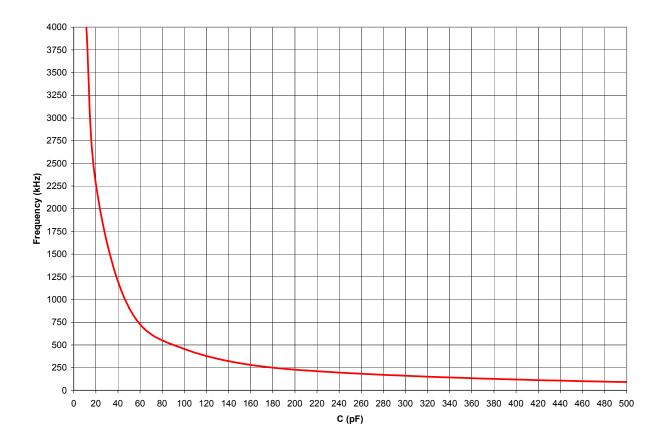

Figure 29 displays the typical (3.3 V and 25 °C) oscillator frequency as a function of the capacitor (C in pF) employed in the RC network assuming a 45 K $\Omega$  external resistor. For very small values of C, the parasitic capacitance of the oscillator XIN pin and the printed circuit board must be included in the estimation of the oscillator frequency.

It is possible to operate the RC oscillator using only the parasitic capacitance of the package and printed circuit board. To minimize sensitivity to external parasitics, external capacitance values in excess of 20 pF are recommended.

## Figure 29. Typical RC Oscillator Frequency as a Function of the External Capacitance with a 45 k $\Omega$ Resistor

**Caution**:

When using the external RC oscillator mode, the oscillator can stop oscillating if the power supply drops below 2.7 V, but before the power supply drops to the Voltage Brownout threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7 V.

## Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

204

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| ТСМ      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |

Table 118. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-Increment Addresses       |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

## Table 119. CPU Control Instructions

| Mnemonic | Operands | Instruction           |

|----------|----------|-----------------------|

| ATM      | _        | Atomic Execution      |

| CCF      | _        | Complement Carry Flag |

| DI       | _        | Disable Interrupts    |

| EI       | _        | Enable Interrupts     |

| HALT     | _        | Halt Mode             |

| NOP      | _        | No Operation          |

| RCF      | _        | Reset Carry Flag      |

223

|                   |                               |         | 40 °C to +<br>therwise | 105 °C<br>specified) |       |                                                                                 |

|-------------------|-------------------------------|---------|------------------------|----------------------|-------|---------------------------------------------------------------------------------|

| Symbol            | Parameter                     | Minimum | Typical                | Maximum              | Units | Conditions                                                                      |

| V <sub>OL2</sub>  | Low Level Output<br>Voltage   | -       | -                      | 0.6                  | V     | I <sub>OL</sub> = 20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.  |

| V <sub>OH2</sub>  | High Level Output<br>Voltage  | 2.4     | _                      | -                    | V     | I <sub>OH</sub> = -20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled. |

| I <sub>IH</sub>   | Input Leakage<br>Current      | -       | <u>+</u> 0.002         | <u>+</u> 5           | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V;$                                          |

| IIL               | Input Leakage<br>Current      | -       | <u>+</u> 0.007         | <u>+</u> 5           | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3 V;$                                          |

| I <sub>TL</sub>   | Tristate Leakage<br>Current   | -       | _                      | <u>+</u> 5           | μA    |                                                                                 |

| I <sub>LED</sub>  | Controlled Current Drive      | 1.8     | 3                      | 4.5                  | mA    | {AFS2,AFS1} = {0,0}                                                             |

|                   |                               | 2.8     | 7                      | 10.5                 | mA    | {AFS2,AFS1} = {0,1}                                                             |

|                   |                               | 7.8     | 13                     | 19.5                 | mA    | {AFS2,AFS1} = {1,0}                                                             |

|                   |                               | 12      | 20                     | 30                   | mA    | {AFS2,AFS1} = {1,1}                                                             |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance  | -       | 8.0 <sup>2</sup>       | -                    | pF    |                                                                                 |

| C <sub>XIN</sub>  | XIN Pad<br>Capacitance        | -       | 8.0 <sup>2</sup>       | _                    | pF    |                                                                                 |

| C <sub>XOUT</sub> | XOUT Pad<br>Capacitance       | -       | 9.5 <sup>2</sup>       | -                    | pF    |                                                                                 |

| I <sub>PU</sub>   | Weak Pull-up<br>Current       | 30      | 100                    | 350                  | μA    | V <sub>DD</sub> = 3.0 V–3.6 V                                                   |

| V <sub>RAM</sub>  | RAM Data<br>Retention Voltage | TBD     |                        |                      | V     | Voltage at which RAM retains static values; no reading or writing is allowed.   |

|                   |                               |         | -                      |                      | -     |                                                                                 |

## Table 127. DC Characteristics (Continued)

#### Notes

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

|                           |                                                              | V <sub>DI</sub> | <sub>0</sub> = 2.7 V to 3 |          |       |                                                                  |

|---------------------------|--------------------------------------------------------------|-----------------|---------------------------|----------|-------|------------------------------------------------------------------|

|                           |                                                              |                 | Maximum <sup>2</sup>      |          |       |                                                                  |

| Symbol                    | Parameter                                                    | Typical $^1$    | Std Temp                  | Ext Temp | Units | Conditions                                                       |

| I <sub>DD</sub> Stop      | Supply Current in STOP<br>Mode                               | 0.1             |                           |          | μA    | No peripherals enabled. All pins driven to $V_{DD}$ or $V_{SS}.$ |

| I <sub>DD</sub> Halt      | Supply Current in HALT                                       | 35              | 55                        | 65       | μA    | 32 kHz                                                           |

|                           | Mode (with all peripherals disabled)                         | 520             |                           |          | μA    | 5.5 MHz                                                          |

|                           | penpinenaie aleaalea)                                        | 2.1             | 2.85                      | 2.85     | mA    | 20 MHz                                                           |

| I <sub>DD</sub>           | Supply Current in                                            | 2.8             |                           |          | mA    | 32 kHz                                                           |

|                           | ACTIVE Mode (with all peripherals disabled)                  | 4.5             | 5.2                       | 5.2      | mA    | 5.5 MHz                                                          |

|                           |                                                              | 5.5             | 6.5                       | 6.5      | mA    | 10 MHz                                                           |

|                           | -                                                            | 7.9             | 11.5                      | 11.5     | mA    | 20 MHz                                                           |

| I <sub>DD</sub> WDT       | Watchdog Timer Supply<br>Current                             | 0.9             | 1.0                       | 1.1      | μA    |                                                                  |

| I <sub>DD</sub>           | Crystal Oscillator<br>Supply Current                         | 40              |                           |          | μA    | 32 kHz                                                           |

| XTAL                      |                                                              | 230             |                           |          | μA    | 4 MHz                                                            |

|                           | -                                                            | 760             |                           |          | μA    | 20 MHz                                                           |

| I <sub>DD</sub> IPO       | Internal Precision<br>Oscillator Supply<br>Current           | 350             | 500                       | 550      | μA    |                                                                  |

| I <sub>DD</sub> VBO       | Voltage Brownout and<br>Low-Voltage Detect<br>Supply Current | 50              |                           |          | μA    | For 20-/28-pin devices<br>(VBO only); See Notes 4                |

|                           |                                                              |                 |                           |          |       | For 8-pin devices; See<br>Notes 4                                |

| I <sub>DD</sub> ADC       | Analog to Digital                                            | 2.8             | 3.1                       | 3.2      | mA    | 32 kHz                                                           |

|                           | Converter Supply Current (with External _ Reference)         | 3.1             | 3.6                       | 3.7      | mA    | 5.5 MHz                                                          |

|                           |                                                              | 3.3             | 3.7                       | 3.8      | mA    | 10 MHz                                                           |

|                           | -                                                            | 3.7             | 4.2                       | 4.3      | mA    | 20 MHz                                                           |

| I <sub>DD</sub><br>ADCRef | ADC Internal Reference<br>Supply Current                     | 0               |                           |          | μA    | See Notes 4                                                      |

| I <sub>DD</sub> CMP       | Comparator supply<br>Current                                 | 150             | 180                       | 190      | μA    | See Notes 4                                                      |

## Table 128. Power Consumption

|                    |                                             |         | = 2.7 V to<br>-40 °C to - |            |       |                                 |

|--------------------|---------------------------------------------|---------|---------------------------|------------|-------|---------------------------------|

| Symbol             | Parameter                                   | Minimum | Typical                   | Maximum    | Units | Conditions                      |

| Av                 | Open loop voltage gain                      |         | 80                        |            | dB    |                                 |

| GBW                | Gain/Bandwidth product                      |         | 500                       |            | kHz   |                                 |

| РМ                 | Phase Margin                                |         | 50                        |            | deg   | Assuming 13 pF load capacitance |

| V <sub>osLPO</sub> | Input Offset Voltage                        |         | <u>+</u> 1                | <u>+</u> 4 | mV    |                                 |

| V <sub>osLPO</sub> | Input Offset Voltage<br>(Temperature Drift) |         | 1                         | 10         | μV/C  |                                 |

| V <sub>IN</sub>    | Input Voltage Range                         | 0.3     |                           | Vdd - 1    | V     |                                 |

| V <sub>OUT</sub>   | Output Voltage Range                        | 0.3     |                           | Vdd - 1    | V     | I <sub>OUT</sub> = 45 μA        |

## Table 136. Low Power Operational Amplifier Electrical Characteristics

## Table 137. Comparator Electrical Characteristics

|                   |                                            |                 | = 2.7 V to<br>40 °C to + |                    |       |                    |  |

|-------------------|--------------------------------------------|-----------------|--------------------------|--------------------|-------|--------------------|--|

| Symbol            | Parameter                                  | Minimum         | Typical                  | Maximum            | Units | Conditions         |  |

| V <sub>OS</sub>   | Input DC Offset                            |                 | 5                        |                    | mV    |                    |  |

|                   | Programmable Internal<br>Reference Voltage |                 | <u>+</u> 5               |                    | %     | 20-/28-pin devices |  |

|                   |                                            |                 | <u>+</u> 3               |                    | %     | 8-pin devices      |  |

| T <sub>PROP</sub> | Propagation Delay                          |                 | 200                      |                    | ns    |                    |  |

| V <sub>HYS</sub>  | Input Hysteresis                           |                 | 4                        |                    | mV    |                    |  |

| V <sub>IN</sub>   | Input Voltage Range                        | V <sub>SS</sub> |                          | V <sub>DD</sub> -1 | V     |                    |  |

Z8 Encore! XP<sup>®</sup> F082A Series | **Product Specification**

zilog 257

| Part Number                     | Flash     | RAM      | SUVN   | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------|-----------|----------|--------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082 | A Serie   | s with 1 | KB Fla | ish, 1    | 0-Bit      | Ana                 | log-t               | o-Dig          | jital C    | Conv               | verter              |

| Standard Temperatu              | re: 0 °C  | to 70 °C | ;      |           |            |                     |                     |                |            |                    |                     |

| Z8F012APB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperatu              | re: -40 ° | C to 10  | 5 °C   |           |            |                     |                     |                |            |                    |                     |

| Z8F012APB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

264

**DJNZ 206** EI 204 **HALT 204 INC 203 INCW 203 IRET 206** JP 206 LD 205 LDC 205 LDCI 204, 205 LDE 205 LDEI 204 LDX 205 LEA 205 logical 205 **MULT 203** NOP 204 OR 205 **ORX 206** POP 205 **POPX 205** program control 206 **PUSH 205** PUSHX 205 **RCF 204 RET 206** RL 206 **RLC 206** rotate and shift 206 RR 206 **RRC 206** SBC 203 SCF 204, 205 SRA 207 SRL 207 **SRP 205 STOP 205** SUB 203 SUBX 203 **SWAP 207** TCM 204 **TCMX 204** TM 204 TMX 204

**TRAP 206** Watchdog Timer refresh 205 XOR 206 **XORX 206** instructions, eZ8 classes of 202 interrupt control register 67 interrupt controller 55 architecture 55 interrupt assertion types 58 interrupt vectors and priority 58 operation 57 register definitions 60 software interrupt assertion 59 interrupt edge select register 66 interrupt request 0 register 60 interrupt request 1 register 61 interrupt request 2 register 62 interrupt return 206 interrupt vector listing 55 interrupts **UART 105** IR 201 lr 201 IrDA architecture 117 block diagram 117 control register definitions 120 operation 117 receiving data 119 transmitting data 118 **IRET 206** IRQ0 enable high and low bit registers 62 IRQ1 enable high and low bit registers 63 IRQ2 enable high and low bit registers 65 **IRR 201** Irr 201

## J

JP 206 jump, conditional, relative, and relative conditional 206