# E·XFL

#### Zilog - Z8F021ASJ020SC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | IrDA, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT               |

| Number of I/O              | 25                                                            |

| Program Memory Size        | 2KB (2K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | 64 x 8                                                        |

| RAM Size                   | 512 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | -                                                             |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f021asj020sc00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

х

| OCD Data Format<br>OCD Auto-Baud Detector/Generator<br>OCD Serial Errors<br>OCD Unlock Sequence (8-Pin Devices Only)<br>Breakpoints<br>Runtime Counter                                               | 176<br>177<br>178<br>178<br>179 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| On-Chip Debugger Commands                                                                                                                                                                            | 184<br>184                      |

| Oscillator Control                                                                                                                                                                                   | 187                             |

| Operation  System Clock Selection    Clock Failure Detection and Recovery  Oscillator Control Register Definitions                                                                                   | 187<br>189                      |

| Crystal Oscillator                                                                                                                                                                                   | 193                             |

| Operating Modes  Crystal Oscillator Operation    Oscillator Operation with an External RC Network  Crystal Oscillator Operation                                                                      | 193                             |

| Internal Precision Oscillator                                                                                                                                                                        | 197                             |

| Operation                                                                                                                                                                                            | 197                             |

| eZ8 CPU Instruction Set                                                                                                                                                                              | 199                             |

| Assembly Language Programming IntroductionAssembly Language SyntaxeZ8 CPU Instruction NotationeZ8 CPU Instruction ClasseseZ8 CPU Instruction ClasseseZ8 CPU Instruction Summary                      | 200<br>200<br>202               |

| Opcode Maps                                                                                                                                                                                          | 216                             |

| Electrical Characteristics                                                                                                                                                                           | 221                             |

| Absolute Maximum Ratings  DC Characteristics    DC Characteristics  AC Characteristics    On-Chip Peripheral AC and DC Electrical Characteristics  General Purpose I/O Port Input Data Sample Timing | 222<br>227<br>229               |

# Zilog <sub>19</sub>

## **Register Map**

Table 7 provides the address map for the Register File of the Z8 Encore! XP<sup>®</sup> F082A Series devices. Not all devices and package styles in the Z8 Encore! XP F082A Series support the ADC, or all of the GPIO Ports. Consider registers for unimplemented peripherals as Reserved.

#### Table 7. Register File Address Map

| Address (Hex) | Register Description              | Mnemonic      | Reset (Hex) | Page No |

|---------------|-----------------------------------|---------------|-------------|---------|

| General-Purpo | se RAM                            |               |             |         |

| Z8F082A/Z8F0  | 81A Devices                       |               |             |         |

| 000–3FF       | General-Purpose Register File RAM | _             | XX          |         |

| 400–EFF       | Reserved                          | —             | XX          |         |

| Z8F042A/Z8F0  | 41A Devices                       |               |             |         |

| 000–3FF       | General-Purpose Register File RAM | _             | XX          |         |

| 400–EFF       | Reserved                          | _             | XX          |         |

| Z8F022A/Z8F0  | 21A Devices                       |               |             |         |

| 000–1FF       | General-Purpose Register File RAM | _             | XX          |         |

| 200–EFF       | Reserved                          | —             | XX          |         |

| Z8F012A/Z8F0  | 11A Devices                       |               |             |         |

| 000–0FF       | General-Purpose Register File RAM | _             | XX          |         |

| 100–EFF       | Reserved                          | —             | XX          |         |

| Timer 0       |                                   |               |             |         |

| F00           | Timer 0 High Byte                 | T0H           | 00          | 87      |

| F01           | Timer 0 Low Byte                  | TOL           | 01          | 87      |

| F02           | Timer 0 Reload High Byte          | T0RH          | FF          | 88      |

| F03           | Timer 0 Reload Low Byte           | T0RL          | FF          | 88      |

| F04           | Timer 0 PWM High Byte             | T0PWMH        | 00          | 88      |

| F05           | Timer 0 PWM Low Byte              | <b>T0PWML</b> | 00          | 89      |

| F06           | Timer 0 Control 0                 | TOCTLO        | 00          | 83      |

| F07           | Timer 0 Control 1                 | T0CTL1        | 00          | 84      |

| Timer 1       |                                   |               |             |         |

| F08           | Timer 1 High Byte                 | T1H           | 00          | 87      |

| F09           | Timer 1 Low Byte                  | T1L           | 01          | 87      |

| F0A           | Timer 1 Reload High Byte          | T1RH          | FF          | 88      |

vector address. Following Stop Mode Recovery, the STOP bit in the Reset Status (RSTSTAT) Register is set to 1. Table 10 lists the Stop Mode Recovery sources and resulting actions. The text following provides more detailed information about each of the Stop Mode Recovery sources.

| Operating Mode | Stop Mode Recovery Source                                                         | Action                                                               |

|----------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------|

| STOP mode      | Watchdog Timer time-out when configured for Reset                                 | Stop Mode Recovery                                                   |

|                | Watchdog Timer time-out when configured for interrupt                             | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |

|                | Data transition on any GPIO Port<br>pin enabled as a Stop Mode<br>Recovery source | Stop Mode Recovery                                                   |

|                | Assertion of external RESET Pin                                                   | System Reset                                                         |

|                | Debug Pin driven Low                                                              | System Reset                                                         |

#### Table 10. Stop Mode Recovery Sources and Resulting Action

#### Stop Mode Recovery Using Watchdog Timer Time-Out

If the Watchdog Timer times out during STOP mode, the device undergoes a Stop Mode Recovery sequence. In the Reset Status (RSTSTAT) register, the WDT and STOP bits are set to 1. If the Watchdog Timer is configured to generate an interrupt upon time-out and the Z8 Encore! XP F082A Series device is configured to respond to interrupts, the eZ8 CPU services the Watchdog Timer interrupt request following the normal Stop Mode Recovery sequence.

#### Stop Mode Recovery Using a GPIO Port Pin Transition

Each of the GPIO Port pins may be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a Stop Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery.

**Note:** The SMR pulses shorter than specified does not trigger a recovery (see Table 131 on page 229). When this happens, the STOP bit in the Reset Status (RSTSTAT) register is set to 1.

**Caution:** In STOP mode, the GPIO Port Input Data registers (PxIN) are disabled. The Port Input Data registers record the Port transition only if the signal stays on the Port pin through the end of the Stop Mode Recovery delay. As a result, short pulses on the Port pin can

## **Low-Power Modes**

The Z8 Encore! XP F082A Series products contain power-saving features. The highest level of power reduction is provided by the STOP mode, in which nearly all device functions are powered down. The next lower level of power reduction is provided by the HALT mode, in which the CPU is powered down.

Further power savings can be implemented by disabling individual peripheral blocks while in Active mode (defined as being in neither STOP nor HALT mode).

### **STOP Mode**

Executing the eZ8 CPU's STOP instruction places the device into STOP mode, powering down all peripherals except the Voltage Brownout detector, the Low-power Operational Amplifier and the Watchdog Timer. These three blocks may also be disabled for additional power savings. Specifically, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; XIN and XOUT (if previously enabled) are disabled, and PA0/PA1 revert to the states programmed by the GPIO registers.

- System clock is stopped.

- eZ8 CPU is stopped.

- Program counter (PC) stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control register.

- If enabled, the Watchdog Timer logic continues to operate.

- If enabled for operation in STOP mode by the associated Flash Option Bit, the Voltage Brownout protection circuit continues to operate.

- Low-power operational amplifier continues to operate if enabled by the Power Control register to do so.

- All other on-chip peripherals are idle.

To minimize current in STOP mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP mode using Stop Mode Recovery. For more information on Stop Mode Recovery, see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23.

Zilog <sub>42</sub>

| Port       | Pin | Mnemonic    | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|------------|-----|-------------|--------------------------------|-----------------------------------------|

| Port B PB0 |     | Reserved    |                                | AFS1[0]: 0                              |

|            |     | ANA0/AMPOUT | ADC Analog Input/LPO Output    | AFS1[0]: 1                              |

|            | PB1 | Reserved    |                                | AFS1[1]: 0                              |

|            |     | ANA1/AMPINN | ADC Analog Input/LPO Input (N) | AFS1[1]: 1                              |

|            | PB2 | Reserved    |                                | AFS1[2]: 0                              |

| -          |     | ANA2/AMPINP | ADC Analog Input/LPO Input (P) | AFS1[2]: 1                              |

|            | PB3 | CLKIN       | External Clock Input           | AFS1[3]: 0                              |

|            |     | ANA3        | ADC Analog Input               | AFS1[3]: 1                              |

|            | PB4 | Reserved    |                                | AFS1[4]: 0                              |

|            |     | ANA7        | ADC Analog Input               | AFS1[4]: 1                              |

|            | PB5 | Reserved    |                                | AFS1[5]: 0                              |

|            |     | VREF*       | ADC Voltage Reference          | AFS1[5]: 1                              |

|            | PB6 | Reserved    |                                | AFS1[6]: 0                              |

|            |     | Reserved    |                                | AFS1[6]: 1                              |

|            | PB7 | Reserved    |                                | AFS1[7]: 0                              |

|            |     | Reserved    |                                | AFS1[7]: 1                              |

#### Table 14. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Note: Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set register AFS2 is not used to select the function. Also, alternate function selection as described in Port A-D Alternate Function Sub-Registers on page 47 must also be enabled.

\* VREF is available on PB5 in 28-pin products only.

zilog<sup>®</sup>

Set 1 Sub-Registers on page 50, GPIO Alternate Functions on page 38, and Port A–D Alternate Function Set 2 Sub-Registers on page 51. See GPIO Alternate Functions on page 38 to determine the alternate function associated with each port pin.

Caution:

Do not enable alternate functions for GPIO port pins for which there is no associated alternate function. Failure to follow this guideline can result in unpredictable operation.

| Table 20. Port A–D Alternate Function Sub-Registers | (PxAF) |  |

|-----------------------------------------------------|--------|--|

|                                                     |        |  |

| BITS  | 7                                                           | 6            | 5           | 4             | 3            | 2             | 1            | 0        |

|-------|-------------------------------------------------------------|--------------|-------------|---------------|--------------|---------------|--------------|----------|

| FIELD | AF7                                                         | AF6          | AF5         | AF4           | AF3          | AF2           | AF1          | AF0      |

| RESET | 00H (Ports A–C); 01H (Port D); 04H (Port A of 8-pin device) |              |             |               |              |               |              |          |

| R/W   | R/W                                                         |              |             |               |              |               |              |          |

| ADDR  | lf 02H i                                                    | n Port A–D / | Address Reg | gister, acces | sible throug | n the Port A- | –D Control F | Register |

AF[7:0]—Port Alternate Function enabled

0 = The port pin is in normal mode and the DDx bit in the Port A–D Data Direction sub-register determines the direction of the pin.

1 = The alternate function selected through Alternate Function Set sub-registers is enabled. Port pin operation is controlled by the alternate function.

#### Port A–D Output Control Sub-Registers

The Port A–D Output Control sub-register (Table 21) is accessed through the Port A–D Control register by writing 03H to the Port A–D Address register. Setting the bits in the Port A–D Output Control sub-registers to 1 configures the specified port pins for opendrain operation. These sub-registers affect the pins directly and, as a result, alternate functions are also affected.

#### Table 21. Port A–D Output Control Sub-Registers (PxOC)

| BITS  | 7                             | 6                                                                                     | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|-------------------------------|---------------------------------------------------------------------------------------|------|------|------|------|------|------|

| FIELD | POC7                          | POC6                                                                                  | POC5 | POC4 | POC3 | POC2 | POC1 | POC0 |

| RESET | 00H (Ports A-C); 01H (Port D) |                                                                                       |      |      |      |      |      |      |

| R/W   | R/W                           | R/W R/W R/W R/W R/W R/W R/W                                                           |      |      |      |      |      |      |

| ADDR  | lf 03H i                      | If 03H in Port A–D Address Register, accessible through the Port A–D Control Register |      |      |      |      |      |      |

POC[7:0]—Port Output Control

These bits function independently of the alternate function bit and always disable the drains if set to 1.

0 = The source current is enabled for any output mode (unless overridden by the alternate

62

#### Interrupt Request 2 Register

The Interrupt Request 2 (IRQ2) register (Table 35) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 register to determine if any interrupt requests are pending.

#### Table 35. Interrupt Request 2 Register (IRQ2)

| BITS  | 7   | 6    | 5     | 4   | 3    | 2    | 1    | 0    |

|-------|-----|------|-------|-----|------|------|------|------|

| FIELD |     | Rese | erved |     | PC3I | PC2I | PC1I | PC0I |

| RESET | 0   | 0    | 0     | 0   | 0    | 0    | 0    | 0    |

| R/W   | R/W | R/W  | R/W   | R/W | R/W  | R/W  | R/W  | R/W  |

| ADDR  |     | FC6H |       |     |      |      |      |      |

Reserved—Must be 0.

PCxI—Port C Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port C pin x.

1 = An interrupt request from GPIO Port C pin x is awaiting service.

where x indicates the specific GPIO Port C pin number (0-3).

#### **IRQ0 Enable High and Low Bit Registers**

Table 36 describes the priority control for IRQ0. The IRQ0 Enable High and Low Bit registers (Table 37 and Table 38) form a priority encoded enabling for interrupts in the Interrupt Request 0 register.

#### Table 36. IRQ0 Enable and Priority Encoding

| IRQ0ENH[x] | IRQ0ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Medium      |

| 1          | 1          | Level 3  | High        |

where x indicates the register bits from 0–7.

Reserved—Must be 0.

C3ENL—Port C3 Interrupt Request Enable Low Bit C2ENL—Port C2 Interrupt Request Enable Low Bit C1ENL—Port C1 Interrupt Request Enable Low Bit C0ENL—Port C0 Interrupt Request Enable Low Bit

#### Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) register (Table 45) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A input pin.

Table 45. Interrupt Edge Select Register (IRQES)

| BITS  | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|------|------|------|------|------|------|------|------|

| FIELD | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |

| RESET | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| ADDR  | FCDH |      |      |      |      |      |      |      |

IES*x*—Interrupt Edge Select *x*

0 = An interrupt request is generated on the falling edge of the PAx input.

1 = An interrupt request is generated on the rising edge of the PAx input.

where *x* indicates the specific GPIO Port pin number (0 through 7).

#### **Shared Interrupt Select Register**

The Shared Interrupt Select (IRQSS) register (Table 46) determines the source of the PADxS interrupts. The Shared Interrupt Select register selects between Port A and alternate sources for the individual interrupts.

Because these shared interrupts are edge-triggered, it is possible to generate an interrupt just by switching from one shared source to another. For this reason, an interrupt must be disabled before switching between sources.

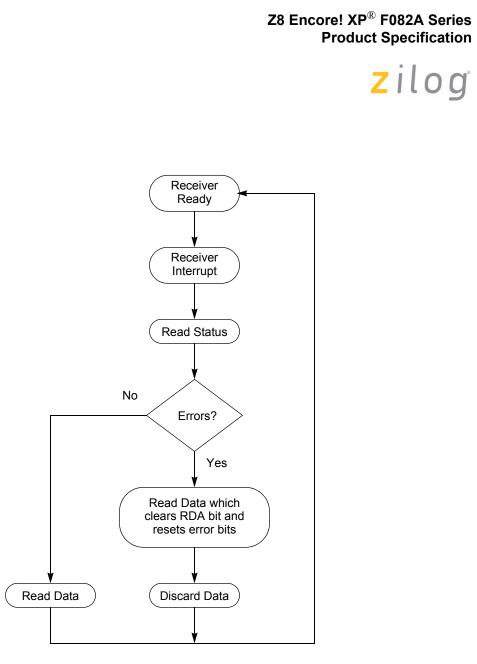

Figure 15. UART Receiver Interrupt Service Routine Flow

#### **Baud Rate Generator Interrupts**

If the baud rate generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud Rate Generator to function as an additional counter if the UART functionality is not employed.

### **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value

107

baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal, allowing the Endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

## Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined in Universal Asynchronous Receiver/Transmitter on page 97.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO Port alternate function for the corresponding pin.

value 63H to the Flash Control register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

#### **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programming is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information on bypassing the Flash Controller, refer to *Third-Party Flash Pro*gramming Support for Z8 Encore!<sup>®</sup> MCU Application Note (AN0117) available for download at <u>www.zilog.com</u>.

#### Flash Controller Behavior in DEBUG Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored.

- The Flash Sector Protect register is ignored for programming and erase operations.

- Programming operations are not limited to the page selected in the Page Select register.

- Bits in the Flash Sector Protect register can be written to one or zero.

- The second write of the Page Select register to unlock the Flash Controller is not necessary.

- The Page Select register can be written when the Flash Controller is unlocked.

- The Mass Erase command is enabled through the Flash Control register.

**Caution:** For security reasons, the Flash controller allows only a single page to be opened for write/erase. When writing multiple Flash pages, the flash controller must go through the unlock sequence again to select another page.

zilog | 17

read operations to illegal addresses. Also, the user code must pop the address byte off the stack.

The read routine uses 9 bytes of stack space in addition to the one byte of address pushed by the user. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS reads exhibit a non-uniform execution time. A read operation takes between 44  $\mu$ s and 489  $\mu$ s (assuming a 20 MHz system clock). Slower system clock speeds result in proportionally higher execution times.

NVDS byte reads from invalid addresses (those exceeding the NVDS array size) return 0xff. Illegal read operations have a 2  $\mu$ s execution time.

The status byte returned by the NVDS read routine is zero for successful read, as determined by a CRC check. If the status byte is non-zero, there was a corrupted value in the NVDS array at the location being read. In this case, the value returned in R0 is the byte most recently written to the array that does not have a CRC error.

#### **Power Failure Protection**

The NVDS routines employ error checking mechanisms to ensure a power failure endangers only the most recently written byte. Bytes previously written to the array are not perturbed.

A system reset (such as a pin reset or Watchdog Timer reset) that occurs during a write operation also perturbs the byte currently being written. All other bytes in the array are unperturbed.

#### Optimizing NVDS Memory Usage for Execution Speed

The NVDS read time varies drastically, this discrepancy being a trade-off for minimizing the frequency of writes that require post-write page erases (see Table 104). The NVDS read time of address N is a function of the number of writes to addresses other than N since the most recent write to address N, as well as the number of writes since the most recent page erase. Neglecting effects caused by page erases and results caused by the initial condition in which the NVDS is blank, a rule of thumb is that every write since the most recent page erase causes read times of unwritten addresses to increase by 1  $\mu$ s, up to a maximum of (511-NVDS SIZE)  $\mu$ s.

| Operation            | Minimum<br>Latency | Maximum<br>Latency |  |  |

|----------------------|--------------------|--------------------|--|--|

| Read (16 byte array) | 875                | 9961               |  |  |

| Read (64 byte array) | 876                | 8952               |  |  |

#### Table 104. NVDS Read Time

## **Crystal Oscillator**

The products in the Z8 Encore! XP<sup>®</sup> F082A Series contain an on-chip crystal oscillator for use with external crystals with 32 kHz to 20 MHz frequencies. In addition, the oscillator supports external RC networks with oscillation frequencies up to 4 MHz or ceramic resonators with frequencies up to 8 MHz. The on-chip crystal oscillator can be used to generate the primary system clock for the internal eZ8 CPU and the majority of the on-chip peripherals. Alternatively, the X<sub>IN</sub> input pin can also accept a CMOS-level clock input signal (32 kHz–20 MHz). If an external clock generator is used, the X<sub>OUT</sub> pin must be left unconnected. The Z8 Encore! XP F082A Series products do not contain an internal clock divider. The frequency of the signal on the X<sub>IN</sub> input pin determines the frequency of the system clock.

Note:

Although the XIN pin can be used as an input for an external clock generator, the CLKIN pin is better suited for such use (see System Clock Selection on page 187).

## **Operating Modes**

The Z8 Encore! XP F082A Series products support four oscillator modes:

- Minimum power for use with very low frequency crystals (32 kHz–1 MHz).

- Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 8 MHz).

- Maximum power for use with high frequency crystals (8 MHz to 20 MHz).

- On-chip oscillator configured for use with external RC networks (<4 MHz).

The oscillator mode is selected using user-programmable Flash Option Bits. See Flash Option Bits on page 153 for information.

## **Crystal Oscillator Operation**

The Flash Option bit XTLDIS controls whether the crystal oscillator is enabled during reset. The crystal may later be disabled after reset if a new oscillator has been selected as the system clock. If the crystal is manually enabled after reset through the OSCCTL register, the user code must wait at least 1000 crystal oscillator cycles for the crystal to stabilize. After this, the crystal oscillator may be selected as the system clock.

• Note: The stabilization time varies depending on the crystal or resonator used, as well as on the feedback network. See Table 111 for transconductance values to compute oscillator stabilization times.

PS022825-0908

**z**ilog<sup>®</sup>

203

Table 116 through Table 123 lists the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

| Mnemonic | Operands | Instruction                                   |  |  |

|----------|----------|-----------------------------------------------|--|--|

| ADC      | dst, src | Add with Carry                                |  |  |

| ADCX     | dst, src | Add with Carry using Extended Addressing      |  |  |

| ADD      | dst, src | Add                                           |  |  |

| ADDX     | dst, src | Add using Extended Addressing                 |  |  |

| CP       | dst, src | Compare                                       |  |  |

| CPC      | dst, src | Compare with Carry                            |  |  |

| CPCX     | dst, src | Compare with Carry using Extended Addressing  |  |  |

| CPX      | dst, src | Compare using Extended Addressing             |  |  |

| DA       | dst      | Decimal Adjust                                |  |  |

| DEC      | dst      | Decrement                                     |  |  |

| DECW     | dst      | Decrement Word                                |  |  |

| INC      | dst      | Increment                                     |  |  |

| INCW     | dst      | Increment Word                                |  |  |

| MULT     | dst      | Multiply                                      |  |  |

| SBC      | dst, src | Subtract with Carry                           |  |  |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |  |  |

| SUB      | dst, src | Subtract                                      |  |  |

| SUBX     | dst, src | Subtract using Extended Addressing            |  |  |

#### **Table 116. Arithmetic Instructions**

207

#### Table 123. Rotate and Shift Instructions (Continued)

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| SRA      | dst      | Shift Right Arithmetic |

| SRL      | dst      | Shift Right Logical    |

| SWAP     | dst      | Swap Nibbles           |

## eZ8 CPU Instruction Summary

Table 124 summarizes the eZ8 CPU instructions. The table identifies the addressing modes employed by the instruction, the effect upon the Flags register, the number of CPU clock cycles required for the instruction fetch, and the number of CPU clock cycles required for the instruction.

| Assembly<br>Mnemonic | Symbolic<br>Operation                                      | Addres        | Address Mode |                    | Flags |          |   |           |   |   | Fetch | Instr. |

|----------------------|------------------------------------------------------------|---------------|--------------|--------------------|-------|----------|---|-----------|---|---|-------|--------|

|                      |                                                            | dst           | src          | Opcode(s)<br>(Hex) | С     | Ζ        | S | ۷         | D | Н |       | Cycles |

| ADC dst, src         | $dst \gets dst + src + C$                                  | r             | r            | 12                 | *     | *        | * | *         | 0 | * | 2     | 3      |

|                      |                                                            | r             | lr           | 13                 | -     |          |   |           |   |   | 2     | 4      |

|                      |                                                            | R             | R            | 14                 | -     |          |   |           |   |   | 3     | 3      |

|                      |                                                            | R             | IR           | 15                 | -     |          |   |           |   |   | 3     | 4      |

|                      |                                                            | R             | IM           | 16                 | -     |          |   |           |   |   | 3     | 3      |

|                      |                                                            | IR            | IM           | 17                 | -     |          |   |           |   |   | 3     | 4      |

| ADCX dst, src        | $dst \gets dst + src + C$                                  | ER            | ER           | 18                 | *     | *        | * | *         | 0 | * | 4     | 3      |

|                      |                                                            | ER            | IM           | 19                 | -     |          |   |           |   |   | 4     | 3      |

| ADD dst, src         | $dst \gets dst + src$                                      | r             | r            | 02                 | *     | *        | * | *         | 0 | * | 2     | 3      |

|                      |                                                            | r             | lr           | 03                 | -     |          |   |           |   |   | 2     | 4      |

|                      |                                                            | R             | R            | 04                 | -     |          |   |           |   |   | 3     | 3      |

|                      |                                                            | R             | IR           | 05                 | -     |          |   |           |   |   | 3     | 4      |

|                      |                                                            | R             | IM           | 06                 | -     |          |   |           |   |   | 3     | 3      |

|                      |                                                            | IR            | IM           | 07                 | -     |          |   |           |   |   | 3     | 4      |

| ADDX dst, src        | $dst \gets dst + src$                                      | ER            | ER           | 08                 | *     | *        | * | *         | 0 | * | 4     | 3      |

|                      |                                                            | ER            | IM           | 09                 | -     |          |   |           |   |   | 4     | 3      |

| Flags Notation:      | * = Value is a function<br>– = Unaffected<br>X = Undefined | of the result | of the o     | peration.          |       | Re<br>Se |   | to (<br>1 | ) |   |       |        |

Table 124. eZ8 CPU Instruction Summary

# zilog

## **Electrical Characteristics**

The data in this chapter is pre-qualification and pre-characterization and is subject to change. Additional electrical characteristics may be found in the individual chapters.

## **Absolute Maximum Ratings**

Stresses greater than those listed in Table 126 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                                      | Minimum | Maximum | Units | Notes |

|----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                 | -40     | +105    | °C    |       |

| Storage temperature                                            | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>             | -0.3    | +5.5    | V     | 1     |

|                                                                | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$               | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin            | -5      | +5      | μA    |       |

| Maximum output current from active output pin                  | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0 °C to 70 °C                |         |         |       |       |

| Total power dissipation                                        |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$               |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0 °C to 70 °C               |         |         |       |       |

| Total power dissipation                                        |         | 430     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub> |         | 120     | mA    |       |

#### Table 126. Absolute Maximum Ratings

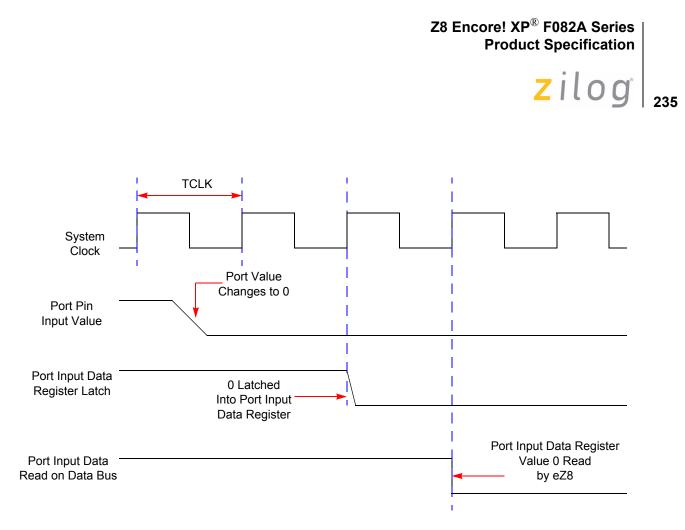

Figure 34. Port Input Sample Timing

|                     |                                                                                                          | Delay (ns) |         |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------|------------|---------|--|--|

| Parameter           | Abbreviation                                                                                             | Minimum    | Maximum |  |  |

| T <sub>S_PORT</sub> | Port Input Transition to XIN Rise Setup Time (Not pictured)                                              | 5          | _       |  |  |

| T <sub>H_PORT</sub> | XIN Rise to Port Input Transition Hold Time (Not pictured)                                               | 0          | -       |  |  |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to ensure Stop Mode<br>Recovery<br>(for GPIO Port Pins enabled as SMR sources) | 1 µs       |         |  |  |

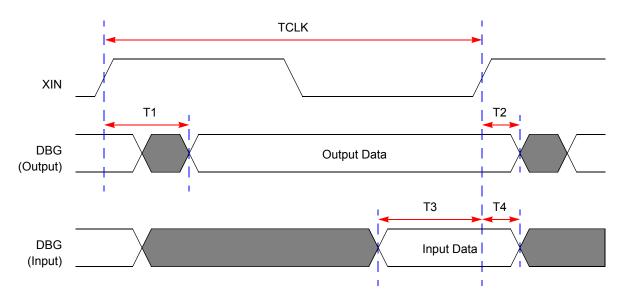

### **On-Chip Debugger Timing**

Figure 36 and Table 141 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

Figure 36. On-Chip Debugger Timing

|                |                                  | Delay (ns) |         |  |

|----------------|----------------------------------|------------|---------|--|

| Parameter      | Abbreviation                     | Minimum    | Maximum |  |

| DBG            |                                  |            |         |  |

| T <sub>1</sub> | XIN Rise to DBG Valid Delay      | -          | 15      |  |

| T <sub>2</sub> | XIN Rise to DBG Output Hold Time | 2          | _       |  |

| T <sub>3</sub> | DBG to XIN Rise Input Setup Time | 5          | _       |  |

| T <sub>4</sub> | DBG to XIN Rise Input Hold Time  | 5          | _       |  |

#### Table 141. On-Chip Debugger Timing

zilog <sub>248</sub>

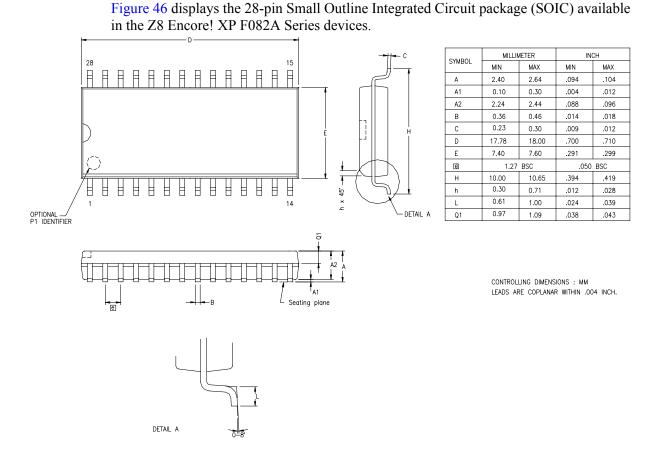

Figure 46. 28-Pin Small Outline Integrated Circuit Package (SOIC)

**z**ilog<sup>°</sup>

268

subtract with carry - extended addressing 203 SUBX 203 SWAP 207 swap nibbles 207 symbols, additional 202

## Т

TCM 204 **TCMX 204 Technical Support 271** test complement under mask 204 test complement under mask - extended addressing 204 test under mask 204 test under mask - extended addressing 204 timer signals 11 timers 69 architecture 69 block diagram 70 CAPTURE mode 77, 78, 85, 86 CAPTURE/COMPARE mode 81, 85 COMPARE mode 79.85 CONTINUOUS mode 71, 84 COUNTER mode 72, 73 COUNTER modes 84 GATED mode 80, 85 ONE-SHOT mode 70, 84 operating mode 70 PWM mode 74, 76, 85 reading the timer count values 82 reload high and low byte registers 87 timer control register definitions 83 timer output signal operation 82 timers 0-3 control registers 83, 84 high and low byte registers 87, 88 TM 204 TMX 204 transmit IrDA data 118 transmitting UART data-polled method 99 transmitting UART dat-interrupt-driven method 100

TRAP 206

## U

#### UART 7

architecture 97 baud rate generator 107 baud rates table 115 control register definitions 108 controller signals 11 data format 98 interrupts 105 multiprocessor mode 103 receiving data using interrupt-driven method 102 receiving data using the polled method 101 transmitting data usin the interrupt-driven method 100 transmitting data using the polled method 99 x baud rate high and low registers 114 x control 0 and control 1 registers 108 x status 0 and status 1 registers 111, 112 UxBRH register 114 UxBRL register 114 UxCTL0 register 108, 114 UxCTL1 register 109 UxRXD register 113 UxSTAT0 register 111 UxSTAT1 register 112 UxTXD register 113

## V

vector 201 Voltage Brownout reset (VBR) 26

## W

Watchdog Timer approximate time-out delay 91 approximate time-out delays 135 CNTL 26 control register 94, 136, 190