# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64 x 8                                                       |

| RAM Size                   | 512 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022ahh020ec    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Low-Power Modes**

The Z8 Encore! XP F082A Series products contain power-saving features. The highest level of power reduction is provided by the STOP mode, in which nearly all device functions are powered down. The next lower level of power reduction is provided by the HALT mode, in which the CPU is powered down.

Further power savings can be implemented by disabling individual peripheral blocks while in Active mode (defined as being in neither STOP nor HALT mode).

## **STOP Mode**

Executing the eZ8 CPU's STOP instruction places the device into STOP mode, powering down all peripherals except the Voltage Brownout detector, the Low-power Operational Amplifier and the Watchdog Timer. These three blocks may also be disabled for additional power savings. Specifically, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; XIN and XOUT (if previously enabled) are disabled, and PA0/PA1 revert to the states programmed by the GPIO registers.

- System clock is stopped.

- eZ8 CPU is stopped.

- Program counter (PC) stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control register.

- If enabled, the Watchdog Timer logic continues to operate.

- If enabled for operation in STOP mode by the associated Flash Option Bit, the Voltage Brownout protection circuit continues to operate.

- Low-power operational amplifier continues to operate if enabled by the Power Control register to do so.

- All other on-chip peripherals are idle.

To minimize current in STOP mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP mode using Stop Mode Recovery. For more information on Stop Mode Recovery, see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23.

# 63

### Table 37. IRQ0 Enable High Bit Register (IRQ0ENH)

| BITS  | 7        | 6                           | 5     | 4      | 3      | 2        | 1        | 0      |  |  |  |

|-------|----------|-----------------------------|-------|--------|--------|----------|----------|--------|--|--|--|

| FIELD | Reserved | T1ENH                       | T0ENH | U0RENH | U0TENH | Reserved | Reserved | ADCENH |  |  |  |

| RESET | 0        | 0                           | 0     | 0      | 0      | 0        | 0        | 0      |  |  |  |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W |       |        |        |          |          |        |  |  |  |

| ADDR  |          | FC1H                        |       |        |        |          |          |        |  |  |  |

Reserved—Must be 0.

T1ENH—Timer 1 Interrupt Request Enable High Bit T0ENH—Timer 0 Interrupt Request Enable High Bit U0RENH—UART 0 Receive Interrupt Request Enable High Bit U0TENH—UART 0 Transmit Interrupt Request Enable High Bit ADCENH—ADC Interrupt Request Enable High Bit

### Table 38. IRQ0 Enable Low Bit Register (IRQ0ENL)

| BITS  | 7        | 6                     | 5            | 4             | 3             | 2        | 1        | 0      |  |  |  |

|-------|----------|-----------------------|--------------|---------------|---------------|----------|----------|--------|--|--|--|

| FIELD | Reserved | T1ENL                 | <b>T0ENL</b> | <b>U0RENL</b> | <b>U0TENL</b> | Reserved | Reserved | ADCENL |  |  |  |

| RESET | 0        | 0                     | 0            | 0             | 0             | 0        | 0        | 0      |  |  |  |

| R/W   | R        | R R/W R/W R/W R R R/W |              |               |               |          |          |        |  |  |  |

| ADDR  |          | FC2H                  |              |               |               |          |          |        |  |  |  |

Reserved—Must be 0.

T1ENL—Timer 1 Interrupt Request Enable Low Bit T0ENL—Timer 0 Interrupt Request Enable Low Bit U0RENL—UART 0 Receive Interrupt Request Enable Low Bit U0TENL—UART 0 Transmit Interrupt Request Enable Low Bit ADCENL—ADC Interrupt Request Enable Low Bit

### **IRQ1 Enable High and Low Bit Registers**

Table 39 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers (Table 40 and Table 41) form a priority encoded enabling for interrupts in the Interrupt Request 1 register.

### Table 39. IRQ1 Enable and Priority Encoding

| IRQ1ENH[x] | IRQ1ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Medium      |

| 1          | 1          | Level 3  | High        |

|            |            |          |             |

where x indicates the register bits from 0–7.

### Table 40. IRQ1 Enable High Bit Register (IRQ1ENH)

| BITS  | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |  |  |  |

|-------|---------|---------|--------|--------|---------------|--------|--------|--------|--|--|--|

| FIELD | PA7VENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |  |  |  |

| RESET | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |  |  |  |

| R/W   | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |  |  |  |

| ADDR  |         | FC4H    |        |        |               |        |        |        |  |  |  |

PA7VENH—Port A Bit[7] or LVD Interrupt Request Enable High Bit PA6CENH—Port A Bit[7] or Comparator Interrupt Request Enable High Bit PAxENH—Port A Bit[x] Interrupt Request Enable High Bit

See Shared Interrupt Select (IRQSS) register for selection of either the LVD or the comparator as the interrupt source.

#### Table 41. IRQ1 Enable Low Bit Register (IRQ1ENL)

| BITS  | 7       | 6                           | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |

|-------|---------|-----------------------------|--------|--------|--------|--------|--------|--------|--|--|--|

| FIELD | PA7VENL | PA6CENL                     | PA5ENL | PA4ENL | PA3ENL | PA2ENL | PA1ENL | PA0ENL |  |  |  |

| RESET | 0       | 0                           | 0      | 0      | 0      | 0      | 0      | 0      |  |  |  |

| R/W   | R/W     | R/W R/W R/W R/W R/W R/W R/W |        |        |        |        |        |        |  |  |  |

| ADDR  |         | FC5H                        |        |        |        |        |        |        |  |  |  |

PA7VENL—Port A Bit[7] or LVD Interrupt Request Enable Low Bit PA6CENL—Port A Bit[6] or Comparator Interrupt Request Enable Low Bit PAxENL—Port A Bit[x] Interrupt Request Enable Low Bit

zilog ,

Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state for one system clock cycle (from Low to High or from High to Low) upon timer Reload. If it is appropriate to have the Timer Output make a state change at a One-Shot time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control Register to the start value before enabling ONE-SHOT mode. After starting the timer, set TPOL to the opposite bit value.

Follow the steps below for configuring a timer for ONE-SHOT mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for ONE-SHOT mode.

- Set the prescale value.

- Set the initial output level (High or Low) if using the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In ONE-SHOT mode, the system clock always provides the timer input. The timer period is given by the following equation:

$\label{eq:one-short} \text{ONE-SHOT Mode Time-Out Period } (s) = \frac{\text{Reload Value} - \text{Start Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

#### **CONTINUOUS Mode**

In CONTINUOUS mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below for configuring a timer for CONTINUOUS mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for CONTINUOUS mode.

- Set the prescale value.

- If using the Timer Output alternate function, set the initial output level (High or Low).

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS mode. After the first timer Reload in CONTINUOUS mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the Timer Output function) for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In CONTINUOUS mode, the system clock always provides the timer input. The timer period is given by the following equation:

CONTINUOUS Mode Time-Out Period (s) =  $\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT mode equation to determine the first time-out period.

#### **COUNTER Mode**

In COUNTER mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO Port pin Timer Input alternate function. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the Timer Input signal. In COUNTER mode, the prescaler is disabled.

**Caution:** The input frequency of the Timer Input signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the input signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

Upon reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

### 86

#### **CAPTURE RESTART mode**

0 = Count is captured on the rising edge of the Timer Input signal. 1 = Count is captured on the falling edge of the Timer Input signal.

# COMPARATOR COUNTER mode

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload. Also:

0 = Count is captured on the rising edge of the comparator output. 1 = Count is captured on the falling edge of the comparator output.

**Caution:** When the Timer Output alternate function TxOUT on a GPIO port pin is enabled, TxOUT changes to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Also, the Port data direction sub register is not needed to be set to output on TxOUT. Changing the TPOL bit with the timer enabled and running does not immediately change the TxOUT.

#### PRES—Prescale value

The timer input clock is divided by  $2^{PRES}$ , where PRES can be set from 0 to 7. The prescaler is reset each time the Timer is disabled. This reset ensures proper clock division each time the Timer is restarted.

000 = Divide by 1 001 = Divide by 2 010 = Divide by 4 011 = Divide by 8 100 = Divide by 16 101 = Divide by 32 110 = Divide by 64 111 = Divide by 128

#### TMODE—Timer mode

This field along with the TMODEHI bit in TxCTL0 register determines the operating mode of the timer. TMODEHI is the most significant bit of the Timer mode selection value. The entire operating mode bits are expressed as {TMODEHI, TMODE[2:0]}. The TMODEHI is bit 7 of the TxCTL0 register while TMODE[2:0] is the lower 3 bits of the TxCTL1 register.

- 0000 = ONE-SHOT mode

- 0001 = CONTINUOUS mode

- 0010 = COUNTER mode

- 0011 = PWM SINGLE OUTPUT mode

- 0100 = CAPTURE mode

- 0101 = COMPARE mode

- 0110 = GATED mode

- 0111 = CAPTURE/COMPARE mode

# zilog | 11

### **UART Address Compare Register**

The UART Address Compare (UxADDR) register stores the multi-node network address of the UART (see Table 67). When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare register. Receive interrupts and RDA assertions only occur in the event of a match.

### Table 67. UART Address Compare Register (U0ADDR)

| BITS  | 7   | 6                           | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|-----|-----------------------------|---|----|----|---|---|---|--|--|

| FIELD |     | COMP_ADDR                   |   |    |    |   |   |   |  |  |

| RESET | 0   | 0                           | 0 | 0  | 0  | 0 | 0 | 0 |  |  |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |    |    |   |   |   |  |  |

| ADDR  |     |                             |   | F4 | 5H |   |   |   |  |  |

COMP\_ADDR—Compare Address

This 8-bit value is compared to incoming address bytes.

## UART Baud Rate High and Low Byte Registers

The UART Baud Rate High (UxBRH) and Low Byte (UxBRL) registers (Table 68 and Table 69) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART.

### Table 68. UART Baud Rate High Byte Register (U0BRH)

| BITS  | 7   | 6                           | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|-----|-----------------------------|---|----|----|---|---|---|--|--|

| FIELD |     | BRH                         |   |    |    |   |   |   |  |  |

| RESET | 1   | 1 1 1 1 1 1 1 1             |   |    |    |   |   |   |  |  |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |    |    |   |   |   |  |  |

| ADDR  |     |                             |   | F4 | 6H |   |   |   |  |  |

#### Table 69. UART Baud Rate Low Byte Register (U0BRL)

| BITS  | 7   | 6                           | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|-----|-----------------------------|---|----|----|---|---|---|--|--|

| FIELD |     | BRL                         |   |    |    |   |   |   |  |  |

| RESET | 1   | 1 1 1 1 1 1 1 1             |   |    |    |   |   |   |  |  |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |    |    |   |   |   |  |  |

| ADDR  |     |                             |   | F4 | 7H |   |   |   |  |  |

# zilog<sup>®</sup> |<sub>11</sub>

The UART data rate is calculated using the following equation:

UART Baud Rate (bits/s) =

$$\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$$

For a given UART data rate, calculate the integer baud rate divisor value using the following equation:

UART Baud Rate Divisor Value (BRG) = Round

$$\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$$

The baud rate error relative to the acceptable baud rate is calculated using the following equation:

UART Baud Rate Error (%) =

$$100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$$

For reliable communication, the UART baud rate error must never exceed 5 percent. Table 70 provides information on the data rate errors for popular baud rates and commonly used crystal oscillator frequencies.

| 10.0 MHz Sy              | stem Clock               |                      |              | 5.5296 MHz \$            | System Clock             |                      |              |

|--------------------------|--------------------------|----------------------|--------------|--------------------------|--------------------------|----------------------|--------------|

| Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) | Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) |

| 1250.0                   | N/A                      | N/A                  | N/A          | 1250.0                   | N/A                      | N/A                  | N/A          |

| 625.0                    | 1                        | 625.0                | 0.00         | 625.0                    | N/A                      | N/A                  | N/A          |

| 250.0                    | 3                        | 208.33               | -16.67       | 250.0                    | 1                        | 345.6                | 38.24        |

| 115.2                    | 5                        | 125.0                | 8.51         | 115.2                    | 3                        | 115.2                | 0.00         |

| 57.6                     | 11                       | 56.8                 | -1.36        | 57.6                     | 6                        | 57.6                 | 0.00         |

| 38.4                     | 16                       | 39.1                 | 1.73         | 38.4                     | 9                        | 38.4                 | 0.00         |

| 19.2                     | 33                       | 18.9                 | 0.16         | 19.2                     | 18                       | 19.2                 | 0.00         |

| 9.60                     | 65                       | 9.62                 | 0.16         | 9.60                     | 36                       | 9.60                 | 0.00         |

| 4.80                     | 130                      | 4.81                 | 0.16         | 4.80                     | 72                       | 4.80                 | 0.00         |

| 2.40                     | 260                      | 2.40                 | -0.03        | 2.40                     | 144                      | 2.40                 | 0.00         |

| 1.20                     | 521                      | 1.20                 | -0.03        | 1.20                     | 288                      | 1.20                 | 0.00         |

| 0.60                     | 1042                     | 0.60                 | -0.03        | 0.60                     | 576                      | 0.60                 | 0.00         |

| 0.30                     | 2083                     | 0.30                 | 0.2          | 0.30                     | 1152                     | 0.30                 | 0.00         |

|                          |                          |                      |              | -                        |                          |                      |              |

### Table 70. UART Baud Rates

## Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

Zilog

### **Receiving IrDA Data**

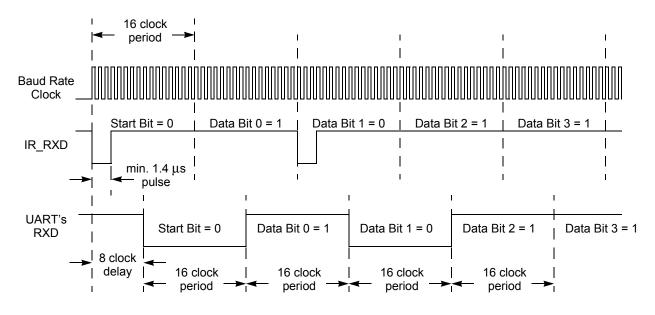

Data received from the infrared transceiver using the IR\_RXD signal through the RXD pin is decoded by the Infrared Endec and passed to the UART. The UART's baud rate clock is used by the Infrared Endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 18 displays data reception. When the Infrared Endec is enabled, the UART's RXD signal is internal to the Z8 Encore! XP<sup>®</sup> F082A Series products while the IR\_RXD signal is received through the RXD pin.

Figure 18. IrDA Data Reception

### **Infrared Data Reception**

**Caution:** The system clock frequency must be at least 1.0 MHz to ensure proper reception of the  $1.4 \,\mu s$  minimum width pulses allowed by the IrDA standard.

### **Endec Receiver Synchronization**

The IrDA receiver uses a local baud rate clock counter (0 to 15 clock periods) to generate an input stream for the UART and to create a sampling window for detection of incoming pulses. The generated UART input (UART RXD) is delayed by 8 baud rate clock periods with respect to the incoming IrDA data stream. When a falling edge in the input data stream is detected, the Endec counter is reset. When the count reaches a value of 8, the UART RXD value is updated to reflect the value of the decoded data. When the count reaches 12 baud clock periods, the sampling window for the next incoming pulse opens. The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the Endec a sampling window of minus four

zilog

baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal, allowing the Endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

# Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined in Universal Asynchronous Receiver/Transmitter on page 97.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO Port alternate function for the corresponding pin.

## **ADC Control/Status Register 1**

The ADC Control/Status Register 1 (ADCCTL1) configures the input buffer stage, enables the threshold interrupts and contains the status of both threshold triggers. It is also used to select the voltage reference configuration.

### Table 72. ADC Control/Status Register 1 (ADCCTL1)

| BITS  | 7       | 6   | 5                     | 4   | 3   | 2   | 1   | 0   |  |

|-------|---------|-----|-----------------------|-----|-----|-----|-----|-----|--|

| FIELD | REFSELH |     | Reserved BUFMODE[2:0] |     |     |     |     |     |  |

| RESET | 1       | 0   | 0                     | 0   | 0   | 0 0 |     |     |  |

| R/W   | R/W     | R/W | R/W                   | R/W | R/W | R/W | R/W | R/W |  |

| ADDR  |         |     |                       | F7  | 1H  |     | ·   |     |  |

REFSELH—Voltage Reference Level Select High Bit; in conjunction with the Low bit (REFSELL) in ADC Control Register 0, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL}; this reference is independent of the Comparator reference.

00= Internal Reference Disabled, reference comes from external pin

01= Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

11= Reserved

BUFMODE[2:0] - Input Buffer Mode Select

000 =Single-ended, unbuffered input

- 001 = Single-ended, buffered input with unity gain

- 010 = Reserved

- 011 = Reserved

- 100 = Differential, unbuffered input

- 101 = Differential, buffered input with unity gain

- 110 = Reserved

- 111 = Reserved

# ADC Data High Byte Register

The ADC Data High Byte (ADCD\_H) register contains the upper eight bits of the ADC output. The output is an 13-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

zilog

value 63H to the Flash Control register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

### **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programming is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information on bypassing the Flash Controller, refer to *Third-Party Flash Pro*gramming Support for Z8 Encore!<sup>®</sup> MCU Application Note (AN0117) available for download at <u>www.zilog.com</u>.

### Flash Controller Behavior in DEBUG Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored.

- The Flash Sector Protect register is ignored for programming and erase operations.

- Programming operations are not limited to the page selected in the Page Select register.

- Bits in the Flash Sector Protect register can be written to one or zero.

- The second write of the Page Select register to unlock the Flash Controller is not necessary.

- The Page Select register can be written when the Flash Controller is unlocked.

- The Mass Erase command is enabled through the Flash Control register.

**Caution:** For security reasons, the Flash controller allows only a single page to be opened for write/erase. When writing multiple Flash pages, the flash controller must go through the unlock sequence again to select another page.

If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

DBG  $\leftarrow$  12H DBG  $\leftarrow$  1-5 byte opcode

# **On-Chip Debugger Control Register Definitions**

### **OCD Control Register**

The OCD Control register controls the state of the On-Chip Debugger. This register is used to enter or exit DEBUG mode and to enable the BRK instruction. It can also reset the Z8 Encore! XP<sup>®</sup> F082A Series device.

A reset and stop function can be achieved by writing \$1H to this register. A reset and go function can be achieved by writing \$1H to this register. If the device is in DEBUG mode, a run function can be implemented by writing \$0H to this register.

### Table 106. OCD Control Register (OCDCTL)

| BITS  | 7       | 6     | 5      | 4 | 3   | 2 | 1 | 0   |

|-------|---------|-------|--------|---|-----|---|---|-----|

| FIELD | DBGMODE | BRKEN | DBGACK |   | RST |   |   |     |

| RESET | 0       | 0     | 0      | 0 | 0   | 0 | 0 | 0   |

| R/W   | R/W     | R/W   | R/W    | R | R   | R | R | R/W |

### DBGMODE—DEBUG Mode

The device enters DEBUG mode when this bit is 1. When in DEBUG mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is automatically set when a BRK instruction is decoded and Breakpoints are enabled. If the Flash Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device. It cannot be written to 0.

0 = The Z8 Encore! XP F082A Series device is operating in NORMAL mode.

1 = The Z8 Encore! XP F082A Series device is in DEBUG mode.

### BRKEN—Breakpoint Enable

This bit controls the behavior of the BRK instruction (opcode 00H). By default, Breakpoints are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1, when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL register is automatically set to 1.

0 = Breakpoints are disabled.

1 = Breakpoints are enabled.

Z8 Encore! XP<sup>®</sup> F082A Series | **Product Specification**

### Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

204

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| ТСМ      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |

Table 118. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-Increment Addresses       |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

### Table 119. CPU Control Instructions

| Mnemonic | Operands | Instruction           |  |  |  |  |  |

|----------|----------|-----------------------|--|--|--|--|--|

| ATM      | _        | Atomic Execution      |  |  |  |  |  |

| CCF      | _        | Complement Carry Flag |  |  |  |  |  |

| DI       | _        | Disable Interrupts    |  |  |  |  |  |

| EI       | _        | Enable Interrupts     |  |  |  |  |  |

| HALT     | _        | Halt Mode             |  |  |  |  |  |

| NOP      | _        | No Operation          |  |  |  |  |  |

| RCF      | _        | Reset Carry Flag      |  |  |  |  |  |

**z**ilog<sup>°</sup>

| 21 | Λ |

|----|---|

| ~  | 4 |

| Assembly        | Symbolic<br>Operation                                                                                                        | Addre        | Address Mode Opcode |           | s) Flags |          |   |           |   | Fetch | Instr.   |   |

|-----------------|------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|-----------|----------|----------|---|-----------|---|-------|----------|---|

| Mnemonic        |                                                                                                                              | dst          | src                 | (Hex)     | С        | Ζ        | S | ۷         | D | Н     | Cycles C |   |

| SUBX dst, src   | $dst \gets dst - src$                                                                                                        | ER           | ER                  | 28        | *        | *        | * | *         | 1 | *     | 4        | 3 |

|                 |                                                                                                                              | ER           | IM                  | 29        | -        |          |   |           |   |       | 4        | 3 |

| SWAP dst        | $dst[7:4] \leftrightarrow dst[3:0]$                                                                                          | R            |                     | F0        | Х        | *        | * | Х         | _ | -     | 2        | 2 |

|                 |                                                                                                                              | IR           |                     | F1        | -        |          |   |           |   |       | 2        | 3 |

| TCM dst, src    | (NOT dst) AND src                                                                                                            | r            | r                   | 62        | _        | *        | * | 0         | _ | _     | 2        | 3 |

|                 |                                                                                                                              | r            | lr                  | 63        | -        |          |   |           |   |       | 2        | 4 |

|                 |                                                                                                                              | R            | R                   | 64        | -        |          |   |           |   |       | 3        | 3 |

|                 |                                                                                                                              | R            | IR                  | 65        | -        |          |   |           |   |       | 3        | 4 |

|                 |                                                                                                                              | R            | IM                  | 66        | -        |          |   |           |   |       | 3        | 3 |

|                 |                                                                                                                              | IR           | IM                  | 67        | -        |          |   |           |   |       | 3        | 4 |

| TCMX dst, src   | (NOT dst) AND src                                                                                                            | ER           | ER                  | 68        | _        | *        | * | 0         | _ | -     | 4        | 3 |

|                 |                                                                                                                              | ER           | IM                  | 69        | -        |          |   |           |   |       | 4        | 3 |

| TM dst, src     | dst AND src                                                                                                                  | r            | r                   | 72        | -        | *        | * | 0         | - | -     | 2        | 3 |

|                 |                                                                                                                              | r            | lr                  | 73        | -        |          |   |           |   |       | 2        | 4 |

|                 |                                                                                                                              | R            | R                   | 74        | -        |          |   |           |   |       | 3        | 3 |

|                 |                                                                                                                              | R            | IR                  | 75        | -        |          |   |           |   |       | 3        | 4 |

|                 |                                                                                                                              | R            | IM                  | 76        | -        |          |   |           |   |       | 3        | 3 |

|                 |                                                                                                                              | IR           | IM                  | 77        | -        |          |   |           |   |       | 3        | 4 |

| TMX dst, src    | dst AND src                                                                                                                  | ER           | ER                  | 78        | -        | *        | * | 0         | - | -     | 4        | 3 |

|                 |                                                                                                                              | ER           | IM                  | 79        | -        |          |   |           |   |       | 4        | 3 |

| TRAP Vector     | $SP \leftarrow SP - 2$<br>@SP $\leftarrow$ PC<br>$SP \leftarrow SP - 1$<br>@SP $\leftarrow$ FLAGS<br>PC $\leftarrow$ @Vector |              | Vector              | F2        | _        | _        | _ | _         | _ | _     | 2        | 6 |

| WDT             |                                                                                                                              |              |                     | 5F        | _        | _        | _ | _         | _ | _     | 1        | 2 |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined                                                                 | of the resul | t of the o          | peration. |          | Re<br>Se |   | to (<br>1 | ) |       |          |   |

### Table 124. eZ8 CPU Instruction Summary (Continued)

zilog

228

|                    |                                                         | T <sub>A</sub> = - | = 2.7 V to<br>40 °C to +⁄<br>otherwise |            |       |                                                   |

|--------------------|---------------------------------------------------------|--------------------|----------------------------------------|------------|-------|---------------------------------------------------|

| Symbol             | Parameter                                               | Minimum            | Typical                                | Maximum    | Units | Conditions                                        |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (High Speed) |                    | 5.53                                   |            | MHz   | V <sub>DD</sub> = 3.3 V<br>T <sub>A</sub> = 30 °C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (Low Speed)  |                    | 32.7                                   |            | kHz   | V <sub>DD</sub> = 3.3 V<br>T <sub>A</sub> = 30 °C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Error                  |                    | <u>+</u> 1                             | <u>+</u> 4 | %     |                                                   |

| T <sub>IPOST</sub> | Internal Precision Oscillator<br>Startup Time           |                    | 3                                      |            | μs    |                                                   |

### Table 130. Internal Precision Oscillator Electrical Characteristics

**z**ilog<sup>°</sup>

### 229

# **On-Chip Peripheral AC and DC Electrical Characteristics**

### Table 131. Power-On Reset and Voltage Brownout Electrical Characteristics and Timing

|                   | Parameter                                                                                                      | T <sub>A</sub> = - | 40 °C to +           | 105 °C  |       |                                                                                                       |  |

|-------------------|----------------------------------------------------------------------------------------------------------------|--------------------|----------------------|---------|-------|-------------------------------------------------------------------------------------------------------|--|

| Symbol            |                                                                                                                | Minimum            | Typical <sup>1</sup> | Maximum | Units | Conditions                                                                                            |  |

| V <sub>POR</sub>  | Power-On Reset<br>Voltage Threshold                                                                            | 2.20               | 2.45                 | 2.70    | V     | V <sub>DD</sub> = V <sub>POR</sub>                                                                    |  |

| V <sub>VBO</sub>  | Voltage Brownout Reset<br>Voltage Threshold                                                                    | 2.15               | 2.40                 | 2.65    | V     | $V_{DD} = V_{VBO}$                                                                                    |  |

|                   | $V_{POR}$ to $V_{VBO}$ hysteresis                                                                              |                    | 50                   | 75      | mV    |                                                                                                       |  |

|                   | Starting V <sub>DD</sub> voltage to<br>ensure valid Power-On<br>Reset.                                         | -                  | $V_{SS}$             | -       | V     |                                                                                                       |  |

| T <sub>ANA</sub>  | Power-On Reset Analog<br>Delay                                                                                 | -                  | 70                   | -       | μs    | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub> Digital<br>Reset delay follows T <sub>ANA</sub> |  |

| T <sub>POR</sub>  | Power-On Reset Digital<br>Delay                                                                                |                    | 16                   |         | μs    | 66 Internal Precision<br>Oscillator cycles + IPO<br>startup time (T <sub>IPOST</sub> )                |  |

| T <sub>POR</sub>  | Power-On Reset Digital<br>Delay                                                                                |                    | 1                    |         | ms    | 5000 Internal Precision<br>Oscillator cycles                                                          |  |

| T <sub>SMR</sub>  | Stop Mode Recovery<br>with crystal oscillator<br>disabled                                                      |                    | 16                   |         | μs    | 66 Internal Precision<br>Oscillator cycles                                                            |  |

| T <sub>SMR</sub>  | Stop Mode Recovery<br>with crystal oscillator<br>enabled                                                       |                    | 1                    |         | ms    | 5000 Internal Precision<br>Oscillator cycles                                                          |  |

| T <sub>VBO</sub>  | Voltage Brownout Pulse<br>Rejection Period                                                                     | _                  | 10                   | -       | μs    | Period of time in which V <sub>DD</sub><br>< V <sub>VBO</sub> without generating<br>a Reset.          |  |

| T <sub>RAMP</sub> | Time for V <sub>DD</sub> to<br>transition from V <sub>SS</sub> to<br>V <sub>POR</sub> to ensure valid<br>Reset | 0.10               | _                    | 100     | ms    |                                                                                                       |  |

| T <sub>SMP</sub>  | Stop Mode Recovery pin pulse rejection period                                                                  |                    | 20                   |         | ns    | For any SMR pin or for the Reset pin when it is asserted in STOP mode.                                |  |

only and are not tested in production.

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

zilog <sub>247</sub>

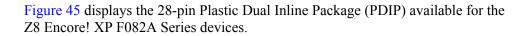

Note: ZILOG supplies both options for production. Component layout PCB design should cover bigger option 01.

### Figure 45. 28-Pin Plastic Dual Inline Package (PDIP)

### Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

261

# Index

## **Symbols**

# 202 % 202 @ 202

## **Numerics**

10-bit ADC 7 40-lead plastic dual-inline package 248, 249

# Α

absolute maximum ratings 221 AC characteristics 227 ADC 203 architecture 121 automatic power-down 122 block diagram 122 continuous conversion 124 control register 130, 132 control register definitions 130 data high byte register 132 data low bits register 133 electrical characteristics and timing 231 operation 122 single-shot conversion 123 ADCCTL register 130, 132 ADCDH register 132 ADCDL register 133 ADCX 203 ADD 203 add - extended addressing 203 add with carry 203 add with carry - extended addressing 203 additional symbols 202 address space 15 ADDX 203 analog signals 12 analog-to-digital converter (ADC) 121 AND 205

ANDX 205 arithmetic instructions 203 assembly language programming 199 assembly language syntax 200

# В

B 202 b 201 baud rate generator, UART 107 **BCLR 204** binary number suffix 202 **BIT 204** bit 201 clear 204 manipulation instructions 204 set 204 set or clear 204 swap 204 test and jump 206 test and jump if non-zero 206 test and jump if zero 206 bit jump and test if non-zero 206 bit swap 206 block diagram 4 block transfer instructions 204 **BRK 206** BSET 204 BSWAP 204, 206 **BTJ 206 BTJNZ 206 BTJZ 206**

# С

CALL procedure 206 CAPTURE mode 85, 86 CAPTURE/COMPARE mode 85 cc 201 CCF 204 characteristics, electrical 221 clear 205 CLR 205 COM 205