# E·XFL

#### Zilog - Z8F022AHH020EC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | IrDA, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT  |

| Number of I/O              | 17                                                            |

| Program Memory Size        | 2KB (2K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | 64 x 8                                                        |

| RAM Size                   | 512 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | A/D 7x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                |

| Supplier Device Package    |                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022ahh020ec00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Pin Description**

The Z8 Encore! XP<sup>®</sup> F082A Series products are available in a variety of packages styles and pin configurations. This chapter describes the signals and available pin configurations for each of the package styles. For information on physical package specifications, see Packaging on page 241.

#### **Available Packages**

The following package styles are available for each device in the Z8 Encore! XP F082A Series product line:

- SOIC

- 8-, 20-, and 28-pin

- PDIP

- 8-, 20-, and 28-pin

- SSOP

- 20- and 28- pin

- QFN (this is an MLF-S, a QFN style package with an 8-pin SOIC footprint)

- 8-pin

In addition, the Z8 Encore! XP F082A Series devices are available both with and without advanced analog capability (ADC, temperature sensor and op amp). Devices Z8F082A, Z8F042A, Z8F022A, and Z8F012A contain the advanced analog, while devices Z8F081A, Z8F041A, Z8F021A, and Z8F011A do not have the advanced analog capability.

#### **Pin Configurations**

Figure 2 through Figure 4 display the pin configurations for all the packages available in the Z8 Encore! XP F082A Series. See Table 2 on page 11 for a description of the signals. The analog input alternate functions (ANAx) are not available on the Z8F081A, Z8F041A, Z8F021A, and Z8F011A devices. The analog supply pins (AV<sub>DD</sub> and AV<sub>SS</sub>) are also not available on these parts, and are replaced by PB6 and PB7.

At reset, all Port A, B and C pins default to an input state. In addition, any alternate functionality is not enabled, so the pins function as general purpose input ports until programmed otherwise. At powerup, the PD0 pin defaults to the RESET alternate function.

**z**ilog<sup>°</sup>

#### Table 3. Pin Characteristics (20- and 28-pin Devices) (Continued)

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal Pull-<br>up<br>or Pull-down                    | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                    | 5 V<br>Tolerance                        |

|--------------------|-----------|-----------------------------------|---------------------------------------|--------------------|---------------------------------------------------------|------------------------------|---------------------------------------------------------|-----------------------------------------|

| PC[7:0]            | I/O       | I                                 | N/A                                   | Yes                | Programmable<br>Pull-up                                 | Yes                          | Yes,<br>Programmable                                    | PC[7:3]<br>unless<br>pullups<br>enabled |

| RESET/PD0          | I/O       | I/O <u>(defaults</u><br>to RESET) | Low (in<br>Reset<br>mode)             | Yes (PD0<br>only)  | Programmable<br>for PD0 <u>; always</u><br>on for RESET | Yes                          | Programmable<br>for PD0 <u>; always</u><br>on for RESET | Yes, unless<br>pullups<br>enabled       |

| VDD                | N/A       | N/A                               | N/A                                   | N/A                |                                                         |                              | N/A                                                     | N/A                                     |

| VSS                | N/A       | N/A                               | N/A                                   | N/A                |                                                         |                              | N/A                                                     | N/A                                     |

**Note:** *PB6 and PB7 are available only in those devices without ADC.*

#### Table 4. Pin Characteristics (8-Pin Devices)

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                                                      | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal Pull-<br>up<br>or Pull-down            | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                            | 5 V<br>Tolerance                   |

|--------------------|-----------|-------------------------------------------------------------------------|---------------------------------------|--------------------|-------------------------------------------------|------------------------------|-------------------------------------------------|------------------------------------|

| PA0/DBG            | I/O       | I (but can<br>change<br>during reset<br>if key<br>sequence<br>detected) | N/A                                   | Yes                | Programmable<br>Pull-up                         | Yes                          | Yes,<br>Programmable                            | Yes, unless<br>pull-ups<br>enabled |

| PA1                | I/O       | I                                                                       | N/A                                   | Yes                | Programmable<br>Pull-up                         | Yes                          | Yes,<br>Programmable                            | Yes, unless<br>pull-ups<br>enabled |

| RESET/PA2          | I/O       | I/O <u>(defaults</u><br>to RESET)                                       | Low (in<br>Reset<br>mode)             | Yes                | Programmable<br>for PA2; always<br>on for RESET | Yes                          | Programmable<br>for PA2; always<br>on for RESET | Yes, unless<br>pull-ups<br>enabled |

| PA[5:3]            | I/O       | I                                                                       | N/A                                   | Yes                | Programmable<br>Pull-up                         | Yes                          | Yes,<br>Programmable                            | Yes, unless<br>pull-ups<br>enabled |

| V <sub>DD</sub>    | N/A       | N/A                                                                     | N/A                                   | N/A                | N/A                                             | N/A                          | N/A                                             | N/A                                |

| V <sub>SS</sub>    | N/A       | N/A                                                                     | N/A                                   | N/A                | N/A                                             | N/A                          | N/A                                             | N/A                                |

14

**z**ilog<sup>°</sup>

addresses outside the available Flash memory addresses returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 5 describes the Program Memory Maps for the Z8 Encore! XP F082A Series products.

| Program Memory Address (Hex) | Function                     |  |  |  |

|------------------------------|------------------------------|--|--|--|

| Z8F082A and Z8F081A Products |                              |  |  |  |

| 0000–0001                    | Flash Option Bits            |  |  |  |

| 0002–0003                    | Reset Vector                 |  |  |  |

| 0004–0005                    | WDT Interrupt Vector         |  |  |  |

| 0006–0007                    | Illegal Instruction Trap     |  |  |  |

| 0008–0037                    | Interrupt Vectors*           |  |  |  |

| 0038–0039                    | Reserved                     |  |  |  |

| 003A-003D                    | Oscillator Fail Trap Vectors |  |  |  |

| 003E-1FFF                    | Program Memory               |  |  |  |

| Z8F042A and Z8F041A Products |                              |  |  |  |

| 0000–0001                    | Flash Option Bits            |  |  |  |

| 0002–0003                    | Reset Vector                 |  |  |  |

| 0004–0005                    | WDT Interrupt Vector         |  |  |  |

| 0006–0007                    | Illegal Instruction Trap     |  |  |  |

| 0008–0037                    | Interrupt Vectors*           |  |  |  |

| 0038–0039                    | Reserved                     |  |  |  |

| 003A-003D                    | Oscillator Fail Trap Vectors |  |  |  |

| 003E-0FFF                    | Program Memory               |  |  |  |

Table 5. Z8 Encore! XP F082A Series Program Memory Maps

16

mation Area data rather than the Program Memory data. Access to the Flash Information Area is read-only.

| Program Memory Address (Hex) | Function                                                                                  |

|------------------------------|-------------------------------------------------------------------------------------------|

| FE00–FE3F                    | Zilog Option Bits/Calibration Data                                                        |

| FE40-FE53                    | Part Number<br>20-character ASCII alphanumeric code<br>Left justified and filled with FFH |

| FE54–FE5F                    | Reserved                                                                                  |

| FE60–FE7F                    | Zilog Calibration Data                                                                    |

| FE80–FFFF                    | Reserved                                                                                  |

Table 6. Z8 Encore! XP F082A Series Flash Memory Information Area Map

PAFS1[7:0]—Port Alternate Function Set 1 0 = Port Alternate Function selected as defined in Table 14 and Table 15 on page 44. 1 = Port Alternate Function selected as defined in Table 14 and Table 15 on page 44.

#### Port A–D Alternate Function Set 2 Sub-Registers

The Port A–D Alternate Function Set 2 sub-register (Table 26) is accessed through the Port A–D Control register by writing 08H to the Port A–D Address register. The Alternate Function Set 2 sub-registers selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register is defined in Table 15.

• Note: Alternate function selection on port pins must also be enabled as described in Port A–D Alternate Function Sub-Registers on page 47.

| BITS  | 7                                                                  | 6                                                                                     | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------|---|---|---|---|---|---|--|--|

| FIELD | PAFS27 PAFS26 PAFS25 PAFS24 PAFS23 PAFS22 PAFS21 PAFS20            |                                                                                       |   |   |   |   |   |   |  |  |

| RESET | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device) |                                                                                       |   |   |   |   |   |   |  |  |

| R/W   | R/W R/W R/W R/W R/W R/W R/W                                        |                                                                                       |   |   |   |   |   |   |  |  |

| ADDR  | lf 08H i                                                           | If 08H in Port A–D Address Register, accessible through the Port A–D Control Register |   |   |   |   |   |   |  |  |

Table 26. Port A–D Alternate Function Set 2 Sub-Registers (PxAFS2)

PAFS2[7:0]—Port Alternate Function Set 2

0 = Port Alternate Function selected as defined in Table 15.

1 = Port Alternate Function selected as defined in Table 15.

#### Port A–C Input Data Registers

Reading from the Port A–C Input Data registers (Table 27) returns the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those missing on the 8- and 28-pin packages, as well as those missing on the ADC-enabled 28-pin packages.

| Table 27. Port A–C Input Data Registers (PxIN) | Table 27. | Port A–C | Input Data | Registers | (PxIN) |

|------------------------------------------------|-----------|----------|------------|-----------|--------|

|------------------------------------------------|-----------|----------|------------|-----------|--------|

| BITS      | 7                | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|-----------|------------------|------|------|------|------|------|------|------|--|

| FIELD     | PIN7             | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |

| RESET     | Х                | Х    | Х    | Х    | Х    | Х    | Х    | Х    |  |

| R/W       | R                | R    | R    | R    | R    | R    | R    | R    |  |

| ADDR      | FD2H, FD6H, FDAH |      |      |      |      |      |      |      |  |

| X = Undef | ined.            |      |      |      |      |      |      |      |  |

zilog',

0001H and counting resumes. The INPCAP bit in TxCTL0 register is cleared to indicate the timer interrupt is not caused by an input capture event.

Follow the steps below for configuring a timer for CAPTURE RESTART mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for CAPTURE RESTART mode by writing the TMODE bits in the TxCTL1 register and the TMODEHI bit in TxCTL0 register.

- Set the prescale value.

- Set the Capture edge (rising or falling) for the Timer Input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. This allows the software to determine if interrupts were generated by either a capture event or a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

In CAPTURE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **COMPARE Mode**

In COMPARE mode, the timer counts up to the 16-bit maximum Compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Compare value, the timer generates an interrupt and counting continues (the timer value is not reset to 0001H). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon Compare.

If the Timer reaches FFFFH, the timer rolls over to 0000H and continue counting.

0 = No framing error occurred. 1 = A framing error occurred.

BRKD—Break Detect

This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data register clears this bit. 0 = No break occurred.

1 = A break occurred.

TDRE—Transmitter Data Register Empty

This bit indicates that the UART Transmit Data register is empty and ready for additional data. Writing to the UART Transmit Data register resets this bit.

0 = Do not write to the UART Transmit Data register.

1 = The UART Transmit Data register is ready to receive an additional byte to be transmitted.

TXE—Transmitter Empty

This bit indicates that the transmit shift register is empty and character transmission is finished.

0 = Data is currently transmitting.

1 = Transmission is complete.

$CTS - \overline{CTS}$  signal

When this bit is read it returns the level of the  $\overline{\text{CTS}}$  signal. This signal is active Low.

#### **UART Status 1 Register**

This register contains multiprocessor control and status bits.

Table 64. UART Status 1 Register (U0STAT1)

| BITS  | 7 | 6 | 5      | 4    | 3  | 2 | 1 | 0 |

|-------|---|---|--------|------|----|---|---|---|

| FIELD |   |   | NEWFRM | MPRX |    |   |   |   |

| RESET | 0 | 0 | 0      | 0    | 0  | 0 | 0 | 0 |

| R/W   | R | R | R      | R    |    |   |   |   |

| ADDR  |   |   |        | F4   | 4H |   |   |   |

Reserved—Must be 0.

NEWFRM—Status bit denoting the start of a new frame. Reading the UART Receive Data register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame.

1 = The current byte is the first data byte of a new frame.

## **Analog-to-Digital Converter**

The analog-to-digital converter (ADC) converts an analog input signal to its digital representation. The features of this sigma-delta ADC include:

- 11-bit resolution in DIFFERENTIAL mode.

- 10-bit resolution in SINGLE-ENDED mode.

- Eight single-ended analog input sources are multiplexed with general-purpose I/O ports.

- 9<sup>th</sup> analog input obtained from temperature sensor peripheral.

- 11 pairs of differential inputs also multiplexed with general-purpose I/O ports.

- Low-power operational amplifier (LPO).

- Interrupt on conversion complete.

- Bandgap generated internal voltage reference with two selectable levels.

- Manual in-circuit calibration is possible employing user code (offset calibration).

- Factory calibrated for in-circuit error compensation.

#### Architecture

Figure 19 displays the major functional blocks of the ADC. An analog multiplexer network selects the ADC input from the available analog pins, ANA0 through ANA7.

The input stage of the ADC allows both differential gain and buffering. The following input options are available:

- Unbuffered input (SINGLE-ENDED and DIFFERENTIAL modes).

- Buffered input with unity gain (SINGLE-ENDED and DIFFERENTIAL modes).

- LPO output with full pin access to the feedback path.

zilog

#### 126

#### **Factory Calibration**

Devices that have been factory calibrated contain 30 bytes of calibration data in the Flash option bit space. This data consists of 3 bytes for each input mode, one for offset and two for gain correction. For a list of input modes for which calibration data exists, see Zilog Calibration Data on page 161.

#### **User Calibration**

If you have precision references available, its own external calibration can be performed using any input modes. This calibration data takes into account buffer offset and non-linearity, so it is recommended that this calibration be performed separately for each of the ADC input modes planned for use.

#### **Manual Offset Calibration**

When uncalibrated, the ADC has significant offset (see Table 135 on page 231). Subsequently, manual offset calibration capability is built into the block. When the ADC Control Register 0 sets the input mode (ANAIN[2:0]) to MANUAL OFFSET CALIBRATION mode, the differential inputs to the ADC are shorted together by an internal switch. Reading the ADC value at this point produces 0 in an ideal system. The value actually read is the ADC offset. This value can be stored in non-volatile memory (see Non-Volatile Data Storage on page 169) and accessed by user code to compensate for the input offset error. There is no provision for manual gain calibration.

#### Software Compensation Procedure Using Factory Calibration Data

The value read from the ADC high and low byte registers is uncompensated. The user mode software must apply gain and offset correction to this uncompensated value for maximum accuracy. The following equation yields the compensated value:

$ADC_{comp} = (ADC_{uncomp} - OFFCAL) + ((ADC_{uncomp} - OFFCAL) \times GAINCAL)/2^{16}$

where GAINCAL is the gain calibration value, OFFCAL is the offset calibration value and  $ADC_{uncomp}$  is the uncompensated value read from the ADC. All values are in two's complement format.

#### Note:

The offset compensation is performed first, followed by the gain compensation. One bit of resolution is lost because of rounding on both the offset and gain computations. As a result the ADC registers read back 13 bits: 1 sign bit, two calibration bits lost to rounding and 10 data bits.

Also note that in the second term, the multiplication must be performed before the division by  $2^{16}$ . Otherwise, the second term incorrectly evaluates to zero.

zilog

162

| Info Page<br>Address | Memory<br>Address | Compensation Usage      | ADC Mode                 | Reference<br>Type |

|----------------------|-------------------|-------------------------|--------------------------|-------------------|

| 60                   | FE60              | Offset                  | Single-Ended Unbuffered  | Internal 2.0 V    |

| 08                   | FE08              | Gain High Byte          | Single-Ended Unbuffered  | Internal 2.0 V    |

| 09                   | FE09              | Gain Low Byte           | Single-Ended Unbuffered  | Internal 2.0 V    |

| 63                   | FE63              | Offset                  | Single-Ended Unbuffered  | Internal 1.0 V    |

| 0A                   | FE0A              | Gain High Byte          | Single-Ended Unbuffered  | Internal 1.0 V    |

| 0B                   | FE0B              | Gain Low Byte           | Single-Ended Unbuffered  | Internal 1.0 V    |

| 66                   | FE66              | Offset                  | Single-Ended Unbuffered  | External 2.0 V    |

| 0C                   | FE0C              | Gain High Byte          | Single-Ended Unbuffered  | External 2.0 V    |

| 0D                   | FE0D              | Gain Low Byte           | Single-Ended Unbuffered  | External 2.0 V    |

| 69                   | FE69              | Offset                  | Single-Ended 1x Buffered | Internal 2.0 V    |

| 0E                   | FE0E              | Gain High Byte          | Single-Ended 1x Buffered | Internal 2.0 V    |

| 0F                   | FE0F              | Gain Low Byte           | Single-Ended 1x Buffered | Internal 2.0 V    |

| 6C                   | FE6C              | Offset                  | Single-Ended 1x Buffered | External 2.0 V    |

| 10                   | FE10              | Gain High Byte          | Single-Ended 1x Buffered | External 2.0 V    |

| 11                   | FE11              | Gain Low Byte           | Single-Ended 1x Buffered | External 2.0 V    |

| 6F                   | FE6F              | Offset                  | Differential Unbuffered  | Internal 2.0 V    |

| 12                   | FE12              | Positive Gain High Byte | Differential Unbuffered  | Internal 2.0 V    |

| 13                   | FE13              | Positive Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V    |

| 30                   | FE30              | Negative Gain High Byte | Differential Unbuffered  | Internal 2.0 V    |

| 31                   | FE31              | Negative Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V    |

| 72                   | FE72              | Offset                  | Differential Unbuffered  | Internal 1.0 V    |

| 14                   | FE14              | Positive Gain High Byte | Differential Unbuffered  | Internal 1.0 V    |

| 15                   | FE15              | Positive Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V    |

| 32                   | FE32              | Negative Gain High Byte | Differential Unbuffered  | Internal 1.0 V    |

| 33                   | FE33              | Negative Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V    |

| 75                   | FE75              | Offset                  | Differential Unbuffered  | External 2.0 V    |

| 16                   | FE16              | Positive Gain High Byte | Differential Unbuffered  | External 2.0 V    |

| 17                   | FE17              | Positive Gain Low Byte  | Differential Unbuffered  | External 2.0 V    |

|                      |                   |                         |                          |                   |

#### Table 94. ADC Calibration Data Location

zilog

163

| Info Page<br>Address | Memory<br>Address | Compensation Usage      | ADC Mode                 | Reference<br>Type |

|----------------------|-------------------|-------------------------|--------------------------|-------------------|

| 34                   | FE34              | Negative Gain High Byte | Differential Unbuffered  | External 2.0 V    |

| 35                   | FE35              | Negative Gain Low Byte  | Differential Unbuffered  | External 2.0 V    |

| 78                   | FE78              | Offset                  | Differential 1x Buffered | Internal 2.0 V    |

| 18                   | FE18              | Positive Gain High Byte | Differential 1x Buffered | Internal 2.0 V    |

| 19                   | FE19              | Positive Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V    |

| 36                   | FE36              | Negative Gain High Byte | Differential 1x Buffered | Internal 2.0 V    |

| 37                   | FE37              | Negative Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V    |

| 7B                   | FE7B              | Offset                  | Differential 1x Buffered | External 2.0 V    |

| 1A                   | FE1A              | Positive Gain High Byte | Differential 1x Buffered | External 2.0 V    |

| 1B                   | FE1B              | Positive Gain Low Byte  | Differential 1x Buffered | External 2.0 V    |

| 38                   | FE38              | Negative Gain High Byte | Differential 1x Buffered | External 2.0 V    |

| 39                   | FE39              | Negative Gain Low Byte  | Differential 1x Buffered | External 2.0 V    |

#### Table 94. ADC Calibration Data Location (Continued)

zilog | 177

The Auto-Baud Detector/Generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous datastreams, the maximum recommended baud rate is the system clock frequency divided by 8. The maximum possible baud rate for asynchronous datastreams is the system clock frequency divided by 4, but this theoretical maximum is possible only for low noise designs with clean signals. Table 105 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock<br>Frequency (MHz) | Recommended Maximum<br>Baud Rate (Kbps) | Recommended<br>Standard PC<br>Baud Rate (bps) | Minimum Baud<br>Rate (Kbps) |

|---------------------------------|-----------------------------------------|-----------------------------------------------|-----------------------------|

| 20.0                            | 2500.0                                  | 1,843,200                                     | 39                          |

| 1.0                             | 125.0                                   | 115,200                                       | 1.95                        |

| 0.032768 (32 kHz)               | 4.096                                   | 2,400                                         | 0.064                       |

#### Table 105. OCD Baud-Rate Limits

If the OCD receives a Serial Break (nine or more continuous bits Low) the Auto-Baud Detector/Generator resets. Reconfigure the Auto-Baud Detector/Generator by sending 80H.

#### **OCD Serial Errors**

The On-Chip Debugger can detect any of the following error conditions on the DBG pin:

- Serial Break (a minimum of nine continuous bits Low)

- Framing Error (received Stop bit is Low)

- Transmit Collision (OCD and host simultaneous transmission detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long Serial Break back to the host, and resets the Auto-Baud Detector/Generator. A Framing Error or Transmit Collision may be caused by the host sending a Serial Break to the OCD. Because of the open-drain nature of the interface, returning a Serial Break break back to the host only extends the length of the Serial Break if the host releases the Serial Break early.

The host transmits a Serial Break on the DBG pin when first connecting to the Z8 Encore! XP F082A Series devices or when recovering from an error. A Serial Break from the host resets the Auto-Baud Generator/Detector but does not reset the OCD Control register. A Serial Break leaves the device in DEBUG mode if that is the current mode. The OCD is held in Reset until the end of the Serial Break when the DBG pin returns

zilog

- **-** 18

- **Read Register (09H)**—The Read Register command reads data from the Register File. Data can be read 1–256 bytes at a time (256 bytes can be read by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for all the data values.

```

DBG \leftarrow 09H

DBG \leftarrow {4'h0,Register Address[11:8]

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-256 data bytes

```

• Write Program Memory (0AH)—The Write Program Memory command writes data to Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

```

DBG \leftarrow 0AH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

• **Read Program Memory (0BH)**—The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1–65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for the data.

```

DBG \leftarrow 0BH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

• Write Data Memory (0CH)—The Write Data Memory command writes data to Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

```

DBG \leftarrow 0CH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

```

<mark>z</mark>ilog<sup>°</sup>

| 211 |

|-----|

| Assembly        | Symbolic                                                     | Addres        | s Mode   | Opcode(s) | Flags |          |   |           |   |   | Fetch  | Instr. |

|-----------------|--------------------------------------------------------------|---------------|----------|-----------|-------|----------|---|-----------|---|---|--------|--------|

| Mnemonic        | Operation                                                    | dst           | src      | (Hex)     | С     | Ζ        | S | ۷         | D | Н | Cycles |        |

| LDC dst, src    | $dst \gets src$                                              | r             | Irr      | C2        | -     | _        | - | -         | - | - | 2      | 5      |

|                 |                                                              | lr            | Irr      | C5        | -     |          |   |           |   |   | 2      | 9      |

|                 |                                                              | Irr           | r        | D2        | -     |          |   |           |   |   | 2      | 5      |

| LDCI dst, src   | $dst \gets src$                                              | lr            | Irr      | C3        | -     | -        | - | -         | - | - | 2      | 9      |

|                 | r ← r + 1<br>rr ← rr + 1                                     | Irr           | Ir       | D3        | -     |          |   |           |   |   | 2      | 9      |

| LDE dst, src    | $dst \gets src$                                              | r             | Irr      | 82        | -     | _        | - | -         | - | - | 2      | 5      |

|                 |                                                              | Irr           | r        | 92        | -     |          |   |           |   |   | 2      | 5      |

| LDEI dst, src   | $dst \gets src$                                              | lr            | Irr      | 83        | _     | _        | - | -         | - | _ | 2      | 9      |

|                 | r ← r + 1<br>rr ← rr + 1                                     | Irr           | lr       | 93        | -     |          |   |           |   |   | 2      | 9      |

| LDWX dst, src   | $dst \gets src$                                              | ER            | ER       | 1FE8      | _     | _        | _ | _         | _ | _ | 5      | 4      |

| LDX dst, src    | $dst \gets src$                                              | r             | ER       | 84        | _     | _        | - | -         | - | _ | 3      | 2      |

|                 |                                                              | lr            | ER       | 85        | -     |          |   |           |   |   | 3      | 3      |

|                 |                                                              | R             | IRR      | 86        | -     |          |   |           |   |   | 3      | 4      |

|                 |                                                              | IR            | IRR      | 87        | -     |          |   |           |   |   | 3      | 5      |

|                 |                                                              | r             | X(rr)    | 88        | -     |          |   |           |   |   | 3      | 4      |

|                 |                                                              | X(rr)         | r        | 89        | -     |          |   |           |   |   | 3      | 4      |

|                 |                                                              | ER            | r        | 94        | -     |          |   |           |   |   | 3      | 2      |

|                 |                                                              | ER            | Ir       | 95        | -     |          |   |           |   |   | 3      | 3      |

|                 |                                                              | IRR           | R        | 96        | -     |          |   |           |   |   | 3      | 4      |

|                 |                                                              | IRR           | IR       | 97        | -     |          |   |           |   |   | 3      | 5      |

|                 |                                                              | ER            | ER       | E8        | -     |          |   |           |   |   | 4      | 2      |

|                 |                                                              | ER            | IM       | E9        | -     |          |   |           |   |   | 4      | 2      |

| LEA dst, X(src) | $dst \gets src + X$                                          | r             | X(r)     | 98        | _     | _        | - | -         | - | _ | 3      | 3      |

|                 |                                                              | rr            | X(rr)    | 99        | -     |          |   |           |   |   | 3      | 5      |

| MULT dst        | dst[15:0] ←<br>dst[15:8] * dst[7:0]                          | RR            |          | F4        | -     | _        | - | -         | - | - | 2      | 8      |

| NOP             | No operation                                                 |               |          | 0F        | _     | _        | _ | _         | _ | _ | 1      | 2      |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined | of the result | of the o | peration. |       | Re<br>Se |   | to (<br>1 | ) |   |        |        |

#### Table 124. eZ8 CPU Instruction Summary (Continued)

**z**ilog<sup>°</sup>

| 21 | Λ |

|----|---|

| ~  | 4 |

| Assembly        | Symbolic                                                                                                                     | Addre                           | ss Mode | Opcode(s) |   |          | FI | Fetch     | Instr. |   |        |   |

|-----------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------|-----------|---|----------|----|-----------|--------|---|--------|---|

| Mnemonic        | Operation                                                                                                                    | dst                             | src     | (Hex)     | С | Ζ        | S  | ۷         | D      | Н | Cycles |   |

| SUBX dst, src   | $dst \gets dst - src$                                                                                                        | ER                              | ER      | 28        | * | *        | *  | *         | 1      | * | 4      | 3 |

|                 |                                                                                                                              | ER                              | IM      | 29        | - |          |    |           |        |   | 4      | 3 |

| SWAP dst        | $dst[7:4] \leftrightarrow dst[3:0]$                                                                                          | R                               |         | F0        | Х | *        | *  | Х         | _      | - | 2      | 2 |

|                 |                                                                                                                              | IR                              |         | F1        | - |          |    |           |        |   | 2      | 3 |

| TCM dst, src    | (NOT dst) AND src                                                                                                            | r                               | r       | 62        | _ | *        | *  | 0         | _      | _ | 2      | 3 |

|                 |                                                                                                                              | r                               | lr      | 63        | - |          |    |           |        |   | 2      | 4 |

|                 |                                                                                                                              | R                               | R       | 64        | - |          |    |           |        |   | 3      | 3 |

|                 |                                                                                                                              | R                               | IR      | 65        | - |          |    |           |        |   | 3      | 4 |

|                 |                                                                                                                              | R                               | IM      | 66        | - |          |    |           |        |   | 3      | 3 |

|                 |                                                                                                                              | IR                              | IM      | 67        | - |          |    |           |        |   | 3      | 4 |

| TCMX dst, src   | (NOT dst) AND src                                                                                                            | ER                              | ER      | 68        | _ | *        | *  | 0         | _      | - | 4      | 3 |

|                 |                                                                                                                              | ER                              | IM      | 69        | - |          |    |           |        |   | 4      | 3 |

| TM dst, src     | dst AND src                                                                                                                  | r                               | r       | 72        | - | *        | *  | 0         | -      | - | 2      | 3 |

|                 |                                                                                                                              | r                               | lr      | 73        | - |          |    |           |        |   | 2      | 4 |

|                 |                                                                                                                              | R                               | R       | 74        | - |          |    |           |        |   | 3      | 3 |

|                 |                                                                                                                              | R                               | IR      | 75        | - |          |    |           |        |   | 3      | 4 |

|                 |                                                                                                                              | R                               | IM      | 76        | - |          |    |           |        |   | 3      | 3 |

|                 |                                                                                                                              | IR                              | IM      | 77        | - |          |    |           |        |   | 3      | 4 |

| TMX dst, src    | dst AND src                                                                                                                  | ER                              | ER      | 78        | - | *        | *  | 0         | -      | - | 4      | 3 |

|                 |                                                                                                                              | ER                              | IM      | 79        | - |          |    |           |        |   | 4      | 3 |

| TRAP Vector     | $SP \leftarrow SP - 2$<br>@SP $\leftarrow$ PC<br>$SP \leftarrow SP - 1$<br>@SP $\leftarrow$ FLAGS<br>PC $\leftarrow$ @Vector |                                 | Vector  | F2        | _ | _        | _  | _         | _      | _ | 2      | 6 |

| WDT             |                                                                                                                              |                                 |         | 5F        | _ | _        | _  | _         | _      | _ | 1      | 2 |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined                                                                 | of the result of the operation. |         |           |   | Re<br>Se |    | to (<br>1 | )      |   |        |   |

#### Table 124. eZ8 CPU Instruction Summary (Continued)

zilog <sub>217</sub>

| Abbreviation | Description                           | Abbreviation                                   | Description            |  |  |  |

|--------------|---------------------------------------|------------------------------------------------|------------------------|--|--|--|

| b            | Bit position                          | IRR                                            | Indirect Register Pair |  |  |  |

| сс           | Condition code                        | р                                              | Polarity (0 or 1)      |  |  |  |

| X            | 8-bit signed index or<br>displacement | r                                              | 4-bit Working Register |  |  |  |

| DA           | Destination address                   | R                                              | 8-bit register         |  |  |  |

| ER           | Extended Addressing register          | r1, R1, Ir1, Irr1, IR1,<br>rr1, RR1, IRR1, ER1 | Destination address    |  |  |  |

| IM           | Immediate data value                  | r2, R2, Ir2, Irr2, IR2,<br>rr2, RR2, IRR2, ER2 | Source address         |  |  |  |

| Ir           | Indirect Working Register             | RA                                             | Relative               |  |  |  |

| IR           | Indirect register                     | rr                                             | Working Register Pair  |  |  |  |

| Irr          | Indirect Working Register Pair        | RR                                             | Register Pair          |  |  |  |

#### Table 125. Opcode Map Abbreviations

220

# zilog

# **Electrical Characteristics**

The data in this chapter is pre-qualification and pre-characterization and is subject to change. Additional electrical characteristics may be found in the individual chapters.

### **Absolute Maximum Ratings**

Stresses greater than those listed in Table 126 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                                      | Minimum | Maximum | Units | Notes |

|----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                 | -40     | +105    | °C    |       |

| Storage temperature                                            | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>             | -0.3    | +5.5    | V     | 1     |

|                                                                | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$               | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin            | -5      | +5      | μA    |       |

| Maximum output current from active output pin                  | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0 °C to 70 °C                |         |         |       |       |

| Total power dissipation                                        |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$               |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0 °C to 70 °C               |         |         |       |       |

| Total power dissipation                                        |         | 430     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub> |         | 120     | mA    |       |

#### Table 126. Absolute Maximum Ratings

#### **On-Chip Debugger Timing**

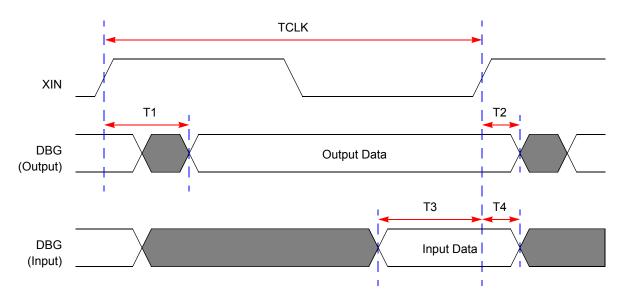

Figure 36 and Table 141 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

Figure 36. On-Chip Debugger Timing

|                |                                  | Dela    | / (ns)  |  |

|----------------|----------------------------------|---------|---------|--|

| Parameter      | Abbreviation                     | Minimum | Maximum |  |

| DBG            |                                  |         |         |  |

| T <sub>1</sub> | XIN Rise to DBG Valid Delay      | -       | 15      |  |

| T <sub>2</sub> | XIN Rise to DBG Output Hold Time | 2       | _       |  |

| T <sub>3</sub> | DBG to XIN Rise Input Setup Time | 5       | _       |  |

| T <sub>4</sub> | DBG to XIN Rise Input Hold Time  | 5       | _       |  |

#### Table 141. On-Chip Debugger Timing

zilog 257

| Part Number                                                                                 | Flash     | RAM      | SUVN | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------------------------------------------------------------------|-----------|----------|------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082A Series with 1 KB Flash, 10-Bit Analog-to-Digital Converter |           |          |      |           |            |                     |                     |                |            |                    |                     |

| Standard Temperatu                                                                          | re: 0 °C  | to 70 °C | ;    |           |            |                     |                     |                |            |                    |                     |

| Z8F012APB020SC                                                                              | 1 KB      | 256 B    | 16 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020SC                                                                              | 1 KB      | 256 B    | 16 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020SC                                                                              | 1 KB      | 256 B    | 16 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020SC                                                                              | 1 KB      | 256 B    | 16 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020SC                                                                              | 1 KB      | 256 B    | 16 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020SC                                                                              | 1 KB      | 256 B    | 16 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020SC                                                                              | 1 KB      | 256 B    | 16 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020SC                                                                              | 1 KB      | 256 B    | 16 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020SC                                                                              | 1 KB      | 256 B    | 16 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperatu                                                                          | re: -40 ° | C to 10  | 5 °C |           |            |                     |                     |                |            |                    |                     |

| Z8F012APB020EC                                                                              | 1 KB      | 256 B    | 16 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020EC                                                                              | 1 KB      | 256 B    | 16 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020EC                                                                              | 1 KB      | 256 B    | 16 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020EC                                                                              | 1 KB      | 256 B    | 16 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020EC                                                                              | 1 KB      | 256 B    | 16 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020EC                                                                              | 1 KB      | 256 B    | 16 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020EC                                                                              | 1 KB      | 256 B    | 16 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020EC                                                                              | 1 KB      | 256 B    | 16 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020EC                                                                              | 1 KB      | 256 B    | 16 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |