# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64 x 8                                                       |

| RAM Size                   | 512 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022ahh020sc    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **z**ilog<sup>°</sup>

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, and Z8 Encore! XP are registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

ISO 9001:2000 FS 507510 Zilog products are designed and manufactured under an ISO registered 9001:2000 Quality Management System. For more details, please visit www.zilog.com/quality.

zilog

operational amplifier (LPO) is OFF. To use the LPO, clear the LPO bit, turning it ON. Clearing this bit might interfere with normal ADC measurements on ANA0 (the LPO output). This bit enables the amplifier even in STOP mode. If the amplifier is not required in STOP mode, disable it. Failure to perform this results in STOP mode currents greater than specified.

**Note:** This register is only reset during a POR sequence. Other system reset events do not affect *it.*

#### Table 12. Power Control Register 0 (PWRCTL0)

| BITS  | 7   | 6        | 5   | 4   | 3    | 2   | 1    | 0        |  |  |

|-------|-----|----------|-----|-----|------|-----|------|----------|--|--|

| FIELD | LPO | Reserved |     | VBO | TEMP | ADC | COMP | Reserved |  |  |

| RESET | 1   | 0 0      |     | 0   | 0    | 0   | 0    | 0        |  |  |

| R/W   | R/W | R/W      | R/W | R/W | R/W  | R/W | R/W  | R/W      |  |  |

| ADDR  |     | F80H     |     |     |      |     |      |          |  |  |

LPO—Low-Power Operational Amplifier Disable

0 = LPO is enabled (this applies even in STOP mode).

1 = LPO is disabled.

Reserved—Must be 0.

VBO—Voltage Brownout Detector Disable

This bit and the VBO\_AO Flash option bit must both enable the VBO for the VBO to be active.

0 = VBO Enabled

1 = VBO Disabled

TEMP—Temperature Sensor Disable

0 = Temperature Sensor Enabled

1 = Temperature Sensor Disabled

ADC—Analog-to-Digital Converter Disable

- 0 = Analog-to-Digital Converter Enabled

- 1 = Analog-to-Digital Converter Disabled

COMP—Comparator Disable

- 0 =Comparator is Enabled

- 1 = Comparator is Disabled

Reserved—Must be 0.

Note: Asserting any power control bit disables the targeted block, regardless of any enable bits contained in the target block's control registers.

# **GPIO Interrupts**

Many of the GPIO port pins can be used as interrupt sources. Some port pins can be configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). See Interrupt Controller on page 55 for more information about interrupts using the GPIO pins.

# **GPIO Control Register Definitions**

Four registers for each Port provide access to GPIO control, input data, and output data. Table 16 lists these Port registers. Use the Port A–D Address and Control registers together to provide access to sub-registers for Port configuration and control.

| Port Register Mnemonic     | Port Register Name                                              |  |  |  |  |

|----------------------------|-----------------------------------------------------------------|--|--|--|--|

| PxADDR                     | Port A–D Address Register<br>(Selects sub-registers)            |  |  |  |  |

| PxCTL                      | Port A–D Control Register<br>(Provides access to sub-registers) |  |  |  |  |

| PxIN                       | Port A–D Input Data Register                                    |  |  |  |  |

| PxOUT                      | Port A–D Output Data Register                                   |  |  |  |  |

| Port Sub-Register Mnemonic | Port Register Name                                              |  |  |  |  |

| PxDD                       | Data Direction                                                  |  |  |  |  |

| PxAF                       | Alternate Function                                              |  |  |  |  |

| PxOC                       | Output Control (Open-Drain)                                     |  |  |  |  |

| PxHDE                      | High Drive Enable                                               |  |  |  |  |

| PxSMRE                     | Stop Mode Recovery Source Enable                                |  |  |  |  |

| PxPUE                      | Pull-up Enable                                                  |  |  |  |  |

| PxAFS1                     | Alternate Function Set 1                                        |  |  |  |  |

| PxAFS2                     | Alternate Function Set 2                                        |  |  |  |  |

|                            |                                                                 |  |  |  |  |

| Table 16. | <b>GPIO Por</b> | t Registers | and Sub-Registers |

|-----------|-----------------|-------------|-------------------|

|-----------|-----------------|-------------|-------------------|

### Table 18. Port A–D Control Registers (PxCTL)

| BITS  | 7    | 7 6 5 4 3 2 1 0             |    |            |           |   |  |  |  |  |

|-------|------|-----------------------------|----|------------|-----------|---|--|--|--|--|

| FIELD | PCTL |                             |    |            |           |   |  |  |  |  |

| RESET | 00H  |                             |    |            |           |   |  |  |  |  |

| R/W   | R/W  | R/W R/W R/W R/W R/W R/W R/W |    |            |           |   |  |  |  |  |

| ADDR  |      |                             | FI | D1H, FD5H, | FD9H, FDD | Н |  |  |  |  |

PCTL[7:0]—Port Control

The Port Control register provides access to all sub-registers that configure the GPIO Port operation.

# Port A–D Data Direction Sub-Registers

The Port A–D Data Direction sub-register is accessed through the Port A–D Control register by writing 01H to the Port A–D Address register (Table 19).

| BITS  | 7        | 6                                                                                     | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|----------|---------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|--|

| FIELD | DD7      | DD6                                                                                   | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |  |  |

| RESET | 1        | 1                                                                                     | 1   | 1   | 1   | 1   | 1   | 1   |  |  |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W                                                           |     |     |     |     |     |     |  |  |

| ADDR  | lf 01H i | If 01H in Port A–D Address Register, accessible through the Port A–D Control Register |     |     |     |     |     |     |  |  |

# Table 19. Port A–D Data Direction Sub-Registers (PxDD)

#### DD[7:0]—Data Direction

These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction register setting.

0 = Output. Data in the Port A–D Output Data register is driven onto the port pin.

1 = Input. The port pin is sampled and the value written into the Port A–D Input Data Register. The output driver is tristated.

# Port A–D Alternate Function Sub-Registers

The Port A–D Alternate Function sub-register (Table 20) is accessed through the Port A–D Control register by writing 02H to the Port A–D Address register. The Port A–D Alternate Function sub-registers enable the alternate function selection on pins. If disabled, pins functions as GPIO. If enabled, select one of four alternate functions using alternate function set subregisters 1 and 2 as described in the Port A–D Alternate Function

PAFS1[7:0]—Port Alternate Function Set 1 0 = Port Alternate Function selected as defined in Table 14 and Table 15 on page 44. 1 = Port Alternate Function selected as defined in Table 14 and Table 15 on page 44.

#### Port A–D Alternate Function Set 2 Sub-Registers

The Port A–D Alternate Function Set 2 sub-register (Table 26) is accessed through the Port A–D Control register by writing 08H to the Port A–D Address register. The Alternate Function Set 2 sub-registers selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register is defined in Table 15.

• Note: Alternate function selection on port pins must also be enabled as described in Port A–D Alternate Function Sub-Registers on page 47.

| BITS  | 7                                                                  | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |

|-------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|--|

| FIELD | PAFS27                                                             | PAFS26                                                                                | PAFS25 | PAFS24 | PAFS23 | PAFS22 | PAFS21 | PAFS20 |  |  |  |

| RESET | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device) |                                                                                       |        |        |        |        |        |        |  |  |  |

| R/W   | R/W                                                                | R/W R/W R/W R/W R/W R/W R/W                                                           |        |        |        |        |        |        |  |  |  |

| ADDR  | lf 08H i                                                           | If 08H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |        |  |  |  |

Table 26. Port A–D Alternate Function Set 2 Sub-Registers (PxAFS2)

PAFS2[7:0]—Port Alternate Function Set 2

0 = Port Alternate Function selected as defined in Table 15.

1 = Port Alternate Function selected as defined in Table 15.

# Port A–C Input Data Registers

Reading from the Port A–C Input Data registers (Table 27) returns the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those missing on the 8- and 28-pin packages, as well as those missing on the ADC-enabled 28-pin packages.

| Table 27. Port A–C Input Data Registers (PxIN) | Table 27. | Port A–C | Input Data | Registers | (PxIN) |

|------------------------------------------------|-----------|----------|------------|-----------|--------|

|------------------------------------------------|-----------|----------|------------|-----------|--------|

| BITS      | 7                | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|-----------|------------------|------|------|------|------|------|------|------|--|

| FIELD     | PIN7             | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |

| RESET     | Х                | Х    | Х    | Х    | Х    | Х    | Х    | Х    |  |

| R/W       | R                | R    | R    | R    | R    | R    | R    | R    |  |

| ADDR      | FD2H, FD6H, FDAH |      |      |      |      |      |      |      |  |

| X = Undef | X = Undefined.   |      |      |      |      |      |      |      |  |

U0RXI—UART 0 Receiver Interrupt Request

0 = No interrupt request is pending for the UART 0 receiver.

1 = An interrupt request from the UART 0 receiver is awaiting service.

U0TXI-UART 0 Transmitter Interrupt Request

0 = No interrupt request is pending for the UART 0 transmitter.

1 = An interrupt request from the UART 0 transmitter is awaiting service.

ADCI—ADC Interrupt Request

0 = No interrupt request is pending for the analog-to-digital Converter.

1 = An interrupt request from the Analog-to-Digital Converter is awaiting service.

# **Interrupt Request 1 Register**

The Interrupt Request 1 (IRQ1) register (Table 34) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ1 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 1 register to determine if any interrupt requests are pending.

| BITS  | 7     | 6     | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|-------|-------|-------|------|------|------|------|------|------|--|--|

| FIELD | PA7VI | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |  |  |

| RESET | 0     | 0     | 0    | 0    | 0    | 0    | 0    | 0    |  |  |

| R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |  |

| ADDR  |       | FC3H  |      |      |      |      |      |      |  |  |

Table 34. Interrupt Request 1 Register (IRQ1)

PA7*V*I—Port A Pin 7 or LVD Interrupt Request

0 = No interrupt request is pending for GPIO Port A or LVD.

1 = An interrupt request from GPIO Port A or LVD.

PA6CI—Port A Pin 6 or Comparator Interrupt Request

0 = No interrupt request is pending for GPIO Port A or Comparator.

1 = An interrupt request from GPIO Port A or Comparator.

PAxI—Port A Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port A pin *x*.

1 = An interrupt request from GPIO Port A pin x is awaiting service.

where x indicates the specific GPIO Port pin number (0–5).

zilog ,

Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state for one system clock cycle (from Low to High or from High to Low) upon timer Reload. If it is appropriate to have the Timer Output make a state change at a One-Shot time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control Register to the start value before enabling ONE-SHOT mode. After starting the timer, set TPOL to the opposite bit value.

Follow the steps below for configuring a timer for ONE-SHOT mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for ONE-SHOT mode.

- Set the prescale value.

- Set the initial output level (High or Low) if using the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In ONE-SHOT mode, the system clock always provides the timer input. The timer period is given by the following equation:

$\label{eq:one-short} \text{ONE-SHOT Mode Time-Out Period } (s) = \frac{\text{Reload Value} - \text{Start Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

#### **CONTINUOUS Mode**

In CONTINUOUS mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below for configuring a timer for CONTINUOUS mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for CONTINUOUS mode.

Follow the steps below for configuring a timer for COUNTER mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for COUNTER mode.

- Select either the rising edge or falling edge of the Timer Input signal for the count. This selection also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER mode. After the first timer Reload in COUNTER mode, counting always begins at the reset value of 0001H. In COUNTER mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer.

In COUNTER mode, the number of Timer Input transitions since the timer start is given by the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value-Start Value

#### **COMPARATOR COUNTER Mode**

In COMPARATOR COUNTER mode, the timer counts input transitions from the analog comparator output. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the comparator output signal. In COMPAR-ATOR COUNTER mode, the prescaler is disabled.

**Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the comparator output signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

After reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below for configuring a timer for COMPARE mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for COMPARE mode.

- Set the prescale value.

- Set the initial logic level (High or Low) for the Timer Output alternate function, if appropriate.

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In COMPARE mode, the system clock always provides the timer input. The Compare time can be calculated by the following equation:

COMPARE Mode Time (s) =  $\frac{(Compare Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### GATED Mode

In GATED mode, the timer counts only when the Timer Input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control register. When the Timer Input signal is asserted, counting begins. A timer interrupt is generated when the Timer Input signal is deasserted or a timer reload occurs. To determine if a Timer Input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. When reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the Timer Input signal remains asserted). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reset.

Follow the steps below for configuring a timer for GATED mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for GATED mode.

- Set the prescale value.

1000 = PWM DUAL OUTPUT mode 1001 = CAPTURE RESTART mode 1010 = COMPARATOR COUNTER mode

# Timer 0–1 High and Low Byte Registers

The Timer 0–1 High and Low Byte (TxH and TxL) registers (Table 50 and Table 51) contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TxL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from TxL read the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

| BITS  | 7   | 6                           | 5 | 4     | 3    | 2 | 1 | 0 |  |  |

|-------|-----|-----------------------------|---|-------|------|---|---|---|--|--|

| FIELD | TH  |                             |   |       |      |   |   |   |  |  |

| RESET | 0   | 0 0 0 0 0 0 0 0             |   |       |      |   |   |   |  |  |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |       |      |   |   |   |  |  |

| ADDR  |     |                             |   | F00H, | F08H |   |   |   |  |  |

#### Table 50. Timer 0–1 High Byte Register (TxH)

#### Table 51. Timer 0–1 Low Byte Register (TxL)

| BITS  | 7   | 6                           | 5 | 4     | 3    | 2 | 1 | 0 |  |  |

|-------|-----|-----------------------------|---|-------|------|---|---|---|--|--|

| FIELD | TL  |                             |   |       |      |   |   |   |  |  |

| RESET | 0   | 0                           | 0 | 0     | 0    | 0 | 0 | 1 |  |  |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |       |      |   |   |   |  |  |

| ADDR  |     |                             |   | F01H, | F09H |   |   |   |  |  |

TH and TL—Timer High and Low Bytes

These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value.

# **Timer Reload High and Low Byte Registers**

The Timer 0–1 Reload High and Low Byte (TxRH and TxRL) registers (Table 52 and Table 53) store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte register are stored in a temporary holding register. When a write to the

# Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which may place the Z8 Encore! XP<sup>®</sup> F082A Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator.

- A selectable time-out response: reset or interrupt.

- 24-bit programmable time-out value.

# Operation

The Watchdog Timer is a one-shot timer that resets or interrupts the Z8 Encore! XP F082A Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash Option Bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10 kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 56 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

#### Table 56. Watchdog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value — | Approximate Time-Out Delay<br>(with 10 kHz typical WDT oscillator frequency) |                        |  |  |  |  |

|------------------|--------------------|------------------------------------------------------------------------------|------------------------|--|--|--|--|

| (Hex)            | (Decimal)          | Typical                                                                      | Description            |  |  |  |  |

| 000004           | 4                  | 400 μs                                                                       | Minimum time-out delay |  |  |  |  |

| FFFFF            | 16,777,215         | 28 minutes                                                                   | Maximum time-out delay |  |  |  |  |

# Operation

#### **Data Format**

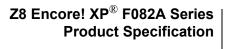

The UART always transmits and receives data in an 8-bit data format, least-significant bit first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low START bit and ends with either 1 or 2 active High STOP bits. Figure 11 and Figure 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

1001 = 1.8 V 1010–1111 = Reserved

For 8-pin devices:

000000 = 0.00 V000001 = 0.05 V000010 = 0.10 V 000011 = 0.15 V 000100 = 0.20 V000101 = 0.25 V000110 = 0.30 V 000111 = 0.35 V 001000 = 0.40 V 001001 = 0.45 V 001010 = 0.50 V 001011 = 0.55 V 001100 = 0.60 V 001101 = 0.65 V 001110 = 0.70 V001111 = 0.75 V 010000 = 0.80 V010001 = 0.85 V010010 = 0.90 V 010011 = 0.95 V 010100 = 1.00 V (Default) 010101 = 1.05 V 010110 = 1.10 V 010111 = 1.15 V 011000 = 1.20 V 011001 = 1.25 V 011010 = 1.30 V 011011 = 1.35 V 011100 = 1.40 V 011101 = 1.45 V 011110 = 1.50 V 011111 = 1.55 V 100000 = 1.60 V100001 = 1.65 V 100010 = 1.70 V 100011 = 1.75 V

#### 200

# Assembly Language Syntax

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed if manual program coding is preferred or if you intend to implement your own assembler.

**Example 1**: If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Table 112. Assembly Language Syntax Example 1

| Assembly Language<br>Code | ADD | 43H, | 08H | (ADD dst, src) |

|---------------------------|-----|------|-----|----------------|

| Object Code               | 04  | 08   | 43  | (OPC src, dst) |

**Example 2**: In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Table 113. Assembly Language Syntax Example 2

| Assembly Language<br>Code | ADD | 43H, | R8 | (ADD dst, src) |

|---------------------------|-----|------|----|----------------|

| Object Code               | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

# eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is described in Table 114.

204

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| ТСМ      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |

Table 118. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-Increment Addresses       |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

# Table 119. CPU Control Instructions

| Mnemonic | Operands | Instruction           |

|----------|----------|-----------------------|

| ATM      | _        | Atomic Execution      |

| CCF      | _        | Complement Carry Flag |

| DI       | _        | Disable Interrupts    |

| EI       | _        | Enable Interrupts     |

| HALT     | _        | Halt Mode             |

| NOP      | _        | No Operation          |

| RCF      | _        | Reset Carry Flag      |

**z**ilog<sup>°</sup>

| 24         | 2 |

|------------|---|

| <b>∠</b> I | 4 |

| Assembly<br>Mnemonic | Symbolic                                                        | Addres    | Address Mode Opcode(s) |           |   |              | FI | ags       | Fetch | Instr. |   |        |

|----------------------|-----------------------------------------------------------------|-----------|------------------------|-----------|---|--------------|----|-----------|-------|--------|---|--------|

|                      | Operation                                                       | dst       | src                    | (Hex)     | С | Ζ            | S  | ۷         | D     | н      |   | Cycles |

| OR dst, src          | $dst \gets dst \ OR \ src$                                      | r         | r                      | 42        | - | *            | *  | 0         | -     | -      | 2 | 3      |

|                      |                                                                 | r         | lr                     | 43        | - |              |    |           |       |        | 2 | 4      |

|                      |                                                                 | R         | R                      | 44        | - |              |    |           |       |        | 3 | 3      |

|                      |                                                                 | R         | IR                     | 45        | - |              |    |           |       |        | 3 | 4      |

|                      |                                                                 | R         | IM                     | 46        | - |              |    |           |       |        | 3 | 3      |

|                      |                                                                 | IR        | IM                     | 47        | - |              |    |           |       |        | 3 | 4      |

| ORX dst, src         | $dst \gets dst \: OR \: src$                                    | ER        | ER                     | 48        | _ | *            | *  | 0         | _     | -      | 4 | 3      |

|                      |                                                                 | ER        | IM                     | 49        | - |              |    |           |       |        | 4 | 3      |

| POP dst              | dst ← @SP                                                       | R         |                        | 50        | - | _            | _  | -         | -     | -      | 2 | 2      |

|                      | $SP \leftarrow SP + 1$                                          | IR        |                        | 51        | - |              |    |           |       |        | 2 | 3      |

| POPX dst             | $dst \leftarrow @SP$<br>SP $\leftarrow$ SP + 1                  | ER        |                        | D8        | - | -            | _  | _         | _     | -      | 3 | 2      |

| PUSH src             | $SP \leftarrow SP - 1$<br>@SP $\leftarrow$ src                  | R         |                        | 70        | - | _            | _  | _         | _     | -      | 2 | 2      |

|                      |                                                                 | IR        |                        | 71        | - |              |    |           |       |        | 2 | 3      |

|                      |                                                                 | IM        |                        | IF70      | _ |              |    |           |       |        | 3 | 2      |

| PUSHX src            | $SP \leftarrow SP - 1$<br>@SP ← src                             | ER        |                        | C8        | _ | _            | _  | _         | _     | _      | 3 | 2      |

| RCF                  | $C \leftarrow 0$                                                |           |                        | CF        | 0 | _            | _  | _         | _     | _      | 1 | 2      |

| RET                  | $PC \leftarrow @SP$<br>$SP \leftarrow SP + 2$                   |           |                        | AF        | _ | _            | _  | _         | _     | _      | 1 | 4      |

| RL dst               | C - D7 D6 D5 D4 D3 D2 D1 D0 - dst                               | R         |                        | 90        | * | *            | *  | *         | _     | _      | 2 | 2      |

|                      |                                                                 | IR        |                        | 91        | - |              |    |           |       |        | 2 | 3      |

| RLC dst              |                                                                 | R         |                        | 10        | * | *            | *  | *         | _     | _      | 2 | 2      |

|                      | C                                                               | IR        |                        | 11        |   |              |    |           |       |        | 2 | 3      |

| Flags Notation:      | * = Value is a function of t<br>– = Unaffected<br>X = Undefined | he result | of the o               | peration. |   | : Re<br>: Se |    | to (<br>1 | C     |        |   |        |

### Table 124. eZ8 CPU Instruction Summary (Continued)

INCH

MAX

0.068

0.010

0.061

0.019

0.010

0.196

0.157

0.242

0.016

0.032

.050 BSC

MIN

0.061

0.004

0.055

0.014

0.007

0.189

0.150

0.230

0.010

0.018

MAX

1.73

0.25

1.55

0.48

0.25

4.98

3.99

6.15

0.40

0.81

zilog 242

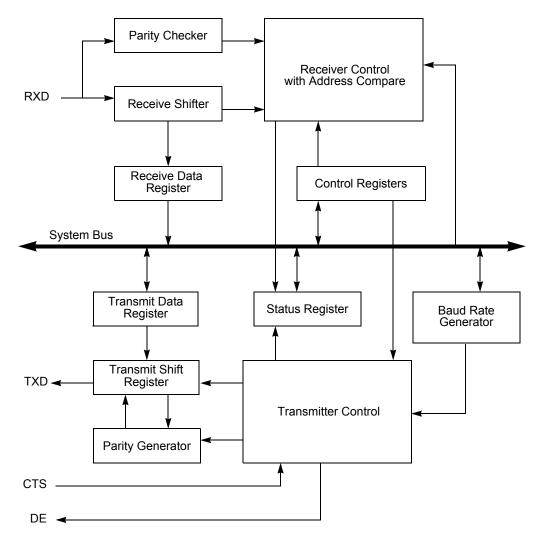

# Figure 40 displays the 8-pin Small Outline Integrated Circuit package (SOIC) available for the Z8 Encore! XP<sup>®</sup> F082A Series devices.

CONTROLLING DIMENSIONS : MM LEADS ARE COPLANAR WITHIN .004 INCH.

Figure 40. 8-Pin Small Outline Integrated Circuit Package (SOIC)

RL 206

Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

zilog | 267

register 201 ADC control (ADCCTL) 130, 132 ADC data high byte (ADCDH) 132 ADC data low bits (ADCDL) 133 flash control (FCTL) 149, 155, 156 flash high and low byte (FFREQH and FREEQL) 152 flash page select (FPS) 150, 151 flash status (FSTAT) 150 GPIO port A-H address (PxADDR) 46 GPIO port A-H alternate function sub-registers 48 GPIO port A-H control address (PxCTL) 47 GPIO port A-H data direction sub-registers 47 OCD control 184 OCD status 185 UARTx baud rate high byte (UxBRH) 114 UARTx baud rate low byte (UxBRL) 114 UARTx Control 0 (UxCTL0) 108, 114 UARTx control 1 (UxCTL1) 109 UARTx receive data (UxRXD) 113 UARTx status 0 (UxSTAT0) 111 UARTx status 1 (UxSTAT1) 112 UARTx transmit data (UxTXD) 113 Watchdog Timer control (WDTCTL) 31, 94, 136, 190 Watchdog Timer reload high byte (WDTH) 95 Watchdog Timer reload low byte (WDTL) 95 Watchdog Timer reload upper byte (WD-TU) 95 register file 15 register pair 201 register pointer 202 reset and stop mode characteristics 24 and Stop Mode Recovery 23 carry flag 204 sources 25 **RET 206** return 206

RLC 206 rotate and shift instuctions 206 rotate left 206 rotate left through carry 206 rotate right 206 rotate right through carry 206 RP 202 RR 201, 206 rr 201 RRC 206

# S

**SBC 203** SCF 204, 205 second opcode map after 1FH 219 set carry flag 204, 205 set register pointer 205 shift right arithmatic 207 shift right logical 207 signal descriptions 11 single-shot conversion (ADC) 123 software trap 206 source operand 202 SP 202 SRA 207 src 202 SRL 207 **SRP 205** stack pointer 202 **STOP 205** STOP mode 33 stop mode 205 Stop Mode Recovery sources 28 using a GPIO port pin transition 29 using Watchdog Timer time-out 29 stop mode recovery sources 30 using a GPIO port pin transition 30 SUB 203 subtract 203 subtract - extended addressing 203 subtract with carry 203