#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64 × 8                                                       |

| RAM Size                   | 512 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022ahj020sc    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

х

| OCD Data Format<br>OCD Auto-Baud Detector/Generator<br>OCD Serial Errors<br>OCD Unlock Sequence (8-Pin Devices Only)<br>Breakpoints<br>Runtime Counter                                                                        | 176<br>177<br>178<br>178<br>179 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| On-Chip Debugger Commands                                                                                                                                                                                                     | 184<br>184                      |

| Oscillator Control                                                                                                                                                                                                            | 187                             |

| Operation       System Clock Selection         Clock Failure Detection and Recovery       Oscillator Control Register Definitions                                                                                             | 187<br>189                      |

| Crystal Oscillator                                                                                                                                                                                                            | 193                             |

| Operating Modes       Crystal Oscillator Operation         Oscillator Operation with an External RC Network       Crystal Oscillator Operation                                                                                | 193                             |

| Internal Precision Oscillator                                                                                                                                                                                                 | 197                             |

| Operation                                                                                                                                                                                                                     | 197                             |

| eZ8 CPU Instruction Set                                                                                                                                                                                                       | 199                             |

| Assembly Language Programming IntroductionAssembly Language SyntaxeZ8 CPU Instruction NotationeZ8 CPU Instruction ClasseseZ8 CPU Instruction ClasseseZ8 CPU Instruction Summary                                               | 200<br>200<br>202               |

| Opcode Maps                                                                                                                                                                                                                   | 216                             |

| Electrical Characteristics                                                                                                                                                                                                    | 221                             |

| Absolute Maximum Ratings       DC Characteristics         DC Characteristics       AC Characteristics         On-Chip Peripheral AC and DC Electrical Characteristics       General Purpose I/O Port Input Data Sample Timing | 222<br>227<br>229               |

## **Signal Descriptions**

Table 2 describes the Z8 Encore! XP F082A Series signals. See Pin Configurations on page 9 to determine the signals available for the specific package styles.

| Signal Mnemonic                                     | I/O     | Description                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose I/                                  | O Ports | A–D                                                                                                                                                                                                                                                                                                     |

| PA[7:0]                                             | I/O     | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| PB[7:0]                                             | I/O     | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |

| PC[7:0]                                             | I/O     | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| PD[0]                                               | I/O     | Port D. This pin is used for general-purpose output only.                                                                                                                                                                                                                                               |

| Note: PB6 and PB7 ar<br>replaced by AV <sub>E</sub> |         | vailable in 28-pin packages without ADC. In 28-pin packages with ADC, they are $V_{\rm SS}.$                                                                                                                                                                                                            |

| UART Controllers                                    |         |                                                                                                                                                                                                                                                                                                         |

| TXD0                                                | 0       | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |

| RXD0                                                | Ι       | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |

| CTS0                                                | Ι       | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |

| DE                                                  | 0       | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 register. The DE signal may be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |

| Timers                                              |         |                                                                                                                                                                                                                                                                                                         |

| T0OUT/T1OUT                                         | 0       | Timer Output 0–1. These signals are outputs from the timers.                                                                                                                                                                                                                                            |

| T0OUT/T1OUT                                         | 0       | Timer Complement Output 0–1. These signals are output from the timers in PWM Dual Output mode.                                                                                                                                                                                                          |

| T0IN/T1IN                                           | Ι       | Timer Input 0–1. These signals are used as the capture, gating and counter inputs.                                                                                                                                                                                                                      |

| Comparator                                          |         |                                                                                                                                                                                                                                                                                                         |

| CINP/CINN                                           | Ι       | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |

| COUT                                                | 0       | Comparator Output.                                                                                                                                                                                                                                                                                      |

#### Table 2. Signal Descriptions

**z**ilog<sup>°</sup>

#### Table 7. Register File Address Map (Continued)

| Address (Hex)   | Register Description                  | Mnemonic | Reset (Hex) | Page No                  |

|-----------------|---------------------------------------|----------|-------------|--------------------------|

| FDF             | Port D Output Data                    | PDOUT    | 00          | 47                       |

| FE0–FEF         | Reserved                              | _        | XX          |                          |

| Watchdog Time   | er (WDT)                              |          |             |                          |

| FF0             | Reset Status (Read-only)              | RSTSTAT  | X0          | 30                       |

|                 | Watchdog Timer Control (Write-only)   | WDTCTL   | N/A         | 94                       |

| FF1             | Watchdog Timer Reload Upper Byte      | WDTU     | 00          | 95                       |

| FF2             | Watchdog Timer Reload High Byte       | WDTH     | 04          | 95                       |

| FF3             | Watchdog Timer Reload Low Byte        | WDTL     | 00          | 95                       |

| FF4–FF5         | Reserved                              | —        | XX          |                          |

| Trim Bit Contro | bl                                    |          |             |                          |

| FF6             | Trim Bit Address                      | TRMADR   | 00          | 155                      |

| FF7             | Trim Bit Data                         | TRMDR    | 00          | 156                      |

| Flash Memory    | Controller                            |          |             |                          |

| FF8             | Flash Control                         | FCTL     | 00          | 149                      |

| FF8             | Flash Status                          | FSTAT    | 00          | 150                      |

| FF9             | Flash Page Select                     | FPS      | 00          | 151                      |

|                 | Flash Sector Protect                  | FPROT    | 00          | 151                      |

| FFA             | Flash Programming Frequency High Byte | FFREQH   | 00          | 152                      |

| FFB             | Flash Programming Frequency Low Byte  | FFREQL   | 00          | 152                      |

| eZ8 CPU         |                                       |          |             |                          |

| FFC             | Flags                                 |          | XX          | Refer to eZ8             |

| FFD             | Register Pointer                      | RP       | XX          | CPU Core                 |

| FFE             | Stack Pointer High Byte               | SPH      | XX          | —User Manual<br>(UM0128) |

| FFF             | Stack Pointer Low Byte                | SPL      | XX          | _(010120)                |

| XX=Undefined    |                                       |          |             |                          |

22

U0RXI—UART 0 Receiver Interrupt Request

0 = No interrupt request is pending for the UART 0 receiver.

1 = An interrupt request from the UART 0 receiver is awaiting service.

U0TXI-UART 0 Transmitter Interrupt Request

0 = No interrupt request is pending for the UART 0 transmitter.

1 = An interrupt request from the UART 0 transmitter is awaiting service.

ADCI—ADC Interrupt Request

0 = No interrupt request is pending for the analog-to-digital Converter.

1 = An interrupt request from the Analog-to-Digital Converter is awaiting service.

#### **Interrupt Request 1 Register**

The Interrupt Request 1 (IRQ1) register (Table 34) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ1 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 1 register to determine if any interrupt requests are pending.

| BITS  | 7     | 6     | 5    | 4    | 3    | 2    | 1    | 0    |  |

|-------|-------|-------|------|------|------|------|------|------|--|

| FIELD | PA7VI | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |  |

| RESET | 0     | 0     | 0    | 0    | 0    | 0    | 0    | 0    |  |

| R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |

| ADDR  | FC3H  |       |      |      |      |      |      |      |  |

Table 34. Interrupt Request 1 Register (IRQ1)

PA7*V*I—Port A Pin 7 or LVD Interrupt Request

0 = No interrupt request is pending for GPIO Port A or LVD.

1 = An interrupt request from GPIO Port A or LVD.

PA6CI—Port A Pin 6 or Comparator Interrupt Request

0 = No interrupt request is pending for GPIO Port A or Comparator.

1 = An interrupt request from GPIO Port A or Comparator.

PAxI—Port A Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port A pin *x*.

1 = An interrupt request from GPIO Port A pin x is awaiting service.

where x indicates the specific GPIO Port pin number (0–5).

#### Table 46. Shared Interrupt Select Register (IRQSS)

| BITS  | 7     | 6     | 5   | 4        | 3   | 2   | 1   | 0   |  |

|-------|-------|-------|-----|----------|-----|-----|-----|-----|--|

| FIELD | PA7VS | PA6CS |     | Reserved |     |     |     |     |  |

| RESET | 0     | 0     | 0   | 0        | 0   | 0   | 0   | 0   |  |

| R/W   | R/W   | R/W   | R/W | R/W      | R/W | R/W | R/W | R/W |  |

| ADDR  |       |       |     | FC       | EH  |     |     |     |  |

PA7VS—PA7/LVD Selection

0 = PA7 is used for the interrupt for PA7VS interrupt request.

1 = The LVD is used for the interrupt for PA7VS interrupt request.

PA6CS—PA6/Comparator Selection

0 = PA6 is used for the interrupt for PA6CS interrupt request.

1 = The Comparator is used for the interrupt for PA6CS interrupt request.

Reserved—Must be 0.

#### **Interrupt Control Register**

The Interrupt Control (IRQCTL) register (Table 47) contains the master enable bit for all interrupts.

| Table 47. | Interrupt | Control | Register | (IRQCTL) |

|-----------|-----------|---------|----------|----------|

|-----------|-----------|---------|----------|----------|

| BITS  | 7    | 6 | 5        | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|------|---|----------|----|----|---|---|---|--|--|

| FIELD | IRQE |   | Reserved |    |    |   |   |   |  |  |

| RESET | 0    | 0 | 0        | 0  | 0  | 0 | 0 | 0 |  |  |

| R/W   | R/W  | R | R        | R  | R  | R | R | R |  |  |

| ADDR  |      |   |          | FC | FH |   |   |   |  |  |

IRQE—Interrupt Request Enable

This bit is set to 1 by executing an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, Reset or by a direct register write of a 0 to this bit.

- 0 = Interrupts are disabled.

- 1 = Interrupts are enabled.

Reserved—Must be 0.

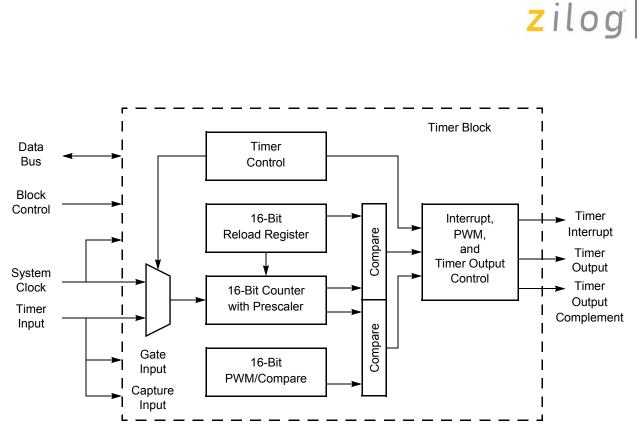

Figure 9. Timer Block Diagram

## Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

#### **Timer Operating Modes**

The timers can be configured to operate in the following modes:

#### **ONE-SHOT Mode**

In ONE-SHOT mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. The timer is automatically disabled and stops counting.

70

Z8 Encore! XP<sup>®</sup> F082A Series

**Product Specification**

zilog<sup>°</sup>.

#### **PWM DUAL OUTPUT Mode**

In PWM DUAL OUTPUT mode, the timer outputs a Pulse-Width Modulated (PWM) output signal pair (basic PWM signal and its complement) through two GPIO Port pins. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

If the TPOL bit in the Timer Control register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

The timer also generates a second PWM output signal Timer Output Complement. The Timer Output Complement is the complement of the Timer Output PWM signal. A programmable deadband delay can be configured to time delay (0 to 128 system clock cycles) PWM output transitions on these two pins from a low to a high (inactive to active). This ensures a time gap between the deassertion of one PWM output to the assertion of its complement.

Follow the steps below for configuring a timer for PWM DUAL OUTPUT mode and initiating the PWM operation:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for PWM DUAL OUTPUT mode by writing the TMODE bits in the TxCTL1 register and the TMODEHI bit in TxCTL0 register.

- Set the prescale value.

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the PWM Control register to set the PWM dead band delay value. The deadband delay must be less than the duration of the positive phase of the PWM signal (as defined by the PWM high and low byte registers). It must also be less than the

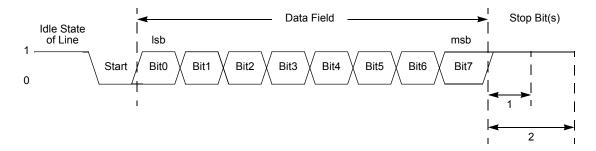

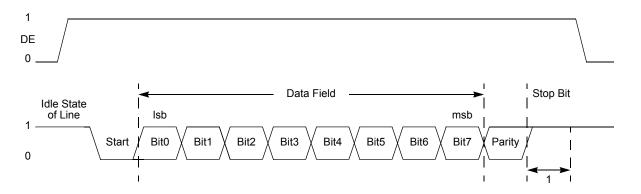

Figure 11. UART Asynchronous Data Format without Parity

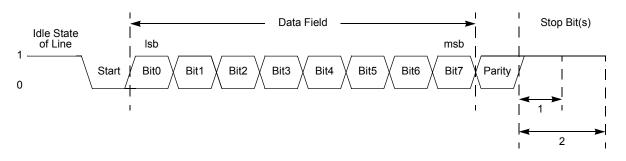

Figure 12. UART Asynchronous Data Format with Parity

#### Transmitting Data using the Polled Method

Follow the steps below to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Write to the UART Control 1 register, if MULTIPROCESSOR mode is appropriate, to enable MULTIPROCESSOR (9-bit) mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR mode.

- 5. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR mode is not enabled, and select either even or odd parity (PSEL).

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin.

**z**ilog<sup>°</sup>

configuration bits. In general, the address compare feature reduces the load on the CPU, because it does not require access to the UART when it receives data directed to other devices on the multi-node network. The following three MULTIPROCESSOR modes are available in hardware:

- 1. Interrupt on all address bytes.

- 2. Interrupt on matched address bytes and correctly framed data bytes.

- 3. Interrupt only on correctly framed data bytes.

These modes are selected with MPMD [1:0] in the UART Control 1 Register. For all multiprocessor modes, bit MPEN of the UART Control 1 Register must be set to 1.

The first scheme is enabled by writing 01b to MPMD[1:0]. In this mode, all incoming address bytes cause an interrupt, while data bytes never cause an interrupt. The interrupt service routine must manually check the address byte that caused triggered the interrupt. If it matches the UART address, the software clears MPMD[0]. Each new incoming byte interrupts the CPU. The software is responsible for determining the end of the frame. It checks for the end-of-frame by reading the MPRX bit of the UART Status 1 Register for each incoming byte. If MPRX=1, a new frame has begun. If the address of this new frame is different from the UART's address, MPMD[0] must be set to 1 causing the UART interrupts to go inactive until the next address byte. If the new frame's address matches the UART's, the data in the new frame is processed as well.

The second scheme requires the following: set MPMD[1:0] to 10B and write the UART's address into the UART Address Compare Register. This mode introduces additional hardware control, interrupting only on frames that match the UART's address. When an incoming address byte does not match the UART's address, it is ignored. All successive data bytes in this frame are also ignored. When a matching address byte occurs, an interrupt is issued and further interrupts now occur on each successive data byte. When the first data byte in the frame is read, the NEWFRM bit of the UART Status 1 Register is asserted. All successive data bytes have NEWFRM=0. When the next address byte occurs, the hardware compares it to the UART's address. If there is a match, the interrupts continues and the NEWFRM bit is set for the first byte of the new frame. If there is no match, the UART ignores all incoming bytes until the next address match.

The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second scheme, except that there are no interrupts on address bytes. The first data byte of each frame remains accompanied by a NEWFRM assertion.

#### **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

**z**ilog<sup>®</sup>

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART Transmit Data register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

#### Figure 14. UART Driver Enable Signal Timing (shown with 1 Stop Bit and Parity)

The Driver Enable to Start bit setup time is calculated as follows:

$$\left(\frac{1}{\text{Baud Rate (Hz)}}\right) \le \text{DE to Start Bit Setup Time (s)} \le \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

#### **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

#### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit shift register has shifted the first bit of data out. The Transmit Data register can now be written with the next character to

105

zilog

baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal, allowing the Endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

## Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined in Universal Asynchronous Receiver/Transmitter on page 97.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO Port alternate function for the corresponding pin.

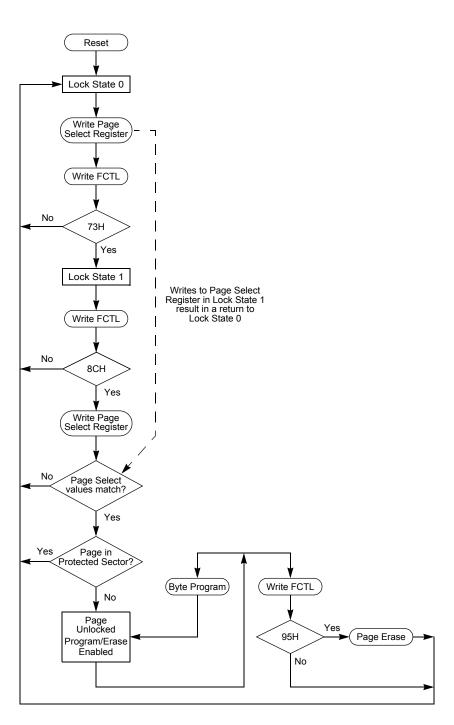

## **Flash Memory**

The products in the Z8 Encore! XP<sup>®</sup> F082A Series feature a non-volatile Flash memory of 8 KB (8192), 4 KB (4096), 2 KB (2048 bytes), or 1 KB (1024) with read/write/ erase capability. The Flash Memory can be programmed and erased in-circuit by user code or through the On-Chip Debugger. The features include:

- User controlled read and write protect capability

- Sector-based write protection scheme

- Additional protection schemes against accidental program and erasure

#### Architecture

The Flash memory array is arranged in pages with 512 bytes per page. The 512 byte page is the minimum Flash block size that can be erased. Each page is divided into 8 rows of 64 bytes.

For program or data protection, the Flash memory is also divided into sectors. In the Z8 Encore! XP F082A Series, these sectors are either 1024 bytes (in the 8 KB devices) or 512 bytes (all other memory sizes) in size. Page and sector sizes are not generally equal.

The first 2 bytes of the Flash Program memory are used as Flash Option Bits. For more information about their operation, see Flash Option Bits on page 153.

Table 76 describes the Flash memory configuration for each device in the Z8 Encore! XPF082A Series. Figure 21 displays the Flash memory arrangement.

| Part Number | Flash Size<br>KB (Bytes) | Flash<br>Pages | Program Memory<br>Addresses | Flash Sector<br>Size (Bytes) |

|-------------|--------------------------|----------------|-----------------------------|------------------------------|

| Z8F08xA     | 8 (8192)                 | 16             | 0000H–1FFFH                 | 1024                         |

| Z8F04xA     | 4 (4096)                 | 8              | 0000H-0FFFH                 | 512                          |

| Z8F02xA     | 2 (2048)                 | 4              | 0000H–07FFH                 | 512                          |

| Z8F01xA     | 1 (1024)                 | 2              | 0000H-03FFH                 | 512                          |

#### Table 76. Z8 Encore! XP F082A Series Flash Memory Configurations

zilog <sub>142</sub>

| 8 KB Flash<br>Program Memor | Addresses (hex) | 4 KB Flash<br>Program Memory | /<br>Addresses (hex)<br>1 0FFF | 2 KB Flash<br>Program Memory<br>Address | /<br>es (hex)        |

|-----------------------------|-----------------|------------------------------|--------------------------------|-----------------------------------------|----------------------|

| Sector 7                    | 1FFF<br>1C00    | Sector 7                     | 0E00                           | Sector 3                                | 07FF<br>0600         |

| Sector 6                    | 1BFF            | Sector 6                     | 0DFF                           | Sector 2                                | 05FF<br>0400<br>03FF |

| Castar 5                    | 1800<br>17FF    | Sector 5                     | 0C00<br>0BFF                   | Sector 1                                | 0200<br>01FF         |

| Sector 5                    | 1400<br>13FF    |                              | 0A00<br>09FF                   | Sector 0                                | 0000                 |

| Sector 4                    | 1000            | Sector 4                     | 0800                           |                                         |                      |

| Sector 3                    | 0FFF<br>0C00    | Sector 3                     | 07FF<br>0600                   | 1 KB Flash<br>Program Memory            | y<br>ses (hex)       |

| Sector 2                    | 0BFF<br>0800    | Sector 2                     | 05FF<br>0400                   | Sector 1                                | 03FF                 |

| Sector 1                    | 07FF<br>0400    | Sector 1                     | 03FF<br>0200                   | Sector 0                                | 01FF                 |

| Sector 0                    | 03FF<br>0000    | Sector 0                     | 01FF<br>0000                   |                                         |                      |

Figure 21. Flash Memory Arrangement

## **Flash Information Area**

The Flash information area is separate from Program Memory and is mapped to the address range FE00H to FFFFH. This area is readable but cannot be erased or overwritten. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

Figure 22. Flash Controller Operation Flow Chart

zilog

165

WDTCALH—Watchdog Timer Calibration High Byte The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload registers result in a one second timeout at room temperature and 3.3 V supply voltage. To use the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDTCALH and WDTL with WDTCALL.

#### Table 98. Watchdog Calibration Low Byte at 007FH (WDTCALL)

| BITS      | 7                             | 6            | 5            | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-----------|-------------------------------|--------------|--------------|-----|-----|-----|-----|-----|--|--|--|

| FIELD     | WDTCALL                       |              |              |     |     |     |     |     |  |  |  |

| RESET     | U                             | U            | U            | U   | U   | U   | U   | U   |  |  |  |

| R/W       | R/W                           | R/W          | R/W          | R/W | R/W | R/W | R/W | R/W |  |  |  |

| ADDR      | Information Page Memory 007FH |              |              |     |     |     |     |     |  |  |  |

| Note: U = | Unchanged b                   | y Reset. R/W | = Read/Write |     |     |     |     |     |  |  |  |

#### WDTCALL—Watchdog Timer Calibration Low Byte

The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload registers result in a one second timeout at room temperature and 3.3 V supply voltage. To use the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDTCALH and WDTL with WDTCALL.

#### **Serialization Data**

#### Table 99. Serial Number at 001C - 001F (S\_NUM)

| BITS      | 7                                 | 6            | 5            | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-----------|-----------------------------------|--------------|--------------|-----|-----|-----|-----|-----|--|--|--|

| FIELD     | S_NUM                             |              |              |     |     |     |     |     |  |  |  |

| RESET     | U                                 | U            | U            | U   | U   | U   | U   | U   |  |  |  |

| R/W       | R/W                               | R/W          | R/W          | R/W | R/W | R/W | R/W | R/W |  |  |  |

| ADDR      | Information Page Memory 001C-001F |              |              |     |     |     |     |     |  |  |  |

| Note: U = | Unchanged by                      | y Reset. R/W | = Read/Write | e.  |     |     |     |     |  |  |  |

S NUM—Serial Number Byte

The serial number is a unique four-byte binary value.

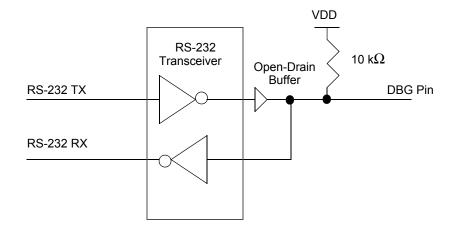

#### Figure 25. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (2)

#### **DEBUG Mode**

The operating characteristics of the devices in DEBUG mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions.

- The system clock operates unless in STOP mode.

- All enabled on-chip peripherals operate unless in STOP mode.

- Automatically exits HALT mode.

- Constantly refreshes the Watchdog Timer, if enabled.

#### **Entering DEBUG Mode**

The operating characteristics of the devices entering DEBUG mode are:

- The device enters DEBUG mode after the eZ8 CPU executes a BRK (Breakpoint) instruction.

- If the DBG pin is held Low during the final clock cycle of system reset, the part enters DEBUG mode immediately (20-/28-pin products only).

- **Note:** Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an Autobaud sequence (see OCD Auto-Baud Detector/Generator on page 176).

zilog | 177

The Auto-Baud Detector/Generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous datastreams, the maximum recommended baud rate is the system clock frequency divided by 8. The maximum possible baud rate for asynchronous datastreams is the system clock frequency divided by 4, but this theoretical maximum is possible only for low noise designs with clean signals. Table 105 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock<br>Frequency (MHz) | Recommended Maximum<br>Baud Rate (Kbps) | Recommended<br>Standard PC<br>Baud Rate (bps) | Minimum Baud<br>Rate (Kbps) |

|---------------------------------|-----------------------------------------|-----------------------------------------------|-----------------------------|

| 20.0                            | 2500.0                                  | 1,843,200                                     | 39                          |

| 1.0                             | 125.0                                   | 115,200                                       | 1.95                        |

| 0.032768 (32 kHz)               | 4.096                                   | 2,400                                         | 0.064                       |

#### Table 105. OCD Baud-Rate Limits

If the OCD receives a Serial Break (nine or more continuous bits Low) the Auto-Baud Detector/Generator resets. Reconfigure the Auto-Baud Detector/Generator by sending 80H.

#### **OCD Serial Errors**

The On-Chip Debugger can detect any of the following error conditions on the DBG pin:

- Serial Break (a minimum of nine continuous bits Low)

- Framing Error (received Stop bit is Low)

- Transmit Collision (OCD and host simultaneous transmission detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long Serial Break back to the host, and resets the Auto-Baud Detector/Generator. A Framing Error or Transmit Collision may be caused by the host sending a Serial Break to the OCD. Because of the open-drain nature of the interface, returning a Serial Break break back to the host only extends the length of the Serial Break if the host releases the Serial Break early.

The host transmits a Serial Break on the DBG pin when first connecting to the Z8 Encore! XP F082A Series devices or when recovering from an error. A Serial Break from the host resets the Auto-Baud Generator/Detector but does not reset the OCD Control register. A Serial Break leaves the device in DEBUG mode if that is the current mode. The OCD is held in Reset until the end of the Serial Break when the DBG pin returns

zilog

183

```

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

• **Read Data Memory (0DH)**—The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode, this command returns FFH for the data.

```

DBG \leftarrow 0DH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

• **Read Program Memory CRC (0EH)**—The Read Program Memory CRC command computes and returns the Cyclic Redundancy Check (CRC) of Program Memory using the 16-bit CRC-CCITT polynomial. If the device is not in DEBUG mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program Memory, calculates the CRC value, and returns the result. The delay is a function of the Program Memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program Memory.

DBG  $\leftarrow$  0EH DBG  $\rightarrow$  CRC[15:8] DBG  $\rightarrow$  CRC[7:0]

• Step Instruction (10H)—The Step Instruction command steps one assembly instruction at the current Program Counter (PC) location. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

DBG  $\leftarrow$  10H

• Stuff Instruction (11H)—The Stuff Instruction command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0-4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

• **Execute Instruction (12H)**—The Execute Instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over Breakpoints. The number of bytes to send for the instruction depends on the opcode.

# zilog

# **Internal Precision Oscillator**

The internal precision oscillator (IPO) is designed for use without external components. You can either manually trim the oscillator for a non-standard frequency or use the automatic factory-trimmed version to achieve a 5.53 MHz frequency. IPO features include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8 kHz (contains both a fast and a slow mode)

- Trimmed through Flash option bits with user override

- Elimination of crystals or ceramic resonators in applications where very high timing accuracy is not required

## Operation

An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed the oscillator frequency is stable and does not require subsequent calibration. Trimming is performed during manufacturing and is not necessary for you to repeat unless a frequency other than 5.53 MHz (fast mode) or 32.8 kHz (slow mode) is required. This trimming is done at +30 °C and a supply voltage of 3.3 V, so accuracy of this operating point is optimal.

If not used, the IPO can be disabled by the Oscillator Control register (see Oscillator Control Register Definitions on page 190).

By default, the oscillator frequency is set by the factory trim value stored in the write-protected Flash information page. However, the user code can override these trim values as described in Trim Bit Address Space on page 158.

Select one of two frequencies for the oscillator: 5.53 MHz and 32.8 kHz, using the OSCSEL bits in the Oscillator Control on page 187.

264

**DJNZ 206** EI 204 **HALT 204 INC 203 INCW 203 IRET 206** JP 206 LD 205 LDC 205 LDCI 204, 205 LDE 205 LDEI 204 LDX 205 LEA 205 logical 205 **MULT 203** NOP 204 OR 205 **ORX 206** POP 205 **POPX 205** program control 206 **PUSH 205** PUSHX 205 **RCF 204 RET 206** RL 206 **RLC 206** rotate and shift 206 RR 206 **RRC 206** SBC 203 SCF 204, 205 SRA 207 SRL 207 **SRP 205 STOP 205** SUB 203 SUBX 203 **SWAP 207** TCM 204 **TCMX 204** TM 204 TMX 204

**TRAP 206** Watchdog Timer refresh 205 XOR 206 **XORX 206** instructions, eZ8 classes of 202 interrupt control register 67 interrupt controller 55 architecture 55 interrupt assertion types 58 interrupt vectors and priority 58 operation 57 register definitions 60 software interrupt assertion 59 interrupt edge select register 66 interrupt request 0 register 60 interrupt request 1 register 61 interrupt request 2 register 62 interrupt return 206 interrupt vector listing 55 interrupts **UART 105** IR 201 lr 201 IrDA architecture 117 block diagram 117 control register definitions 120 operation 117 receiving data 119 transmitting data 118 **IRET 206** IRQ0 enable high and low bit registers 62 IRQ1 enable high and low bit registers 63 IRQ2 enable high and low bit registers 65 **IRR 201** Irr 201

## J

JP 206 jump, conditional, relative, and relative conditional 206