### Zilog - Z8F022APB020SC Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 6                                                            |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64 x 8                                                       |

| RAM Size                   | 512 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 4x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                       |

| Supplier Device Package    | <u>.</u>                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022apb020sc    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| BITS  | 7     | 6            | 5     | 4   | 3        | 2 | 1 | 0   |

|-------|-------|--------------|-------|-----|----------|---|---|-----|

| FIELD | POR   | STOP         | WDT   | EXT | Reserved |   |   | LVD |

| RESET | See d | lescriptions | below | 0   | 0 0 0    |   |   | 0   |

| R/W   | R     | R            | R     | R   | R R R F  |   |   | R   |

| ADDR  |       | FF0H         |       |     |          |   |   |     |

### Table 11. Reset Status Register (RSTSTAT)

| Reset or Stop Mode Recovery Event                     | POR | STOP | WDT | EXT |

|-------------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                        | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion                       | 0   | 0    | 0   | 1   |

| Reset using Watchdog Timer time-out                   | 0   | 0    | 1   | 0   |

| Reset using the On-Chip Debugger (OCTCTL[1] set to 1) | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low         | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition          | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using Watchdog Timer time-out      | 0   | 1    | 1   | 0   |

### POR—Power-On Reset Indicator

If this bit is set to 1, a Power-On Reset event occurs. This bit is reset to 0 if a WDT time-out or Stop Mode Recovery occurs. This bit is also reset to 0 when the register is read.

### STOP—Stop Mode Recovery Indicator

If this bit is set to 1, a Stop Mode Recovery occurs. If the STOP and WDT bits are both set to 1, the Stop Mode Recovery occurs because of a WDT time-out. If the STOP bit is 1 and the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a Power-On Reset or a WDT time-out that occurred while not in STOP mode. Reading this register also resets this bit.

### WDT—Watchdog Timer Time-Out Indicator

If this bit is set to 1, a WDT time-out occurs. A POR resets this pin. A Stop Mode Recovery from a change in an input pin also resets this bit. Reading this register resets this bit. This read must occur before clearing the WDT interrupt.

### EXT-External Reset Indicator

If this bit is set to 1, a Reset initiated by the external  $\overline{\text{RESET}}$  pin occurs. A Power-On Reset or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register resets this bit.

### Reserved—Must be 0.

LVD—Low Voltage Detection Indicator

If this bit is set to 1 the current state of the supply voltage is below the low voltage detection threshold. This value is not latched but is a real-time indicator of the supply voltage level.

LEDEN[7:0]—LED Drive Enable These bits determine which Port C pins are connected to an internal current sink. 0 = Tristate the Port C pin. 1= Enable controlled current sink on the Port C pin.

# LED Drive Level High Register

The LED Drive Level registers contain two control bits for each Port C pin (Table 30). These two bits select between four programmable drive levels. Each pin is individually programmable.

### Table 30. LED Drive Level High Register (LEDLVLH)

| BITS  | 7    | 6            | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|------|--------------|-----|-----|-----|-----|-----|-----|--|

| FIELD |      | LEDLVLH[7:0] |     |     |     |     |     |     |  |

| RESET | 0    | 0            | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W   | R/W  | R/W          | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR  | F83H |              |     |     |     |     |     |     |  |

LEDLVLH[7:0]—LED Level High Bit

{LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin.

00 = 3 mA 01= 7 mA 10= 13 mA 11= 20 mA

## **LED Drive Level Low Register**

The LED Drive Level registers contain two control bits for each Port C pin (Table 31). These two bits select between four programmable drive levels. Each pin is individually programmable.

**Caution:** The following coding style that clears bits in the Interrupt Request registers is not recommended. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost.

Poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

Caution: To avoid missing interrupts, use the following coding style to clear bits in the Interrupt Request 0 register:

Good coding style that avoids lost interrupt requests:

ANDX IRQ0, MASK

### Software Interrupt Assertion

Program code can generate interrupts directly. Writing a 1 to the correct bit in the Interrupt Request register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request register is automatically cleared to 0.

**Caution:** The following coding style used to generate software interrupts by setting bits in the Interrupt Request registers is not recommended. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost.

Poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 OR r0, MASK LDX IRQ0, r0

**Caution:** To avoid missing interrupts, use the following coding style to set bits in the Interrupt Request registers:

> Good coding style that avoids lost interrupt requests: ORX IRQO, MASK

### Watchdog Timer Interrupt Assertion

The Watchdog Timer interrupt behavior is different from interrupts generated by other sources. The Watchdog Timer continues to assert an interrupt as long as the timeout condition continues. As it operates on a different (and usually slower) clock domain than the rest of the device, the Watchdog Timer continues to assert this interrupt for many system clocks until the counter rolls over.

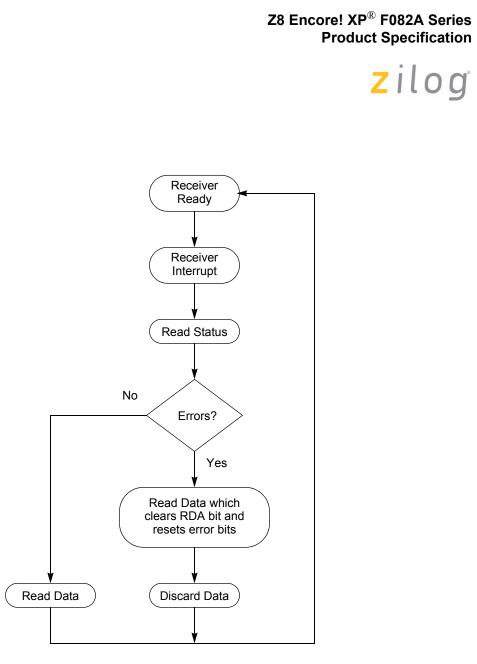

Figure 15. UART Receiver Interrupt Service Routine Flow

### **Baud Rate Generator Interrupts**

If the baud rate generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud Rate Generator to function as an additional counter if the UART functionality is not employed.

# **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value

107

MPRX—Multiprocessor Receive

Returns the value of the most recent multiprocessor bit received. Reading from the UART Receive Data register resets this bit to 0.

# **UART Transmit Data Register**

Data bytes written to the UART Transmit Data (UxTXD) register (Table 65) are shifted out on the TXDx pin. The Write-only UART Transmit Data register shares a Register File address with the read-only UART Receive Data register.

| BITS  | 7 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|------|---|---|---|---|---|---|--|

| FIELD |   | TXD  |   |   |   |   |   |   |  |

| RESET | Х | Х    | Х | Х | Х | Х | Х | Х |  |

| R/W   | W | W    | W | W | W | W | W | W |  |

| ADDR  |   | F40H |   |   |   |   |   |   |  |

### Table 65. UART Transmit Data Register (U0TXD)

TXD-Transmit Data

UART transmitter data byte to be shifted out through the TXDx pin.

## **UART Receive Data Register**

Data bytes received through the RXDx pin are stored in the UART Receive Data (UxRXD) register (Table 66). The read-only UART Receive Data register shares a Register File address with the Write-only UART Transmit Data register.

### Table 66. UART Receive Data Register (U0RXD)

| BITS           | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|----------------|------|---|---|---|---|---|---|---|--|

| FIELD          | RXD  |   |   |   |   |   |   |   |  |

| RESET          | Х    | Х | Х | Х | Х | Х | Х | Х |  |

| R/W            | R    | R | R | R | R | R | R | R |  |

| ADDR           | F40H |   |   |   |   |   |   |   |  |

| X = Undefined. |      |   |   |   |   |   |   |   |  |

RXD—Receive Data

UART receiver data byte from the RXDx pin

# **ADC Control Register Definitions**

# ADC Control Register 0

The ADC Control Register 0 (ADCCTL0) selects the analog input channel and initiates the analog-to-digital conversion. It also selects the voltage reference configuration.

Table 71. ADC Control Register 0 (ADCCTL0)

| BITS  | 7   | 6       | 5      | 4    | 3          | 2   | 1   | 0   |

|-------|-----|---------|--------|------|------------|-----|-----|-----|

| FIELD | CEN | REFSELL | REFOUT | CONT | ANAIN[3:0] |     |     |     |

| RESET | 0   | 0       | 0      | 0    | 0          | 0   | 0   | 0   |

| R/W   | R/W | R/W     | R/W    | R/W  | R/W        | R/W | R/W | R/W |

| ADDR  |     | F70H    |        |      |            |     |     |     |

### CEN—Conversion Enable

0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion is complete.

1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.

REFSELL—Voltage Reference Level Select Low Bit; in conjunction with the High bit (REFSELH) in ADC Control/Status Register 1, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL}; note that this reference is independent of the Comparator reference.

00= Internal Reference Disabled, reference comes from external pin

01= Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

11= Reserved

REFOUT—Internal Reference Output Enable

0 = Reference buffer is disabled; Vref pin is available for GPIO or analog functions

1 = The internal ADC reference is buffered and driven out to the Vref pin

<u>/</u>

**Warning:** When the ADC is used with an external reference ({REFSELH,REFSELL}=00), the REFOUT bit must be set to 0.

### CONT

0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles (measurements of the internal temperature sensor take twice as long) 1 = Continuous conversion. ADC data updated every 256 system clock cycles after an initial 5129 clock conversion (measurements of the internal temperature sensor take twice as long)

138

# **Flash Option Bits**

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore! XP<sup>®</sup> F082A Series operation. The feature configuration data is stored in the Flash program memory and loaded into holding registers during Reset. The features available for control through the Flash Option Bits include:

- Watchdog Timer time-out response selection-interrupt or system reset

- Watchdog Timer always on (enabled at Reset)

- The ability to prevent unwanted read access to user code in Program Memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Program Memory

- Voltage Brownout configuration-always enabled or disabled during STOP mode to reduce STOP mode power consumption

- Oscillator mode selection-for high, medium, and low power crystal oscillators, or external RC oscillator

- Factory trimming information for the internal precision oscillator and low voltage detection

- Factory calibration values for ADC, temperature sensor, and Watchdog Timer compensation

- Factory serialization and randomized lot identifier (optional)

# Operation

### **Option Bit Configuration By Reset**

Each time the Flash Option Bits are programmed or erased, the device must be Reset for the change to take effect. During any reset operation (System Reset, Power-On Reset, or Stop Mode Recovery), the Flash Option Bits are automatically read from the Flash Program Memory and written to Option Configuration registers. The Option Configuration registers control operation of the devices within the Z8 Encore! XP F082A Series. Option Bit control is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

zilog

163

| Info Page<br>Address | Memory<br>Address | Compensation Usage      | ADC Mode                 | Reference<br>Type |

|----------------------|-------------------|-------------------------|--------------------------|-------------------|

| 34                   | FE34              | Negative Gain High Byte | Differential Unbuffered  | External 2.0 V    |

| 35                   | FE35              | Negative Gain Low Byte  | Differential Unbuffered  | External 2.0 V    |

| 78                   | FE78              | Offset                  | Differential 1x Buffered | Internal 2.0 V    |

| 18                   | FE18              | Positive Gain High Byte | Differential 1x Buffered | Internal 2.0 V    |

| 19                   | FE19              | Positive Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V    |

| 36                   | FE36              | Negative Gain High Byte | Differential 1x Buffered | Internal 2.0 V    |

| 37                   | FE37              | Negative Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V    |

| 7B                   | FE7B              | Offset                  | Differential 1x Buffered | External 2.0 V    |

| 1A                   | FE1A              | Positive Gain High Byte | Differential 1x Buffered | External 2.0 V    |

| 1B                   | FE1B              | Positive Gain Low Byte  | Differential 1x Buffered | External 2.0 V    |

| 38                   | FE38              | Negative Gain High Byte | Differential 1x Buffered | External 2.0 V    |

| 39                   | FE39              | Negative Gain Low Byte  | Differential 1x Buffered | External 2.0 V    |

### Table 94. ADC Calibration Data Location (Continued)

zilog

165

WDTCALH—Watchdog Timer Calibration High Byte The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload registers result in a one second timeout at room temperature and 3.3 V supply voltage. To use the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDTCALH and WDTL with WDTCALL.

### Table 98. Watchdog Calibration Low Byte at 007FH (WDTCALL)

| BITS      | 7                             | 6                           | 5            | 4 | 3 | 2 | 1 | 0 |  |

|-----------|-------------------------------|-----------------------------|--------------|---|---|---|---|---|--|

| FIELD     | WDTCALL                       |                             |              |   |   |   |   |   |  |

| RESET     | U                             | U                           | U            | U | U | U | U | U |  |

| R/W       | R/W                           | R/W R/W R/W R/W R/W R/W R/W |              |   |   |   |   |   |  |

| ADDR      | Information Page Memory 007FH |                             |              |   |   |   |   |   |  |

| Note: U = | Unchanged b                   | y Reset. R/W                | = Read/Write |   |   |   |   |   |  |

WDTCALL—Watchdog Timer Calibration Low Byte

The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload registers result in a one second timeout at room temperature and 3.3 V supply voltage. To use the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDTCALH and WDTL with WDTCALL.

# **Serialization Data**

### Table 99. Serial Number at 001C - 001F (S\_NUM)

| BITS      | 7                                 | 6            | 5            | 4   | 3   | 2   | 1   | 0   |  |

|-----------|-----------------------------------|--------------|--------------|-----|-----|-----|-----|-----|--|

| FIELD     | S_NUM                             |              |              |     |     |     |     |     |  |

| RESET     | U                                 |              |              |     |     |     |     |     |  |

| R/W       | R/W                               | R/W          | R/W          | R/W | R/W | R/W | R/W | R/W |  |

| ADDR      | Information Page Memory 001C-001F |              |              |     |     |     |     |     |  |

| Note: U = | Unchanged by                      | y Reset. R/W | = Read/Write | e.  |     |     |     |     |  |

S NUM—Serial Number Byte

The serial number is a unique four-byte binary value.

# **Non-Volatile Data Storage**

The Z8 Encore! XP<sup>®</sup> F082A Series devices contain a non-volatile data storage (NVDS) element of up to 128 bytes. This memory can perform over 100,000 write cycles.

# Operation

The NVDS is implemented by special purpose Zilog<sup>®</sup> software stored in areas of program memory, which are not user-accessible. These special-purpose routines use the Flash memory to store the data. The routines incorporate a dynamic addressing scheme to maximize the write/erase endurance of the Flash.

Note: Different members of the Z8 Encore! XP F082A Series feature multiple NVDS array sizes. See Z8 Encore! XP<sup>®</sup> F082A Series Family Part Selection Guide on page 3 for details. Also the members containing 8 KB of Flash memory do not include the NVDS feature.

# **NVDS Code Interface**

Two routines are required to access the NVDS: a write routine and a read routine. Both of these routines are accessed with a CALL instruction to a pre-defined address outside of the user-accessible program memory. Both the NVDS address and data are single-byte values. Because these routines disturb the working register set, user code must ensure that any required working register values are preserved by pushing them onto the stack or by changing the working register pointer just prior to NVDS execution.

During both read and write accesses to the NVDS, interrupt service is NOT disabled. Any interrupts that occur during the NVDS execution must take care not to disturb the working register and existing stack contents or else the array may become corrupted. Disabling interrupts before executing NVDS operations is recommended.

Use of the NVDS requires 15 bytes of available stack space. Also, the contents of the working register set are overwritten.

For correct NVDS operation, the Flash Frequency Registers must be programmed based on the system clock frequency (see Flash Operation Timing Using the Flash Frequency Registers on page 145).

### Byte Write

To write a byte to the NVDS array, the user code must first push the address, then the data byte onto the stack. The user code issues a CALL instruction to the address of the byte-write routine (0x10B3). At the return from the sub-routine, the write status byte

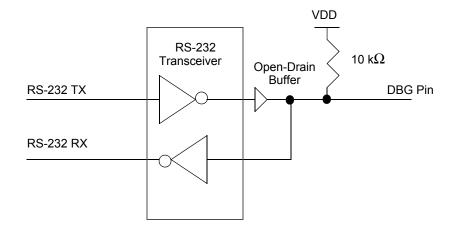

### Figure 25. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (2)

### **DEBUG Mode**

The operating characteristics of the devices in DEBUG mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions.

- The system clock operates unless in STOP mode.

- All enabled on-chip peripherals operate unless in STOP mode.

- Automatically exits HALT mode.

- Constantly refreshes the Watchdog Timer, if enabled.

### **Entering DEBUG Mode**

The operating characteristics of the devices entering DEBUG mode are:

- The device enters DEBUG mode after the eZ8 CPU executes a BRK (Breakpoint) instruction.

- If the DBG pin is held Low during the final clock cycle of system reset, the part enters DEBUG mode immediately (20-/28-pin products only).

- **Note:** Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an Autobaud sequence (see OCD Auto-Baud Detector/Generator on page 176).

If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

DBG  $\leftarrow$  12H DBG  $\leftarrow$  1-5 byte opcode

# **On-Chip Debugger Control Register Definitions**

# **OCD Control Register**

The OCD Control register controls the state of the On-Chip Debugger. This register is used to enter or exit DEBUG mode and to enable the BRK instruction. It can also reset the Z8 Encore! XP<sup>®</sup> F082A Series device.

A reset and stop function can be achieved by writing \$1H to this register. A reset and go function can be achieved by writing \$1H to this register. If the device is in DEBUG mode, a run function can be implemented by writing \$0H to this register.

### Table 106. OCD Control Register (OCDCTL)

| BITS  | 7       | 6     | 5      | 4        | 3 | 2 | 1 | 0   |

|-------|---------|-------|--------|----------|---|---|---|-----|

| FIELD | DBGMODE | BRKEN | DBGACK | Reserved |   |   |   | RST |

| RESET | 0       | 0     | 0      | 0        | 0 | 0 | 0 | 0   |

| R/W   | R/W     | R/W   | R/W    | R        | R | R | R | R/W |

### DBGMODE—DEBUG Mode

The device enters DEBUG mode when this bit is 1. When in DEBUG mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is automatically set when a BRK instruction is decoded and Breakpoints are enabled. If the Flash Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device. It cannot be written to 0.

0 = The Z8 Encore! XP F082A Series device is operating in NORMAL mode.

1 = The Z8 Encore! XP F082A Series device is in DEBUG mode.

### BRKEN—Breakpoint Enable

This bit controls the behavior of the BRK instruction (opcode 00H). By default, Breakpoints are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1, when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL register is automatically set to 1.

0 = Breakpoints are disabled.

1 = Breakpoints are enabled.

### 200

# Assembly Language Syntax

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed if manual program coding is preferred or if you intend to implement your own assembler.

**Example 1**: If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

### Table 112. Assembly Language Syntax Example 1

| Assembly Language<br>Code | ADD | 43H, | 08H | (ADD dst, src) |

|---------------------------|-----|------|-----|----------------|

| Object Code               | 04  | 08   | 43  | (OPC src, dst) |

**Example 2**: In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

### Table 113. Assembly Language Syntax Example 2

| Assembly Language<br>Code | ADD | 43H, | R8 | (ADD dst, src) |

|---------------------------|-----|------|----|----------------|

| Object Code               | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

# eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is described in Table 114.

<mark>z</mark>ilog<sup>°</sup>

| 211 |

|-----|

| Assembly<br>Mnemonic | Symbolic                                                     | Addres | s Mode | Opcode(s) |   |   | Fla                            | ags | Fetch | Instr. |        |   |

|----------------------|--------------------------------------------------------------|--------|--------|-----------|---|---|--------------------------------|-----|-------|--------|--------|---|

|                      | Operation                                                    | dst    | src    | (Hex)     | С | Ζ | S                              | ۷   | D     | Н      | Cycles |   |

| LDC dst, src         | $dst \gets src$                                              | r      | Irr    | C2        | - | _ | -                              | -   | _     | -      | 2      | 5 |

|                      |                                                              | lr     | Irr    | C5        | - |   |                                |     |       |        | 2      | 9 |

|                      |                                                              | Irr    | r      | D2        | - |   |                                |     |       |        | 2      | 5 |

| LDCI dst, src        | $dst \leftarrow src$                                         | lr     | Irr    | C3        | - | - | -                              | -   | -     | -      | 2      | 9 |

|                      | r ← r + 1<br>rr ← rr + 1                                     | Irr    | Ir     | D3        | - |   |                                |     |       |        | 2      | 9 |

| LDE dst, src         | $dst \gets src$                                              | r      | Irr    | 82        | - | _ | -                              | -   | _     | -      | 2      | 5 |

|                      |                                                              | Irr    | r      | 92        | - |   |                                |     |       |        | 2      | 5 |

| LDEI dst, src        | $dst \gets src$                                              | lr     | Irr    | 83        | _ | _ | -                              | -   | -     | _      | 2      | 9 |

|                      | r ← r + 1<br>rr ← rr + 1                                     | Irr    | lr     | 93        | - |   |                                |     |       |        | 2      | 9 |

| LDWX dst, src        | $dst \gets src$                                              | ER     | ER     | 1FE8      | _ | _ | _                              | _   | _     | _      | 5      | 4 |

| LDX dst, src         | $dst \gets src$                                              | r      | ER     | 84        | - | - | -                              | -   | -     | -      | 3      | 2 |

|                      |                                                              | lr     | ER     | 85        | - |   |                                |     |       |        | 3      | 3 |

|                      |                                                              | R      | IRR    | 86        | - |   |                                |     |       |        | 3      | 4 |

|                      |                                                              | IR     | IRR    | 87        | - |   |                                |     |       |        | 3      | 5 |

|                      |                                                              | r      | X(rr)  | 88        | - |   |                                |     |       |        | 3      | 4 |

|                      |                                                              | X(rr)  | r      | 89        | - |   |                                |     |       |        | 3      | 4 |

|                      |                                                              | ER     | r      | 94        | - |   |                                |     |       |        | 3      | 2 |

|                      |                                                              | ER     | Ir     | 95        | - |   |                                |     |       |        | 3      | 3 |

|                      |                                                              | IRR    | R      | 96        | - |   |                                |     |       |        | 3      | 4 |

|                      |                                                              | IRR    | IR     | 97        | - |   |                                |     |       |        | 3      | 5 |

|                      |                                                              | ER     | ER     | E8        | - |   |                                |     |       |        | 4      | 2 |

|                      |                                                              | ER     | IM     | E9        | - |   |                                |     |       |        | 4      | 2 |

| LEA dst, X(src)      | $dst \gets src + X$                                          | r      | X(r)   | 98        | _ | _ | _                              | _   | -     | _      | 3      | 3 |

|                      |                                                              | rr     | X(rr)  | 99        | - |   |                                |     |       |        | 3      | 5 |

| MULT dst             | dst[15:0] ←<br>dst[15:8] * dst[7:0]                          | RR     |        | F4        | - | _ | _                              | -   | -     | -      | 2      | 8 |

| NOP                  | No operation                                                 |        |        | 0F        | _ | _ | _                              | _   | -     | _      | 1      | 2 |

| Flags Notation:      | * = Value is a function o<br>– = Unaffected<br>X = Undefined |        |        |           |   |   | 0 = Reset to 0<br>1 = Set to 1 |     |       |        |        |   |

### Table 124. eZ8 CPU Instruction Summary (Continued)

zilog <sub>217</sub>

| Abbreviation | Description                           | Abbreviation                                   | Description            |  |  |  |

|--------------|---------------------------------------|------------------------------------------------|------------------------|--|--|--|

| b            | Bit position                          | IRR                                            | Indirect Register Pair |  |  |  |

| сс           | Condition code                        | р                                              | Polarity (0 or 1)      |  |  |  |

| X            | 8-bit signed index or<br>displacement | r                                              | 4-bit Working Register |  |  |  |

| DA           | Destination address                   | R                                              | 8-bit register         |  |  |  |

| ER           | Extended Addressing register          | r1, R1, Ir1, Irr1, IR1,<br>rr1, RR1, IRR1, ER1 | Destination address    |  |  |  |

| IM           | Immediate data value                  | r2, R2, Ir2, Irr2, IR2,<br>rr2, RR2, IRR2, ER2 | Source address         |  |  |  |

| Ir           | Indirect Working Register             | RA                                             | Relative               |  |  |  |

| IR           | Indirect register                     | rr                                             | Working Register Pair  |  |  |  |

| Irr          | Indirect Working Register Pair        | RR                                             | Register Pair          |  |  |  |

### Table 125. Opcode Map Abbreviations

# Packaging

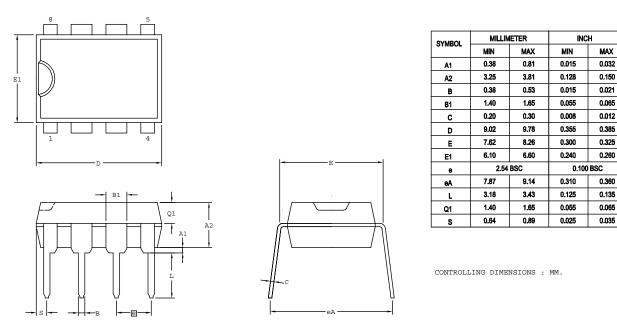

Figure 39 displays the 8-pin Plastic Dual Inline Package (PDIP) available for Z8 Encore!  $XP^{\textcircled{R}}$  F082A Series devices.

Figure 39. 8-Pin Plastic Dual Inline Package (PDIP)

| Part Number                         | Flash    | RAM      | NVDS   | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|-------------------------------------|----------|----------|--------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082A    | A Series | s with 8 | KB Fla | ash       |            |                     |                     |                |            |                    |                     |

| Standard Temperature: 0 °C to 70 °C |          |          |        |           |            |                     |                     |                |            |                    |                     |

| Z8F081APB020SC                      | 8 KB     | 1 KB     | 0      | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F081AQB020SC                      | 8 KB     | 1 KB     | 0      | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F081ASB020SC                      | 8 KB     | 1 KB     | 0      | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F081ASH020SC                      | 8 KB     | 1 KB     | 0      | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F081AHH020SC                      | 8 KB     | 1 KB     | 0      | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F081APH020SC                      | 8 KB     | 1 KB     | 0      | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F081ASJ020SC                      | 8 KB     | 1 KB     | 0      | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F081AHJ020SC                      | 8 KB     | 1 KB     | 0      | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F081APJ020SC                      | 8 KB     | 1 KB     | 0      | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperatur                 | e: -40 ° | C to 105 | 5 °C   |           |            |                     |                     |                |            |                    |                     |

| Z8F081APB020EC                      | 8 KB     | 1 KB     | 0      | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F081AQB020EC                      | 8 KB     | 1 KB     | 0      | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F081ASB020EC                      | 8 KB     | 1 KB     | 0      | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F081ASH020EC                      | 8 KB     | 1 KB     | 0      | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F081AHH020EC                      | 8 KB     | 1 KB     | 0      | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F081APH020EC                      | 8 KB     | 1 KB     | 0      | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F081ASJ020EC                      | 8 KB     | 1 KB     | 0      | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F081AHJ020EC                      | 8 KB     | 1 KB     | 0      | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F081APJ020EC                      | 8 KB     | 1 KB     | 0      | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Replace C with G for Lead           | d-Free P | ackaging |        |           |            |                     |                     |                |            |                    |                     |

263

page erase 147 page select register 150, 151 FPS register 150, 151 FSTAT register 150

# G

GATED mode 85 general-purpose I/O 37 GPIO 7, 37 alternate functions 38 architecture 38 control register definitions 45 input data sample timing 234 interrupts 45 port A-C pull-up enable sub-registers 50, 51 port A-H address registers 46 port A-H alternate function sub-registers 47 port A-H control registers 46 port A-H data direction sub-registers 47 port A-H high drive enable sub-registers 49 port A-H input data registers 51 port A-H output control sub-registers 48 port A-H output data registers 52 port A-H stop mode recovery sub-registers 49 port availability by device 37 port input timing 235 port output timing 236

# Η

H 202 HALT 204 halt mode 34, 204 hexadecimal number prefix/suffix 202

# I

I2C 7 IM 201 immediate data 201 immediate operand prefix 202 **INC 203** increment 203 increment word 203 **INCW 203** indexed 201 indirect address prefix 202 indirect register 201 indirect register pair 201 indirect working register 201 indirect working register pair 201 infrared encoder/decoder (IrDA) 117 Instruction Set 199 instruction set. eZ8 CPU 199 instructions ADC 203 ADCX 203 ADD 203 **ADDX 203** AND 205 **ANDX 205** arithmetic 203 **BCLR 204** BIT 204 bit manipulation 204 block transfer 204 **BRK 206 BSET 204** BSWAP 204, 206 **BTJ 206 BTJNZ 206 BTJZ 206 CALL 206** CCF 204 CLR 205 COM 205 CP 203 CPC 203 **CPCX 203** CPU control 204 **CPX 203** DA 203 **DEC 203 DECW 203**

DI 204

269

electrical characteristics and timing 230, 233 interrupt in normal operation 92 interrupt in STOP mode 92 operation 135 refresh 92, 205 reload unlock sequence 93 reload upper, high and low registers 94 reset 27 reset in normal operation 93 reset in STOP mode 93 time-out response 92 WDTCTL register 31, 94, 136, 190 WDTH register 95 WDTL register 95 working register 201 working register pair 201 WTDU register 95

# Х

X 201 XOR 206 XORX 206

# Ζ

Z8 Encore! block diagram 4 features 1 part selection guide 2