Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64 x 8                                                       |

| RAM Size                   | 512 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                      |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022aph020sc    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

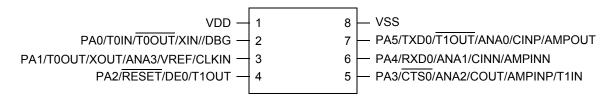

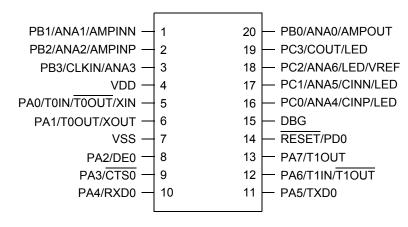

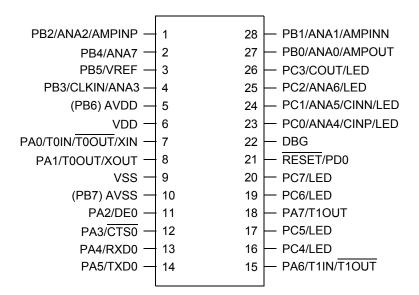

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

Figure 2. Z8F08xA, Z8F04xA, Z8F02xA, and Z8F01xA in 8-Pin SOIC, QFN/MLF-S, or PDIP Package

Figure 3. Z8F08xA, Z8F04xA, Z8F02xA, and Z8F01xA in 20-Pin SOIC, SSOP or PDIP Package

Figure 4. Z8F08xA, Z8F04xA, Z8F02xA, and Z8F01xA in 28-Pin SOIC, SSOP or PDIP Package

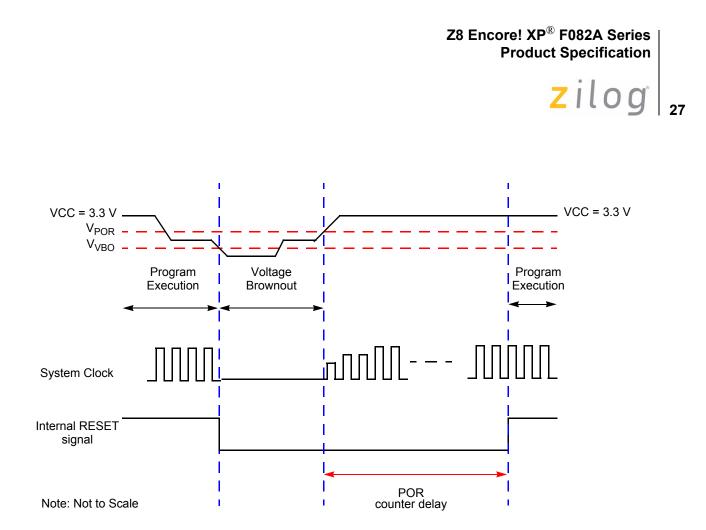

Figure 6. Voltage Brownout Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a Power-On Reset after recovering from a VBO condition.

## Watchdog Timer Reset

If the device is in NORMAL or HALT mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash Option Bit is programmed to 1. This is the unprogrammed state of the WDT\_RES Flash Option Bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT bit in the Reset Status (RSTSTAT) register is set to signify that the reset was initiated by the Watchdog Timer.

### External Reset Input

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system clock and reset signals, the required reset duration may be as short as three clock periods

## **GPIO Interrupts**

Many of the GPIO port pins can be used as interrupt sources. Some port pins can be configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). See Interrupt Controller on page 55 for more information about interrupts using the GPIO pins.

## **GPIO Control Register Definitions**

Four registers for each Port provide access to GPIO control, input data, and output data. Table 16 lists these Port registers. Use the Port A–D Address and Control registers together to provide access to sub-registers for Port configuration and control.

| Port Register Mnemonic     | Port Register Name                                              |

|----------------------------|-----------------------------------------------------------------|

| PxADDR                     | Port A–D Address Register<br>(Selects sub-registers)            |

| PxCTL                      | Port A–D Control Register<br>(Provides access to sub-registers) |

| PxIN                       | Port A–D Input Data Register                                    |

| PxOUT                      | Port A–D Output Data Register                                   |

| Port Sub-Register Mnemonic | Port Register Name                                              |

| PxDD                       | Data Direction                                                  |

| PxAF                       | Alternate Function                                              |

| PxOC                       | Output Control (Open-Drain)                                     |

| PxHDE                      | High Drive Enable                                               |

| PxSMRE                     | Stop Mode Recovery Source Enable                                |

| PxPUE                      | Pull-up Enable                                                  |

| PxAFS1                     | Alternate Function Set 1                                        |

| PxAFS2                     | Alternate Function Set 2                                        |

|                            |                                                                 |

| Table 16. | <b>GPIO Por</b> | t Registers | and Sub-Registers |

|-----------|-----------------|-------------|-------------------|

|-----------|-----------------|-------------|-------------------|

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source       |

|----------|-------------------------------------|--------------------------------|

|          | 0034H                               | Port C Pin 1, both input edges |

| Lowest   | 0036H                               | Port C Pin 0, both input edges |

|          | 0038H                               | Reserved                       |

#### Table 32. Trap and Interrupt Vectors in Order of Priority (Continued)

## Architecture

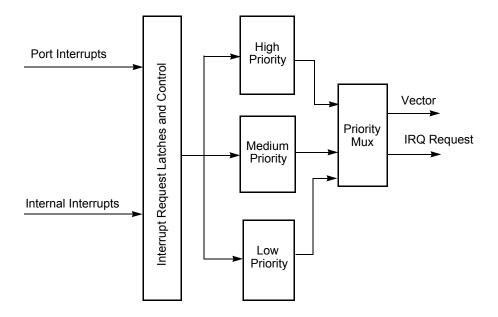

Figure 8 displays the interrupt controller block diagram.

Figure 8. Interrupt Controller Block Diagram

## Operation

#### **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control register globally enables and disables interrupts.

**Caution:** To avoid re-triggerings of the Watchdog Timer interrupt after exiting the associated interrupt service routine, it is recommended that the service routine continues to read from the RSTSTAT register until the WDT bit is cleared as given in the following coding sample:

CLEARWDT: LDX r0, RSTSTAT ; read reset status register to clear wdt bit BTJNZ 5, r0, CLEARWDT ; loop until bit is cleared

## **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap, and the Watchdog Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

### **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) register (Table 33) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 0 register to determine if any interrupt requests are pending.

| BITS  | 7        | 6                           | 5   | 4            | 3     | 2        | 1        | 0    |

|-------|----------|-----------------------------|-----|--------------|-------|----------|----------|------|

| FIELD | Reserved | T1I                         | TOI | <b>U0RXI</b> | U0TXI | Reserved | Reserved | ADCI |

| RESET | 0        | 0                           | 0   | 0            | 0     | 0        | 0        | 0    |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W |     |              |       |          |          |      |

| ADDR  |          | FC0H                        |     |              |       |          |          |      |

Table 33. Interrupt Request 0 Register (IRQ0)

Reserved—Must be 0.

T1I—Timer 1 Interrupt Request

- 0 = No interrupt request is pending for Timer 1.

- 1 = An interrupt request from Timer 1 is awaiting service.

T0I—Timer 0 Interrupt Request

- 0 = No interrupt request is pending for Timer 0.

- 1 = An interrupt request from Timer 0 is awaiting service.

## Timers

These Z8 Encore! XP<sup>®</sup> F082A Series products contain two 16-bit reloadable timers that can be used for timing, event counting, or generation of pulse-width modulated (PWM) signals. The timers' feature include:

- 16-bit reload counter.

- Programmable prescaler with prescale values from 1 to 128.

- PWM output generation.

- Capture and compare capability.

- External input pin for timer input, clock gating, or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency.

- Timer output pin.

- Timer interrupt.

In addition to the timers described in this chapter, the Baud Rate Generator of the UART (if unused) may also provide basic timing functionality. For information on using the Baud Rate Generator as an additional timer, see Universal Asynchronous Receiver/Transmitter on page 97.

## Architecture

Figure 9 on page 70 displays the architecture of the timers.

# zilog<sup>®</sup> |<sub>11</sub>

The UART data rate is calculated using the following equation:

UART Baud Rate (bits/s) =

$$\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$$

For a given UART data rate, calculate the integer baud rate divisor value using the following equation:

UART Baud Rate Divisor Value (BRG) = Round

$$\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$$

The baud rate error relative to the acceptable baud rate is calculated using the following equation:

UART Baud Rate Error (%) =

$$100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$$

For reliable communication, the UART baud rate error must never exceed 5 percent. Table 70 provides information on the data rate errors for popular baud rates and commonly used crystal oscillator frequencies.

| 10.0 MHz Sy              | stem Clock               |                      |              | 5.5296 MHz \$            | System Clock             |                      |              |

|--------------------------|--------------------------|----------------------|--------------|--------------------------|--------------------------|----------------------|--------------|

| Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) | Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) |

| 1250.0                   | N/A                      | N/A                  | N/A          | 1250.0                   | N/A                      | N/A                  | N/A          |

| 625.0                    | 1                        | 625.0                | 0.00         | 625.0                    | N/A                      | N/A                  | N/A          |

| 250.0                    | 3                        | 208.33               | -16.67       | 250.0                    | 1                        | 345.6                | 38.24        |

| 115.2                    | 5                        | 125.0                | 8.51         | 115.2                    | 3                        | 115.2                | 0.00         |

| 57.6                     | 11                       | 56.8                 | -1.36        | 57.6                     | 6                        | 57.6                 | 0.00         |

| 38.4                     | 16                       | 39.1                 | 1.73         | 38.4                     | 9                        | 38.4                 | 0.00         |

| 19.2                     | 33                       | 18.9                 | 0.16         | 19.2                     | 18                       | 19.2                 | 0.00         |

| 9.60                     | 65                       | 9.62                 | 0.16         | 9.60                     | 36                       | 9.60                 | 0.00         |

| 4.80                     | 130                      | 4.81                 | 0.16         | 4.80                     | 72                       | 4.80                 | 0.00         |

| 2.40                     | 260                      | 2.40                 | -0.03        | 2.40                     | 144                      | 2.40                 | 0.00         |

| 1.20                     | 521                      | 1.20                 | -0.03        | 1.20                     | 288                      | 1.20                 | 0.00         |

| 0.60                     | 1042                     | 0.60                 | -0.03        | 0.60                     | 576                      | 0.60                 | 0.00         |

| 0.30                     | 2083                     | 0.30                 | 0.2          | 0.30                     | 1152                     | 0.30                 | 0.00         |

|                          |                          |                      |              | -                        |                          |                      |              |

#### Table 70. UART Baud Rates

## **Analog-to-Digital Converter**

The analog-to-digital converter (ADC) converts an analog input signal to its digital representation. The features of this sigma-delta ADC include:

- 11-bit resolution in DIFFERENTIAL mode.

- 10-bit resolution in SINGLE-ENDED mode.

- Eight single-ended analog input sources are multiplexed with general-purpose I/O ports.

- 9<sup>th</sup> analog input obtained from temperature sensor peripheral.

- 11 pairs of differential inputs also multiplexed with general-purpose I/O ports.

- Low-power operational amplifier (LPO).

- Interrupt on conversion complete.

- Bandgap generated internal voltage reference with two selectable levels.

- Manual in-circuit calibration is possible employing user code (offset calibration).

- Factory calibrated for in-circuit error compensation.

## Architecture

Figure 19 displays the major functional blocks of the ADC. An analog multiplexer network selects the ADC input from the available analog pins, ANA0 through ANA7.

The input stage of the ADC allows both differential gain and buffering. The following input options are available:

- Unbuffered input (SINGLE-ENDED and DIFFERENTIAL modes).

- Buffered input with unity gain (SINGLE-ENDED and DIFFERENTIAL modes).

- LPO output with full pin access to the feedback path.

- If the internal voltage reference must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- Set CEN to 1 to start the conversion.

- 4. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered-down state, the ADC uses 40 additional clock cycles to power up before beginning the 5129 cycle conversion.

- 5. When the conversion is complete, the ADC control logic performs the following operations:

- 13-bit two's-complement result written to {ADCD\_H[7:0], ADCD\_L[7:3]}.

- Sends an interrupt request to the Interrupt Controller denoting conversion complete.

- CEN resets to 0 to indicate the conversion is complete.

- 6. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered-down.

#### **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analog-to-digital conversion on the selected analog input. Each new data value over-writes the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS mode, ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not immediately detected at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Follow the steps below for setting up the ADC and initiating continuous conversion:

- 1. Enable the desired analog input by configuring the general-purpose I/O pins for alternate function. This action disables the digital input and output driver.

- 2. Write the ADC Control/Status Register 1 to configure the ADC.

- Write to BUFMODE[2:0] to select SINGLE-ENDED or DIFFERENTIAL mode, as well as unbuffered or buffered mode.

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in the ADC Control Register 0.

```

Z8 Encore! XP<sup>®</sup> F082A Series

Product Specification

```

136

```

nop ; wait for output to settle

clr irq0 ; clear any spurious interrupts pending

ei

```

## **Comparator Control Register Definitions**

#### **Comparator Control Register**

The Comparator Control Register (CMP0) configures the comparator inputs and sets the value of the internal voltage reference.

| Table 75 | . Comparator | Control | Register | (CMP0) |

|----------|--------------|---------|----------|--------|

|----------|--------------|---------|----------|--------|

| BITS  | 7      | 6      | 5                                              | 4  | 3  | 2 | 1 | 0 |

|-------|--------|--------|------------------------------------------------|----|----|---|---|---|

| FIELD | INPSEL | INNSEL | REFLVL Reserved (20-/28-pin)<br>REFLVL (8-pin) |    |    |   |   |   |

| RESET | 0      | 0      | 0 1 0 1 0 0                                    |    |    |   | 0 |   |

| R/W   | R/W    | R/W    | R/W R/W R/W R/W R/W                            |    |    |   |   |   |

| ADDR  |        |        |                                                | F9 | 0H |   |   |   |

INPSEL—Signal Select for Positive Input

0 =GPIO pin used as positive comparator input

1 = temperature sensor used as positive comparator input

INNSEL—Signal Select for Negative Input

0 = internal reference disabled, GPIO pin used as negative comparator input

1 = internal reference enabled as negative comparator input

REFLVL—Internal Reference Voltage Level (this reference is independent of the ADC voltage reference). Note that the 8-pin devices contain two additional LSBs for increased resolution.

For 20-/28-pin devices:

$\begin{array}{l} 0000 = 0.0 \ V \\ 0001 = 0.2 \ V \\ 0010 = 0.4 \ V \\ 0011 = 0.6 \ V \\ 0100 = 0.8 \ V \\ 0101 = 1.0 \ V \ (Default) \\ 0110 = 1.2 \ V \\ 0111 = 1.4 \ V \\ 1000 = 1.6 \ V \end{array}$

**z**ilog<sup>®</sup>

## Flash Status Register

The Flash Status (FSTAT) register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status register shares its Register File address with the Write-only Flash Control register.

Table 79. Flash Status Register (FSTAT)

| BITS  | 7             | 6 | 5           | 4  | 3  | 2 | 1 | 0 |

|-------|---------------|---|-------------|----|----|---|---|---|

| FIELD | IELD Reserved |   | FSTAT       |    |    |   |   |   |

| RESET | 0             | 0 | 0 0 0 0 0 0 |    |    |   |   |   |

| R/W   | R             | R | R R R R R R |    |    |   |   |   |

| ADDR  |               |   |             | FF | 8H |   |   |   |

Reserved—Must be 0.

FSTAT—Flash Controller Status

000000 = Flash Controller locked

000001 = First unlock command received (73H written)

000010 = Second unlock command received (8CH written)

000011 = Flash Controller unlocked

000100 = Sector protect register selected

001xxx = Program operation in progress

010xxx = Page erase operation in progress

100xxx = Mass erase operation in progress

## Flash Page Select Register

The Flash Page Select (FPS) register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7 bits given by FPS[6:0] are chosen for program/erase operation.

**z**ilog<sup>°</sup>

#### **Option Bit Types**

#### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. User access to these bits has been provided because these locations contain application-specific device configurations. The information contained here is lost when page 0 of the program memory is erased.

#### **Trim Option Bits**

The trim option bits are contained in the information page of the Flash memory. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered. Program Memory may be erased without endangering these values. It is possible to alter working values of these bits by accessing the Trim Bit Address and Data Registers, but these working values are lost after a power loss or any other reset event.

There are 32 bytes of trim data. To modify one of these values the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data register returns the working value of the target trim data byte.

The trim address range is from information address 20-3F only. The remainder of the information page is not accessible through the trim bit address and data registers.

#### **Calibration Option Bits**

The calibration option bits are also contained in the information page. These bits are factory programmed values intended for use in software correcting the device's analog performance. To read these values, the user code must employ the LDC instruction to access the information area of the address space as defined in See Flash Information Area on page 17.

#### **Serialization Bits**

As an optional feature, Zilog<sup>®</sup> is able to provide factory-programmed serialization. For serialized products, the individual devices are programmed with unique serial numbers. These serial numbers are binary values, four bytes in length. The numbers increase in size with each device, but gaps in the serial sequence may exist.

These serial numbers are stored in the Flash information page (see Reading the Flash Information Page on page 155 and Serialization Data on page 165 for more details) and are unaffected by mass erasure of the device's Flash memory.

Note:

## **Trim Bit Data Register**

The Trim Bid Data (TRMDR) register contains the read or write data for access to the trim option bits (Table 85).

### Table 85. Trim Bit Data Register (TRMDR)

| BITS  | 7                     | 6                           | 5 | 4  | 3  | 2 | 1 | 0 |

|-------|-----------------------|-----------------------------|---|----|----|---|---|---|

| FIELD | TRMDR - Trim Bit Data |                             |   |    |    |   |   |   |

| RESET | 0                     | 0                           | 0 | 0  | 0  | 0 | 0 | 0 |

| R/W   | R/W                   | R/W R/W R/W R/W R/W R/W R/W |   |    |    |   |   |   |

| ADDR  |                       |                             |   | FF | 7H |   |   |   |

## Flash Option Bit Address Space

The first two bytes of Flash program memory at addresses 0000H and 0001H are reserved for the user-programmable Flash option bits.

## Flash Program Memory Address 0000H

Table 86. Flash Option Bits at Program Memory Address 0000H

| BITS      | 7                       | 6                       | 5            | 4  | 3      | 2   | 1        | 0   |

|-----------|-------------------------|-------------------------|--------------|----|--------|-----|----------|-----|

| FIELD     | WDT_RES                 | WDT_AO                  | OSC_SEL[1:0] |    | VBO_AO | FRP | Reserved | FWP |

| RESET     | U                       | U                       | U            | U  | U      | U   | U        | U   |

| R/W       | R/W                     | R/W R/W R/W R/W R/W R/W |              |    |        |     |          | R/W |

| ADDR      | DR Program Memory 0000H |                         |              |    |        |     |          |     |

| Note: U = | Unchanged by            | y Reset. R/W            | = Read/Write | ). |        |     |          |     |

WDT\_RES—Watchdog Timer Reset

0 = Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.

1 = Watchdog Timer time-out causes a system reset. This setting is the default for unprogrammed (erased) Flash.

WDT\_AO—Watchdog Timer Always On

0 = Watchdog Timer is automatically enabled upon application of system power. Watchdog Timer can not be disabled.

## **Non-Volatile Data Storage**

The Z8 Encore! XP<sup>®</sup> F082A Series devices contain a non-volatile data storage (NVDS) element of up to 128 bytes. This memory can perform over 100,000 write cycles.

## Operation

The NVDS is implemented by special purpose Zilog<sup>®</sup> software stored in areas of program memory, which are not user-accessible. These special-purpose routines use the Flash memory to store the data. The routines incorporate a dynamic addressing scheme to maximize the write/erase endurance of the Flash.

Note: Different members of the Z8 Encore! XP F082A Series feature multiple NVDS array sizes. See Z8 Encore! XP<sup>®</sup> F082A Series Family Part Selection Guide on page 3 for details. Also the members containing 8 KB of Flash memory do not include the NVDS feature.

## **NVDS Code Interface**

Two routines are required to access the NVDS: a write routine and a read routine. Both of these routines are accessed with a CALL instruction to a pre-defined address outside of the user-accessible program memory. Both the NVDS address and data are single-byte values. Because these routines disturb the working register set, user code must ensure that any required working register values are preserved by pushing them onto the stack or by changing the working register pointer just prior to NVDS execution.

During both read and write accesses to the NVDS, interrupt service is NOT disabled. Any interrupts that occur during the NVDS execution must take care not to disturb the working register and existing stack contents or else the array may become corrupted. Disabling interrupts before executing NVDS operations is recommended.

Use of the NVDS requires 15 bytes of available stack space. Also, the contents of the working register set are overwritten.

For correct NVDS operation, the Flash Frequency Registers must be programmed based on the system clock frequency (see Flash Operation Timing Using the Flash Frequency Registers on page 145).

#### **Byte Write**

To write a byte to the NVDS array, the user code must first push the address, then the data byte onto the stack. The user code issues a CALL instruction to the address of the byte-write routine (0x10B3). At the return from the sub-routine, the write status byte

- **-** 18

- **Read Register (09H)**—The Read Register command reads data from the Register File. Data can be read 1–256 bytes at a time (256 bytes can be read by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for all the data values.

```

DBG \leftarrow 09H

DBG \leftarrow {4'h0,Register Address[11:8]

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-256 data bytes

```

• Write Program Memory (0AH)—The Write Program Memory command writes data to Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

```

DBG \leftarrow 0AH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

• **Read Program Memory (0BH)**—The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1–65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for the data.

```

DBG \leftarrow 0BH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

• Write Data Memory (0CH)—The Write Data Memory command writes data to Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

```

DBG \leftarrow 0CH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

```

196

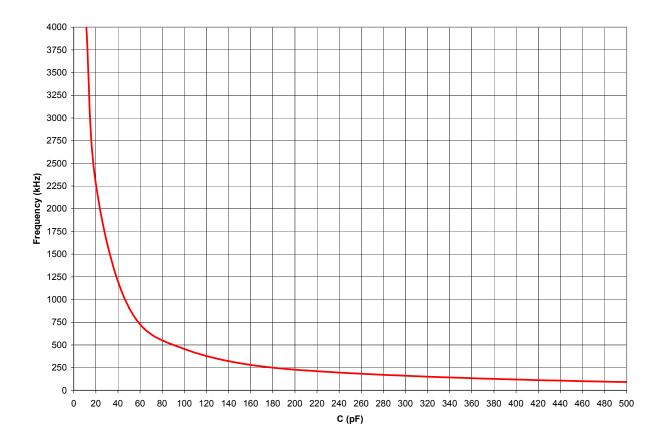

Figure 29 displays the typical (3.3 V and 25 °C) oscillator frequency as a function of the capacitor (C in pF) employed in the RC network assuming a 45 K $\Omega$  external resistor. For very small values of C, the parasitic capacitance of the oscillator XIN pin and the printed circuit board must be included in the estimation of the oscillator frequency.

It is possible to operate the RC oscillator using only the parasitic capacitance of the package and printed circuit board. To minimize sensitivity to external parasitics, external capacitance values in excess of 20 pF are recommended.

## Figure 29. Typical RC Oscillator Frequency as a Function of the External Capacitance with a 45 k $\Omega$ Resistor

**Caution**:

When using the external RC oscillator mode, the oscillator can stop oscillating if the power supply drops below 2.7 V, but before the power supply drops to the Voltage Brownout threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7 V.

207

#### Table 123. Rotate and Shift Instructions (Continued)

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| SRA      | dst      | Shift Right Arithmetic |

| SRL      | dst      | Shift Right Logical    |

| SWAP     | dst      | Swap Nibbles           |

## eZ8 CPU Instruction Summary

Table 124 summarizes the eZ8 CPU instructions. The table identifies the addressing modes employed by the instruction, the effect upon the Flags register, the number of CPU clock cycles required for the instruction fetch, and the number of CPU clock cycles required for the instruction.

| Assembly<br>Mnemonic | Symbolic<br>Operation                                      | Addres        | Address Mode |                    | Flags |          |   |           |   |   | Fetch | Instr. |

|----------------------|------------------------------------------------------------|---------------|--------------|--------------------|-------|----------|---|-----------|---|---|-------|--------|

|                      |                                                            | dst           | src          | Opcode(s)<br>(Hex) | С     | Ζ        | S | ۷         | D | Н |       | Cycles |

| ADC dst, src         | $dst \gets dst + src + C$                                  | r             | r            | 12                 | *     | *        | * | *         | 0 | * | 2     | 3      |

|                      |                                                            | r             | lr           | 13                 | -     |          |   |           |   |   | 2     | 4      |

|                      |                                                            | R             | R            | 14                 | -     |          |   |           |   |   | 3     | 3      |

|                      |                                                            | R             | IR           | 15                 | -     |          |   |           |   |   | 3     | 4      |

|                      |                                                            | R             | IM           | 16                 | -     |          |   |           |   |   | 3     | 3      |

|                      |                                                            | IR            | IM           | 17                 | -     |          |   |           |   |   | 3     | 4      |

| ADCX dst, src        | $dst \gets dst + src + C$                                  | ER            | ER           | 18                 | *     | *        | * | *         | 0 | * | 4     | 3      |

|                      |                                                            | ER            | IM           | 19                 | -     |          |   |           |   |   | 4     | 3      |

| ADD dst, src         | $dst \gets dst + src$                                      | r             | r            | 02                 | *     | *        | * | *         | 0 | * | 2     | 3      |

|                      |                                                            | r             | lr           | 03                 | _     |          |   |           |   |   | 2     | 4      |

|                      |                                                            | R             | R            | 04                 | -     |          |   |           |   |   | 3     | 3      |

|                      |                                                            | R             | IR           | 05                 | -     |          |   |           |   |   | 3     | 4      |

|                      |                                                            | R             | IM           | 06                 | _     |          |   |           |   |   | 3     | 3      |

|                      |                                                            | IR            | IM           | 07                 | _     |          |   |           |   |   | 3     | 4      |

| ADDX dst, src        | $dst \gets dst + src$                                      | ER            | ER           | 08                 | *     | *        | * | *         | 0 | * | 4     | 3      |

|                      |                                                            | ER            | IM           | 09                 | -     |          |   |           |   |   | 4     | 3      |

| Flags Notation:      | * = Value is a function<br>– = Unaffected<br>X = Undefined | of the result | of the o     | peration.          |       | Re<br>Se |   | to (<br>1 | ) |   |       |        |

Table 124. eZ8 CPU Instruction Summary

<mark>z</mark>ilog<sup>°</sup>

## **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs.

#### Table 129. AC Characteristics

|                     | Parameter                    | T <sub>A</sub> = -40 °C<br>(unless o | V to 3.6 V<br>to +105 °C<br>otherwise<br>ted) |       |                                                                                                         |  |

|---------------------|------------------------------|--------------------------------------|-----------------------------------------------|-------|---------------------------------------------------------------------------------------------------------|--|

| Symbol              |                              | Minimum                              | Maximum                                       | Units | Conditions                                                                                              |  |

| F <sub>SYSCLK</sub> | System Clock Frequency       | _                                    | 20.0                                          | MHz   | Read-only from Flash memory                                                                             |  |

|                     |                              | 0.032768                             | 20.0                                          | MHz   | Program or erasure of the<br>Flash memory                                                               |  |

| F <sub>XTAL</sub>   | Crystal Oscillator Frequency | -                                    | 20.0                                          | MHz   | System clock frequencies<br>below the crystal oscillator<br>minimum require an external<br>clock driver |  |

| T <sub>XIN</sub>    | System Clock Period          | 50                                   | _                                             | ns    | T <sub>CLK</sub> = 1/F <sub>syscik</sub>                                                                |  |

| T <sub>XINH</sub>   | System Clock High Time       | 20                                   | 30                                            | ns    | T <sub>CLK</sub> = 50 ns                                                                                |  |

| T <sub>XINL</sub>   | System Clock Low Time        | 20                                   | 30                                            | ns    | T <sub>CLK</sub> = 50 ns                                                                                |  |

| T <sub>XINR</sub>   | System Clock Rise Time       | -                                    | 3                                             | ns    | T <sub>CLK</sub> = 50 ns                                                                                |  |

| T <sub>XINF</sub>   | System Clock Fall Time       | -                                    | 3                                             | ns    | T <sub>CLK</sub> = 50 ns                                                                                |  |

zilog <sub>238</sub>

## **UART** Timing

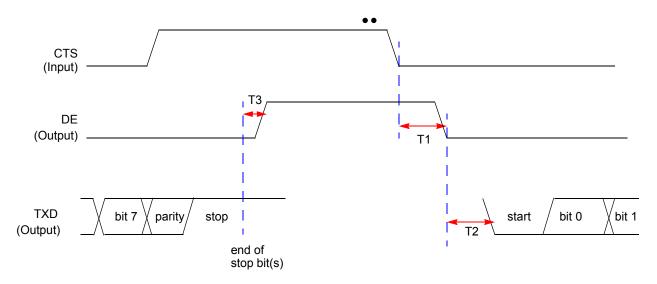

Figure 37 and Table 142 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the transmit data register has been loaded with data prior to CTS assertion.

|                |                                                    | Delay (ns)        |                                |  |  |  |

|----------------|----------------------------------------------------|-------------------|--------------------------------|--|--|--|

| Parameter      | Abbreviation                                       | Minimum           | Maximum                        |  |  |  |

| UART           |                                                    |                   |                                |  |  |  |

| T <sub>1</sub> | CTS Fall to DE output delay                        | 2 * XIN<br>period | 2 * XIN period<br>+ 1 bit time |  |  |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) delay | / ± 5             |                                |  |  |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay         | ± 5               |                                |  |  |  |

#### Table 142. UART Timing With CTS