Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 6                                                            |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64 x 8                                                       |

| RAM Size                   | 512 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 4x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                |

| Supplier Device Package    | ·                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022asb020sc    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **z**ilog<sup>°</sup>

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, and Z8 Encore! XP are registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

ISO 9001:2000 FS 507510 Zilog products are designed and manufactured under an ISO registered 9001:2000 Quality Management System. For more details, please visit www.zilog.com/quality.

#### Low-Power Operational Amplifier

The optional low-power operational amplifier (LPO) is a general-purpose amplifier primarily targeted for current sense applications. The LPO output may be routed internally to the ADC or externally to a pin.

#### **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

#### **Temperature Sensor**

The optional temperature sensor produces an analog output proportional to the device temperature. This signal can be sent to either the ADC or the analog comparator.

#### **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

#### **External Crystal Oscillator**

The crystal oscillator circuit provides highly accurate clock frequencies with the use of an external crystal, ceramic resonator or RC network.

#### Low Voltage Detector

The low voltage detector (LVD) is able to generate an interrupt when the supply voltage drops below a user-programmable level. The LVD is available on 8-pin devices only.

#### **On-Chip Debugger**

The Z8 Encore! XP<sup>®</sup> F082A Series products feature an integrated on-chip debugger (OCD) accessed via a single-pin interface. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints, and executing code.

#### Table 2. Signal Descriptions (Continued)

| Signal Mnemonic     | I/O     | Description                                                                                                                                                                                                                                                                   |

|---------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog              |         |                                                                                                                                                                                                                                                                               |

| ANA[7:0]            | I       | Analog Port. These signals are used as inputs to the analog-to-digital converter (ADC).                                                                                                                                                                                       |

| VREF                | I/O     | Analog-to-digital converter reference voltage input, or buffered output for internal reference.                                                                                                                                                                               |

| Low-Power Operation | onal An | nplifier (LPO)                                                                                                                                                                                                                                                                |

| AMPINP/AMPINN       | Ι       | LPO inputs. If enabled, these pins drive the positive and negative amplifier inputs respectively.                                                                                                                                                                             |

| AMPOUT              | 0       | LPO output. If enabled, this pin is driven by the on-chip LPO.                                                                                                                                                                                                                |

| Oscillators         |         |                                                                                                                                                                                                                                                                               |

| XIN                 | I       | External Crystal Input. This is the input pin to the crystal oscillator. A crystal can be connected between it and the <b>XOUT</b> pin to form the oscillator. In addition, this pin is used with external RC networks or external clock drivers to provide the system clock. |

| XOUT                | 0       | External Crystal Output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the <b>XIN</b> pin to form the oscillator.                                                                                                               |

| Clock Input         |         |                                                                                                                                                                                                                                                                               |

| CLKIN               | I       | Clock Input Signal. This pin may be used to input a TTL-level signal to be used as the system clock.                                                                                                                                                                          |

| LED Drivers         |         |                                                                                                                                                                                                                                                                               |

| LED                 | 0       | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                                                                                   |

| On-Chip Debugger    |         |                                                                                                                                                                                                                                                                               |

| DBG                 | I/O     | Debug. This signal is the control and data input and output to and from the On-Chip Debugger.                                                                                                                                                                                 |

|                     |         | <b>Caution:</b> The DBG pin is open-drain and requires a pull-up resistor to ensure proper operation.                                                                                                                                                                         |

| Reset               |         |                                                                                                                                                                                                                                                                               |

| RESET               | I/O     | RESET. Generates a Reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin low when in reset. This pin is open-drain and features an enabled internal pull-up resistor.                                                         |

12

#### Table 2. Signal Descriptions (Continued)

| Signal Mnemonic  | I/O      | Description                                                                       |

|------------------|----------|-----------------------------------------------------------------------------------|

| Power Supply     |          |                                                                                   |

| V <sub>DD</sub>  | Ι        | Digital Power Supply.                                                             |

| AV <sub>DD</sub> | Ι        | Analog Power Supply.                                                              |

| V <sub>SS</sub>  | I        | Digital Ground.                                                                   |

| AV <sub>SS</sub> | Ι        | Analog Ground.                                                                    |

| Note: The AV     | Vee siar | nals are available only in 28-pin packages with ADC. They are replaced by PB6 and |

**Note:** The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

#### **Pin Characteristics**

Table 3 describes the characteristics for each pin available on the Z8 Encore! XP F082A Series 20- and 28-pin devices. Data in Table 3 is sorted alphabetically by the pin symbol mnemonic.

Table 4 on page 14 provides detailed information about the characteristics for each pin available on the Z8 Encore! XP F082A Series 8-pin devices.

Note:

All six I/O pins on the 8-pin packages are 5 V-tolerant (unless the pull-up devices are enabled). The column in Table 3 below describes 5 V-tolerance for the 20- and 28-pin packages only.

#### Table 3. Pin Characteristics (20- and 28-pin Devices)

| Symbol<br>Mnemonic | Direction | Reset<br>Direction | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal Pull-<br>up<br>or Pull-down | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output | 5 V<br>Tolerance                        |

|--------------------|-----------|--------------------|---------------------------------------|--------------------|--------------------------------------|------------------------------|----------------------|-----------------------------------------|

| AVDD               | N/A       | N/A                | N/A                                   | N/A                | N/A                                  | N/A                          | N/A                  | N/A                                     |

| AVSS               | N/A       | N/A                | N/A                                   | N/A                | N/A                                  | N/A                          | N/A                  | NA                                      |

| DBG                | I/O       | I                  | N/A                                   | Yes                | Yes                                  | Yes                          | Yes                  | No                                      |

| PA[7:0]            | I/O       | I                  | N/A                                   | Yes                | Programmable<br>Pull-up              | Yes                          | Yes,<br>Programmable | PA[7:2]<br>unless<br>pullups<br>enabled |

| PB[7:0]            | I/O       | I                  | N/A                                   | Yes                | Programmable<br>Pull-up              | Yes                          | Yes,<br>Programmable | PB[7:6]<br>unless<br>pullups<br>enabled |

### zilog .

# Reset, Stop Mode Recovery, and Low Voltage Detection

The Reset Controller within the Z8 Encore! XP<sup>®</sup> F082A Series controls Reset and Stop Mode Recovery operation and provides indication of low supply voltage conditions. In typical operation, the following events cause a Reset:

- Power-On Reset (POR)

- Voltage Brownout (VBO)

- Watchdog Timer time-out (when configured by the WDT\_RES Flash Option Bit to initiate a reset)

- External RESET pin assertion (when the alternate RESET function is enabled by the GPIO register)

- On-chip debugger initiated Reset (OCDCTL[0] set to 1)

When the device is in STOP mode, a Stop Mode Recovery is initiated by either of the following:

- Watchdog Timer time-out

- GPIO Port input pin transition on an enabled Stop Mode Recovery source

The low voltage detection circuitry on the device (available on the 8-pin product versions only) performs the following functions:

- Generates the VBO reset when the supply voltage drops below a minimum safe level.

- Generates an interrupt when the supply voltage drops below a user-defined level (8-pin devices only).

#### **Reset Types**

The Z8 Encore! XP F082A Series provides several different types of Reset operation. Stop Mode Recovery is considered as a form of Reset. Table 8 lists the types of Reset and their operating characteristics. The System Reset is longer if the external crystal oscillator is enabled by the Flash option bits, allowing additional time for oscillator start-up.

PAFS1[7:0]—Port Alternate Function Set 1 0 = Port Alternate Function selected as defined in Table 14 and Table 15 on page 44. 1 = Port Alternate Function selected as defined in Table 14 and Table 15 on page 44.

#### Port A–D Alternate Function Set 2 Sub-Registers

The Port A–D Alternate Function Set 2 sub-register (Table 26) is accessed through the Port A–D Control register by writing 08H to the Port A–D Address register. The Alternate Function Set 2 sub-registers selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register is defined in Table 15.

• Note: Alternate function selection on port pins must also be enabled as described in Port A–D Alternate Function Sub-Registers on page 47.

| BITS  | 7                                                                  | 6                           | 5           | 4             | 3             | 2             | 1            | 0        |  |

|-------|--------------------------------------------------------------------|-----------------------------|-------------|---------------|---------------|---------------|--------------|----------|--|

| FIELD | PAFS27                                                             | PAFS26                      | PAFS25      | PAFS24        | PAFS23        | PAFS22        | PAFS21       | PAFS20   |  |

| RESET | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device) |                             |             |               |               |               |              |          |  |

| R/W   | R/W                                                                | R/W R/W R/W R/W R/W R/W R/W |             |               |               |               |              |          |  |

| ADDR  | lf 08H i                                                           | n Port A–D /                | Address Reg | gister, acces | sible through | n the Port A- | -D Control F | Register |  |

Table 26. Port A–D Alternate Function Set 2 Sub-Registers (PxAFS2)

PAFS2[7:0]—Port Alternate Function Set 2

0 = Port Alternate Function selected as defined in Table 15.

1 = Port Alternate Function selected as defined in Table 15.

#### Port A–C Input Data Registers

Reading from the Port A–C Input Data registers (Table 27) returns the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those missing on the 8- and 28-pin packages, as well as those missing on the ADC-enabled 28-pin packages.

| Table 27. Port A–C Input Data Registers (PxIN) | Table 27. | Port A–C | Input Data | Registers | (PxIN) |

|------------------------------------------------|-----------|----------|------------|-----------|--------|

|------------------------------------------------|-----------|----------|------------|-----------|--------|

| BITS      | 7                | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|-----------|------------------|------|------|------|------|------|------|------|--|

| FIELD     | PIN7             | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |

| RESET     | Х                | Х    | Х    | Х    | Х    | Х    | Х    | Х    |  |

| R/W       | R                | R    | R    | R    | R    | R    | R    | R    |  |

| ADDR      | FD2H, FD6H, FDAH |      |      |      |      |      |      |      |  |

| X = Undef | X = Undefined.   |      |      |      |      |      |      |      |  |

zilog ,

Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state for one system clock cycle (from Low to High or from High to Low) upon timer Reload. If it is appropriate to have the Timer Output make a state change at a One-Shot time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control Register to the start value before enabling ONE-SHOT mode. After starting the timer, set TPOL to the opposite bit value.

Follow the steps below for configuring a timer for ONE-SHOT mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for ONE-SHOT mode.

- Set the prescale value.

- Set the initial output level (High or Low) if using the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In ONE-SHOT mode, the system clock always provides the timer input. The timer period is given by the following equation:

$\label{eq:one-short} \text{ONE-SHOT Mode Time-Out Period } (s) = \frac{\text{Reload Value} - \text{Start Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

#### **CONTINUOUS Mode**

In CONTINUOUS mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below for configuring a timer for CONTINUOUS mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for CONTINUOUS mode.

Follow the steps below for configuring a timer for COMPARATOR COUNTER mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for COMPARATOR COUNTER mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER mode. After the first timer Reload in COMPARATOR COUNTER mode, counting always begins at the reset value of 0001H. Generally, in COMPARATOR COUNTER mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer.

In COMPARATOR COUNTER mode, the number of comparator output transitions since the timer start is given by the following equation:

Comparator Output Transitions = Current Count Value – Start Value

#### **PWM SINGLE OUTPUT Mode**

In PWM SINGLE OUTPUT mode, the timer outputs a Pulse-Width Modulator (PWM) output signal through a GPIO Port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

zilog<sup>\*</sup>

If the TPOL bit in the Timer Control register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

Follow the steps below for configuring a timer for PWM SINGLE OUTPUT mode and initiating the PWM operation:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for PWM SINGLE OUTPUT mode.

- Set the prescale value.

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM period). The Reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

$PWM Period (s) = \frac{Reload Value \times Prescale}{System Clock Frequency (Hz)}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT mode equation to determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{PWM Value}{Reload Value} \times 100$

1000 = PWM DUAL OUTPUT mode 1001 = CAPTURE RESTART mode 1010 = COMPARATOR COUNTER mode

#### Timer 0–1 High and Low Byte Registers

The Timer 0–1 High and Low Byte (TxH and TxL) registers (Table 50 and Table 51) contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TxL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from TxL read the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

| BITS  | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |  |  |

|-------|-----|-----|-----|-------|------|-----|-----|-----|--|--|

| FIELD |     | TH  |     |       |      |     |     |     |  |  |

| RESET | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 0   |  |  |

| R/W   | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |  |  |

| ADDR  |     |     |     | F00H, | F08H |     |     |     |  |  |

#### Table 50. Timer 0–1 High Byte Register (TxH)

#### Table 51. Timer 0–1 Low Byte Register (TxL)

| BITS  | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |  |

|-------|-----|-----|-----|-------|------|-----|-----|-----|--|

| FIELD |     | TL  |     |       |      |     |     |     |  |

| RESET | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 1   |  |

| R/W   | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |  |

| ADDR  |     |     |     | F01H, | F09H |     |     |     |  |

TH and TL—Timer High and Low Bytes

These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value.

#### **Timer Reload High and Low Byte Registers**

The Timer 0–1 Reload High and Low Byte (TxRH and TxRL) registers (Table 52 and Table 53) store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte register are stored in a temporary holding register. When a write to the

zilog 1

- If the internal voltage reference must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- Set CEN to 1 to start the conversion.

- 4. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered-down state, the ADC uses 40 additional clock cycles to power up before beginning the 5129 cycle conversion.

- 5. When the conversion is complete, the ADC control logic performs the following operations:

- 13-bit two's-complement result written to {ADCD\_H[7:0], ADCD\_L[7:3]}.

- Sends an interrupt request to the Interrupt Controller denoting conversion complete.

- CEN resets to 0 to indicate the conversion is complete.

- 6. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered-down.

#### **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analog-to-digital conversion on the selected analog input. Each new data value over-writes the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS mode, ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not immediately detected at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Follow the steps below for setting up the ADC and initiating continuous conversion:

- 1. Enable the desired analog input by configuring the general-purpose I/O pins for alternate function. This action disables the digital input and output driver.

- 2. Write the ADC Control/Status Register 1 to configure the ADC.

- Write to BUFMODE[2:0] to select SINGLE-ENDED or DIFFERENTIAL mode, as well as unbuffered or buffered mode.

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in the ADC Control Register 0.

| İ | l | 0 | g | 133 |

|---|---|---|---|-----|

|   |   |   |   | 133 |

| BITS      | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----------|----------------|---|---|---|---|---|---|---|--|

| FIELD     | ADCDH          |   |   |   |   |   |   |   |  |

| RESET     | Х              | Х | Х | Х | Х | Х | Х | Х |  |

| R/W       | R              | R | R | R | R | R | R | R |  |

| ADDR      | F72H           |   |   |   |   |   |   |   |  |

| X = Undef | X = Undefined. |   |   |   |   |   |   |   |  |

#### Table 73. ADC Data High Byte Register (ADCD\_H)

ADCDH—ADC Data High Byte

This byte contains the upper eight bits of the ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the most recent conversion output is held in this register. These bits are undefined after a Reset.

#### ADC Data Low Byte Register

The ADC Data Low Byte (ADCD\_L) register contains the lower bits of the ADC output as well as an overflow status bit. The output is a 13-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data Low Byte register is read-only. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

Table 74. ADC Data Low Byte Register (ADCD\_L)

| BITS      | 7              | 6 | 5     | 4 | 3          | 2 | 1   | 0 |  |

|-----------|----------------|---|-------|---|------------|---|-----|---|--|

| FIELD     |                |   | ADCDL |   | Reserved ( |   | OVF |   |  |

| RESET     | Х              | Х | Х     | Х | Х          | Х | Х   | Х |  |

| R/W       | R              | R | R     | R | R          | R | R   | R |  |

| ADDR      | F73H           |   |       |   |            |   |     |   |  |

| X = Undef | X = Undefined. |   |       |   |            |   |     |   |  |

ADCDL—ADC Data Low Bits

These bits are the least significant five bits of the 13-bits of the ADC output. These bits are undefined after a Reset.

Reserved—Must be undefined.

OVF—Overflow Status

0= A hardware overflow did not occur in the ADC for the current sample. 1= A hardware overflow did occur in the ADC for the current sample, therefore the current sample is invalid.

zilog

160

Reserved—Must be 1.

LVD TRIM-Low Voltage Detect Trim

This trimming affects the low voltage detection threshold. Each LSB represents a 50 mV change in the threshold level. Alternatively, the low voltage threshold may be computed from the options bit value by the following equation:

LVD\_LVL =  $3.6 \text{ V} - \text{LVD} \text{TRIM} \times 0.05 \text{ V}$

| LVD Threshold (V) |            |                       |  |  |  |  |  |  |  |

|-------------------|------------|-----------------------|--|--|--|--|--|--|--|

| LVD_TRIM          | Typical    | Description           |  |  |  |  |  |  |  |

| 00000             | 3.60       | Maximum LVD threshold |  |  |  |  |  |  |  |

| 00001             | 3.55       |                       |  |  |  |  |  |  |  |

| 00010             | 3.50       |                       |  |  |  |  |  |  |  |

| 00011             | 3.45       |                       |  |  |  |  |  |  |  |

| 00100             | 3.40       |                       |  |  |  |  |  |  |  |

| 00101             | 3.35       |                       |  |  |  |  |  |  |  |

| 00110             | 3.30       |                       |  |  |  |  |  |  |  |

| 00111             | 3.25       |                       |  |  |  |  |  |  |  |

| 01000             | 3.20       |                       |  |  |  |  |  |  |  |

| 01001             | 3.15       |                       |  |  |  |  |  |  |  |

| 01010             | 3.10       | Default on Reset      |  |  |  |  |  |  |  |

| 01011             | 3.05       |                       |  |  |  |  |  |  |  |

| 01100             | 3.00       |                       |  |  |  |  |  |  |  |

| 01101             | 2.95       |                       |  |  |  |  |  |  |  |

| 01110             | 2.90       |                       |  |  |  |  |  |  |  |

| 01111             | 2.85       |                       |  |  |  |  |  |  |  |

| 10000             | 2.80       |                       |  |  |  |  |  |  |  |

| 10001             | 2.75       |                       |  |  |  |  |  |  |  |

| 10010             | 2.70       |                       |  |  |  |  |  |  |  |

| 10011             | 2.70       |                       |  |  |  |  |  |  |  |

| to<br>11111       | to<br>1.65 | Minimum LVD threshold |  |  |  |  |  |  |  |

zilog | 177

The Auto-Baud Detector/Generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous datastreams, the maximum recommended baud rate is the system clock frequency divided by 8. The maximum possible baud rate for asynchronous datastreams is the system clock frequency divided by 4, but this theoretical maximum is possible only for low noise designs with clean signals. Table 105 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock<br>Frequency (MHz) | Recommended Maximum<br>Baud Rate (Kbps) | Recommended<br>Standard PC<br>Baud Rate (bps) | Minimum Baud<br>Rate (Kbps) |

|---------------------------------|-----------------------------------------|-----------------------------------------------|-----------------------------|

| 20.0                            | 2500.0                                  | 1,843,200                                     | 39                          |

| 1.0                             | 125.0                                   | 115,200                                       | 1.95                        |

| 0.032768 (32 kHz)               | 4.096                                   | 2,400                                         | 0.064                       |

#### Table 105. OCD Baud-Rate Limits

If the OCD receives a Serial Break (nine or more continuous bits Low) the Auto-Baud Detector/Generator resets. Reconfigure the Auto-Baud Detector/Generator by sending 80H.

#### **OCD Serial Errors**

The On-Chip Debugger can detect any of the following error conditions on the DBG pin:

- Serial Break (a minimum of nine continuous bits Low)

- Framing Error (received Stop bit is Low)

- Transmit Collision (OCD and host simultaneous transmission detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long Serial Break back to the host, and resets the Auto-Baud Detector/Generator. A Framing Error or Transmit Collision may be caused by the host sending a Serial Break to the OCD. Because of the open-drain nature of the interface, returning a Serial Break break back to the host only extends the length of the Serial Break if the host releases the Serial Break early.

The host transmits a Serial Break on the DBG pin when first connecting to the Z8 Encore! XP F082A Series devices or when recovering from an error. A Serial Break from the host resets the Auto-Baud Generator/Detector but does not reset the OCD Control register. A Serial Break leaves the device in DEBUG mode if that is the current mode. The OCD is held in Reset until the end of the Serial Break when the DBG pin returns

### zilog

### **Crystal Oscillator**

The products in the Z8 Encore! XP<sup>®</sup> F082A Series contain an on-chip crystal oscillator for use with external crystals with 32 kHz to 20 MHz frequencies. In addition, the oscillator supports external RC networks with oscillation frequencies up to 4 MHz or ceramic resonators with frequencies up to 8 MHz. The on-chip crystal oscillator can be used to generate the primary system clock for the internal eZ8 CPU and the majority of the on-chip peripherals. Alternatively, the X<sub>IN</sub> input pin can also accept a CMOS-level clock input signal (32 kHz–20 MHz). If an external clock generator is used, the X<sub>OUT</sub> pin must be left unconnected. The Z8 Encore! XP F082A Series products do not contain an internal clock divider. The frequency of the signal on the X<sub>IN</sub> input pin determines the frequency of the system clock.

Note:

Although the XIN pin can be used as an input for an external clock generator, the CLKIN pin is better suited for such use (see System Clock Selection on page 187).

#### **Operating Modes**

The Z8 Encore! XP F082A Series products support four oscillator modes:

- Minimum power for use with very low frequency crystals (32 kHz–1 MHz).

- Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 8 MHz).

- Maximum power for use with high frequency crystals (8 MHz to 20 MHz).

- On-chip oscillator configured for use with external RC networks (<4 MHz).

The oscillator mode is selected using user-programmable Flash Option Bits. See Flash Option Bits on page 153 for information.

#### **Crystal Oscillator Operation**

The Flash Option bit XTLDIS controls whether the crystal oscillator is enabled during reset. The crystal may later be disabled after reset if a new oscillator has been selected as the system clock. If the crystal is manually enabled after reset through the OSCCTL register, the user code must wait at least 1000 crystal oscillator cycles for the crystal to stabilize. After this, the crystal oscillator may be selected as the system clock.

• Note: The stabilization time varies depending on the crystal or resonator used, as well as on the feedback network. See Table 111 for transconductance values to compute oscillator stabilization times.

PS022825-0908

zilog <sub>201</sub>

#### Table 114. Notational Shorthand

| Notation | Description                    | Operand | Rangeb represents a value from 0 to 7 (000B to 111B)                                                                         |  |  |  |  |  |

|----------|--------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| b        | Bit                            | b       |                                                                                                                              |  |  |  |  |  |

| CC       | Condition Code                 | _       | Refer to Condition Codes section in the <i>eZ8 CPU Core User Manual (UM0128)</i> .                                           |  |  |  |  |  |

| DA       | Direct Address                 | Addrs   | Addrs. represents a number in the range of 0000H to FFFFH                                                                    |  |  |  |  |  |

| ER       | Extended Addressing Register   | Reg     | Reg. represents a number in the range of 000H to FFFH                                                                        |  |  |  |  |  |

| IM       | Immediate Data                 | #Data   | Data is a number between 00H to FFH                                                                                          |  |  |  |  |  |

| lr       | Indirect Working Register      | @Rn     | n = 0–15                                                                                                                     |  |  |  |  |  |

| IR       | Indirect Register              | @Reg    | Reg. represents a number in the range of 00H to FFH                                                                          |  |  |  |  |  |

| Irr      | Indirect Working Register Pair | @RRp    | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                             |  |  |  |  |  |

| IRR      | Indirect Register Pair         | @Reg    | Reg. represents an even number in the range 00H to FEH                                                                       |  |  |  |  |  |

| р        | Polarity                       | р       | Polarity is a single bit binary value of either 0B or 1B.                                                                    |  |  |  |  |  |

| r        | Working Register               | Rn      | n = 0 – 15                                                                                                                   |  |  |  |  |  |

| R        | Register                       | Reg     | Reg. represents a number in the range of 00H to FFH                                                                          |  |  |  |  |  |

| RA       | Relative Address               | Х       | X represents an index in the range of +127 to –<br>128 which is an offset relative to the address of<br>the next instruction |  |  |  |  |  |

| rr       | Working Register Pair          | RRp     | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                             |  |  |  |  |  |

| RR       | Register Pair                  | Reg     | Reg. represents an even number in the range of 00H to FEH                                                                    |  |  |  |  |  |

| Vector   | Vector Address                 | Vector  | Vector represents a number in the range of 00H to FFH                                                                        |  |  |  |  |  |

| X        | Indexed                        | #Index  | The register or register pair to be indexed is<br>offset by the signed Index value (#Index) in a<br>+127 to<br>-128 range.   |  |  |  |  |  |

Table 115 lists additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

zilog

| ) g | 213 |

|-----|-----|

|     |     |

| Assembly        | Symbolic                                                        | Addres    | s Mode   | Opcode(s) |   |          | Fla | ags       | Fetch | Instr. |        |   |

|-----------------|-----------------------------------------------------------------|-----------|----------|-----------|---|----------|-----|-----------|-------|--------|--------|---|

| Mnemonic        | Operation                                                       | dst       | src      | (Hex)     | С | Ζ        | S   | V         | D     | Н      | Cycles |   |

| RR dst          |                                                                 | R         |          | E0        | * | *        | *   | *         | _     | _      | 2      | 2 |

|                 | ► D7 D6 D5 D4 D3 D2 D1 D0 C<br>dst                              | IR        |          | E1        |   |          |     |           |       |        | 2      | 3 |

|                 |                                                                 |           |          |           |   |          |     |           |       |        |        |   |

| RRC dst         |                                                                 | R         |          | C0        | * | *        | *   | *         | -     | -      | 2      | 2 |

|                 | ► <u>D7D6D5D4D3D2D1D0</u> ► C<br>dst                            | IR        |          | C1        |   |          |     |           |       |        | 2      | 3 |

| SBC dst, src    | $dst \gets dst - src - C$                                       | r         | r        | 32        | * | *        | *   | *         | 1     | *      | 2      | 3 |

|                 |                                                                 | r         | lr       | 33        |   |          |     |           |       |        | 2      | 4 |

|                 |                                                                 | R         | R        | 34        |   |          |     |           |       |        | 3      | 3 |

|                 |                                                                 | R         | IR       | 35        | • |          |     |           |       |        | 3      | 4 |

|                 |                                                                 | R         | IM       | 36        | • |          |     |           |       |        | 3      | 3 |

|                 |                                                                 | IR        | IM       | 37        | • |          |     |           |       |        | 3      | 4 |

| SBCX dst, src   | $dst \gets dst - src - C$                                       | ER        | ER       | 38        | * | *        | *   | *         | 1     | *      | 4      | 3 |

|                 |                                                                 | ER        | IM       | 39        | • |          |     |           |       |        | 4      | 3 |

| SCF             | C ← 1                                                           |           |          | DF        | 1 | -        | _   | _         | _     | _      | 1      | 2 |

| SRA dst         |                                                                 | R         |          | D0        | * | *        | *   | 0         | -     | _      | 2      | 2 |

|                 | D7D6D5D4D3D2D1D0 C                                              | IR        |          | D1        |   |          |     |           |       |        | 2      | 3 |

| SRL dst         | 0 - <b>▶</b> D7D6D5D4D3D2D1D0- <b>▶</b> C                       | R         |          | 1F C0     | * | *        | 0   | *         | _     | _      | 3      | 2 |

|                 | dst                                                             | IR        |          | 1F C1     | - |          |     |           |       |        | 3      | 3 |

| SRP src         | $RP \gets src$                                                  |           | IM       | 01        | _ | _        | _   | -         | _     | _      | 2      | 2 |

| STOP            | STOP Mode                                                       |           |          | 6F        | _ | _        | _   | _         | _     | _      | 1      | 2 |

| SUB dst, src    | $dst \gets dst - src$                                           | r         | r        | 22        | * | *        | *   | *         | 1     | *      | 2      | 3 |

|                 |                                                                 | r         | lr       | 23        | • |          |     |           |       |        | 2      | 4 |

|                 |                                                                 | R         | R        | 24        | • |          |     |           |       |        | 3      | 3 |

|                 |                                                                 | R         | IR       | 25        |   |          |     |           |       |        | 3      | 4 |

|                 |                                                                 | R         | IM       | 26        | • |          |     |           |       |        | 3      | 3 |

|                 |                                                                 | IR        | IM       | 27        |   |          |     |           |       |        | 3      | 4 |

| Flags Notation: | * = Value is a function of t<br>– = Unaffected<br>X = Undefined | he result | of the o | peration. |   | Re<br>Se |     | to (<br>1 | )     |        |        |   |

#### Table 124. eZ8 CPU Instruction Summary (Continued)

220

zilog <sub>247</sub>

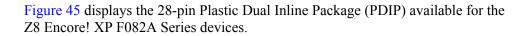

Note: ZILOG supplies both options for production. Component layout PCB design should cover bigger option 01.

#### Figure 45. 28-Pin Plastic Dual Inline Package (PDIP)

## **z**ilog<sup>°</sup>

255

| Part Number                                                                                 | Flash     | RAM      | SOVN | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------------------------------------------------------------------|-----------|----------|------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082A Series with 2 KB Flash, 10-Bit Analog-to-Digital Converter |           |          |      |           |            |                     |                     |                |            | verter             |                     |

| Standard Temperature                                                                        |           |          |      |           |            |                     |                     |                |            |                    |                     |

| Z8F022APB020SC                                                                              |           | 512 B    | 64 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F022AQB020SC                                                                              | 2 KB      | 512 B    | 64 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F022ASB020SC                                                                              | 2 KB      | 512 B    | 64 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F022ASH020SC                                                                              | 2 KB      | 512 B    | 64 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F022AHH020SC                                                                              | 2 KB      | 512 B    | 64 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F022APH020SC                                                                              | 2 KB      | 512 B    | 64 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F022ASJ020SC                                                                              | 2 KB      | 512 B    | 64 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F022AHJ020SC                                                                              | 2 KB      | 512 B    | 64 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F022APJ020SC                                                                              | 2 KB      | 512 B    | 64 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperatur                                                                         | 'e: -40 ° | C to 10  | 5 °C |           |            |                     |                     |                |            |                    |                     |

| Z8F022APB020EC                                                                              | 2 KB      | 512 B    | 64 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F022AQB020EC                                                                              | 2 KB      | 512 B    | 64 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F022ASB020EC                                                                              | 2 KB      | 512 B    | 64 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F022ASH020EC                                                                              | 2 KB      | 512 B    | 64 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F022AHH020EC                                                                              | 2 KB      | 512 B    | 64 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F022APH020EC                                                                              | 2 KB      | 512 B    | 64 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F022ASJ020EC                                                                              | 2 KB      | 512 B    | 64 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F022AHJ020EC                                                                              | 2 KB      | 512 B    | 64 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F022APJ020EC                                                                              | 2 KB      | 512 B    | 64 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Replace C with G for Lead                                                                   | d-Free F  | ackaging |      |           |            |                     |                     |                |            |                    |                     |