# E·XFL

#### Zilog - Z8F022ASH020EC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | IrDA, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT  |

| Number of I/O              | 17                                                            |

| Program Memory Size        | 2KB (2K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | 64 x 8                                                        |

| RAM Size                   | 512 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | A/D 7x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                |

| Supplier Device Package    |                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022ash020ec00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

zilog

vector address. Following Stop Mode Recovery, the STOP bit in the Reset Status (RSTSTAT) Register is set to 1. Table 10 lists the Stop Mode Recovery sources and resulting actions. The text following provides more detailed information about each of the Stop Mode Recovery sources.

| Operating Mode | Stop Mode Recovery Source                                                         | Action                                                               |

|----------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------|

| STOP mode      | Watchdog Timer time-out when configured for Reset                                 | Stop Mode Recovery                                                   |

|                | Watchdog Timer time-out when configured for interrupt                             | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |

|                | Data transition on any GPIO Port<br>pin enabled as a Stop Mode<br>Recovery source | Stop Mode Recovery                                                   |

|                | Assertion of external RESET Pin                                                   | System Reset                                                         |

|                | Debug Pin driven Low                                                              | System Reset                                                         |

#### Table 10. Stop Mode Recovery Sources and Resulting Action

### Stop Mode Recovery Using Watchdog Timer Time-Out

If the Watchdog Timer times out during STOP mode, the device undergoes a Stop Mode Recovery sequence. In the Reset Status (RSTSTAT) register, the WDT and STOP bits are set to 1. If the Watchdog Timer is configured to generate an interrupt upon time-out and the Z8 Encore! XP F082A Series device is configured to respond to interrupts, the eZ8 CPU services the Watchdog Timer interrupt request following the normal Stop Mode Recovery sequence.

### Stop Mode Recovery Using a GPIO Port Pin Transition

Each of the GPIO Port pins may be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a Stop Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery.

**Note:** The SMR pulses shorter than specified does not trigger a recovery (see Table 131 on page 229). When this happens, the STOP bit in the Reset Status (RSTSTAT) register is set to 1.

**Caution:** In STOP mode, the GPIO Port Input Data registers (PxIN) are disabled. The Port Input Data registers record the Port transition only if the signal stays on the Port pin through the end of the Stop Mode Recovery delay. As a result, short pulses on the Port pin can

# **Low-Power Modes**

The Z8 Encore! XP F082A Series products contain power-saving features. The highest level of power reduction is provided by the STOP mode, in which nearly all device functions are powered down. The next lower level of power reduction is provided by the HALT mode, in which the CPU is powered down.

Further power savings can be implemented by disabling individual peripheral blocks while in Active mode (defined as being in neither STOP nor HALT mode).

## **STOP Mode**

Executing the eZ8 CPU's STOP instruction places the device into STOP mode, powering down all peripherals except the Voltage Brownout detector, the Low-power Operational Amplifier and the Watchdog Timer. These three blocks may also be disabled for additional power savings. Specifically, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; XIN and XOUT (if previously enabled) are disabled, and PA0/PA1 revert to the states programmed by the GPIO registers.

- System clock is stopped.

- eZ8 CPU is stopped.

- Program counter (PC) stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control register.

- If enabled, the Watchdog Timer logic continues to operate.

- If enabled for operation in STOP mode by the associated Flash Option Bit, the Voltage Brownout protection circuit continues to operate.

- Low-power operational amplifier continues to operate if enabled by the Power Control register to do so.

- All other on-chip peripherals are idle.

To minimize current in STOP mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP mode using Stop Mode Recovery. For more information on Stop Mode Recovery, see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23.

## **HALT Mode**

Executing the eZ8 CPU's HALT instruction places the device into HALT mode, which powers down the CPU but leaves all other peripherals active. In HALT mode, the operating characteristics are:

- Primary oscillator is enabled and continues to operate.

- System clock is enabled and continues to operate.

- eZ8 CPU is stopped.

- Program counter (PC) stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate.

- If enabled, the Watchdog Timer continues to operate.

- All other on-chip peripherals continue to operate, if enabled.

The eZ8 CPU can be brought out of HALT mode by any of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brownout reset

- External **RESET** pin assertion

To minimize current in HALT mode, all GPIO pins that are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

## **Peripheral-Level Power Control**

In addition to the STOP and HALT modes, it is possible to disable each peripheral on each of the Z8 Encore! XP F082A Series devices. Disabling a given peripheral minimizes its power consumption.

## **Power Control Register Definitions**

The following sections define the Power Control registers.

### **Power Control Register 0**

Each bit of the following registers disables a peripheral block, either by gating its system clock input or by removing power from the block. The default state of the low-power

**z**ilog<sup>°</sup>

PA0 and PA6 contain two different timer functions, a timer input and a complementary timer output. Both of these functions require the same GPIO configuration, the selection between the two is based on the timer mode. See Timers on page 69 for more details.

**Caution:** For pin with multiple alternate functions, it is recommended to write to the AFS1 and AFS2 sub-registers before enabling the alternate function via the AF sub-register. This prevents spurious transitions through unwanted alternate function modes.

## **Direct LED Drive**

The Port C pins provide a current sinked output capable of driving an LED without requiring an external resistor. The output sinks current at programmable levels of 3 mA, 7 mA, 13 mA and 20 mA. This mode is enabled through the Alternate Function sub-register AFS1 and is programmable through the LED control registers. The LED Drive Enable (LEDEN) register turns on the drivers. The LED Drive Level (LEDLVLH and LEDLVLL) registers select the sink current.

For correct function, the LED anode must be connected to  $V_{DD}$  and the cathode to the GPIO pin. Using all Port C pins in LED drive mode with maximum current may result in excessive total current. See Electrical Characteristics on page 221 for the maximum total current for the applicable package.

## **Shared Reset Pin**

On the 20- and 28-pin devices, the PD0 pin shares function with a bi-directional reset pin. Unlike all other I/O pins, this pin does not default to GPIO function on power-up. This pin acts as a bi-directional reset until the software re-configures it. The PD0 pin is output-only when in GPIO mode.

On the 8-pin product versions, the reset pin is shared with PA2, but the pin is not limited to output-only when in GPIO mode.

PS022825-0908

**Caution:** If PA2 on the 8-pin product is reconfigured as an input, ensure that no external stimulus drives the pin low during any reset sequence. Since PA2 returns to its RESET alternate function during system resets, driving it Low holds the chip in a reset state until the pin is released.

## **Shared Debug Pin**

On the 8-pin version of this device only, the Debug pin shares function with the PA0 GPIO pin. This pin performs as a general purpose input pin on power-up, but the debug logic monitors this pin during the reset sequence to determine if the unlock sequence occurs. If the unlock sequence is present, the debug function is unlocked and the pin no longer func-

### Table 31. LED Drive Level Low Register (LEDLVLL)

| BITS  | 7   | 6                       | 5 | 4  | 3  | 2 | 1 | 0 |

|-------|-----|-------------------------|---|----|----|---|---|---|

| FIELD |     | LEDLVLL[7:0]            |   |    |    |   |   |   |

| RESET | 0   | 0                       | 0 | 0  | 0  | 0 | 0 | 0 |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W |   |    |    |   |   |   |

| ADDR  |     |                         |   | F8 | 4H |   |   |   |

LEDLVLL[7:0]—LED Level Low Bit

{LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin.

00 = 3 mA01 = 7 mA10 = 13 mA

11 = 20 mA

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source       |

|----------|-------------------------------------|--------------------------------|

|          | 0034H                               | Port C Pin 1, both input edges |

| Lowest   | 0036H                               | Port C Pin 0, both input edges |

|          | 0038H                               | Reserved                       |

#### Table 32. Trap and Interrupt Vectors in Order of Priority (Continued)

## Architecture

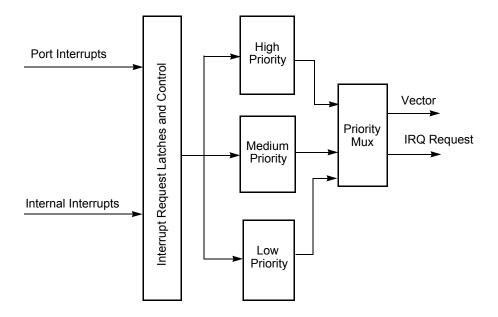

Figure 8 displays the interrupt controller block diagram.

Figure 8. Interrupt Controller Block Diagram

## Operation

### **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control register globally enables and disables interrupts.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED mode. After the first timer reset in GATED mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deassertion and reload events. If appropriate, configure the timer interrupt to be generated only at the input deassertion event or the reload event by setting TICONFIG field of the TxCTL0 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### CAPTURE/COMPARE Mode

In CAPTURE/COMPARE mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte Registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL0 register is set to indicate the timer interrupt is caused by an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 register is cleared to indicate the timer interrupt is not because of an input capture event.

Follow the steps below for configuring a timer for CAPTURE/COMPARE mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for CAPTURE/COMPARE mode.

- Set the prescale value.

- Set the Capture edge (rising or falling) for the Timer Input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

#### 85

#### **PWM SINGLE OUTPUT mode**

0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload.

1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload.

#### **CAPTURE mode**

0 = Count is captured on the rising edge of the Timer Input signal.

1 = Count is captured on the falling edge of the Timer Input signal.

#### **COMPARE mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **GATED** mode

0 = Timer counts when the Timer Input signal is High (1) and interrupts are generated on the falling edge of the Timer Input.

1 = Timer counts when the Timer Input signal is Low (0) and interrupts are generated on the rising edge of the Timer Input.

#### **CAPTURE/COMPARE mode**

0 = Counting is started on the first rising edge of the Timer Input signal. The current count is captured on subsequent rising edges of the Timer Input signal.

1 = Counting is started on the first falling edge of the Timer Input signal. The current count is captured on subsequent falling edges of the Timer Input signal.

#### **PWM DUAL OUTPUT mode**

0 = Timer Output is forced Low (0) and Timer Output Complement is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload. When enabled, the Timer Output Complement is forced Low (0) upon PWM count match and forced High (1) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to High (1).

1 = Timer Output is forced High (1) and Timer Output Complement is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced Low (0) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to Low (0).

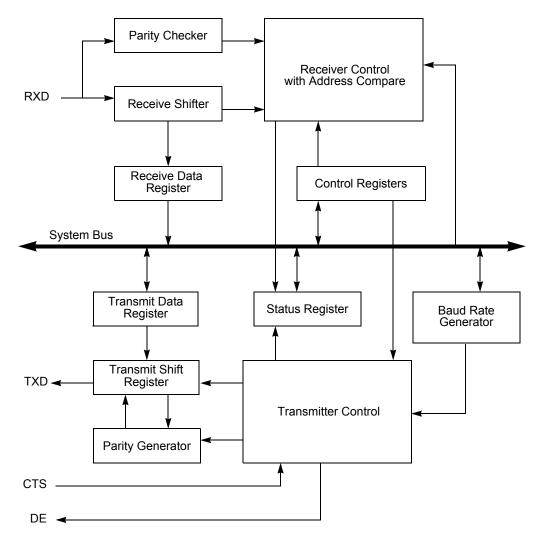

## Operation

#### **Data Format**

The UART always transmits and receives data in an 8-bit data format, least-significant bit first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low START bit and ends with either 1 or 2 active High STOP bits. Figure 11 and Figure 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

0 = No framing error occurred. 1 = A framing error occurred.

BRKD—Break Detect

This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data register clears this bit. 0 = No break occurred.

1 = A break occurred.

TDRE—Transmitter Data Register Empty

This bit indicates that the UART Transmit Data register is empty and ready for additional data. Writing to the UART Transmit Data register resets this bit.

0 = Do not write to the UART Transmit Data register.

1 = The UART Transmit Data register is ready to receive an additional byte to be transmitted.

TXE—Transmitter Empty

This bit indicates that the transmit shift register is empty and character transmission is finished.

0 = Data is currently transmitting.

1 = Transmission is complete.

$CTS - \overline{CTS}$  signal

When this bit is read it returns the level of the  $\overline{\text{CTS}}$  signal. This signal is active Low.

### **UART Status 1 Register**

This register contains multiprocessor control and status bits.

Table 64. UART Status 1 Register (U0STAT1)

| BITS  | 7 | 7 6 5 4 3 2 1 0      |  |    |    |  |  |      |

|-------|---|----------------------|--|----|----|--|--|------|

| FIELD |   | Reserved NEWFRM MPRX |  |    |    |  |  | MPRX |

| RESET | 0 | 0 0 0 0 0 0 0 0      |  |    |    |  |  |      |

| R/W   | R | R R R R R/W R/W R R  |  |    |    |  |  |      |

| ADDR  |   |                      |  | F4 | 4H |  |  |      |

Reserved—Must be 0.

NEWFRM—Status bit denoting the start of a new frame. Reading the UART Receive Data register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame.

1 = The current byte is the first data byte of a new frame.

zilog<sup>°</sup>

#### ANAIN[3:0]—Analog Input Select

These bits select the analog input for conversion. Not all Port pins in this list are available in all packages for the Z8 Encore! XP<sup>®</sup> F082A Series. For information on port pins available with each package style, see Pin Description on page 9. Do not enable unavailable analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.

For the reserved values, all input switches are disabled to avoid leakage or other undesirable operation. ADC samples taken with reserved bit settings are undefined.

SINGLE-ENDED:

- 0000 = ANA0 (transimpedance amp output when enabled)

- 0001 = ANA1 (transimpedance amp inverting input)

- 0010 = ANA2 (transimpedance amp non-inverting input)

- 0011 = ANA3

- 0100 = ANA4

- 0101 = ANA5

- 0110 = ANA6

- 0111 = ANA7

- 1000 = Reserved

- 1001 = Reserved

- 1010 = Reserved

- 1011 = Reserved

- 1100 = Hold transimpedance input nodes (ANA1 and ANA2) to ground.

- 1101 = Reserved

- 1110 = Temperature Sensor.

- 1111 = Reserved.

DIFFERENTIAL (non-inverting input and inverting input respectively):

- 0000 = ANA0 and ANA10001 = ANA2 and ANA30010 = ANA4 and ANA50011 = ANA1 and ANA00100 = ANA3 and ANA20101 = ANA5 and ANA40110 = ANA6 and ANA50111 = ANA0 and ANA50111 = ANA0 and ANA21000 = ANA0 and ANA31001 = ANA0 and ANA41010 = ANA0 and ANA51011 = Reserved1100 = Reserved1101 = Reserved1101 = Reserved1110 = Reserved

- 1111 = Manual Offset Calibration Mode

```

Z8 Encore! XP<sup>®</sup> F082A Series

Product Specification

```

136

```

nop ; wait for output to settle

clr irq0 ; clear any spurious interrupts pending

ei

```

## **Comparator Control Register Definitions**

### **Comparator Control Register**

The Comparator Control Register (CMP0) configures the comparator inputs and sets the value of the internal voltage reference.

| Table 75 | . Comparator | Control | Register | (CMP0) |

|----------|--------------|---------|----------|--------|

|----------|--------------|---------|----------|--------|

| BITS  | 7      | 6      | 5                                              | 4   | 3   | 2   | 1   | 0   |

|-------|--------|--------|------------------------------------------------|-----|-----|-----|-----|-----|

| FIELD | INPSEL | INNSEL | REFLVL Reserved (20-/28-pin)<br>REFLVL (8-pin) |     |     |     |     |     |

| RESET | 0      | 0      | 0                                              | 1   | 0   | 1   | 0   | 0   |

| R/W   | R/W    | R/W    | R/W                                            | R/W | R/W | R/W | R/W | R/W |

| ADDR  |        |        |                                                | F9  | 0H  |     |     |     |

INPSEL—Signal Select for Positive Input

0 =GPIO pin used as positive comparator input

1 = temperature sensor used as positive comparator input

INNSEL—Signal Select for Negative Input

0 = internal reference disabled, GPIO pin used as negative comparator input

1 = internal reference enabled as negative comparator input

REFLVL—Internal Reference Voltage Level (this reference is independent of the ADC voltage reference). Note that the 8-pin devices contain two additional LSBs for increased resolution.

For 20-/28-pin devices:

$\begin{array}{l} 0000 = 0.0 \ V \\ 0001 = 0.2 \ V \\ 0010 = 0.4 \ V \\ 0011 = 0.6 \ V \\ 0100 = 0.8 \ V \\ 0101 = 1.0 \ V \ (Default) \\ 0110 = 1.2 \ V \\ 0111 = 1.4 \ V \\ 1000 = 1.6 \ V \end{array}$

zilog

152

SPROT7-SPROT0—Sector Protection

Each bit corresponds to a 512 byte Flash sector. For the Z8F08xx devices, the upper 3 bits must be zero. For the Z8F04xx devices all bits are used. For the Z8F02xx devices, the upper 4 bits are unused. For the Z8F01xx devices, the upper 6 bits are unused.

## Flash Frequency High and Low Byte Registers

The Flash Frequency High (FFREQH) and Low Byte (FFREQL) registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:

$FFREQ[15:0] = \{FFREQH[7:0], FFREQL[7:0]\} = \frac{System Clock Frequency}{1000}$

**Caution:** The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper operation of the device. Also, Flash programming and erasure is not supported for system clock frequencies below 20 kHz or above 20 MHz.

#### Table 82. Flash Frequency High Byte Register (FFREQH)

| BITS  | 7   | 7 6 5 4 3 2 1 0             |   |    |    |   |   |   |

|-------|-----|-----------------------------|---|----|----|---|---|---|

| FIELD |     | FFREQH                      |   |    |    |   |   |   |

| RESET | 0   | 0                           | 0 | 0  | 0  | 0 | 0 | 0 |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |    |    |   |   |   |

| ADDR  |     |                             |   | FF | AH |   |   |   |

FFREQH—Flash Frequency High Byte

High byte of the 16-bit Flash Frequency value.

#### Table 83. Flash Frequency Low Byte Register (FFREQL)

| BITS  | 7 | 6      | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|--------|---|---|---|---|---|---|

| FIELD |   | FFREQL |   |   |   |   |   |   |

| RESET |   |        |   | ( | 0 |   |   |   |

| R/W   |   | R/W    |   |   |   |   |   |   |

| ADDR  |   | FFBH   |   |   |   |   |   |   |

FFREQL—Flash Frequency Low Byte Low byte of the 16-bit Flash Frequency value.

zilog

165

WDTCALH—Watchdog Timer Calibration High Byte The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload registers result in a one second timeout at room temperature and 3.3 V supply voltage. To use the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDTCALH and WDTL with WDTCALL.

#### Table 98. Watchdog Calibration Low Byte at 007FH (WDTCALL)

| BITS      | 7                             | 6               | 5            | 4   | 3   | 2   | 1   | 0   |

|-----------|-------------------------------|-----------------|--------------|-----|-----|-----|-----|-----|

| FIELD     |                               | WDTCALL         |              |     |     |     |     |     |

| RESET     | U                             | U U U U U U U U |              |     |     |     |     |     |

| R/W       | R/W                           | R/W             | R/W          | R/W | R/W | R/W | R/W | R/W |

| ADDR      | Information Page Memory 007FH |                 |              |     |     |     |     |     |

| Note: U = | Unchanged b                   | y Reset. R/W    | = Read/Write |     |     |     |     |     |

#### WDTCALL—Watchdog Timer Calibration Low Byte

The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload registers result in a one second timeout at room temperature and 3.3 V supply voltage. To use the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDTCALH and WDTL with WDTCALL.

### **Serialization Data**

#### Table 99. Serial Number at 001C - 001F (S\_NUM)

| BITS      | 7                                 | 6            | 5            | 4   | 3   | 2   | 1   | 0   |

|-----------|-----------------------------------|--------------|--------------|-----|-----|-----|-----|-----|

| FIELD     |                                   | S_NUM        |              |     |     |     |     |     |

| RESET     | U                                 | U            | U            | U   | U   | U   | U   | U   |

| R/W       | R/W                               | R/W          | R/W          | R/W | R/W | R/W | R/W | R/W |

| ADDR      | Information Page Memory 001C-001F |              |              |     |     |     |     |     |

| Note: U = | Unchanged by                      | y Reset. R/W | = Read/Write | e.  |     |     |     |     |

S NUM—Serial Number Byte

The serial number is a unique four-byte binary value.

# **On-Chip Debugger**

The Z8 Encore! XP<sup>®</sup> F082A Series devices contain an integrated On-Chip Debugger (OCD) that provides advanced debugging features including:

- Single pin interface.

- Reading and writing of the register file.

- Reading and writing of program and data memory.

- Setting of breakpoints and watchpoints.

- Executing eZ8 CPU instructions.

- Debug pin sharing with general-purpose input-output function to maximize pins available to the user (8-pin product only).

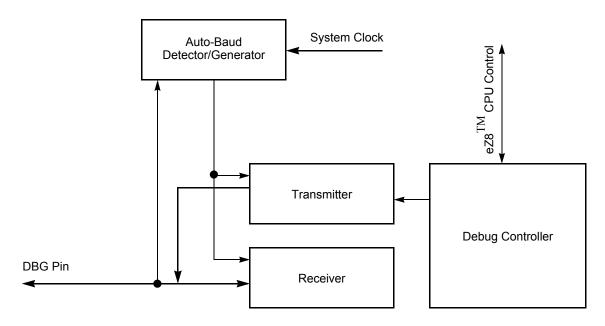

## Architecture

The on-chip debugger consists of four primary functional blocks: transmitter, receiver, auto-baud detector/generator, and debug controller. Figure 23 displays the architecture of the on-chip debugger.

Figure 23. On-Chip Debugger Block Diagram

Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

186

**z**ilog<sup>®</sup>

203

Table 116 through Table 123 lists the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| ADC      | dst, src | Add with Carry                                |

| ADCX     | dst, src | Add with Carry using Extended Addressing      |

| ADD      | dst, src | Add                                           |

| ADDX     | dst, src | Add using Extended Addressing                 |

| СР       | dst, src | Compare                                       |

| CPC      | dst, src | Compare with Carry                            |

| CPCX     | dst, src | Compare with Carry using Extended Addressing  |

| CPX      | dst, src | Compare using Extended Addressing             |

| DA       | dst      | Decimal Adjust                                |

| DEC      | dst      | Decrement                                     |

| DECW     | dst      | Decrement Word                                |

| INC      | dst      | Increment                                     |

| INCW     | dst      | Increment Word                                |

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

#### **Table 116. Arithmetic Instructions**

**z**ilog<sup>°</sup>

## 215

| Assembly<br>Mnemonic | Symbolic<br>Operation                                         | Address Mode |          | Opcode(s) | Flags |              |   |           |   |   | Fetch | Instr. |

|----------------------|---------------------------------------------------------------|--------------|----------|-----------|-------|--------------|---|-----------|---|---|-------|--------|

|                      |                                                               | dst          | src      | (Hex)     | С     | Ζ            | S | ۷         | D | Н |       |        |

| XOR dst, src         | $dst \gets dst \ XOR \ src$                                   | r            | r        | B2        | _     | *            | * | 0         | _ | - | 2     | 3      |

|                      |                                                               | r            | lr       | B3        | -     |              |   |           |   |   | 2     | 4      |

|                      |                                                               | R            | R        | B4        | -     |              |   |           |   |   | 3     | 3      |

|                      |                                                               | R            | IR       | B5        | -     |              |   |           |   |   | 3     | 4      |

|                      |                                                               | R            | IM       | B6        | -     |              |   |           |   |   | 3     | 3      |

|                      |                                                               | IR           | IM       | B7        | -     |              |   |           |   |   | 3     | 4      |

| XORX dst, src        | $dst \gets dst \ XOR \ src$                                   | ER           | ER       | B8        | -     | *            | * | 0         | _ | - | 4     | 3      |

|                      |                                                               | ER           | IM       | B9        | -     |              |   |           |   |   | 4     | 3      |

| Flags Notation:      | * = Value is a function of<br>– = Unaffected<br>X = Undefined | the result   | of the o | peration. | -     | : Re<br>: Se |   | to (<br>1 | C |   |       |        |

### Table 124. eZ8 CPU Instruction Summary (Continued)

|                           | V <sub>DD</sub> = 2.7 V to 3.6 V                                              |              |                      |          |       |                                                                  |  |  |

|---------------------------|-------------------------------------------------------------------------------|--------------|----------------------|----------|-------|------------------------------------------------------------------|--|--|

|                           |                                                                               |              | Maximum <sup>2</sup> |          |       |                                                                  |  |  |

| Symbol                    | Parameter                                                                     | Typical $^1$ | Std Temp             | Ext Temp | Units | Conditions                                                       |  |  |

| I <sub>DD</sub> Stop      | Supply Current in STOP<br>Mode                                                | 0.1          |                      |          | μA    | No peripherals enabled. All pins driven to $V_{DD}$ or $V_{SS}.$ |  |  |

| I <sub>DD</sub> Halt      | Supply Current in HALT<br>Mode (with all<br>peripherals disabled)             | 35           | 55                   | 65       | μA    | 32 kHz                                                           |  |  |

|                           |                                                                               | 520          |                      |          | μA    | 5.5 MHz                                                          |  |  |

|                           |                                                                               | 2.1          | 2.85                 | 2.85     | mA    | 20 MHz                                                           |  |  |

| I <sub>DD</sub>           | Supply Current in<br>ACTIVE Mode (with all<br>peripherals disabled)           | 2.8          |                      |          | mA    | 32 kHz                                                           |  |  |

|                           |                                                                               | 4.5          | 5.2                  | 5.2      | mA    | 5.5 MHz                                                          |  |  |

|                           |                                                                               | 5.5          | 6.5                  | 6.5      | mA    | 10 MHz                                                           |  |  |

|                           |                                                                               | 7.9          | 11.5                 | 11.5     | mA    | 20 MHz                                                           |  |  |

| I <sub>DD</sub> WDT       | Watchdog Timer Supply<br>Current                                              | 0.9          | 1.0                  | 1.1      | μA    |                                                                  |  |  |

| I <sub>DD</sub><br>XTAL   | Crystal Oscillator<br>Supply Current                                          | 40           |                      |          | μA    | 32 kHz                                                           |  |  |

|                           |                                                                               | 230          |                      |          | μA    | 4 MHz                                                            |  |  |

|                           |                                                                               | 760          |                      |          | μA    | 20 MHz                                                           |  |  |

| I <sub>DD</sub> IPO       | Internal Precision<br>Oscillator Supply<br>Current                            | 350          | 500                  | 550      | μA    |                                                                  |  |  |

| I <sub>DD</sub> VBO       | Voltage Brownout and<br>Low-Voltage Detect<br>Supply Current                  | 50           |                      |          | μA    | For 20-/28-pin devices<br>(VBO only); See Notes 4                |  |  |

|                           |                                                                               |              |                      |          |       | For 8-pin devices; See<br>Notes 4                                |  |  |

| I <sub>DD</sub> ADC       | Analog to Digital<br>Converter Supply<br>Current (with External<br>Reference) | 2.8          | 3.1                  | 3.2      | mA    | 32 kHz                                                           |  |  |

|                           |                                                                               | 3.1          | 3.6                  | 3.7      | mA    | 5.5 MHz                                                          |  |  |

|                           |                                                                               | 3.3          | 3.7                  | 3.8      | mA    | 10 MHz                                                           |  |  |

|                           |                                                                               | 3.7          | 4.2                  | 4.3      | mA    | 20 MHz                                                           |  |  |

| I <sub>DD</sub><br>ADCRef | ADC Internal Reference<br>Supply Current                                      | 0            |                      |          | μA    | See Notes 4                                                      |  |  |

| I <sub>DD</sub> CMP       | Comparator supply<br>Current                                                  | 150          | 180                  | 190      | μA    | See Notes 4                                                      |  |  |

## Table 128. Power Consumption

## Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

zilog <sub>238</sub>

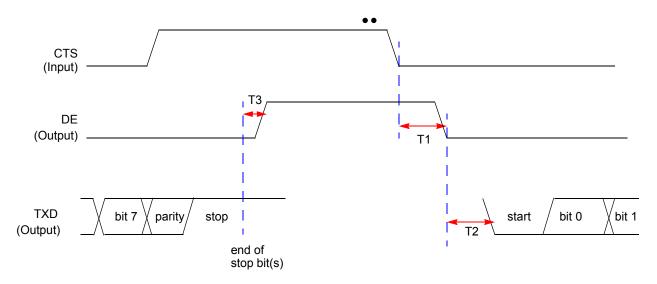

## **UART** Timing

Figure 37 and Table 142 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the transmit data register has been loaded with data prior to CTS assertion.

|                |                                                    | Delay (ns)        |                                |  |  |  |

|----------------|----------------------------------------------------|-------------------|--------------------------------|--|--|--|

| Parameter      | Abbreviation                                       | Minimum           | Maximum                        |  |  |  |

| UART           |                                                    |                   |                                |  |  |  |

| T <sub>1</sub> | CTS Fall to DE output delay                        | 2 * XIN<br>period | 2 * XIN period<br>+ 1 bit time |  |  |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) delay | / ± 5             |                                |  |  |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay         | ± 5               |                                |  |  |  |

#### Table 142. UART Timing With CTS