# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64 × 8                                                       |

| RAM Size                   | 512 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022ash020sc    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Up to thirteen 5 V-tolerant input pins

- Up to 8 ports capable of direct LED drive with no current limit resistor required

- On-Chip Debugger (OCD)

- Voltage Brownout (VBO) protection

- Programmable low battery detection (LVD) (8-pin devices only)

- Bandgap generated precision voltage references available for the ADC, comparator, VBO, and LVD

- Power-On Reset (POR)

- 2.7 V to 3.6 V operating voltage

- 8-, 20-, and 28-pin packages

- 0 °C to +70 °C and -40 °C to +105 °C for operating temperature ranges

# **Part Selection Guide**

Table 1 on page 3 identifies the basic features and package styles available for each device within the Z8 Encore!  $XP^{\ensuremath{\mathbb{R}}}$  F082A Series product line.

## **Interrupt Controller**

The Z8 Encore! XP<sup>®</sup> F082A Series products support up to 20 interrupts. These interrupts consist of 8 internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

### **Reset Controller**

The Z8 Encore! XP F082A Series products can be reset using the  $\overline{\text{RESET}}$  pin, Power-On Reset, Watchdog Timer (WDT) time-out, STOP mode exit, or Voltage Brownout (VBO) warning signal. The  $\overline{\text{RESET}}$  pin is bi-directional, that is, it functions as reset source as well as a reset indicator.

zilog

and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the  $\overline{\text{RESET}}$  input pin is asserted Low, the Z8 Encore! XP<sup>®</sup> F082A Series devices remain in the Reset state. If the  $\overline{\text{RESET}}$  pin is held Low beyond the System Reset time-out, the device exits the Reset state on the system clock rising edge following  $\overline{\text{RESET}}$  pin deassertion. Following a System Reset initiated by the external  $\overline{\text{RESET}}$  pin, the EXT status bit in the Reset Status (RSTSTAT) register is set to 1.

#### **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see Port A–D Control Registers on page 46), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows a Z8 Encore! XP F082A Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the RESET pin Low. The RESET pin is held Low by the internal circuitry until the appropriate delay listed in Table 8 has elapsed.

### **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control register. The On-Chip Debugger block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset the POR bit in the Reset Status (RSTSTAT) register is set.

## Stop Mode Recovery

STOP mode is entered by execution of a STOP instruction by the eZ8 CPU. See Low-Power Modes on page 33 for detailed STOP mode information. During Stop Mode Recovery (SMR), the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay (see Table 131 on page 229)  $T_{SMR}$ , also includes the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control register (WDTCTL) and the Oscillator Control register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset

# **Low-Power Modes**

The Z8 Encore! XP F082A Series products contain power-saving features. The highest level of power reduction is provided by the STOP mode, in which nearly all device functions are powered down. The next lower level of power reduction is provided by the HALT mode, in which the CPU is powered down.

Further power savings can be implemented by disabling individual peripheral blocks while in Active mode (defined as being in neither STOP nor HALT mode).

## **STOP Mode**

Executing the eZ8 CPU's STOP instruction places the device into STOP mode, powering down all peripherals except the Voltage Brownout detector, the Low-power Operational Amplifier and the Watchdog Timer. These three blocks may also be disabled for additional power savings. Specifically, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; XIN and XOUT (if previously enabled) are disabled, and PA0/PA1 revert to the states programmed by the GPIO registers.

- System clock is stopped.

- eZ8 CPU is stopped.

- Program counter (PC) stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control register.

- If enabled, the Watchdog Timer logic continues to operate.

- If enabled for operation in STOP mode by the associated Flash Option Bit, the Voltage Brownout protection circuit continues to operate.

- Low-power operational amplifier continues to operate if enabled by the Power Control register to do so.

- All other on-chip peripherals are idle.

To minimize current in STOP mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP mode using Stop Mode Recovery. For more information on Stop Mode Recovery, see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23.

# Timers

These Z8 Encore! XP<sup>®</sup> F082A Series products contain two 16-bit reloadable timers that can be used for timing, event counting, or generation of pulse-width modulated (PWM) signals. The timers' feature include:

- 16-bit reload counter.

- Programmable prescaler with prescale values from 1 to 128.

- PWM output generation.

- Capture and compare capability.

- External input pin for timer input, clock gating, or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency.

- Timer output pin.

- Timer interrupt.

In addition to the timers described in this chapter, the Baud Rate Generator of the UART (if unused) may also provide basic timing functionality. For information on using the Baud Rate Generator as an additional timer, see Universal Asynchronous Receiver/Transmitter on page 97.

## Architecture

Figure 9 on page 70 displays the architecture of the timers.

- Set the prescale value.

- If using the Timer Output alternate function, set the initial output level (High or Low).

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS mode. After the first timer Reload in CONTINUOUS mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the Timer Output function) for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In CONTINUOUS mode, the system clock always provides the timer input. The timer period is given by the following equation:

CONTINUOUS Mode Time-Out Period (s) =  $\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT mode equation to determine the first time-out period.

#### **COUNTER Mode**

In COUNTER mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO Port pin Timer Input alternate function. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the Timer Input signal. In COUNTER mode, the prescaler is disabled.

**Caution:** The input frequency of the Timer Input signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the input signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

Upon reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

#### MPMD[1:0]—MULTIPROCESSOR Mode

If MULTIPROCESSOR (9-bit) mode is enabled,

00 = The UART generates an interrupt request on all received bytes (data and address).

01 = The UART generates an interrupt request only on received address bytes.

10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs.

11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register.

#### MPEN—MULTIPROCESSOR (9-bit) Enable

This bit is used to enable MULTIPROCESSOR (9-bit) mode.

0 = Disable MULTIPROCESSOR (9-bit) mode.

1 = Enable MULTIPROCESSOR (9-bit) mode.

#### MPBT—Multiprocessor Bit Transmit

This bit is applicable only when MULTIPROCESSOR (9-bit) mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.

0 = Send a 0 in the multiprocessor bit location of the data stream (data byte).

1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).

#### DEPOL—Driver Enable Polarity

0 = DE signal is Active High.

1 = DE signal is Active Low.

#### BRGCTL—Baud Rate Control

This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register.

When the UART receiver is **not** enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value 1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.

When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value. 1 = Reads from the Baud Rate High and Low Byte registers return the current BRG count value. Unlike the Timers, there is no mechanism to latch the Low Byte when the High Byte is read.

RDAIRQ—Receive Data Interrupt Enable

0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.

0 = No framing error occurred. 1 = A framing error occurred.

BRKD—Break Detect

This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data register clears this bit. 0 = No break occurred.

1 = A break occurred.

TDRE—Transmitter Data Register Empty

This bit indicates that the UART Transmit Data register is empty and ready for additional data. Writing to the UART Transmit Data register resets this bit.

0 = Do not write to the UART Transmit Data register.

1 = The UART Transmit Data register is ready to receive an additional byte to be transmitted.

TXE—Transmitter Empty

This bit indicates that the transmit shift register is empty and character transmission is finished.

0 = Data is currently transmitting.

1 = Transmission is complete.

$CTS - \overline{CTS}$  signal

When this bit is read it returns the level of the  $\overline{\text{CTS}}$  signal. This signal is active Low.

### **UART Status 1 Register**

This register contains multiprocessor control and status bits.

Table 64. UART Status 1 Register (U0STAT1)

| BITS  | 7               | 6 | 5 | 4  | 3   | 2   | 1 | 0 |  |  |

|-------|-----------------|---|---|----|-----|-----|---|---|--|--|

| FIELD | Reserved NEWFRM |   |   |    |     |     |   |   |  |  |

| RESET | 0 0 0 0 0 0 0 0 |   |   |    |     |     |   |   |  |  |

| R/W   | R               | R | R | R  | R/W | R/W | R | R |  |  |

| ADDR  |                 |   |   | F4 | 4H  |     |   |   |  |  |

Reserved—Must be 0.

NEWFRM—Status bit denoting the start of a new frame. Reading the UART Receive Data register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame.

1 = The current byte is the first data byte of a new frame.

zilog <sub>123</sub>

can output values across the entire 11-bit range, from -1024 to +1023. In SINGLE-ENDED mode, the output generally ranges from 0 to +1023, but offset errors can cause small negative values.

The ADC registers actually return 13 bits of data, but the two LSBs are intended for compensation use only. When the software compensation routine is performed on the 13 bit raw ADC value, two bits of resolution are lost because of a rounding error. As a result, the final value is an 11-bit number.

#### Hardware Overflow

When the hardware overflow bit (OVF) is set in ADC Data Low Byte (ADCD\_L) register, all other data bits are invalid. The hardware overflow bit is set for values greater than  $V_{ref}$  and less than  $-V_{ref}$  (DIFFERENTIAL mode).

#### **Automatic Powerdown**

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to power up. The ADC powers up when a conversion is requested by the ADC Control register.

### Single-Shot Conversion

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Follow the steps below for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the desired analog inputs by configuring the general-purpose I/O pins for alternate analog function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC.

- Write to BUFMODE [2:0] to select SINGLE-ENDED or DIFFERENTIAL mode, as well as unbuffered or buffered mode.

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is. contained in the ADC Control Register 0.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control register can be written simultaneously (the ADC can be configured and enabled with the same write instruction):

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

129

| #5 MSB #5 LSB |

|---------------|

|---------------|

6. Add the gain correction factor to the original offset corrected value.

|   | #5 MSB | #5 LSB |

|---|--------|--------|

| + |        |        |

|   | #1 MSB | #1 LSB |

| = |        |        |

| #6 MSB #6 LSB |

|---------------|

|---------------|

7. Shift the result to the right, using the sign bit determined in Step 1. This allows for the detection of computational overflow.

| S-> #0 MSB #0 LSB |

|-------------------|

|-------------------|

#### **Output Data**

The following is the output format of the corrected ADC value.

| MSB      | LSB    |

|----------|--------|

| svba9876 | 543210 |

The overflow bit in the corrected output indicates that the computed value was greater than the maximum logical value (+1023) or less than the minimum logical value (-1024). Unlike the hardware overflow bit, this is not a simple binary Flag. For a normal sample (non-overflow), the sign and the overflow bit matches. If the sign bit and overflow bit do not match, a computational overflow has occurred.

### Input Buffer Stage

Many applications require the measurement of an input voltage source with a high output impedance. This ADC provides a buffered input for such situations. The drawback of the buffered input is a limitation of the input range. When using unity gain buffered mode, the input signal must be prevented from coming too close to either  $V_{SS}$  or  $V_{DD}$ . See Table 135 on page 231 for details.

This condition applies only to the input voltage level (with respect to ground) of each differential input signal. The actual differential input voltage magnitude may be less than 300 mV.

The input range of the unbuffered ADC swings from  $V_{SS}$  to  $V_{DD}$ . Input signals smaller than 300 mV must use the unbuffered input mode. If these signals do not contain low output impedances, they might require off-chip buffering.

Signals outside the allowable input range can be used without instability or device damage. Any ADC readings made outside the input range are subject to greater inaccuracy than specified.

## **ADC Control/Status Register 1**

The ADC Control/Status Register 1 (ADCCTL1) configures the input buffer stage, enables the threshold interrupts and contains the status of both threshold triggers. It is also used to select the voltage reference configuration.

### Table 72. ADC Control/Status Register 1 (ADCCTL1)

| BITS  | 7                             | 7 6 5 4 3 2 1 0 |     |     |     |     |     |     |  |  |  |  |

|-------|-------------------------------|-----------------|-----|-----|-----|-----|-----|-----|--|--|--|--|

| FIELD | REFSELH Reserved BUFMODE[2:0] |                 |     |     |     |     |     |     |  |  |  |  |

| RESET | 1                             | 0 0 0 0         |     |     | 0   | 0   |     |     |  |  |  |  |

| R/W   | R/W                           | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| ADDR  |                               |                 |     | F7  | 1H  |     | ·   |     |  |  |  |  |

REFSELH—Voltage Reference Level Select High Bit; in conjunction with the Low bit (REFSELL) in ADC Control Register 0, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL}; this reference is independent of the Comparator reference.

00= Internal Reference Disabled, reference comes from external pin

01= Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

11= Reserved

BUFMODE[2:0] - Input Buffer Mode Select

000 =Single-ended, unbuffered input

- 001 = Single-ended, buffered input with unity gain

- 010 = Reserved

- 011 = Reserved

- 100 = Differential, unbuffered input

- 101 = Differential, buffered input with unity gain

- 110 = Reserved

- 111 = Reserved

# ADC Data High Byte Register

The ADC Data High Byte (ADCD\_H) register contains the upper eight bits of the ADC output. The output is an 13-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

138

zilog <sub>142</sub>

| 8 KB Flash<br>Program Memor | Addresses (hex) | 4 KB Flash<br>Program Memory | /<br>Addresses (hex)<br>1 0FFF | 2 KB Flash<br>Program Memory<br>Address | /<br>es (hex)        |

|-----------------------------|-----------------|------------------------------|--------------------------------|-----------------------------------------|----------------------|

| Sector 7                    | 1FFF<br>1C00    | Sector 7                     | 0E00                           | Sector 3                                | 07FF<br>0600         |

| Sector 6                    | 1BFF            | Sector 6                     | 0DFF                           | Sector 2                                | 05FF<br>0400<br>03FF |

| Castar 5                    | 1800<br>17FF    | Sector 5                     | 0C00<br>0BFF                   | Sector 1                                | 0200<br>01FF         |

| Sector 5                    | 1400<br>13FF    |                              | 0A00<br>09FF                   | Sector 0                                | 0000                 |

| Sector 4                    | 1000            | Sector 4                     | 0800                           |                                         |                      |

| Sector 3                    | 0FFF<br>0C00    | Sector 3                     | 07FF<br>0600                   | 1 KB Flash<br>Program Memory            | y<br>ses (hex)       |

| Sector 2                    | 0BFF<br>0800    | Sector 2                     | 05FF<br>0400                   | Sector 1                                | 03FF                 |

| Sector 1                    | 07FF<br>0400    | Sector 1                     | 03FF<br>0200                   | Sector 0                                | 01FF                 |

| Sector 0                    | 03FF<br>0000    | Sector 0                     | 01FF<br>0000                   |                                         |                      |

Figure 21. Flash Memory Arrangement

## **Flash Information Area**

The Flash information area is separate from Program Memory and is mapped to the address range FE00H to FFFFH. This area is readable but cannot be erased or overwritten. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

zilog<sup>®</sup>

1 = Watchdog Timer is enabled upon execution of the WDT instruction. Once enabled, the Watchdog Timer can only be disabled by a Reset or Stop Mode Recovery. This setting is the default for unprogrammed (erased) Flash.

OSC SEL[1:0]—Oscillator Mode Selection

00 = On-chip oscillator configured for use with external RC networks (<4 MHz).

01 = Minimum power for use with very low frequency crystals (32 kHz to 1.0 MHz).

10 = Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 5.0 MHz).

11 = Maximum power for use with high frequency crystals (5.0 MHz to 20.0 MHz). This setting is the default for unprogrammed (erased) Flash.

VBO AO-Voltage Brownout Protection Always On

0 = Voltage Brownout Protection can be disabled in STOP mode to reduce total power consumption. For the block to be disabled, the power control register bit must also be written (see Power Control Register Definitions on page 34).

1 = Voltage Brownout Protection is always enabled including during STOP mode. This setting is the default for unprogrammed (erased) Flash.

FRP—Flash Read Protect

0 = User program code is inaccessible. Limited control features are available through the On-Chip Debugger.

1 = User program code is accessible. All On-Chip Debugger commands are enabled. This setting is the default for unprogrammed (erased) Flash.

Reserved—Must be 1.

FWP—Flash Write Protect

This Option Bit provides Flash Program Memory protection:

0 = Programming and erasure disabled for all of Flash Program Memory. Programming,

Page Erase, and Mass Erase through User Code is disabled. Mass Erase is available using the On-Chip Debugger.

1 = Programming, Page Erase, and Mass Erase are enabled for all of Flash program memory.

zilog

194

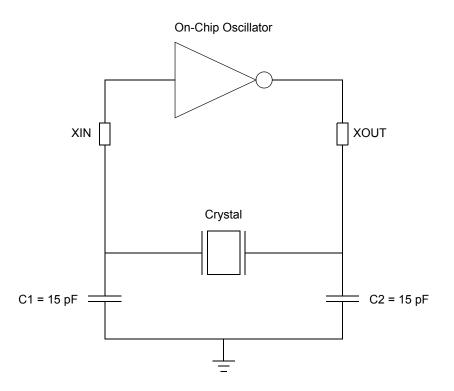

Figure 27 displays a recommended configuration for connection with an external fundamental-mode, parallel-resonant crystal operating at 20 MHz. Recommended 20 MHz crystal specifications are provided in Table 110. Printed circuit board layout must add no more than 4 pF of stray capacitance to either the X<sub>IN</sub> or X<sub>OUT</sub> pins. If oscillation does not occur, reduce the values of capacitors C<sub>1</sub> and C<sub>2</sub> to decrease loading.

#### Figure 27. Recommended 20 MHz Crystal Oscillator Configuration

| Table 110. Recommended Crystal Oscillator Specifications |

|----------------------------------------------------------|

|----------------------------------------------------------|

| Parameter                           | Value       | Units | Comments |

|-------------------------------------|-------------|-------|----------|

| Frequency                           | 20          | MHz   |          |

| Resonance                           | Parallel    |       |          |

| Mode                                | Fundamental |       |          |

| Series Resistance (R <sub>S</sub> ) | 60          | Ω     | Maximum  |

| Load Capacitance (C <sub>L</sub> )  | 30          | pF    | Maximum  |

| Shunt Capacitance (C <sub>0</sub> ) | 7           | pF    | Maximum  |

| Drive Level                         | 1           | mW    | Maximum  |

**z**ilog<sup>°</sup>

|   |             |             |                     |                     |                     |                 | Lo           | ower Ni       | bble (He        | x)             |              |            |             |             |           |           |

|---|-------------|-------------|---------------------|---------------------|---------------------|-----------------|--------------|---------------|-----------------|----------------|--------------|------------|-------------|-------------|-----------|-----------|

|   | 0           | 1           | 2                   | 3                   | 4                   | 5               | 6            | 7             | 8               | 9              | А            | В          | С           | D           | Е         | F         |

| ~ | 1.1         | 2.2         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            | 2.3          | 2.2        | 2.2         | 3.2         | 1.2       | 1.2       |

| 0 | BRK         | SRP<br>IM   | <b>ADD</b><br>r1,r2 | ADD<br>r1,lr2       | <b>ADD</b><br>R2,R1 | ADD<br>IR2,R1   | ADD<br>R1,IM | ADD<br>IR1,IM | ADDX<br>ER2,ER1 | ADDX<br>IM,ER1 | DJNZ<br>r1,X | JR<br>cc,X | LD<br>r1,IM | JP<br>cc,DA | INC<br>r1 | NO        |

|   | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            | ,            |            | ,           | 00,271      | 1         | See       |

| 1 | RLC         | RLC         | ADC                 | ADC                 | ADC                 | ADC             | ADC          | ADC           | ADCX            | ADCX           |              |            |             |             |           | Орсо      |

|   | R1          | IR1         | r1,r2               | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           | Ma        |

| 2 | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1,        |

| 2 | INC<br>R1   | INC<br>IR1  | <b>SUB</b><br>r1,r2 | SUB<br>r1,lr2       | <b>SUB</b><br>R2,R1 | SUB<br>IR2,R1   | SUB<br>R1,IM | SUB<br>IR1,IM | SUBX<br>ER2,ER1 | SUBX<br>IM,ER1 |              |            |             |             |           | AT        |

|   | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           |           |

| 3 | DEC         | DEC         | SBC                 | SBC                 | SBC                 | SBC             | SBC          | SBC           | SBCX            | SBCX           |              |            |             |             |           |           |

|   | R1          | IR1         | r1,r2               | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           |           |

| 4 | DA          | DA          | OR                  | OR                  | OR                  | OR              | OR           | OR            | ORX             | ORX            |              |            |             |             |           |           |

|   | R1          | IR1         | r1,r2               | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| 5 | 2.2<br>POP  | 2.3<br>POP  | 2.3<br>AND          | 2.4<br>AND          | 3.3<br>AND          | 3.4<br>AND      | 3.3<br>AND   | 3.4<br>AND    | 4.3<br>ANDX     | 4.3<br>ANDX    |              |            |             |             |           | 1.<br>WE  |

| Ŭ | R1          | IR1         | r1,r2               | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.        |

| 6 | СОМ         | COM         | тсм                 | тсм                 | тсм                 | тсм             | тсм          | тсм           | тсмх            | тсмх           |              |            |             |             |           | STO       |

|   | R1          | IR1         | r1,r2               | r1,Ir2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| - | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.1       |

| 7 | PUSH<br>R2  | PUSH<br>IR2 | <b>TM</b><br>r1,r2  | <b>TM</b><br>r1,lr2 | <b>TM</b><br>R2,R1  | TM<br>IR2,R1    | TM<br>R1,IM  | TM<br>IR1,IM  | TMX<br>ER2,ER1  | TMX<br>IM,ER1  |              |            |             |             |           | HA        |

|   | 2.5         | 2.6         | 2.5                 | 2.9                 | 3.2                 | 3.3             | 3.4          | 3.5           | 3.4             | 3.4            |              |            |             |             |           | 1.:       |

| 8 | DECW        |             | LDE                 | LDEI                | LDX                 | LDX             | LDX          | LDX           | LDX             | LDX            |              |            |             |             |           | D         |

|   | RR1         | IRR1        | r1,Irr2             | lr1,lrr2            | r1,ER2              | lr1,ER2         | IRR2,R1      | IRR2,IR1      | r1,rr2,X        | rr1,r2,X       |              |            |             |             |           |           |

|   | 2.2         | 2.3         | 2.5                 | 2.9                 | 3.2                 | 3.3             | 3.4          | 3.5           | 3.3             | 3.5            |              |            |             |             |           | 1.2       |

| 9 | RL          | RL          | LDE                 | LDEI                | LDX                 | LDX             | LDX          | LDX           | LEA             | LEA            |              |            |             |             |           | E         |

|   | R1          | IR1         | r2,Irr1             | lr2,lrr1            | r2,ER1              | Ir2,ER1         |              | IR2,IRR1      | r1,r2,X         | rr1,rr2,X      |              |            |             |             |           | <u> </u>  |

| А | 2.5<br>INCW | 2.6<br>INCW | 2.3<br>CP           | 2.4<br>CP           | 3.3<br>CP           | 3.4<br>CP       | 3.3<br>CP    | 3.4<br>CP     | 4.3<br>CPX      | 4.3<br>CPX     |              |            |             |             |           | 1.4<br>RE |

| ~ | RR1         | IRR1        | r1,r2               | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.        |

| В | CLR         | CLR         | XOR                 | XOR                 | XOR                 | XOR             | XOR          | XOR           | XORX            | XORX           |              |            |             |             |           | IRE       |

|   | R1          | IR1         | r1,r2               | r1,Ir2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| ~ | 2.2         | 2.3         | 2.5                 | 2.9                 | 2.3                 | 2.9             |              | 3.4           | 3.2             |                |              |            |             |             |           | 1.1       |

| С | RRC<br>R1   | IR1         | LDC<br>r1,Irr2      | LDCI<br>Ir1,Irr2    | JP<br>IRR1          | LDC<br>Ir1,Irr2 |              | LD<br>r1,r2,X | PUSHX<br>ER2    |                |              |            |             |             |           | RC        |

|   | 2.2         | 2.3         | 2.5                 | 2.9                 | 2.6                 | 2.2             | 3.3          | 3.4           | 3.2             |                |              |            |             |             |           | 1.:       |

| D | SRA         | SRA         | LDC                 | LDCI                | -                   | BSWAP           |              | LD            | POPX            |                |              |            |             |             |           | SC        |

|   | R1          | IR1         | r2,Irr1             | lr2,Irr1            | IRR1                | R1              | DA           | r2,r1,X       | ER1             |                |              |            |             |             |           |           |

|   | 2.2         | 2.3         | 2.2                 | 2.3                 | 3.2                 | 3.3             | 3.2          | 3.3           | 4.2             | 4.2            |              |            |             |             |           | 1.:       |

| E | RR          | RR          | BIT                 | LD                  | LD                  | LD              | LD           | LD            | LDX             | LDX            |              |            |             |             |           | cc        |

|   | R1          | IR1         | p,b,r1              | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| F | 2.2<br>SWAP | 2.3<br>SWAP | 2.6<br><b>TRAP</b>  | 2.3<br>LD           | 2.8<br>MULT         | 3.3<br>LD       | 3.3<br>BTJ   | 3.4<br>BTJ    |                 |                |              | 4          |             |             |           |           |

|   | R1          | IR1         | Vector              | Ir1,r2              | RR1                 | R2,IR1          | p,b,r1,X     |               |                 |                | V            | V          |             |             |           |           |

Figure 31. First Opcode Map

Upper Nibble (Hex)

218

<mark>z</mark>ilog<sup>°</sup>

# **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs.

#### Table 129. AC Characteristics

|                     |                              | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C<br>(unless otherwise<br>stated) |         |       |                                                                                                         |

|---------------------|------------------------------|--------------------------------------------------------------------------------------------------------|---------|-------|---------------------------------------------------------------------------------------------------------|

| Symbol              | Parameter                    | Minimum                                                                                                | Maximum | Units | Conditions                                                                                              |

| F <sub>SYSCLK</sub> | System Clock Frequency       | _                                                                                                      | 20.0    | MHz   | Read-only from Flash memory                                                                             |

|                     |                              | 0.032768                                                                                               | 20.0    | MHz   | Program or erasure of the<br>Flash memory                                                               |

| F <sub>XTAL</sub>   | Crystal Oscillator Frequency | -                                                                                                      | 20.0    | MHz   | System clock frequencies<br>below the crystal oscillator<br>minimum require an external<br>clock driver |

| T <sub>XIN</sub>    | System Clock Period          | 50                                                                                                     | _       | ns    | T <sub>CLK</sub> = 1/F <sub>sysclk</sub>                                                                |

| T <sub>XINH</sub>   | System Clock High Time       | 20                                                                                                     | 30      | ns    | T <sub>CLK</sub> = 50 ns                                                                                |

| T <sub>XINL</sub>   | System Clock Low Time        | 20                                                                                                     | 30      | ns    | T <sub>CLK</sub> = 50 ns                                                                                |

| T <sub>XINR</sub>   | System Clock Rise Time       | -                                                                                                      | 3       | ns    | T <sub>CLK</sub> = 50 ns                                                                                |

| T <sub>XINF</sub>   | System Clock Fall Time       | -                                                                                                      | 3       | ns    | T <sub>CLK</sub> = 50 ns                                                                                |

Zilog <sub>243</sub>

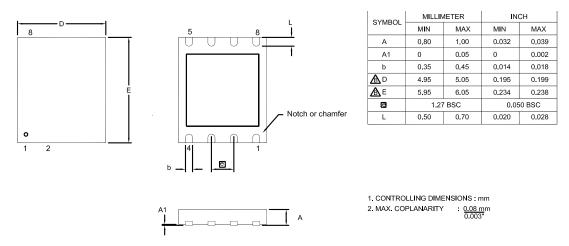

Figure 41 displays the 8-pin Quad Flat No-Lead package (QFN)/MLF-S available for the Z8 Encore! XP F082A Series devices. This package has a footprint identical to that of the 8-pin SOIC, but with a lower profile.

Figure 41. 8-Pin Quad Flat No-Lead Package (QFN)/MLF-S

262

compare 85 compare - extended addressing 203 COMPARE mode 85 compare with carry 203 compare with carry - extended addressing 203 complement 205 complement carry flag 204 condition code 201 continuous conversion (ADC) 124 CONTINUOUS mode 84 control register definition, UART 108 Control Registers 15, 19 **COUNTER modes 84** CP 203 **CPC 203 CPCX 203** CPU and peripheral overview 5 CPU control instructions 204 **CPX 203** Customer Feedback Form 271

# D

DA 201, 203 data memory 17 DC characteristics 222 debugger, on-chip 173 **DEC 203** decimal adjust 203 decrement 203 decrement and jump non-zero 206 decrement word 203 **DECW 203** destination operand 202 device, port availability 37 DI 204 direct address 201 disable interrupts 204 **DJNZ 206** dst 202

## Ε

EI 204

electrical characteristics 221 ADC 231 flash memory and timing 230 GPIO input data sample timing 234 Watchdog Timer 230, 233 enable interrupt 204 ER 201 extended addressing register 201 external pin reset 27 eZ8 CPU features 5 eZ8 CPU instruction classes 202 eZ8 CPU instruction notation 200 eZ8 CPU instruction set 199 eZ8 CPU instruction summary 207

# F

FCTL register 149, 155, 156 features, Z8 Encore! 1 first opcode map 218 FLAGS 202 flags register 202 flash controller 7 option bit address space 156 option bit configuration - reset 153 program memory address 0000H 156 program memory address 0001H 158 flash memory 141 arrangement 142 byte programming 147 code protection 145 configurations 141 control register definitions 149, 155 controller bypass 148 electrical characteristics and timing 230 flash control register 149, 155, 156 flash option bits 146 flash status register 150 flow chart 144 frequency high and low byte registers 152 mass erase 147 operation 143 operation timing 145