# E·XFL

#### Zilog - Z8F022ASJ020SC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | IrDA, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT  |

| Number of I/O              | 23                                                            |

| Program Memory Size        | 2KB (2K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | 64 x 8                                                        |

| RAM Size                   | 512 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | A/D 8x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                |

| Supplier Device Package    | · ·                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022asj020sc00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# zilog <sub>3</sub>

| Part<br>Number | Flash<br>(KB) | RAM<br>(B) | NVDS <sup>1</sup><br>(B) | I/O  | Comparator | Advanced<br>Analog <sup>2</sup> | ADC<br>Inputs | Packages           |

|----------------|---------------|------------|--------------------------|------|------------|---------------------------------|---------------|--------------------|

| Z8F082A        | 8             | 1024       | 0                        | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F081A        | 8             | 1024       | 0                        | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F042A        | 4             | 1024       | 128                      | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F041A        | 4             | 1024       | 128                      | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F022A        | 2             | 512        | 64                       | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F021A        | 2             | 512        | 64                       | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F012A        | 1             | 256        | 16                       | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F011A        | 1             | 256        | 16                       | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pir |

Table 1. Z8 Encore! XP<sup>®</sup> F082A Series Family Part Selection Guide

<sup>1</sup>Non-volatile data storage.

<sup>2</sup>Advanced Analog includes ADC, temperature sensor, and low-power operational amplifier.

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source       |

|----------|-------------------------------------|--------------------------------|

|          | 0034H                               | Port C Pin 1, both input edges |

| Lowest   | 0036H                               | Port C Pin 0, both input edges |

|          | 0038H                               | Reserved                       |

#### Table 32. Trap and Interrupt Vectors in Order of Priority (Continued)

## Architecture

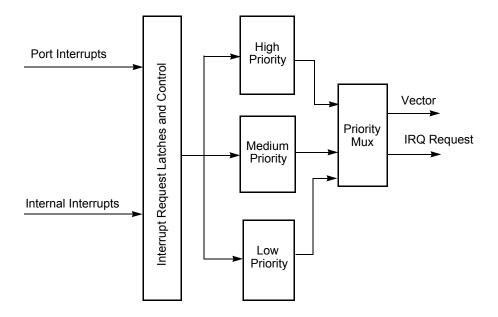

Figure 8 displays the interrupt controller block diagram.

Figure 8. Interrupt Controller Block Diagram

## Operation

#### **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control register globally enables and disables interrupts.

**Caution:** The following coding style that clears bits in the Interrupt Request registers is not recommended. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost.

Poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

Caution: To avoid missing interrupts, use the following coding style to clear bits in the Interrupt Request 0 register:

Good coding style that avoids lost interrupt requests:

ANDX IRQ0, MASK

#### Software Interrupt Assertion

Program code can generate interrupts directly. Writing a 1 to the correct bit in the Interrupt Request register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request register is automatically cleared to 0.

**Caution:** The following coding style used to generate software interrupts by setting bits in the Interrupt Request registers is not recommended. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost.

Poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 OR r0, MASK LDX IRQ0, r0

**Caution:** To avoid missing interrupts, use the following coding style to set bits in the Interrupt Request registers:

> Good coding style that avoids lost interrupt requests: ORX IRQO, MASK

#### Watchdog Timer Interrupt Assertion

The Watchdog Timer interrupt behavior is different from interrupts generated by other sources. The Watchdog Timer continues to assert an interrupt as long as the timeout condition continues. As it operates on a different (and usually slower) clock domain than the rest of the device, the Watchdog Timer continues to assert this interrupt for many system clocks until the counter rolls over.

zilog<sup>\*</sup>

If the TPOL bit in the Timer Control register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

Follow the steps below for configuring a timer for PWM SINGLE OUTPUT mode and initiating the PWM operation:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for PWM SINGLE OUTPUT mode.

- Set the prescale value.

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM period). The Reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

$PWM Period (s) = \frac{Reload Value \times Prescale}{System Clock Frequency (Hz)}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT mode equation to determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{PWM Value}{Reload Value} \times 100$

#### Watchdog Timer Refresh

When first enabled, the Watchdog Timer is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT Reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When the Z8 Encore! XP<sup>®</sup> F082A Series devices are operating in DEBUG mode (using the on-chip debugger), the Watchdog Timer is continuously refreshed to prevent any Watchdog Timer time-outs.

#### Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash Option Bit determines the time-out response of the Watchdog Timer. For information on programming the WDT\_RES Flash Option Bit, see Flash Option Bits on page 153.

#### WDT Interrupt in Normal Operation

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Reset Status (RSTSTAT) register (see Reset Status Register on page 30). If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its Reload Value.

The Reset Status (RSTSTAT) register must be read before clearing the WDT interrupt. This read clears the WDT timeout Flag and prevents further WDT interrupts from immediately occurring.

#### WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and the Z8 Encore! XP F082A Series devices are in STOP mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Reset Status (RSTSTAT) register are set to 1 following a WDT time-out in STOP mode. For more information on Stop Mode Recovery, see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address.

92

# zilog

## Universal Asynchronous Receiver/Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. Features of the UART include:

- 8-bit asynchronous data transfer.

- Selectable even- and odd-parity generation and checking.

- Option of one or two STOP bits.

- Separate transmit and receive interrupts.

- Framing, parity, overrun and break detection.

- Separate transmit and receive enables.

- 16-bit baud rate generator (BRG).

- Selectable MULTIPROCESSOR (9-bit) mode with three configurable interrupt schemes.

- Baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

- Driver enable (DE) output for external bus transceivers.

#### Architecture

The UART consists of three primary functional blocks: transmitter, receiver, and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 on page 98 displays the UART architecture.

0 = No framing error occurred. 1 = A framing error occurred.

BRKD—Break Detect

This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data register clears this bit. 0 = No break occurred.

1 = A break occurred.

TDRE—Transmitter Data Register Empty

This bit indicates that the UART Transmit Data register is empty and ready for additional data. Writing to the UART Transmit Data register resets this bit.

0 = Do not write to the UART Transmit Data register.

1 = The UART Transmit Data register is ready to receive an additional byte to be transmitted.

TXE—Transmitter Empty

This bit indicates that the transmit shift register is empty and character transmission is finished.

0 = Data is currently transmitting.

1 = Transmission is complete.

$CTS - \overline{CTS}$  signal

When this bit is read it returns the level of the  $\overline{\text{CTS}}$  signal. This signal is active Low.

#### **UART Status 1 Register**

This register contains multiprocessor control and status bits.

Table 64. UART Status 1 Register (U0STAT1)

| BITS  | 7 | 6    | 5    | 4    | 3   | 2   | 1      | 0    |  |  |

|-------|---|------|------|------|-----|-----|--------|------|--|--|

| FIELD |   |      | Rese | rved |     |     | NEWFRM | MPRX |  |  |

| RESET | 0 | 0    | 0    | 0    | 0   | 0   | 0      | 0    |  |  |

| R/W   | R | R    | R    | R    | R/W | R/W | R      | R    |  |  |

| ADDR  |   | F44H |      |      |     |     |        |      |  |  |

Reserved—Must be 0.

NEWFRM—Status bit denoting the start of a new frame. Reading the UART Receive Data register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame.

1 = The current byte is the first data byte of a new frame.

zilog <sub>123</sub>

can output values across the entire 11-bit range, from -1024 to +1023. In SINGLE-ENDED mode, the output generally ranges from 0 to +1023, but offset errors can cause small negative values.

The ADC registers actually return 13 bits of data, but the two LSBs are intended for compensation use only. When the software compensation routine is performed on the 13 bit raw ADC value, two bits of resolution are lost because of a rounding error. As a result, the final value is an 11-bit number.

#### Hardware Overflow

When the hardware overflow bit (OVF) is set in ADC Data Low Byte (ADCD\_L) register, all other data bits are invalid. The hardware overflow bit is set for values greater than  $V_{ref}$  and less than  $-V_{ref}$  (DIFFERENTIAL mode).

#### **Automatic Powerdown**

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to power up. The ADC powers up when a conversion is requested by the ADC Control register.

#### Single-Shot Conversion

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Follow the steps below for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the desired analog inputs by configuring the general-purpose I/O pins for alternate analog function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC.

- Write to BUFMODE [2:0] to select SINGLE-ENDED or DIFFERENTIAL mode, as well as unbuffered or buffered mode.

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is. contained in the ADC Control Register 0.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control register can be written simultaneously (the ADC can be configured and enabled with the same write instruction):

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

129

| #5 MSB #5 LSB |

|---------------|

|---------------|

6. Add the gain correction factor to the original offset corrected value.

|   | #5 MSB | #5 LSB |

|---|--------|--------|

| + |        |        |

|   | #1 MSB | #1 LSB |

| = |        |        |

| #6 MSB #6 LSB |

|---------------|

|---------------|

7. Shift the result to the right, using the sign bit determined in Step 1. This allows for the detection of computational overflow.

| S-> #0 MSB #0 LSB |

|-------------------|

|-------------------|

#### **Output Data**

The following is the output format of the corrected ADC value.

| MSB      | LSB    |

|----------|--------|

| svba9876 | 543210 |

The overflow bit in the corrected output indicates that the computed value was greater than the maximum logical value (+1023) or less than the minimum logical value (-1024). Unlike the hardware overflow bit, this is not a simple binary Flag. For a normal sample (non-overflow), the sign and the overflow bit matches. If the sign bit and overflow bit do not match, a computational overflow has occurred.

#### Input Buffer Stage

Many applications require the measurement of an input voltage source with a high output impedance. This ADC provides a buffered input for such situations. The drawback of the buffered input is a limitation of the input range. When using unity gain buffered mode, the input signal must be prevented from coming too close to either  $V_{SS}$  or  $V_{DD}$ . See Table 135 on page 231 for details.

This condition applies only to the input voltage level (with respect to ground) of each differential input signal. The actual differential input voltage magnitude may be less than 300 mV.

The input range of the unbuffered ADC swings from  $V_{SS}$  to  $V_{DD}$ . Input signals smaller than 300 mV must use the unbuffered input mode. If these signals do not contain low output impedances, they might require off-chip buffering.

Signals outside the allowable input range can be used without instability or device damage. Any ADC readings made outside the input range are subject to greater inaccuracy than specified.

## **ADC Control Register Definitions**

## ADC Control Register 0

The ADC Control Register 0 (ADCCTL0) selects the analog input channel and initiates the analog-to-digital conversion. It also selects the voltage reference configuration.

Table 71. ADC Control Register 0 (ADCCTL0)

| BITS  | 7   | 6       | 5      | 4    | 3   | 2    | 1      | 0   |

|-------|-----|---------|--------|------|-----|------|--------|-----|

| FIELD | CEN | REFSELL | REFOUT | CONT |     | ANAI | N[3:0] |     |

| RESET | 0   | 0       | 0      | 0    | 0   | 0    | 0      | 0   |

| R/W   | R/W | R/W     | R/W    | R/W  | R/W | R/W  | R/W    | R/W |

| ADDR  |     |         |        | F7   | 0H  |      |        |     |

#### CEN—Conversion Enable

0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion is complete.

1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.

REFSELL—Voltage Reference Level Select Low Bit; in conjunction with the High bit (REFSELH) in ADC Control/Status Register 1, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL}; note that this reference is independent of the Comparator reference.

00= Internal Reference Disabled, reference comes from external pin

01= Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

11= Reserved

REFOUT—Internal Reference Output Enable

0 = Reference buffer is disabled; Vref pin is available for GPIO or analog functions

1 = The internal ADC reference is buffered and driven out to the Vref pin

<u>/</u>

**Warning:** When the ADC is used with an external reference ({REFSELH,REFSELL}=00), the REFOUT bit must be set to 0.

#### CONT

0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles (measurements of the internal temperature sensor take twice as long) 1 = Continuous conversion. ADC data updated every 256 system clock cycles after an initial 5129 clock conversion (measurements of the internal temperature sensor take twice as long)

zilog |

## Comparator

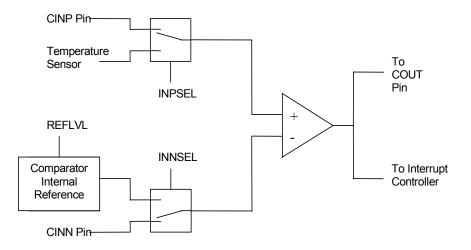

The Z8 Encore! XP<sup>®</sup> F082A Series devices feature a general purpose comparator that compares two analog input signals. These analog signals may be external stimulus from a pin (CINP and/or CINN) or internally generated signals. Both a programmable voltage reference and the temperature sensor output voltage are available internally. The output is available as an interrupt source or can be routed to an external pin.

Figure 20. Comparator Block Diagram

## Operation

When the positive comparator input exceeds the negative input by more than the specified hysteresis, the output is a logic HIGH. When the negative input exceeds the positive by more than the hysteresis, the output is a logic LOW. Otherwise, the comparator output retains its present value. See Table 137 on page 233 for details.

The comparator may be powered down to reduce supply current. See Power Control Register 0 on page 34 for details.

**Caution:** Because of the propagation delay of the comparator, it is not recommended to enable or reconfigure the comparator without first disabling interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts. The following example describes how to safely enable the comparator:

```

di

ld cmp0, r0 ; load some new configuration

nop

```

1001 = 1.8 V 1010–1111 = Reserved

For 8-pin devices:

000000 = 0.00 V000001 = 0.05 V000010 = 0.10 V 000011 = 0.15 V 000100 = 0.20 V000101 = 0.25 V000110 = 0.30 V 000111 = 0.35 V 001000 = 0.40 V 001001 = 0.45 V 001010 = 0.50 V 001011 = 0.55 V 001100 = 0.60 V 001101 = 0.65 V 001110 = 0.70 V001111 = 0.75 V 010000 = 0.80 V010001 = 0.85 V010010 = 0.90 V 010011 = 0.95 V 010100 = 1.00 V (Default) 010101 = 1.05 V 010110 = 1.10 V 010111 = 1.15 V 011000 = 1.20 V 011001 = 1.25 V 011010 = 1.30 V 011011 = 1.35 V 011100 = 1.40 V 011101 = 1.45 V 011110 = 1.50 V 011111 = 1.55 V 100000 = 1.60 V100001 = 1.65 V 100010 = 1.70 V 100011 = 1.75 V

## Operation

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for Byte Programming, Page Erase, and Mass Erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

The Flow Chart in Figure 22 displays basic Flash Controller operation. The following subsections provide details about the various operations (Lock, Unlock, Byte Programming, Page Protect, Page Unprotect, Page Select, Page Erase, and Mass Erase) displayed in Figure 22.

# **Flash Option Bits**

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore!  $XP^{\text{(R)}}$  F082A Series operation. The feature configuration data is stored in the Flash program memory and loaded into holding registers during Reset. The features available for control through the Flash Option Bits include:

- Watchdog Timer time-out response selection-interrupt or system reset

- Watchdog Timer always on (enabled at Reset)

- The ability to prevent unwanted read access to user code in Program Memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Program Memory

- Voltage Brownout configuration-always enabled or disabled during STOP mode to reduce STOP mode power consumption

- Oscillator mode selection-for high, medium, and low power crystal oscillators, or external RC oscillator

- Factory trimming information for the internal precision oscillator and low voltage detection

- Factory calibration values for ADC, temperature sensor, and Watchdog Timer compensation

- Factory serialization and randomized lot identifier (optional)

## Operation

## **Option Bit Configuration By Reset**

Each time the Flash Option Bits are programmed or erased, the device must be Reset for the change to take effect. During any reset operation (System Reset, Power-On Reset, or Stop Mode Recovery), the Flash Option Bits are automatically read from the Flash Program Memory and written to Option Configuration registers. The Option Configuration registers control operation of the devices within the Z8 Encore! XP F082A Series. Option Bit control is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

## **Oscillator Control**

The Z8 Encore!  $XP^{\mathbb{R}}$  F082A Series devices uses five possible clocking schemes, each user-selectable:

- Internal precision trimmed RC oscillator (IPO).

- On-chip oscillator using off-chip crystal or resonator.

- On-chip oscillator using external RC network.

- External clock drive.

- On-chip low power Watchdog Timer oscillator.

- Clock failure detection circuitry.

In addition, Z8 Encore! XP F082A Series devices contain clock failure detection and recovery circuitry, allowing continued operation despite a failure of the system clock oscillator.

### Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures.

#### **System Clock Selection**

The oscillator control block selects from the available clocks. Table 108 details each clock source and its usage.

230

|                                               | $T_A = -$ | = 2.7 V to<br>40 °C to +<br>otherwis | 105 °C  |        |                                                                                                                                                                   |

|-----------------------------------------------|-----------|--------------------------------------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                     | Minimum   | Typical                              | Maximum | Units  | Notes                                                                                                                                                             |

| Flash Byte Read Time                          | 100       | -                                    | -       | ns     |                                                                                                                                                                   |

| Flash Byte Program Time                       | 20        | _                                    | 40      | μs     |                                                                                                                                                                   |

| Flash Page Erase Time                         | 10        | -                                    | -       | ms     |                                                                                                                                                                   |

| Flash Mass Erase Time                         | 200       | -                                    | -       | ms     |                                                                                                                                                                   |

| Writes to Single Address<br>Before Next Erase | -         | _                                    | 2       |        |                                                                                                                                                                   |

| Flash Row Program Time                        | -         | -                                    | 8       | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This<br>parameter is only an issue<br>when bypassing the Flash<br>Controller. |

| Data Retention                                | 100       | _                                    | _       | years  | 25 °C                                                                                                                                                             |

| Endurance                                     | 10,000    | _                                    | _       | cycles | Program/erase cycles                                                                                                                                              |

#### Table 132. Flash Memory Electrical Characteristics and Timing

#### Table 133. Watchdog Timer Electrical Characteristics and Timing

| V <sub>DD</sub> = 2.7 V to 3.6 V   |  |

|------------------------------------|--|

| T <sub>A</sub> = -40 °C to +105 °C |  |

| (unless otherwise stated)          |  |

| Symbol              | Parameter                | Minimum | Typical | Maximum     | Units | Conditions                                                      |

|---------------------|--------------------------|---------|---------|-------------|-------|-----------------------------------------------------------------|

| F <sub>WDT</sub>    | WDT Oscillator Frequency |         | 10      |             | kHz   |                                                                 |

| F <sub>WDT</sub>    | WDT Oscillator Error     |         |         | <u>+</u> 50 | %     |                                                                 |

| T <sub>WDTCAL</sub> | WDT Calibrated Timeout   | 0.98    | 1       | 1.02        | S     | V <sub>DD</sub> = 3.3 V;<br>T <sub>A</sub> = 30 °C              |

|                     |                          | 0.70    | 1       | 1.30        | S     | $V_{DD}$ = 2.7 V to 3.6 V<br>T <sub>A</sub> = 0 °C to 70 °C     |

|                     |                          | 0.50    | 1       | 1.50        | S     | $V_{DD}$ = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C |

Zilog 239

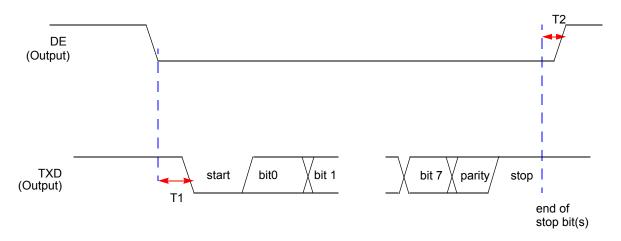

Figure 38 and Table 143 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the transmit data register has been written. DE remains asserted for multiple characters as long as the transmit data register is written with the next character before the current character has completed.

Figure 38. UART Timing Without CTS

| Table | 143. | UART | Timing | Without CTS |

|-------|------|------|--------|-------------|

|-------|------|------|--------|-------------|

|                |                                                                        | Delay (ns)        |            |  |  |  |

|----------------|------------------------------------------------------------------------|-------------------|------------|--|--|--|

| Parameter      | Abbreviation                                                           | Minimum           | Maximum    |  |  |  |

| UART           |                                                                        |                   |            |  |  |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * XIN<br>period | 1 bit time |  |  |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx data register is empty) | ± 5               |            |  |  |  |

250

| 25 |

|----|

| Part Number                                             | Flash     | RAM      | SUVN | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------------------------------|-----------|----------|------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082A Series with 1 KB Flash |           |          |      |           |            |                     |                     |                |            |                    |                     |

| Standard Temperatur                                     | e: 0 °C   | to 70 °C |      |           |            |                     |                     |                |            |                    |                     |

| Z8F011APB020SC                                          | 1 KB      | 256 B    | 16 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F011AQB020SC                                          | 1 KB      | 256 B    | 16 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F011ASB020SC                                          | 1 KB      | 256 B    | 16 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F011ASH020SC                                          | 1 KB      | 256 B    | 16 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F011AHH020SC                                          | 1 KB      | 256 B    | 16 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F011APH020SC                                          | 1 KB      | 256 B    | 16 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F011ASJ020SC                                          | 1 KB      | 256 B    | 16 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F011AHJ020SC                                          | 1 KB      | 256 B    | 16 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F011APJ020SC                                          | 1 KB      | 256 B    | 16 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperatur                                     | re: -40 ° | C to 10  | 5 °C |           |            |                     |                     |                |            |                    |                     |

| Z8F011APB020EC                                          | 1 KB      | 256 B    | 16 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F011AQB020EC                                          | 1 KB      | 256 B    | 16 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F011ASB020EC                                          | 1 KB      | 256 B    | 16 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F011ASH020EC                                          | 1 KB      | 256 B    | 16 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F011AHH020EC                                          | 1 KB      | 256 B    | 16 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F011APH020EC                                          | 1 KB      | 256 B    | 16 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F011ASJ020EC                                          | 1 KB      | 256 B    | 16 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F011AHJ020EC                                          | 1 KB      | 256 B    | 16 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F011APJ020EC                                          | 1 KB      | 256 B    | 16 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging                |           |          |      |           |            |                     |                     |                |            |                    |                     |

262

compare 85 compare - extended addressing 203 COMPARE mode 85 compare with carry 203 compare with carry - extended addressing 203 complement 205 complement carry flag 204 condition code 201 continuous conversion (ADC) 124 CONTINUOUS mode 84 control register definition, UART 108 Control Registers 15, 19 **COUNTER modes 84** CP 203 **CPC 203 CPCX 203** CPU and peripheral overview 5 CPU control instructions 204 **CPX 203** Customer Feedback Form 271

## D

DA 201, 203 data memory 17 DC characteristics 222 debugger, on-chip 173 **DEC 203** decimal adjust 203 decrement 203 decrement and jump non-zero 206 decrement word 203 **DECW 203** destination operand 202 device, port availability 37 DI 204 direct address 201 disable interrupts 204 **DJNZ 206** dst 202

### Ε

EI 204

electrical characteristics 221 ADC 231 flash memory and timing 230 GPIO input data sample timing 234 Watchdog Timer 230, 233 enable interrupt 204 ER 201 extended addressing register 201 external pin reset 27 eZ8 CPU features 5 eZ8 CPU instruction classes 202 eZ8 CPU instruction notation 200 eZ8 CPU instruction set 199 eZ8 CPU instruction summary 207

## F

FCTL register 149, 155, 156 features, Z8 Encore! 1 first opcode map 218 FLAGS 202 flags register 202 flash controller 7 option bit address space 156 option bit configuration - reset 153 program memory address 0000H 156 program memory address 0001H 158 flash memory 141 arrangement 142 byte programming 147 code protection 145 configurations 141 control register definitions 149, 155 controller bypass 148 electrical characteristics and timing 230 flash control register 149, 155, 156 flash option bits 146 flash status register 150 flow chart 144 frequency high and low byte registers 152 mass erase 147 operation 143 operation timing 145