Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

|                            |                                                           |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 128 x 8                                                   |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | ·                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f041ahj020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Universal Asynchronous Receiver/Transmitter**

The full-duplex universal asynchronous receiver/transmitter (UART) is included in all Z8 Encore! XP package types. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

#### Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE and COMPARE, PWM SINGLE OUTPUT and PWM DUAL OUTPUT modes.

#### General-Purpose Input/Output

The Z8 Encore! XP F082A Series features 6 to 25 port pins (Ports A–D) for general- purpose input/output (GPIO). The number of GPIO pins available is a function of package, and each pin is individually programmable. 5 V tolerant input pins are available on all I/Os on 8-pin devices and most I/Os on other package types.

#### **Direct LED Drive**

The 20- and 28-pin devices support controlled current sinking output pins capable of driving LEDs without the need for a current limiting resistor. These LED drivers are independently programmable to four different intensity levels.

#### **Flash Controller**

The Flash Controller programs and erases Flash memory. The Flash Controller supports several protection mechanisms against accidental program and erasure, as well as factory serialization and read protection.

#### Non-Volatile Data Storage

The non-volatile data storage (NVDS) uses a hybrid hardware/software scheme to implement a byte programmable data memory and is capable of over 100,000 write cycles.

**Note:** Devices with 8 KB Flash memory do not include the NVDS feature.

mation Area data rather than the Program Memory data. Access to the Flash Information Area is read-only.

| Program Memory Address (Hex) | Function                                                                                  |

|------------------------------|-------------------------------------------------------------------------------------------|

| FE00–FE3F                    | Zilog Option Bits/Calibration Data                                                        |

| FE40-FE53                    | Part Number<br>20-character ASCII alphanumeric code<br>Left justified and filled with FFH |

| FE54–FE5F                    | Reserved                                                                                  |

| FE60–FE7F                    | Zilog Calibration Data                                                                    |

| FE80–FFFF                    | Reserved                                                                                  |

Table 6. Z8 Encore! XP F082A Series Flash Memory Information Area Map

# Zilog <sub>19</sub>

# **Register Map**

Table 7 provides the address map for the Register File of the Z8 Encore! XP<sup>®</sup> F082A Series devices. Not all devices and package styles in the Z8 Encore! XP F082A Series support the ADC, or all of the GPIO Ports. Consider registers for unimplemented peripherals as Reserved.

#### Table 7. Register File Address Map

| Address (Hex) | Register Description              | Mnemonic      | Reset (Hex) | Page No |

|---------------|-----------------------------------|---------------|-------------|---------|

| General-Purpo | se RAM                            |               |             |         |

| Z8F082A/Z8F0  | 81A Devices                       |               |             |         |

| 000–3FF       | General-Purpose Register File RAM | _             | XX          |         |

| 400–EFF       | Reserved                          | —             | XX          |         |

| Z8F042A/Z8F0  | 41A Devices                       |               |             |         |

| 000–3FF       | General-Purpose Register File RAM | _             | XX          |         |

| 400–EFF       | Reserved                          | _             | XX          |         |

| Z8F022A/Z8F0  | 21A Devices                       |               |             |         |

| 000–1FF       | General-Purpose Register File RAM | _             | XX          |         |

| 200–EFF       | Reserved                          | —             | XX          |         |

| Z8F012A/Z8F0  | 11A Devices                       |               |             |         |

| 000–0FF       | General-Purpose Register File RAM | _             | XX          |         |

| 100–EFF       | Reserved                          | —             | XX          |         |

| Timer 0       |                                   |               |             |         |

| F00           | Timer 0 High Byte                 | T0H           | 00          | 87      |

| F01           | Timer 0 Low Byte                  | TOL           | 01          | 87      |

| F02           | Timer 0 Reload High Byte          | T0RH          | FF          | 88      |

| F03           | Timer 0 Reload Low Byte           | T0RL          | FF          | 88      |

| F04           | Timer 0 PWM High Byte             | T0PWMH        | 00          | 88      |

| F05           | Timer 0 PWM Low Byte              | <b>T0PWML</b> | 00          | 89      |

| F06           | Timer 0 Control 0                 | TOCTLO        | 00          | 83      |

| F07           | Timer 0 Control 1                 | T0CTL1        | 00          | 84      |

| Timer 1       |                                   |               |             |         |

| F08           | Timer 1 High Byte                 | T1H           | 00          | 87      |

| F09           | Timer 1 Low Byte                  | T1L           | 01          | 87      |

| F0A           | Timer 1 Reload High Byte          | T1RH          | FF          | 88      |

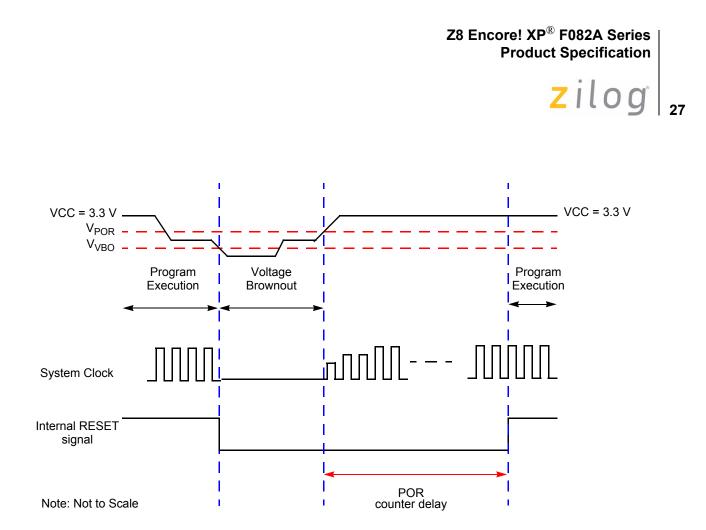

Figure 6. Voltage Brownout Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a Power-On Reset after recovering from a VBO condition.

### Watchdog Timer Reset

If the device is in NORMAL or HALT mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash Option Bit is programmed to 1. This is the unprogrammed state of the WDT\_RES Flash Option Bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT bit in the Reset Status (RSTSTAT) register is set to signify that the reset was initiated by the Watchdog Timer.

### External Reset Input

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system clock and reset signals, the required reset duration may be as short as three clock periods

# **Interrupt Controller**

The interrupt controller on the Z8 Encore! XP F082A Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of interrupt controller include:

- 20 possible interrupt sources with 18 unique interrupt vectors:

- Twelve GPIO port pin interrupt sources (two interrupt vectors are shared).

- Eight on-chip peripheral interrupt sources (two interrupt vectors are shared).

- Flexible GPIO interrupts:

- Eight selectable rising and falling edge GPIO interrupts.

- Four dual-edge interrupts.

- Three levels of individually programmable interrupt priority.

- Watchdog Timer and LVD can be configured to generate an interrupt.

- Supports vectored as well as polled interrupts

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt controller has no effect on operation. For more information on interrupt servicing by the eZ8 CPU, refer to *eZ8 CPU Core User Manual (UM0128)* available for download at <u>www.zilog.com</u>.

# Interrupt Vector Listing

Table 32 on page 56 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most-significant byte (MSB) at the even Program Memory address and the least-significant byte (LSB) at the following odd Program Memory address.

**Note:** Some port interrupts are not available on the 8- and 20-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

# Timers

These Z8 Encore! XP<sup>®</sup> F082A Series products contain two 16-bit reloadable timers that can be used for timing, event counting, or generation of pulse-width modulated (PWM) signals. The timers' feature include:

- 16-bit reload counter.

- Programmable prescaler with prescale values from 1 to 128.

- PWM output generation.

- Capture and compare capability.

- External input pin for timer input, clock gating, or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency.

- Timer output pin.

- Timer interrupt.

In addition to the timers described in this chapter, the Baud Rate Generator of the UART (if unused) may also provide basic timing functionality. For information on using the Baud Rate Generator as an additional timer, see Universal Asynchronous Receiver/Transmitter on page 97.

## Architecture

Figure 9 on page 70 displays the architecture of the timers.

zilog

Timer Reload Low Byte register occurs, the temporary holding register value is written to the Timer High Byte register. This operation allows simultaneous updates of the 16-bit Timer Reload value.

In COMPARE mode, the Timer Reload High and Low Byte registers store the 16-bit Compare value.

#### Table 52. Timer 0–1 Reload High Byte Register (TxRH)

| BITS  | 7   | 6               | 5   | 4     | 3    | 2   | 1   | 0   |  |  |  |

|-------|-----|-----------------|-----|-------|------|-----|-----|-----|--|--|--|

| FIELD |     | TRH             |     |       |      |     |     |     |  |  |  |

| RESET | 1   | 1 1 1 1 1 1 1 1 |     |       |      |     |     |     |  |  |  |

| R/W   | R/W | R/W             | R/W | R/W   | R/W  | R/W | R/W | R/W |  |  |  |

| ADDR  |     |                 |     | F02H, | F0AH |     |     |     |  |  |  |

Table 53. Timer 0–1 Reload Low Byte Register (TxRL)

| BITS  | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |  |  |  |

|-------|-----|-----|-----|-------|------|-----|-----|-----|--|--|--|

| FIELD |     | TRL |     |       |      |     |     |     |  |  |  |

| RESET | 1   | 1   | 1   | 1     | 1    | 1   | 1   | 1   |  |  |  |

| R/W   | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |  |  |  |

| ADDR  |     |     |     | F03H, | F0BH |     |     |     |  |  |  |

TRH and TRL—Timer Reload Register High and Low

These two bytes form the 16-bit Reload value, {TRH[7:0], TRL[7:0]}. This value sets the maximum count value which initiates a timer reload to 0001H. In COMPARE mode, these two bytes form the 16-bit Compare value.

### **Timer 0-1 PWM High and Low Byte Registers**

The Timer 0-1 PWM High and Low Byte (TxPWMH and TxPWML) registers (Table 54 and Table 55) control Pulse-Width Modulator (PWM) operations. These registers also store the Capture values for the CAPTURE and CAPTURE/COMPARE modes.

#### Table 54. Timer 0–1 PWM High Byte Register (TxPWMH)

| BITS  | 7   | 6    | 5   | 4     | 3    | 2   | 1   | 0   |  |  |  |

|-------|-----|------|-----|-------|------|-----|-----|-----|--|--|--|

| FIELD |     | PWMH |     |       |      |     |     |     |  |  |  |

| RESET | 0   | 0    | 0   | 0     | 0    | 0   | 0   | 0   |  |  |  |

| R/W   | R/W | R/W  | R/W | R/W   | R/W  | R/W | R/W | R/W |  |  |  |

| ADDR  |     |      |     | F04H, | F0CH |     |     |     |  |  |  |

MPRX—Multiprocessor Receive

Returns the value of the most recent multiprocessor bit received. Reading from the UART Receive Data register resets this bit to 0.

### **UART Transmit Data Register**

Data bytes written to the UART Transmit Data (UxTXD) register (Table 65) are shifted out on the TXDx pin. The Write-only UART Transmit Data register shares a Register File address with the read-only UART Receive Data register.

| BITS  | 7 | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|-------|---|-----|---|----|----|---|---|---|--|--|--|

| FIELD |   | TXD |   |    |    |   |   |   |  |  |  |

| RESET | Х | Х   | Х | Х  | Х  | Х | Х | Х |  |  |  |

| R/W   | W | W   | W | W  | W  | W | W | W |  |  |  |

| ADDR  |   |     |   | F4 | 0H |   |   |   |  |  |  |

#### Table 65. UART Transmit Data Register (U0TXD)

TXD-Transmit Data

UART transmitter data byte to be shifted out through the TXDx pin.

### **UART Receive Data Register**

Data bytes received through the RXDx pin are stored in the UART Receive Data (UxRXD) register (Table 66). The read-only UART Receive Data register shares a Register File address with the Write-only UART Transmit Data register.

#### Table 66. UART Receive Data Register (U0RXD)

| BITS      | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------|-------|---|---|---|---|---|---|---|--|--|

| FIELD     | RXD   |   |   |   |   |   |   |   |  |  |

| RESET     | Х     | Х | Х | Х | Х | Х | Х | Х |  |  |

| R/W       | R     | R | R | R | R | R | R | R |  |  |

| ADDR      | F40H  |   |   |   |   |   |   |   |  |  |

| X = Undef | ined. |   |   |   |   |   |   |   |  |  |

RXD—Receive Data

UART receiver data byte from the RXDx pin

# zilog<sup>®</sup> |<sub>11</sub>

The UART data rate is calculated using the following equation:

UART Baud Rate (bits/s) =

$$\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$$

For a given UART data rate, calculate the integer baud rate divisor value using the following equation:

UART Baud Rate Divisor Value (BRG) = Round

$$\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$$

The baud rate error relative to the acceptable baud rate is calculated using the following equation:

UART Baud Rate Error (%) =

$$100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$$

For reliable communication, the UART baud rate error must never exceed 5 percent. Table 70 provides information on the data rate errors for popular baud rates and commonly used crystal oscillator frequencies.

| 10.0 MHz Sy              | stem Clock               |                      |              | 5.5296 MHz \$            | System Clock             |                      |              |

|--------------------------|--------------------------|----------------------|--------------|--------------------------|--------------------------|----------------------|--------------|

| Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) | Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) |

| 1250.0                   | N/A                      | N/A                  | N/A          | 1250.0                   | N/A                      | N/A                  | N/A          |

| 625.0                    | 1                        | 625.0                | 0.00         | 625.0                    | N/A                      | N/A                  | N/A          |

| 250.0                    | 3                        | 208.33               | -16.67       | 250.0                    | 1                        | 345.6                | 38.24        |

| 115.2                    | 5                        | 125.0                | 8.51         | 115.2                    | 3                        | 115.2                | 0.00         |

| 57.6                     | 11                       | 56.8                 | -1.36        | 57.6                     | 6                        | 57.6                 | 0.00         |

| 38.4                     | 16                       | 39.1                 | 1.73         | 38.4                     | 9                        | 38.4                 | 0.00         |

| 19.2                     | 33                       | 18.9                 | 0.16         | 19.2                     | 18                       | 19.2                 | 0.00         |

| 9.60                     | 65                       | 9.62                 | 0.16         | 9.60                     | 36                       | 9.60                 | 0.00         |

| 4.80                     | 130                      | 4.81                 | 0.16         | 4.80                     | 72                       | 4.80                 | 0.00         |

| 2.40                     | 260                      | 2.40                 | -0.03        | 2.40                     | 144                      | 2.40                 | 0.00         |

| 1.20                     | 521                      | 1.20                 | -0.03        | 1.20                     | 288                      | 1.20                 | 0.00         |

| 0.60                     | 1042                     | 0.60                 | -0.03        | 0.60                     | 576                      | 0.60                 | 0.00         |

| 0.30                     | 2083                     | 0.30                 | 0.2          | 0.30                     | 1152                     | 0.30                 | 0.00         |

|                          |                          |                      |              | -                        |                          |                      |              |

#### Table 70. UART Baud Rates

# **Analog-to-Digital Converter**

The analog-to-digital converter (ADC) converts an analog input signal to its digital representation. The features of this sigma-delta ADC include:

- 11-bit resolution in DIFFERENTIAL mode.

- 10-bit resolution in SINGLE-ENDED mode.

- Eight single-ended analog input sources are multiplexed with general-purpose I/O ports.

- 9<sup>th</sup> analog input obtained from temperature sensor peripheral.

- 11 pairs of differential inputs also multiplexed with general-purpose I/O ports.

- Low-power operational amplifier (LPO).

- Interrupt on conversion complete.

- Bandgap generated internal voltage reference with two selectable levels.

- Manual in-circuit calibration is possible employing user code (offset calibration).

- Factory calibrated for in-circuit error compensation.

### Architecture

Figure 19 displays the major functional blocks of the ADC. An analog multiplexer network selects the ADC input from the available analog pins, ANA0 through ANA7.

The input stage of the ADC allows both differential gain and buffering. The following input options are available:

- Unbuffered input (SINGLE-ENDED and DIFFERENTIAL modes).

- Buffered input with unity gain (SINGLE-ENDED and DIFFERENTIAL modes).

- LPO output with full pin access to the feedback path.

138

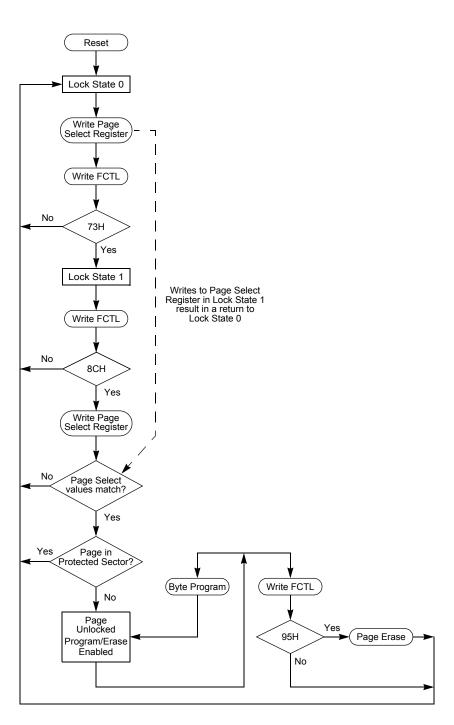

# **Flash Memory**

The products in the Z8 Encore! XP<sup>®</sup> F082A Series feature a non-volatile Flash memory of 8 KB (8192), 4 KB (4096), 2 KB (2048 bytes), or 1 KB (1024) with read/write/ erase capability. The Flash Memory can be programmed and erased in-circuit by user code or through the On-Chip Debugger. The features include:

- User controlled read and write protect capability

- Sector-based write protection scheme

- Additional protection schemes against accidental program and erasure

#### Architecture

The Flash memory array is arranged in pages with 512 bytes per page. The 512 byte page is the minimum Flash block size that can be erased. Each page is divided into 8 rows of 64 bytes.

For program or data protection, the Flash memory is also divided into sectors. In the Z8 Encore! XP F082A Series, these sectors are either 1024 bytes (in the 8 KB devices) or 512 bytes (all other memory sizes) in size. Page and sector sizes are not generally equal.

The first 2 bytes of the Flash Program memory are used as Flash Option Bits. For more information about their operation, see Flash Option Bits on page 153.

Table 76 describes the Flash memory configuration for each device in the Z8 Encore! XPF082A Series. Figure 21 displays the Flash memory arrangement.

| Part Number | Flash Size<br>KB (Bytes) | Flash<br>Pages | Program Memory<br>Addresses | Flash Sector<br>Size (Bytes) |

|-------------|--------------------------|----------------|-----------------------------|------------------------------|

| Z8F08xA     | 8 (8192)                 | 16             | 0000H–1FFFH                 | 1024                         |

| Z8F04xA     | 4 (4096)                 | 8              | 0000H-0FFFH                 | 512                          |

| Z8F02xA     | 2 (2048)                 | 4              | 0000H–07FFH                 | 512                          |

| Z8F01xA     | 1 (1024)                 | 2              | 0000H-03FFH                 | 512                          |

#### Table 76. Z8 Encore! XP F082A Series Flash Memory Configurations

Figure 22. Flash Controller Operation Flow Chart

**z**ilog<sup>°</sup>

### **Option Bit Types**

#### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. User access to these bits has been provided because these locations contain application-specific device configurations. The information contained here is lost when page 0 of the program memory is erased.

#### **Trim Option Bits**

The trim option bits are contained in the information page of the Flash memory. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered. Program Memory may be erased without endangering these values. It is possible to alter working values of these bits by accessing the Trim Bit Address and Data Registers, but these working values are lost after a power loss or any other reset event.

There are 32 bytes of trim data. To modify one of these values the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data register returns the working value of the target trim data byte.

The trim address range is from information address 20-3F only. The remainder of the information page is not accessible through the trim bit address and data registers.

#### **Calibration Option Bits**

The calibration option bits are also contained in the information page. These bits are factory programmed values intended for use in software correcting the device's analog performance. To read these values, the user code must employ the LDC instruction to access the information area of the address space as defined in See Flash Information Area on page 17.

#### **Serialization Bits**

As an optional feature, Zilog<sup>®</sup> is able to provide factory-programmed serialization. For serialized products, the individual devices are programmed with unique serial numbers. These serial numbers are binary values, four bytes in length. The numbers increase in size with each device, but gaps in the serial sequence may exist.

These serial numbers are stored in the Flash information page (see Reading the Flash Information Page on page 155 and Serialization Data on page 165 for more details) and are unaffected by mass erasure of the device's Flash memory.

Note:

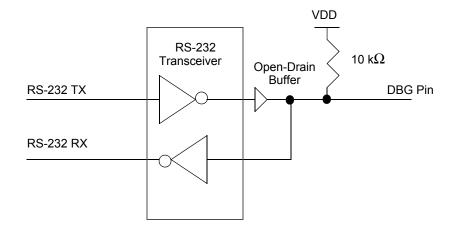

#### Figure 25. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (2)

#### **DEBUG Mode**

The operating characteristics of the devices in DEBUG mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions.

- The system clock operates unless in STOP mode.

- All enabled on-chip peripherals operate unless in STOP mode.

- Automatically exits HALT mode.

- Constantly refreshes the Watchdog Timer, if enabled.

#### **Entering DEBUG Mode**

The operating characteristics of the devices entering DEBUG mode are:

- The device enters DEBUG mode after the eZ8 CPU executes a BRK (Breakpoint) instruction.

- If the DBG pin is held Low during the final clock cycle of system reset, the part enters DEBUG mode immediately (20-/28-pin products only).

- **Note:** Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an Autobaud sequence (see OCD Auto-Baud Detector/Generator on page 176).

# zilog

#### 199

# eZ8 CPU Instruction Set

# **Assembly Language Programming Introduction**

The eZ8 CPU assembly language provides a means for writing an application program without concern for actual memory addresses or machine instruction formats. A program written in assembly language is called a source program. Assembly language allows the use of symbolic addresses to identify memory locations. It also allows mnemonic codes (opcodes and operands) to represent the instructions themselves. The opcodes identify the instruction while the operands represent memory locations, registers, or immediate data values.

Each assembly language program consists of a series of symbolic commands called statements. Each statement can contain labels, operations, operands and comments.

Labels can be assigned to a particular instruction step in a source program. The label identifies that step in the program as an entry point for use by other instructions.

The assembly language also includes assembler directives that supplement the machine instruction. The assembler directives, or pseudo-ops, are not translated into a machine instruction. Rather, the pseudo-ops are interpreted as directives that control or assist the assembly process.

The source program is processed (assembled) by the assembler to obtain a machine language program called the object code. The object code is executed by the eZ8 CPU. An example segment of an assembly language program is detailed in the following example.

#### Assembly Language Source Program Example

| JP START      | ; Everything after the semicolon is a comment.                                                                                                                                                                         |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:        | ; A label called 'START'. The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs.                                          |

| LD R4, R7     | ; A Load (LD) instruction with two operands. The first operand,<br>; Working Register R4, is the destination. The second operand,<br>; Working Register R7, is the source. The contents of R7 is<br>; written into R4. |

| LD 234H, #%01 | ; Another Load (LD) instruction with two operands.<br>; The first operand, Extended Mode Register Address 234H,<br>; identifies the destination. The second operand, Immediate Data                                    |

|               | ; value 01H, is the source. The value 01H is written into the ; Register at address 234H.                                                                                                                              |

#### Table 128. Power Consumption (Continued)

|                     |                                                      | V <sub>DI</sub> | <sub>o</sub> = 2.7 V to 3 | 5.6 V    |       |                                   |

|---------------------|------------------------------------------------------|-----------------|---------------------------|----------|-------|-----------------------------------|

|                     |                                                      |                 | Maximum <sup>2</sup>      |          |       |                                   |

| Symbol              | Parameter                                            | Typical $^1$    | Std Temp                  | Ext Temp | Units | Conditions                        |

| I <sub>DD</sub> LPO | Low-Power Operational<br>Amplifier Supply<br>Current | 3               | 5                         | 5        | μΑ    | Driving a high-<br>impedance load |

| I <sub>DD</sub> TS  | Temperature Sensor<br>Supply Current                 | 60              |                           |          | μA    | See Notes 4                       |

| I <sub>DD</sub> BG  | Band Gap Supply                                      | 320             | 480                       | 500      | μA    | For 20-/28-pin devices            |

|                     | Current                                              |                 |                           |          |       | For 8-pin devices                 |

#### Notes

1. Typical conditions are defined as  $V_{DD}$  = 3.3 V and +30 °C.

2. Standard temperature is defined as  $T_A = 0$  °C to +70 °C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

3. Extended temperature is defined as T<sub>A</sub> = -40 °C to +105 °C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

| Part Number                                             | Flash | RAM  | NVDS | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------------------------------|-------|------|------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082A Series with 8 KB Flash |       |      |      |           |            |                     |                     |                |            |                    |                     |

| Standard Temperature: 0 °C to 70 °C                     |       |      |      |           |            |                     |                     |                |            |                    |                     |

| Z8F081APB020SC                                          | 8 KB  | 1 KB | 0    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F081AQB020SC                                          | 8 KB  | 1 KB | 0    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F081ASB020SC                                          | 8 KB  | 1 KB | 0    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F081ASH020SC                                          | 8 KB  | 1 KB | 0    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F081AHH020SC                                          | 8 KB  | 1 KB | 0    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F081APH020SC                                          | 8 KB  | 1 KB | 0    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F081ASJ020SC                                          | 8 KB  | 1 KB | 0    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F081AHJ020SC                                          | 8 KB  | 1 KB | 0    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F081APJ020SC                                          | 8 KB  | 1 KB | 0    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperature: -40 °C to 105 °C                  |       |      |      |           |            |                     |                     |                |            |                    |                     |

| Z8F081APB020EC                                          | 8 KB  | 1 KB | 0    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F081AQB020EC                                          | 8 KB  | 1 KB | 0    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F081ASB020EC                                          | 8 KB  | 1 KB | 0    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F081ASH020EC                                          | 8 KB  | 1 KB | 0    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F081AHH020EC                                          | 8 KB  | 1 KB | 0    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F081APH020EC                                          | 8 KB  | 1 KB | 0    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F081ASJ020EC                                          | 8 KB  | 1 KB | 0    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F081AHJ020EC                                          | 8 KB  | 1 KB | 0    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F081APJ020EC                                          | 8 KB  | 1 KB | 0    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging                |       |      |      |           |            |                     |                     |                |            |                    |                     |

**z**ilog<sup>°</sup>

268

subtract with carry - extended addressing 203 SUBX 203 SWAP 207 swap nibbles 207 symbols, additional 202

### Т

TCM 204 **TCMX 204 Technical Support 271** test complement under mask 204 test complement under mask - extended addressing 204 test under mask 204 test under mask - extended addressing 204 timer signals 11 timers 69 architecture 69 block diagram 70 CAPTURE mode 77, 78, 85, 86 CAPTURE/COMPARE mode 81, 85 COMPARE mode 79, 85 CONTINUOUS mode 71, 84 COUNTER mode 72, 73 COUNTER modes 84 GATED mode 80, 85 ONE-SHOT mode 70, 84 operating mode 70 PWM mode 74, 76, 85 reading the timer count values 82 reload high and low byte registers 87 timer control register definitions 83 timer output signal operation 82 timers 0-3 control registers 83, 84 high and low byte registers 87, 88 TM 204 TMX 204 transmit IrDA data 118 transmitting UART data-polled method 99 transmitting UART dat-interrupt-driven method 100

TRAP 206

# U

#### UART 7

architecture 97 baud rate generator 107 baud rates table 115 control register definitions 108 controller signals 11 data format 98 interrupts 105 multiprocessor mode 103 receiving data using interrupt-driven method 102 receiving data using the polled method 101 transmitting data usin the interrupt-driven method 100 transmitting data using the polled method 99 x baud rate high and low registers 114 x control 0 and control 1 registers 108 x status 0 and status 1 registers 111, 112 UxBRH register 114 UxBRL register 114 UxCTL0 register 108, 114 UxCTL1 register 109 UxRXD register 113 UxSTAT0 register 111 UxSTAT1 register 112 UxTXD register 113

# V

vector 201 Voltage Brownout reset (VBR) 26

# W

Watchdog Timer approximate time-out delay 91 approximate time-out delays 135 CNTL 26 control register 94, 136, 190