Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 128 x 8                                                   |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f041apj020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Port A–C Input Data Registers51Port A–D Output Data Register52LED Drive Enable Register52LED Drive Level High Register53LED Drive Level Low Register53                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt Controller 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Interrupt Vector Listing55Architecture57Operation57Master Interrupt Enable57Interrupt Vectors and Priority58Interrupt Assertion59Watchdog Timer Interrupt Assertion59Watchdog Timer Interrupt Assertion59Interrupt Request 0 Register Definitions60Interrupt Request 1 Register61Interrupt Request 2 Register62IRQ0 Enable High and Low Bit Registers63IRQ2 Enable High and Low Bit Registers65Interrupt Edge Select Register66Shared Interrupt Select Register66Interrupt Control Register66 |

| Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Architecture69Operation70Timer Operating Modes70Reading the Timer Count Values82Timer Pin Signal Operation82Timer Control Register Definitions83Timer 0–1 Control Registers83Timer 0–1 High and Low Byte Registers87Timer 0-1 PWM High and Low Byte Registers88                                                                                                                                                                                                                               |

| Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Operation    91      Watchdog Timer Refresh    92                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# **Pin Description**

The Z8 Encore! XP<sup>®</sup> F082A Series products are available in a variety of packages styles and pin configurations. This chapter describes the signals and available pin configurations for each of the package styles. For information on physical package specifications, see Packaging on page 241.

# **Available Packages**

The following package styles are available for each device in the Z8 Encore! XP F082A Series product line:

- SOIC

- 8-, 20-, and 28-pin

- PDIP

- 8-, 20-, and 28-pin

- SSOP

- 20- and 28- pin

- QFN (this is an MLF-S, a QFN style package with an 8-pin SOIC footprint)

- 8-pin

In addition, the Z8 Encore! XP F082A Series devices are available both with and without advanced analog capability (ADC, temperature sensor and op amp). Devices Z8F082A, Z8F042A, Z8F022A, and Z8F012A contain the advanced analog, while devices Z8F081A, Z8F041A, Z8F021A, and Z8F011A do not have the advanced analog capability.

# **Pin Configurations**

Figure 2 through Figure 4 display the pin configurations for all the packages available in the Z8 Encore! XP F082A Series. See Table 2 on page 11 for a description of the signals. The analog input alternate functions (ANAx) are not available on the Z8F081A, Z8F041A, Z8F021A, and Z8F011A devices. The analog supply pins (AV<sub>DD</sub> and AV<sub>SS</sub>) are also not available on these parts, and are replaced by PB6 and PB7.

At reset, all Port A, B and C pins default to an input state. In addition, any alternate functionality is not enabled, so the pins function as general purpose input ports until programmed otherwise. At powerup, the PD0 pin defaults to the RESET alternate function.

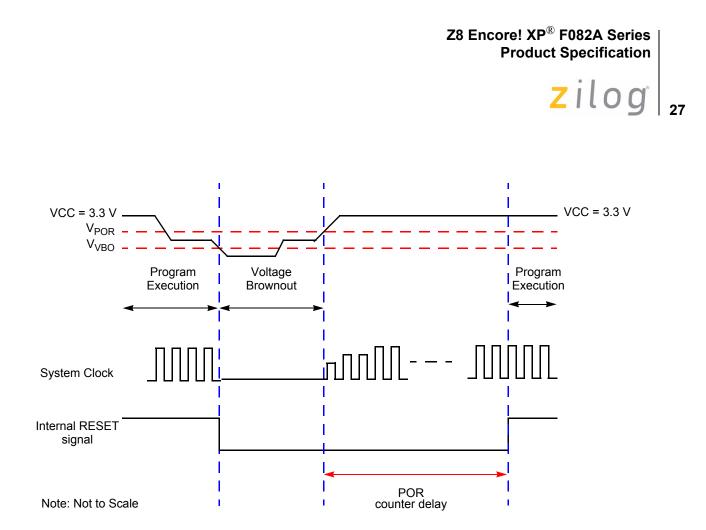

Figure 6. Voltage Brownout Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a Power-On Reset after recovering from a VBO condition.

# Watchdog Timer Reset

If the device is in NORMAL or HALT mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash Option Bit is programmed to 1. This is the unprogrammed state of the WDT\_RES Flash Option Bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT bit in the Reset Status (RSTSTAT) register is set to signify that the reset was initiated by the Watchdog Timer.

### External Reset Input

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system clock and reset signals, the required reset duration may be as short as three clock periods

**Caution:** The following coding style that clears bits in the Interrupt Request registers is not recommended. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost.

Poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

Caution: To avoid missing interrupts, use the following coding style to clear bits in the Interrupt Request 0 register:

Good coding style that avoids lost interrupt requests:

ANDX IRQO, MASK

### Software Interrupt Assertion

Program code can generate interrupts directly. Writing a 1 to the correct bit in the Interrupt Request register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request register is automatically cleared to 0.

**Caution:** The following coding style used to generate software interrupts by setting bits in the Interrupt Request registers is not recommended. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost.

Poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 OR r0, MASK LDX IRQ0, r0

**Caution:** To avoid missing interrupts, use the following coding style to set bits in the Interrupt Request registers:

> Good coding style that avoids lost interrupt requests: ORX IRQO, MASK

### Watchdog Timer Interrupt Assertion

The Watchdog Timer interrupt behavior is different from interrupts generated by other sources. The Watchdog Timer continues to assert an interrupt as long as the timeout condition continues. As it operates on a different (and usually slower) clock domain than the rest of the device, the Watchdog Timer continues to assert this interrupt for many system clocks until the counter rolls over.

Follow the steps below for configuring a timer for CAPTURE mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for CAPTURE mode.

- Set the prescale value.

- Set the Capture edge (rising or falling) for the Timer Input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. Clearing these registers allows the software to determine if interrupts were generated by either a capture event or a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

In CAPTURE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

### **CAPTURE RESTART Mode**

In CAPTURE RESTART mode, the current timer count value is recorded when the acceptable external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte Registers. The timer input is the system clock. The TPOL bit in the Timer Control register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 register is set to indicate the timer interrupt is because of an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to

# Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which may place the Z8 Encore! XP<sup>®</sup> F082A Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator.

- A selectable time-out response: reset or interrupt.

- 24-bit programmable time-out value.

# Operation

The Watchdog Timer is a one-shot timer that resets or interrupts the Z8 Encore! XP F082A Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash Option Bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10 kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 56 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

### Table 56. Watchdog Timer Approximate Time-Out Delays

| WDT Reload Value | (Decimal)<br>4 |            | e Time-Out Delay<br>VDT oscillator frequency) |

|------------------|----------------|------------|-----------------------------------------------|

|                  |                | Typical    | Description                                   |

| 000004           | 4              | 400 μs     | Minimum time-out delay                        |

| FFFFF            | 16,777,215     | 28 minutes | Maximum time-out delay                        |

Watchdog Timer Reload Registers results in a one-second timeout at room temperature and 3.3 V supply voltage.

Timeouts other than one second may be obtained by scaling the calibration values up or down as required.

**Note:** *The Watchdog Timer accuracy still degrades as temperature and supply voltage vary. See* Table 133 on page 230 *for* details.

# Watchdog Timer Control Register Definitions

### Watchdog Timer Control Register

The Watchdog Timer Control (WDTCTL) register is a write-only control register. Writing the 55H, AAH unlock sequence to the WDTCTL register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers.

This register address is shared with the read-only Reset Status register.

| BITS      | 7              | 6 | 5 | 4   | 3    | 2 | 1   | 0 |  |

|-----------|----------------|---|---|-----|------|---|-----|---|--|

| FIELD     |                |   |   | WDT | UNLK |   |     |   |  |

| RESET     | Х              | Х | Х | Х   | Х    | Х | X X |   |  |

| R/W       | W              | W | W | W   | W    | W | W   | W |  |

| ADDR      | FF0H           |   |   |     |      |   |     |   |  |

| X = Undef | K = Undefined. |   |   |     |      |   |     |   |  |

### Table 57. Watchdog Timer Control Register (WDTCTL)

WDTUNLK—Watchdog Timer Unlock

The software must write the correct unlocking sequence to this register before it is allowed to modify the contents of the Watchdog Timer reload registers.

### Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers (Table 58 through Table 60) form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. The 24-bit reload value is {WDTU[7:0], WDTH[7:0]}. Writing to these registers sets the appropriate Reload Value. Reading from these registers returns the current Watchdog Timer count value.

**Caution:** *The 24-bit WDT Reload Value must not be set to a value less than* 000004H.

### Table 58. Watchdog Timer Reload Upper Byte Register (WDTU)

| BITS       | 7                                                                                      | 6    | 5 | 4  | 3   | 2 | 1 | 0 |  |

|------------|----------------------------------------------------------------------------------------|------|---|----|-----|---|---|---|--|

| FIELD      |                                                                                        |      |   | WD | UTU |   |   |   |  |

| RESET      |                                                                                        | 00H  |   |    |     |   |   |   |  |

| R/W        |                                                                                        | R/W* |   |    |     |   |   |   |  |

| ADDR       |                                                                                        | FF1H |   |    |     |   |   |   |  |

| R/W* - Rea | * - Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |   |    |     |   |   |   |  |

R/W\* - Read returns the current WDT count value. Write sets the appropriate Reload Value.

WDTU—WDT Reload Upper Byte

Most-significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value.

### Table 59. Watchdog Timer Reload High Byte Register (WDTH)

| BITS       | 7                                                                                         | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|------------|-------------------------------------------------------------------------------------------|------|---|---|---|---|---|---|--|--|

| FIELD      |                                                                                           | WDTH |   |   |   |   |   |   |  |  |

| RESET      |                                                                                           | 04H  |   |   |   |   |   |   |  |  |

| R/W        |                                                                                           | R/W* |   |   |   |   |   |   |  |  |

| ADDR       |                                                                                           | FF2H |   |   |   |   |   |   |  |  |

| R/W* - Rea | R/W* - Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |   |   |   |   |   |   |  |  |

WDTH—WDT Reload High Byte

Middle byte, Bits[15:8], of the 24-bit WDT reload value.

### Table 60. Watchdog Timer Reload Low Byte Register (WDTL)

| BITS       | 7                                                                                         | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|------------|-------------------------------------------------------------------------------------------|------|---|---|---|---|---|---|--|--|

| FIELD      |                                                                                           | WDTL |   |   |   |   |   |   |  |  |

| RESET      |                                                                                           | 00H  |   |   |   |   |   |   |  |  |

| R/W        |                                                                                           | R/W* |   |   |   |   |   |   |  |  |

| ADDR       |                                                                                           | FF3H |   |   |   |   |   |   |  |  |

| R/W* - Rea | R/W* - Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |   |   |   |   |   |   |  |  |

WDTL—WDT Reload Low

Least significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value.

# Universal Asynchronous Receiver/Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. Features of the UART include:

- 8-bit asynchronous data transfer.

- Selectable even- and odd-parity generation and checking.

- Option of one or two STOP bits.

- Separate transmit and receive interrupts.

- Framing, parity, overrun and break detection.

- Separate transmit and receive enables.

- 16-bit baud rate generator (BRG).

- Selectable MULTIPROCESSOR (9-bit) mode with three configurable interrupt schemes.

- Baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

- Driver enable (DE) output for external bus transceivers.

### Architecture

The UART consists of three primary functional blocks: transmitter, receiver, and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 on page 98 displays the UART architecture.

value 63H to the Flash Control register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

### **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programming is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information on bypassing the Flash Controller, refer to *Third-Party Flash Pro*gramming Support for Z8 Encore!<sup>®</sup> MCU Application Note (AN0117) available for download at <u>www.zilog.com</u>.

### Flash Controller Behavior in DEBUG Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored.

- The Flash Sector Protect register is ignored for programming and erase operations.

- Programming operations are not limited to the page selected in the Page Select register.

- Bits in the Flash Sector Protect register can be written to one or zero.

- The second write of the Page Select register to unlock the Flash Controller is not necessary.

- The Page Select register can be written when the Flash Controller is unlocked.

- The Mass Erase command is enabled through the Flash Control register.

**Caution:** For security reasons, the Flash controller allows only a single page to be opened for write/erase. When writing multiple Flash pages, the flash controller must go through the unlock sequence again to select another page.

165

WDTCALH—Watchdog Timer Calibration High Byte The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload registers result in a one second timeout at room temperature and 3.3 V supply voltage. To use the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDTCALH and WDTL with WDTCALL.

### Table 98. Watchdog Calibration Low Byte at 007FH (WDTCALL)

| BITS      | 7                                               | 6       | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-----------|-------------------------------------------------|---------|-----|-----|-----|-----|-----|-----|--|--|

| FIELD     |                                                 | WDTCALL |     |     |     |     |     |     |  |  |

| RESET     | U                                               | U       | U   | U   | U   | U   | UU  |     |  |  |

| R/W       | R/W                                             | R/W     | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR      | Information Page Memory 007FH                   |         |     |     |     |     |     |     |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |         |     |     |     |     |     |     |  |  |

WDTCALL—Watchdog Timer Calibration Low Byte

The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload registers result in a one second timeout at room temperature and 3.3 V supply voltage. To use the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDTCALH and WDTL with WDTCALL.

# **Serialization Data**

### Table 99. Serial Number at 001C - 001F (S\_NUM)

| BITS      | 7                                               | 6     | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-----------|-------------------------------------------------|-------|-----|-----|-----|-----|-----|-----|--|--|

| FIELD     |                                                 | S_NUM |     |     |     |     |     |     |  |  |

| RESET     | U                                               | U     | U   | U   | U   | U   | UU  |     |  |  |

| R/W       | R/W                                             | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR      | Information Page Memory 001C-001F               |       |     |     |     |     |     |     |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |       |     |     |     |     |     |     |  |  |

S NUM—Serial Number Byte

The serial number is a unique four-byte binary value.

zilog |

Write Memory, Read Memory, Write Register, Read Register, Read Memory CRC, Step Instruction, Stuff Instruction, and Execute Instruction commands.

DBG  $\leftarrow$  03H DBG  $\rightarrow$  RuntimeCounter[15:8] DBG  $\rightarrow$  RuntimeCounter[7:0]

• Write OCD Control Register (04H)—The Write OCD Control Register command writes the data that follows to the OCDCTL register. When the Flash Read Protect Option Bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0 and the only method of returning the device to normal operating mode is to reset the device.

DBG  $\leftarrow$  04H DBG  $\leftarrow$  OCDCTL[7:0]

• **Read OCD Control Register (05H)**—The Read OCD Control Register command reads the value of the OCDCTL register.

```

DBG \leftarrow 05H

DBG \rightarrow OCDCTL[7:0]

```

• Write Program Counter (06H)—The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter (PC). If the device is not in DE-BUG mode or if the Flash Read Protect Option bit is enabled, the Program Counter (PC) values are discarded.

```

DBG ← 06H

DBG ← ProgramCounter[15:8]

DBG ← ProgramCounter[7:0]

```

• **Read Program Counter (07H)**—The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

• Write Register (08H)—The Write Register command writes data to the Register File. Data can be written 1–256 bytes at a time (256 bytes can be written by setting size to 0). If the device is not in DEBUG mode, the address and data values are discarded. If the Flash Read Protect Option bit is enabled, only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

zilog <sub>201</sub>

### Table 114. Notational Shorthand

| Notation | Description                    | Operand | Range                                                                                                                        |  |  |  |  |  |

|----------|--------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| b        | Bit                            | b       | b represents a value from 0 to 7 (000B to 111B)                                                                              |  |  |  |  |  |

| СС       | Condition Code                 | _       | Refer to Condition Codes section in the <i>eZ8 CPU Core User Manual (UM0128)</i> .                                           |  |  |  |  |  |

| DA       | Direct Address                 | Addrs   | Addrs. represents a number in the range of 0000H to FFFFH                                                                    |  |  |  |  |  |

| ER       | Extended Addressing Register   | Reg     | Reg. represents a number in the range of 000H to FFFH                                                                        |  |  |  |  |  |

| IM       | Immediate Data                 | #Data   | Data is a number between 00H to FFH                                                                                          |  |  |  |  |  |

| lr       | Indirect Working Register      | @Rn     | n = 0–15                                                                                                                     |  |  |  |  |  |

| IR       | Indirect Register              | @Reg    | Reg. represents a number in the range of 00H to FFH                                                                          |  |  |  |  |  |

| Irr      | Indirect Working Register Pair | @RRp    | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                             |  |  |  |  |  |

| IRR      | Indirect Register Pair         | @Reg    | Reg. represents an even number in the range 00H to FEH                                                                       |  |  |  |  |  |

| р        | Polarity                       | р       | Polarity is a single bit binary value of either 0B or 1B.                                                                    |  |  |  |  |  |

| r        | Working Register               | Rn      | n = 0 – 15                                                                                                                   |  |  |  |  |  |

| R        | Register                       | Reg     | Reg. represents a number in the range of 00H to FFH                                                                          |  |  |  |  |  |

| RA       | Relative Address               | Х       | X represents an index in the range of +127 to –<br>128 which is an offset relative to the address of<br>the next instruction |  |  |  |  |  |

| rr       | Working Register Pair          | RRp     | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                             |  |  |  |  |  |

| RR       | Register Pair                  | Reg     | Reg. represents an even number in the range of 00H to FEH                                                                    |  |  |  |  |  |

| Vector   | Vector Address                 | Vector  | Vector represents a number in the range of 00H to FFH                                                                        |  |  |  |  |  |

| X        | Indexed                        | #Index  | The register or register pair to be indexed is<br>offset by the signed Index value (#Index) in a<br>+127 to<br>-128 range.   |  |  |  |  |  |

Table 115 lists additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

207

### Table 123. Rotate and Shift Instructions (Continued)

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| SRA      | dst      | Shift Right Arithmetic |

| SRL      | dst      | Shift Right Logical    |

| SWAP     | dst      | Swap Nibbles           |

# eZ8 CPU Instruction Summary

Table 124 summarizes the eZ8 CPU instructions. The table identifies the addressing modes employed by the instruction, the effect upon the Flags register, the number of CPU clock cycles required for the instruction fetch, and the number of CPU clock cycles required for the instruction.

| Assembly        | Symbolic                                                   | Addres        | s Mode   | Opcode(s) |   |          | FI | ags       |   |   | Fetch | Instr. |

|-----------------|------------------------------------------------------------|---------------|----------|-----------|---|----------|----|-----------|---|---|-------|--------|

| Mnemonic        | Operation                                                  | dst           | src      | (Hex)     | С | Ζ        | S  | ۷         | D | Н |       | Cycles |

| ADC dst, src    | $dst \gets dst + src + C$                                  | r             | r        | 12        | * | *        | *  | *         | 0 | * | 2     | 3      |

|                 |                                                            | r             | lr       | 13        | - |          |    |           |   |   | 2     | 4      |

|                 |                                                            | R             | R        | 14        | - |          |    |           |   |   | 3     | 3      |

|                 |                                                            | R             | IR       | 15        | - |          |    |           |   |   | 3     | 4      |

|                 |                                                            | R             | IM       | 16        | - |          |    |           |   |   | 3     | 3      |

|                 |                                                            | IR            | IM       | 17        | - |          |    |           |   |   | 3     | 4      |

| ADCX dst, src   | $dst \gets dst + src + C$                                  | ER            | ER       | 18        | * | *        | *  | *         | 0 | * | 4     | 3      |

|                 |                                                            | ER            | IM       | 19        | - |          |    |           |   |   | 4     | 3      |

| ADD dst, src    | $dst \gets dst + src$                                      | r             | r        | 02        | * | *        | *  | *         | 0 | * | 2     | 3      |

|                 |                                                            | r             | lr       | 03        | - |          |    |           |   |   | 2     | 4      |

|                 |                                                            | R             | R        | 04        | - |          |    |           |   |   | 3     | 3      |

|                 |                                                            | R             | IR       | 05        | - |          |    |           |   |   | 3     | 4      |

|                 |                                                            | R             | IM       | 06        | - |          |    |           |   |   | 3     | 3      |

|                 |                                                            | IR            | IM       | 07        | - |          |    |           |   |   | 3     | 4      |

| ADDX dst, src   | $dst \gets dst + src$                                      | ER            | ER       | 08        | * | *        | *  | *         | 0 | * | 4     | 3      |

|                 |                                                            | ER            | IM       | 09        | - |          |    |           |   |   | 4     | 3      |

| Flags Notation: | * = Value is a function<br>– = Unaffected<br>X = Undefined | of the result | of the o | peration. |   | Re<br>Se |    | to (<br>1 | C |   |       |        |

Table 124. eZ8 CPU Instruction Summary

**z**ilog<sup>°</sup>

|   |             |              |                     |                  |                     |               | Lo           | ower Ni       | bble (He        | x)             |              |            |             |             |           |           |

|---|-------------|--------------|---------------------|------------------|---------------------|---------------|--------------|---------------|-----------------|----------------|--------------|------------|-------------|-------------|-----------|-----------|

|   | 0           | 1            | 2                   | 3                | 4                   | 5             | 6            | 7             | 8               | 9              | А            | В          | С           | D           | Е         | F         |

| • | 1.1         | 2.2          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            | 2.3          | 2.2        | 2.2         | 3.2         | 1.2       | 1.2       |

| 0 | BRK         | SRP<br>IM    | <b>ADD</b><br>r1,r2 | ADD<br>r1,lr2    | <b>ADD</b><br>R2,R1 | ADD<br>IR2,R1 | ADD<br>R1,IM | ADD<br>IR1,IM | ADDX<br>ER2,ER1 | ADDX<br>IM,ER1 | DJNZ<br>r1,X | JR<br>cc,X | LD<br>r1,IM | JP<br>cc,DA | INC<br>r1 | NO        |

|   | 2.2         | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            | ,            |            |             | 00,271      | 1         | See       |

| 1 | RLC         | RLC          | ADC                 | ADC              | ADC                 | ADC           | ADC          | ADC           | ADCX            | ADCX           |              |            |             |             |           | Орсо      |

|   | R1          | IR1          | r1,r2               | r1,lr2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           | Ma        |

|   | 2.2         | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1,        |

| 2 | INC<br>R1   | INC<br>IR1   | <b>SUB</b><br>r1,r2 | SUB<br>r1,lr2    | <b>SUB</b><br>R2,R1 | SUB<br>IR2,R1 | SUB<br>R1,IM | SUB<br>IR1,IM | SUBX<br>ER2,ER1 | SUBX<br>IM,ER1 |              |            |             |             |           | AT        |

|   | 2.2         | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           |           |

| 3 | DEC         | DEC          | SBC                 | SBC              | SBC                 | SBC           | SBC          | SBC           | SBCX            | SBCX           |              |            |             |             |           |           |

| - | R1          | IR1          | r1,r2               | r1,lr2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2         | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           |           |

| 4 | DA          | DA           | OR                  | OR               | OR                  | OR            | OR           | OR            | ORX             | ORX            |              |            |             |             |           |           |

|   | R1          | IR1          | r1,r2               | r1,Ir2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| 5 | 2.2<br>POP  | 2.3<br>POP   | 2.3<br>AND          | 2.4<br>AND       | 3.3<br>AND          | 3.4<br>AND    | 3.3<br>AND   | 3.4<br>AND    | 4.3<br>ANDX     | 4.3<br>ANDX    |              |            |             |             |           | 1.:<br>WE |

| 5 | R1          | IR1          | r1,r2               | r1,lr2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           | VVL       |

|   | 2.2         | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.:       |

| 6 | COM         | COM          | ТСМ                 | TCM              | TCM                 | TCM           | тсм          | TCM           | тсмх            | тсмх           |              |            |             |             |           | STO       |

|   | R1          | IR1          | r1,r2               | r1,lr2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2         | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.2       |

| 7 | PUSH        | PUSH         | ТМ                  | TM               | TM                  | TM            | ТМ           | ТМ            | TMX             | TMX            |              |            |             |             |           | HA        |

|   | R2          | IR2          | r1,r2               | r1,lr2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| 8 | 2.5<br>DECW | 2.6<br>DECW  | 2.5<br>LDE          | 2.9<br>LDEI      | 3.2<br>LDX          | 3.3<br>LDX    | 3.4<br>LDX   | 3.5<br>LDX    | 3.4<br>LDX      | 3.4<br>LDX     |              |            |             |             |           | 1.:<br>D  |

| 0 | RR1         | IRR1         | r1,Irr2             | lr1,lrr2         | r1,ER2              | Ir1,ER2       | IRR2,R1      | IRR2,IR1      | r1,rr2,X        | rr1,r2,X       |              |            |             |             |           | -         |

|   | 2.2         | 2.3          | 2.5                 | 2.9              | 3.2                 | 3.3           | 3.4          | 3.5           | 3.3             | 3.5            |              |            |             |             |           | 1.2       |

| 9 | RL          | RL           | LDE                 | LDEI             | LDX                 | LDX           | LDX          | LDX           | LEA             | LEA            |              |            |             |             |           | E         |

|   | R1          | IR1          | r2,Irr1             | lr2,lrr1         | r2,ER1              | Ir2,ER1       | R2,IRR1      | IR2,IRR1      | r1,r2,X         | rr1,rr2,X      |              |            |             |             |           |           |

|   | 2.5         | 2.6          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.4       |

| A | RR1         | INCW<br>IRR1 | CP                  | CP<br>r1,lr2     | CP<br>D2 D1         | CP            |              |               | CPX<br>ER2,ER1  |                |              |            |             |             |           | RE        |

|   | 2.2         |              | r1,r2<br>2.3        | 2.4              | R2,R1<br>3.3        | IR2,R1<br>3.4 | R1,IM<br>3.3 | IR1,IM<br>3.4 | 4.3             | IM,ER1<br>4.3  |              |            |             |             |           | 1.3       |

| в | CLR         | 2.3<br>CLR   | XOR                 | XOR              | XOR                 | XOR           | XOR          | XOR           | XORX            | XORX           |              |            |             |             |           | IRE       |

|   | R1          | IR1          | r1,r2               | r1,lr2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2         | 2.3          | 2.5                 | 2.9              | 2.3                 | 2.9           |              | 3.4           | 3.2             |                |              |            |             |             |           | 1.2       |

| С | RRC         | RRC          | LDC                 | LDCI             | JP                  | LDC           |              | LD            | PUSHX           |                |              |            |             |             |           | RC        |

|   | R1          | IR1          | r1,Irr2             | lr1,lrr2         | IRR1                | lr1,lrr2      |              | r1,r2,X       | ER2             |                |              |            |             |             |           |           |

|   | 2.2         | 2.3          | 2.5                 | 2.9              | 2.6                 | 2.2           | 3.3          | 3.4<br>LD     | 3.2<br>POPX     |                |              |            |             |             |           | 1.2<br>SC |

| D | SRA<br>R1   | IR1          | LDC<br>r2,Irr1      | LDCI<br>Ir2,Irr1 | IRR1                | BSWAP<br>R1   | DA           | r2,r1,X       | ER1             |                |              |            |             |             |           | 30        |

|   | 2.2         | 2.3          | 2.2                 | 2.3              | 3.2                 | 3.3           | 3.2          | 3.3           | 4.2             | 4.2            |              |            |             |             |           | 1.2       |

| Е | RR          | RR           | BIT                 | LD               | LD                  | LD            | LD           | LD            | LDX             | LDX            |              |            |             |             |           | cc        |

|   | R1          | IR1          | p,b,r1              | r1,Ir2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2         | 2.3          | 2.6                 | 2.3              | 2.8                 | 3.3           | 3.3          | 3.4           |                 |                |              | $\bot$     |             |             |           |           |

| F | SWAP        | SWAP         | TRAP                | LD               | MULT                | LD            | BTJ          | BTJ           |                 |                |              | V          |             |             |           |           |

|   | R1          | IR1          | Vector              | lr1,r2           | RR1                 | R2,IR1        | p,b,r1,X     | p,b,lr1,X     |                 |                | 1            | 1          | 1           | 1           | Ţ         |           |

Figure 31. First Opcode Map

Upper Nibble (Hex)

218

220

# zilog

# **Electrical Characteristics**

The data in this chapter is pre-qualification and pre-characterization and is subject to change. Additional electrical characteristics may be found in the individual chapters.

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 126 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                                      | Minimum | Maximum | Units | Notes |

|----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                 | -40     | +105    | °C    |       |

| Storage temperature                                            | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>             | -0.3    | +5.5    | V     | 1     |

|                                                                | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$               | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin            | -5      | +5      | μA    |       |

| Maximum output current from active output pin                  | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0 °C to 70 °C                |         |         |       |       |

| Total power dissipation                                        |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$               |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0 °C to 70 °C               |         |         |       |       |

| Total power dissipation                                        |         | 430     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub> |         | 120     | mA    |       |

#### Table 126. Absolute Maximum Ratings

|                           |                                                    | V <sub>DI</sub> | <sub>0</sub> = 2.7 V to 3 | 5.6 V    |       |                                                                  |

|---------------------------|----------------------------------------------------|-----------------|---------------------------|----------|-------|------------------------------------------------------------------|

|                           |                                                    |                 | Maximum <sup>2</sup>      |          |       |                                                                  |

| Symbol                    | Parameter                                          | Typical $^1$    | Std Temp                  | Ext Temp | Units | Conditions                                                       |

| I <sub>DD</sub> Stop      | Supply Current in STOP<br>Mode                     | 0.1             |                           |          | μA    | No peripherals enabled. All pins driven to $V_{DD}$ or $V_{SS}.$ |

| I <sub>DD</sub> Halt      | Supply Current in HALT                             | 35              | 55                        | 65       | μA    | 32 kHz                                                           |

|                           | Mode (with all peripherals disabled)               | 520             |                           |          | μA    | 5.5 MHz                                                          |

|                           | penpinenale aleases) -                             | 2.1             | 2.85                      | 2.85     | mA    | 20 MHz                                                           |

| I <sub>DD</sub>           | Supply Current in                                  | 2.8             |                           |          | mA    | 32 kHz                                                           |

|                           | ACTIVE Mode (with all peripherals disabled)        | 4.5             | 5.2                       | 5.2      | mA    | 5.5 MHz                                                          |

|                           |                                                    | 5.5             | 6.5                       | 6.5      | mA    | 10 MHz                                                           |

|                           | -                                                  | 7.9             | 11.5                      | 11.5     | mA    | 20 MHz                                                           |

| I <sub>DD</sub> WDT       | Watchdog Timer Supply<br>Current                   | 0.9             | 1.0                       | 1.1      | μA    |                                                                  |

| I <sub>DD</sub>           | Crystal Oscillator                                 | 40              |                           |          | μA    | 32 kHz                                                           |

| XTAL                      | Supply Current                                     | 230             |                           |          | μA    | 4 MHz                                                            |

|                           | -                                                  | 760             |                           |          | μA    | 20 MHz                                                           |

| I <sub>DD</sub> IPO       | Internal Precision<br>Oscillator Supply<br>Current | 350             | 500                       | 550      | μA    |                                                                  |

| I <sub>DD</sub> VBO       | Low-Voltage Detect                                 | 50              |                           |          | μA    | For 20-/28-pin devices<br>(VBO only); See Notes 4                |

|                           | Supply Current                                     |                 |                           |          |       | For 8-pin devices; See<br>Notes 4                                |

| I <sub>DD</sub> ADC       | Analog to Digital                                  | 2.8             | 3.1                       | 3.2      | mA    | 32 kHz                                                           |

|                           | Converter Supply<br>Current (with External         | 3.1             | 3.6                       | 3.7      | mA    | 5.5 MHz                                                          |

|                           | Reference)                                         | 3.3             | 3.7                       | 3.8      | mA    | 10 MHz                                                           |

|                           | -                                                  | 3.7             | 4.2                       | 4.3      | mA    | 20 MHz                                                           |

| I <sub>DD</sub><br>ADCRef | ADC Internal Reference<br>Supply Current           | 0               |                           |          | μA    | See Notes 4                                                      |

| I <sub>DD</sub> CMP       | Comparator supply<br>Current                       | 150             | 180                       | 190      | μA    | See Notes 4                                                      |

### Table 128. Power Consumption

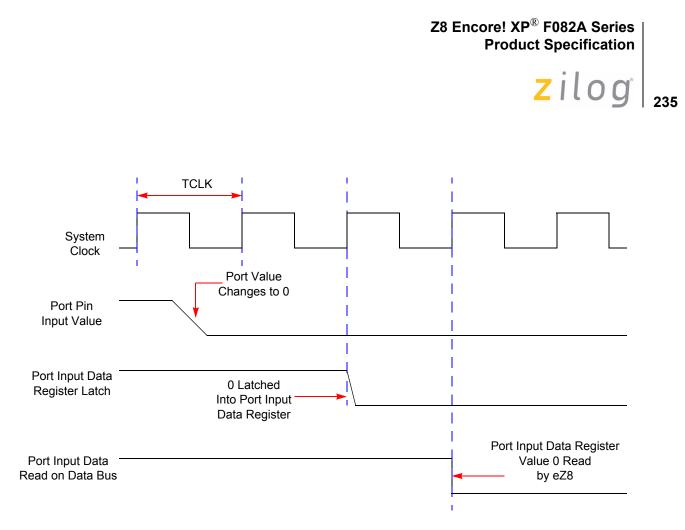

Figure 34. Port Input Sample Timing

|                     |                                                                                                          | Delay (ns) |         |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------|------------|---------|--|--|

| Parameter           | Abbreviation                                                                                             | Minimum    | Maximum |  |  |

| T <sub>S_PORT</sub> | Port Input Transition to XIN Rise Setup Time (Not pictured)                                              | 5          | _       |  |  |

| T <sub>H_PORT</sub> | XIN Rise to Port Input Transition Hold Time (Not pictured)                                               | 0          | -       |  |  |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to ensure Stop Mode<br>Recovery<br>(for GPIO Port Pins enabled as SMR sources) | 1 µs       |         |  |  |

265

L LD 205 LDC 205 LDCI 204, 205 LDE 205 LDEI 204, 205 LDX 205 LEA 205 load 205 load constant 204 load constant to/from program memory 205 load constant with auto-increment addresses 205 load effective address 205 load external data 205 load external data to/from data memory and auto-increment addresses 204 load external to/from data memory and auto-increment addresses 205 load using extended addressing 205 logical AND 205 logical AND/extended addressing 205 logical exclusive OR 206 logical exclusive OR/extended addressing 206 logical instructions 205 logical OR 205 logical OR/extended addressing 206 low power modes 33

# Μ

master interrupt enable 57 memory data 17 program 15 mode CAPTURE 85, 86 CAPTURE/COMPARE 85 CONTINUOUS 84 COUNTER 84 GATED 85 ONE-SHOT 84 PWM 85 modes 85 MULT 203 multiply 203 multiprocessor mode, UART 103

# Ν

NOP (no operation) 204 notation b 201 cc 201 DA 201 ER 201 IM 201 IR 201 Ir 201 IRR 201 Irr 201 p 201 R 201 r 201 RA 201 RR 201 rr 201 vector 201 X 201 notational shorthand 201

### O OCD

architecture 173 auto-baud detector/generator 176 baud rate limits 177 block diagram 173 breakpoints 178 commands 179 control register 184 data format 176 DBG pin to RS-232 Interface 174 debug mode 175 debugger break 206 interface 174 serial errors 177 status register 185