Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 128 x 8                                                   |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f041asb020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Flash Sector Protect Register       1         Flash Frequency High and Low Byte Registers       1                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Flash Option Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53                                                                               |

| Operation11Option Bit Configuration By Reset11Option Bit Types11Reading the Flash Information Page11Flash Option Bit Control Register Definitions11Trim Bit Address Register11Trim Bit Data Register11Flash Option Bit Address Space11Flash Program Memory Address 0000H11Flash Program Memory Address 0001H11Trim Bit Address Space11Trim Bit Address 0000H11Trim Bit Address 0000H11Trim Bit Address 0000H11Trim Bit Address 0001H11Trim Bit Address 0002H11Trim Bit Address 0003H11Trim Bit Address 0004H11 | 53<br>54<br>55<br>55<br>56<br>56<br>56<br>58<br>58<br>58<br>58<br>59<br>59<br>59 |

| Zilog Calibration Data       10         ADC Calibration Data       10         Temperature Sensor Calibration Data       10         Watchdog Timer Calibration Data       10         Serialization Data       10         Randomized Lot Identifier       10                                                                                                                                                                                                                                                     | 61<br>64<br>64<br>65<br>66                                                       |

| Non-Volatile Data Storage 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| NVDS Code Interface       10         Byte Write       10         Byte Read       11                                                                                                                                                                                                                                                                                                                                                                                                                            | 69<br>70<br>71                                                                   |

| On-Chip Debugger1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 74<br>74                                                                         |

# **Universal Asynchronous Receiver/Transmitter**

The full-duplex universal asynchronous receiver/transmitter (UART) is included in all Z8 Encore! XP package types. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

#### Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE and COMPARE, PWM SINGLE OUTPUT and PWM DUAL OUTPUT modes.

## General-Purpose Input/Output

The Z8 Encore! XP F082A Series features 6 to 25 port pins (Ports A–D) for general- purpose input/output (GPIO). The number of GPIO pins available is a function of package, and each pin is individually programmable. 5 V tolerant input pins are available on all I/Os on 8-pin devices and most I/Os on other package types.

# **Direct LED Drive**

The 20- and 28-pin devices support controlled current sinking output pins capable of driving LEDs without the need for a current limiting resistor. These LED drivers are independently programmable to four different intensity levels.

## **Flash Controller**

The Flash Controller programs and erases Flash memory. The Flash Controller supports several protection mechanisms against accidental program and erasure, as well as factory serialization and read protection.

## Non-Volatile Data Storage

The non-volatile data storage (NVDS) uses a hybrid hardware/software scheme to implement a byte programmable data memory and is capable of over 100,000 write cycles.

**Note:** Devices with 8 KB Flash memory do not include the NVDS feature.

# Table 2. Signal Descriptions (Continued)

| Signal Mnemonic  | I/O      | Description                                                                       |

|------------------|----------|-----------------------------------------------------------------------------------|

| Power Supply     |          |                                                                                   |

| V <sub>DD</sub>  | Ι        | Digital Power Supply.                                                             |

| AV <sub>DD</sub> | Ι        | Analog Power Supply.                                                              |

| V <sub>SS</sub>  | I        | Digital Ground.                                                                   |

| AV <sub>SS</sub> | Ι        | Analog Ground.                                                                    |

| Note: The AV     | Vee siar | nals are available only in 28-pin packages with ADC. They are replaced by PB6 and |

**Note:** The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

# **Pin Characteristics**

Table 3 describes the characteristics for each pin available on the Z8 Encore! XP F082A Series 20- and 28-pin devices. Data in Table 3 is sorted alphabetically by the pin symbol mnemonic.

Table 4 on page 14 provides detailed information about the characteristics for each pin available on the Z8 Encore! XP F082A Series 8-pin devices.

Note:

All six I/O pins on the 8-pin packages are 5 V-tolerant (unless the pull-up devices are enabled). The column in Table 3 below describes 5 V-tolerance for the 20- and 28-pin packages only.

#### Table 3. Pin Characteristics (20- and 28-pin Devices)

| Symbol<br>Mnemonic | Direction | Reset<br>Direction | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal Pull-<br>up<br>or Pull-down | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output | 5 V<br>Tolerance                        |

|--------------------|-----------|--------------------|---------------------------------------|--------------------|--------------------------------------|------------------------------|----------------------|-----------------------------------------|

| AVDD               | N/A       | N/A                | N/A                                   | N/A                | N/A                                  | N/A                          | N/A                  | N/A                                     |

| AVSS               | N/A       | N/A                | N/A                                   | N/A                | N/A                                  | N/A                          | N/A                  | NA                                      |

| DBG                | I/O       | I                  | N/A                                   | Yes                | Yes                                  | Yes                          | Yes                  | No                                      |

| PA[7:0]            | I/O       | I                  | N/A                                   | Yes                | Programmable<br>Pull-up              | Yes                          | Yes,<br>Programmable | PA[7:2]<br>unless<br>pullups<br>enabled |

| PB[7:0]            | I/O       | I                  | N/A                                   | Yes                | Programmable<br>Pull-up              | Yes                          | Yes,<br>Programmable | PB[7:6]<br>unless<br>pullups<br>enabled |

function). (Push-pull output)

1 = The source current for the associated pin is disabled (open-drain mode).

## Port A–D High Drive Enable Sub-Registers

The Port A–D High Drive Enable sub-register (Table 22) is accessed through the Port A–D Control register by writing 04H to the Port A–D Address register. Setting the bits in the Port A–D High Drive Enable sub-registers to 1 configures the specified port pins for high current output drive operation. The Port A–D High Drive Enable sub-register affects the pins directly and, as a result, alternate functions are also affected.

Table 22. Port A–D High Drive Enable Sub-Registers (PxHDE)

| BITS  | 7        | 6                                                                                     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |  |

|-------|----------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|--|--|

| FIELD | PHDE7    | PHDE6                                                                                 | PHDE5 | PHDE4 | PHDE3 | PHDE2 | PHDE1 | PHDE0 |  |  |  |

| RESET | 0        | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |

| R/W   | R/W      | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |  |

| ADDR  | lf 04H i | If 04H in Port A–D Address Register, accessible through the Port A–D Control Register |       |       |       |       |       |       |  |  |  |

PHDE[7:0]—Port High Drive Enabled

0 = The Port pin is configured for standard output current drive.

1 = The Port pin is configured for high output current drive.

## Port A–D Stop Mode Recovery Source Enable Sub-Registers

The Port A–D Stop Mode Recovery Source Enable sub-register (Table 23) is accessed through the Port A–D Control register by writing 05H to the Port A–D Address register. Setting the bits in the Port A–D Stop Mode Recovery Source Enable sub-registers to 1 configures the specified Port pins as a Stop Mode Recovery source. During STOP mode, any logic transition on a Port pin enabled as a Stop Mode Recovery source initiates Stop Mode Recovery.

| BITS  | 7        | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|-------|----------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|

| FIELD | PSMRE7   | PSMRE6                                                                                | PSMRE5 | PSMRE4 | PSMRE3 | PSMRE2 | PSMRE1 | PSMRE0 |  |  |

| RESET | 0        | 0                                                                                     | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| R/W   | R/W      | R/W                                                                                   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| ADDR  | lf 05H i | If 05H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |        |  |  |

PSMRE[7:0]—Port Stop Mode Recovery Source Enabled

0 = The Port pin is not configured as a Stop Mode Recovery source. Transitions on this pin

# Table 31. LED Drive Level Low Register (LEDLVLL)

| BITS  | 7            | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|--------------|------|-----|-----|-----|-----|-----|-----|--|--|

| FIELD | LEDLVLL[7:0] |      |     |     |     |     |     |     |  |  |

| RESET | 0            | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W   | R/W          | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR  |              | F84H |     |     |     |     |     |     |  |  |

LEDLVLL[7:0]—LED Level Low Bit

{LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin.

00 = 3 mA01 = 7 mA10 = 13 mA

11 = 20 mA

# 56

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source                                                                                                              |

|----------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Highest  | 0002H                               | Reset (not an interrupt)                                                                                                              |

|          | 0004H                               | Watchdog Timer (see Watchdog Timer on page 91)                                                                                        |

|          | 003AH                               | Primary Oscillator Fail Trap (not an interrupt)                                                                                       |

|          | 003CH                               | Watchdog Oscillator Fail Trap (not an interrupt)                                                                                      |

|          | 0006H                               | Illegal Instruction Trap (not an interrupt)                                                                                           |

|          | 0008H                               | Reserved                                                                                                                              |

|          | 000AH                               | Timer 1                                                                                                                               |

|          | 000CH                               | Timer 0                                                                                                                               |

|          | 000EH                               | UART 0 receiver                                                                                                                       |

|          | 0010H                               | UART 0 transmitter                                                                                                                    |

|          | 0012H                               | Reserved                                                                                                                              |

|          | 0014H                               | Reserved                                                                                                                              |

|          | 0016H                               | ADC                                                                                                                                   |

|          | 0018H                               | Port A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop<br>Mode Recovery, and Low Voltage Detection on page 23) |

|          | 001AH                               | Port A Pin 6, selectable rising or falling input edge or Comparator Output                                                            |

|          | 001CH                               | Port A Pin 5, selectable rising or falling input edge                                                                                 |

|          | 001EH                               | Port A Pin 4, selectable rising or falling input edge                                                                                 |

|          | 0020H                               | Port A Pin 3, selectable rising or falling input edge                                                                                 |

|          | 0022H                               | Port A Pin 2, selectable rising or falling input edge                                                                                 |

|          | 0024H                               | Port A Pin 1, selectable rising or falling input edge                                                                                 |

|          | 0026H                               | Port A Pin 0, selectable rising or falling input edge                                                                                 |

|          | 0028H                               | Reserved                                                                                                                              |

|          | 002AH                               | Reserved                                                                                                                              |

|          | 002CH                               | Reserved                                                                                                                              |

|          | 002EH                               | Reserved                                                                                                                              |

|          | 0030H                               | Port C Pin 3, both input edges                                                                                                        |

|          | 0032H                               | Port C Pin 2, both input edges                                                                                                        |

# Table 32. Trap and Interrupt Vectors in Order of Priority

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source       |

|----------|-------------------------------------|--------------------------------|

|          | 0034H                               | Port C Pin 1, both input edges |

| Lowest   | 0036H                               | Port C Pin 0, both input edges |

|          | 0038H                               | Reserved                       |

#### Table 32. Trap and Interrupt Vectors in Order of Priority (Continued)

# Architecture

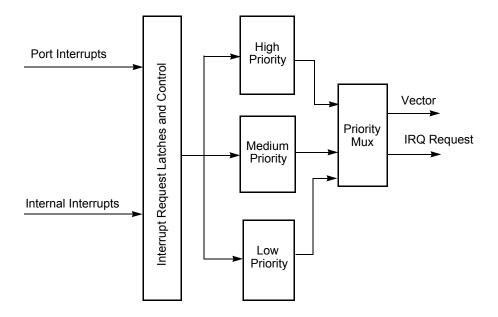

Figure 8 displays the interrupt controller block diagram.

Figure 8. Interrupt Controller Block Diagram

# Operation

# **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control register globally enables and disables interrupts.

zilog

**Caution:** To avoid re-triggerings of the Watchdog Timer interrupt after exiting the associated interrupt service routine, it is recommended that the service routine continues to read from the RSTSTAT register until the WDT bit is cleared as given in the following coding sample:

CLEARWDT: LDX r0, RSTSTAT ; read reset status register to clear wdt bit BTJNZ 5, r0, CLEARWDT ; loop until bit is cleared

# **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap, and the Watchdog Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

# **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) register (Table 33) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 0 register to determine if any interrupt requests are pending.

| BITS  | 7        | 6    | 5   | 4            | 3     | 2        | 1        | 0    |  |  |

|-------|----------|------|-----|--------------|-------|----------|----------|------|--|--|

| FIELD | Reserved | T1I  | TOI | <b>U0RXI</b> | U0TXI | Reserved | Reserved | ADCI |  |  |

| RESET | 0        | 0    | 0   | 0            | 0     | 0        | 0        | 0    |  |  |

| R/W   | R/W      | R/W  | R/W | R/W          | R/W   | R/W      | R/W      | R/W  |  |  |

| ADDR  |          | FC0H |     |              |       |          |          |      |  |  |

Table 33. Interrupt Request 0 Register (IRQ0)

Reserved—Must be 0.

T1I—Timer 1 Interrupt Request

- 0 = No interrupt request is pending for Timer 1.

- 1 = An interrupt request from Timer 1 is awaiting service.

T0I—Timer 0 Interrupt Request

- 0 = No interrupt request is pending for Timer 0.

- 1 = An interrupt request from Timer 0 is awaiting service.

Follow the steps below for configuring a timer for COUNTER mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for COUNTER mode.

- Select either the rising edge or falling edge of the Timer Input signal for the count. This selection also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER mode. After the first timer Reload in COUNTER mode, counting always begins at the reset value of 0001H. In COUNTER mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer.

In COUNTER mode, the number of Timer Input transitions since the timer start is given by the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value-Start Value

#### **COMPARATOR COUNTER Mode**

In COMPARATOR COUNTER mode, the timer counts input transitions from the analog comparator output. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the comparator output signal. In COMPAR-ATOR COUNTER mode, the prescaler is disabled.

**Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the comparator output signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

After reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

zilog

| BITS  | 7       | 6    | 5    | 4   | 3   | 2   | 1   | 0   |  |

|-------|---------|------|------|-----|-----|-----|-----|-----|--|

| FIELD | INFO_EN |      | PAGE |     |     |     |     |     |  |

| RESET | 0       | 0    | 0    | 0   | 0   | 0   | 0   | 0   |  |

| R/W   | R/W     | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W |  |

| ADDR  |         | FF9H |      |     |     |     |     |     |  |

#### Table 80. Flash Page Select Register (FPS)

INFO\_EN—Information Area Enable

0 = Information Area us not selected.

1 = Information Area is selected. The Information Area is mapped into the Program Memory address space at addresses FE00H through FFFFH.

PAGE—Page Select

This 7-bit field identifies the Flash memory page for Page Erase and page unlocking. Program Memory Address[15:9] = PAGE[6:0]. For the Z8F08xx devices, the upper 3 bits must be zero. For the Z8F04xx devices, the upper 4 bits must be zero. For Z8F02xx devices, the upper 5 bits must always be 0. For the Z8F01xx devices, the upper 6 bits must always be 0.

# **Flash Sector Protect Register**

The Flash Sector Protect (FPROT) register is shared with the Flash Page Select Register. When the Flash Control Register is written with 73H followed by 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the 8 available Flash memory sectors to be protected. The reset state of each Sector Protect bit is an unprotected state. After a sector is protected by setting its corresponding register bit, it cannot be unprotected (the register bit cannot be cleared) without powering down the device.

| Table 81. Flash S | ector Protect | Register ( | FPROI) |  |

|-------------------|---------------|------------|--------|--|

|                   |               |            |        |  |

| BITS  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|--|--|

| FIELD | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |  |  |

| RESET | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| R/W   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| ADDR  |        | FF9H   |        |        |        |        |        |        |  |  |

**z**ilog<sup>°</sup>

# **Option Bit Types**

#### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. User access to these bits has been provided because these locations contain application-specific device configurations. The information contained here is lost when page 0 of the program memory is erased.

#### **Trim Option Bits**

The trim option bits are contained in the information page of the Flash memory. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered. Program Memory may be erased without endangering these values. It is possible to alter working values of these bits by accessing the Trim Bit Address and Data Registers, but these working values are lost after a power loss or any other reset event.

There are 32 bytes of trim data. To modify one of these values the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data register returns the working value of the target trim data byte.

The trim address range is from information address 20-3F only. The remainder of the information page is not accessible through the trim bit address and data registers.

## **Calibration Option Bits**

The calibration option bits are also contained in the information page. These bits are factory programmed values intended for use in software correcting the device's analog performance. To read these values, the user code must employ the LDC instruction to access the information area of the address space as defined in See Flash Information Area on page 17.

#### **Serialization Bits**

As an optional feature, Zilog<sup>®</sup> is able to provide factory-programmed serialization. For serialized products, the individual devices are programmed with unique serial numbers. These serial numbers are binary values, four bytes in length. The numbers increase in size with each device, but gaps in the serial sequence may exist.

These serial numbers are stored in the Flash information page (see Reading the Flash Information Page on page 155 and Serialization Data on page 165 for more details) and are unaffected by mass erasure of the device's Flash memory.

Note:

168

If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

DBG  $\leftarrow$  12H DBG  $\leftarrow$  1-5 byte opcode

# **On-Chip Debugger Control Register Definitions**

# **OCD Control Register**

The OCD Control register controls the state of the On-Chip Debugger. This register is used to enter or exit DEBUG mode and to enable the BRK instruction. It can also reset the Z8 Encore! XP<sup>®</sup> F082A Series device.

A reset and stop function can be achieved by writing \$1H to this register. A reset and go function can be achieved by writing \$1H to this register. If the device is in DEBUG mode, a run function can be implemented by writing \$0H to this register.

# Table 106. OCD Control Register (OCDCTL)

| BITS  | 7       | 6     | 5      | 4 | 3   | 2 | 1 | 0   |

|-------|---------|-------|--------|---|-----|---|---|-----|

| FIELD | DBGMODE | BRKEN | DBGACK |   | RST |   |   |     |

| RESET | 0       | 0     | 0      | 0 | 0   | 0 | 0 | 0   |

| R/W   | R/W     | R/W   | R/W    | R | R   | R | R | R/W |

## DBGMODE—DEBUG Mode

The device enters DEBUG mode when this bit is 1. When in DEBUG mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is automatically set when a BRK instruction is decoded and Breakpoints are enabled. If the Flash Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device. It cannot be written to 0.

0 = The Z8 Encore! XP F082A Series device is operating in NORMAL mode.

1 = The Z8 Encore! XP F082A Series device is in DEBUG mode.

## BRKEN—Breakpoint Enable

This bit controls the behavior of the BRK instruction (opcode 00H). By default, Breakpoints are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1, when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL register is automatically set to 1.

0 = Breakpoints are disabled.

1 = Breakpoints are enabled.

204

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| ТСМ      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |

Table 118. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-Increment Addresses       |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

# Table 119. CPU Control Instructions

| Mnemonic | Operands | Instruction           |

|----------|----------|-----------------------|

| ATM      | _        | Atomic Execution      |

| CCF      | _        | Complement Carry Flag |

| DI       | _        | Disable Interrupts    |

| EI       | _        | Enable Interrupts     |

| HALT     | _        | Halt Mode             |

| NOP      | _        | No Operation          |

| RCF      | _        | Reset Carry Flag      |

**z**ilog<sup>°</sup>

| 2 | n | 0 |

|---|---|---|

| 4 | υ | 3 |

| Assembly        | Symbolic                                                                                         | Addres        | s Mode   | Opcode(s) |   |          | Fla | ags | Fetch | Instr. |        |   |

|-----------------|--------------------------------------------------------------------------------------------------|---------------|----------|-----------|---|----------|-----|-----|-------|--------|--------|---|

| Mnemonic        | Operation                                                                                        | dst           | src      | (Hex)     | С | Ζ        | S   | ۷   | D     | Н      | Cycles |   |

| COM dst         | $dst \gets \simdst$                                                                              | R             |          | 60        | - | *        | *   | 0   | -     | -      | 2      | 2 |

|                 |                                                                                                  | IR            |          | 61        | - |          |     |     |       |        | 2      | 3 |

| CP dst, src     | dst - src                                                                                        | r             | r        | A2        | * | *        | *   | *   | -     | -      | 2      | 3 |

|                 |                                                                                                  | r             | lr       | A3        | - |          |     |     |       |        | 2      | 4 |

|                 |                                                                                                  | R             | R        | A4        | - |          |     |     |       |        | 3      | 3 |

|                 |                                                                                                  | R             | IR       | A5        | - |          |     |     |       |        | 3      | 4 |

|                 |                                                                                                  | R             | IM       | A6        | - |          |     |     |       |        | 3      | 3 |

|                 |                                                                                                  | IR            | IM       | A7        | - |          |     |     |       |        | 3      | 4 |

| CPC dst, src    | dst - src - C                                                                                    | r             | r        | 1F A2     | * | *        | *   | *   | -     | -      | 3      | 3 |

|                 |                                                                                                  | r             | lr       | 1F A3     | - |          |     |     |       |        | 3      | 4 |

|                 |                                                                                                  | R             | R        | 1F A4     | - |          |     |     |       |        | 4      | 3 |

|                 |                                                                                                  | R             | IR       | 1F A5     | - |          |     |     |       |        | 4      | 4 |

|                 |                                                                                                  | R             | IM       | 1F A6     | - |          |     |     |       |        | 4      | 3 |

|                 |                                                                                                  | IR            | IM       | 1F A7     | - |          |     |     |       |        | 4      | 4 |

| CPCX dst, src   | dst - src - C                                                                                    | ER            | ER       | 1F A8     | * | *        | *   | *   | _     | _      | 5      | 3 |

|                 |                                                                                                  | ER            | IM       | 1F A9     | - |          |     |     |       |        | 5      | 3 |

| CPX dst, src    | dst - src                                                                                        | ER            | ER       | A8        | * | *        | *   | *   | _     | _      | 4      | 3 |

|                 |                                                                                                  | ER            | IM       | A9        | - |          |     |     |       |        | 4      | 3 |

| DA dst          | $dst \gets DA(dst)$                                                                              | R             |          | 40        | * | *        | *   | Х   | _     | _      | 2      | 2 |

|                 |                                                                                                  | IR            |          | 41        | - |          |     |     |       |        | 2      | 3 |

| DEC dst         | $dst \gets dst \text{ - } 1$                                                                     | R             |          | 30        | _ | *        | *   | *   | _     | _      | 2      | 2 |

|                 |                                                                                                  | IR            |          | 31        | - |          |     |     |       |        | 2      | 3 |

| DECW dst        | $dst \gets dst \text{ - } 1$                                                                     | RR            |          | 80        | _ | *        | *   | *   | _     | _      | 2      | 5 |

|                 |                                                                                                  | IRR           |          | 81        | - |          |     |     |       |        | 2      | 6 |

| DI              | $IRQCTL[7] \leftarrow 0$                                                                         |               |          | 8F        | _ | _        | _   | _   | _     | _      | 1      | 2 |

| DJNZ dst, RA    | $\begin{array}{l} dst \leftarrow dst - 1 \\ if \ dst \neq 0 \\ PC \leftarrow PC + X \end{array}$ | r             |          | 0A-FA     | _ | _        | _   | _   | _     | _      | 2      | 3 |

| EI              | $IRQCTL[7] \leftarrow 1$                                                                         |               |          | 9F        | _ | -        | _   | _   | -     | -      | 1      | 2 |

| Flags Notation: | * = Value is a function<br>– = Unaffected<br>X = Undefined                                       | of the result | of the o | peration. |   | Re<br>Se |     |     | )     |        |        |   |

# Table 124. eZ8 CPU Instruction Summary (Continued)

zilog

#### 22

## Table 126. Absolute Maximum Ratings (Continued)

| Parameter                                        | Minimum Maximum | Units | Notes |

|--------------------------------------------------|-----------------|-------|-------|

| 28-pin Packages Maximum Ratings at 0 °C to 70 °C |                 |       |       |

| Total power dissipation                          | 450             | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$ | 125             | mA    |       |

|                                                  |                 |       |       |

Operating temperature is specified in DC Characteristics.

This voltage applies to all pins except the following: V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1). On the 8-pin packages, this applies to all pins but V<sub>DD</sub>.

2. This voltage applies to pins on the 20-/28-pin packages supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1).

# **DC Characteristics**

Table 127 lists the DC characteristics of the Z8 Encore!  $XP^{\mathbb{R}}$  F082A Series products. All voltages are referenced to  $V_{SS}$ , the primary system ground.

| Table 127. DC Characteristics |  |

|-------------------------------|--|

|-------------------------------|--|

|                  |                              |                     | 40 °C to +<br>therwise | 105 °C<br>specified) |       |                                                                                                                                                              |

|------------------|------------------------------|---------------------|------------------------|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                    | Minimum             | Typical                | Maximum              | Units | Conditions                                                                                                                                                   |

| V <sub>DD</sub>  | Supply Voltage               | 2.7                 | _                      | 3.6                  | V     |                                                                                                                                                              |

| V <sub>IL1</sub> | Low Level Input<br>Voltage   | -0.3                | _                      | 0.3*V <sub>DD</sub>  | V     |                                                                                                                                                              |

| V <sub>IH1</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | 5.5                  | V     | For all input pins without analog<br>or oscillator function. For all<br>signal pins on the 8-pin devices.<br>Programmable pull-ups must<br>also be disabled. |

| V <sub>IH2</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | V <sub>DD</sub> +0.3 | V     | For those pins with analog or<br>oscillator function (20-/28-pin<br>devices only), or when<br>programmable pull-ups are<br>enabled.                          |

| V <sub>OL1</sub> | Low Level Output<br>Voltage  | -                   | -                      | 0.4                  | V     | I <sub>OL</sub> = 2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                               |

| V <sub>OH1</sub> | High Level Output<br>Voltage | 2.4                 | -                      | _                    | V     | I <sub>OH</sub> = -2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                              |

230

|                                               | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C<br>(unless otherwise stated) |   |         |        |                                                                                                                                                                   |  |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------|---|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                                     | Minimum Typical                                                                                     |   | Maximum | Units  | Notes                                                                                                                                                             |  |

| Flash Byte Read Time                          | 100                                                                                                 | - | -       | ns     |                                                                                                                                                                   |  |

| Flash Byte Program Time                       | 20                                                                                                  | _ | 40      | μs     |                                                                                                                                                                   |  |

| Flash Page Erase Time                         | 10                                                                                                  | - | -       | ms     |                                                                                                                                                                   |  |

| Flash Mass Erase Time                         | 200                                                                                                 | - | -       | ms     |                                                                                                                                                                   |  |

| Writes to Single Address<br>Before Next Erase | -                                                                                                   | _ | 2       |        |                                                                                                                                                                   |  |

| Flash Row Program Time                        | -                                                                                                   | _ | 8       | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This<br>parameter is only an issue<br>when bypassing the Flash<br>Controller. |  |

| Data Retention                                | 100                                                                                                 | _ | _       | years  | 25 °C                                                                                                                                                             |  |

| Endurance                                     | 10,000                                                                                              | _ | _       | cycles | Program/erase cycles                                                                                                                                              |  |

## Table 132. Flash Memory Electrical Characteristics and Timing

## Table 133. Watchdog Timer Electrical Characteristics and Timing

| V <sub>DD</sub> = 2.7 V to 3.6 V   |  |

|------------------------------------|--|

| T <sub>A</sub> = -40 °C to +105 °C |  |

| (unless otherwise stated)          |  |

| Symbol              | Parameter                | Minimum | Typical | Maximum     | Units | Conditions                                                      |

|---------------------|--------------------------|---------|---------|-------------|-------|-----------------------------------------------------------------|

| F <sub>WDT</sub>    | WDT Oscillator Frequency |         | 10      |             | kHz   |                                                                 |

| F <sub>WDT</sub>    | WDT Oscillator Error     |         |         | <u>+</u> 50 | %     |                                                                 |

| T <sub>WDTCAL</sub> | WDT Calibrated Timeout   | 0.98    | 1       | 1.02        | S     | V <sub>DD</sub> = 3.3 V;<br>T <sub>A</sub> = 30 °C              |

|                     |                          | 0.70    | 1       | 1.30        | S     | $V_{DD}$ = 2.7 V to 3.6 V<br>T <sub>A</sub> = 0 °C to 70 °C     |

|                     |                          | 0.50    | 1       | 1.50        | S     | $V_{DD}$ = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C |

zilog

|                   |                   | V <sub>DD</sub> | V <sub>DD</sub> = 2.7 V to 3.6 V |            |       |                                                                           |

|-------------------|-------------------|-----------------|----------------------------------|------------|-------|---------------------------------------------------------------------------|

| Symbol            | Parameter         | Minimum         | Typical                          | Maximum    | Units | Conditions                                                                |

| T <sub>AERR</sub> | Temperature Error |                 | <u>+</u> 0.5                     | <u>+</u> 2 | °C    | Over the range +20 °C<br>to +30 °C (as<br>measured by ADC) <sup>1</sup>   |

|                   |                   |                 | <u>+</u> 1                       | <u>+</u> 5 | °C    | Over the range +0 °C<br>to +70 °C (as<br>measured by ADC)                 |

|                   |                   |                 | <u>+</u> 2                       | <u>+</u> 7 | °C    | Over the range +0 °C<br>to +105 °C (as<br>measured by ADC)                |

|                   |                   |                 | <u>+</u> 7                       |            | °C    | Over the range -40 °C<br>to +105 °C (as<br>measured by ADC)               |

| T <sub>AERR</sub> | Temperature Error |                 | TBD                              |            | °C    | Over the range -40 °C<br>to +105 °C (as<br>measured by<br>comparator)     |

| t <sub>WAKE</sub> | Wakeup Time       |                 | 80                               | 100        | μs    | Time required for<br>Temperature Sensor<br>to stabilize after<br>enabling |

#### **Table 138. Temperature Sensor Electrical Characteristics**

<sup>1</sup>Devices are factory calibrated at for maximal accuracy between +20 °C and +30 °C, so the sensor is maximally accurate in that range. User re-calibration for a different temperature range is possible and increases accuracy near the new calibration point.

# General Purpose I/O Port Input Data Sample Timing

Figure 34 displays timing of the GPIO Port input sampling. The input value on a GPIO Port pin is sampled on the rising edge of the system clock. The Port value is available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

265

L LD 205 LDC 205 LDCI 204, 205 LDE 205 LDEI 204, 205 LDX 205 LEA 205 load 205 load constant 204 load constant to/from program memory 205 load constant with auto-increment addresses 205 load effective address 205 load external data 205 load external data to/from data memory and auto-increment addresses 204 load external to/from data memory and auto-increment addresses 205 load using extended addressing 205 logical AND 205 logical AND/extended addressing 205 logical exclusive OR 206 logical exclusive OR/extended addressing 206 logical instructions 205 logical OR 205 logical OR/extended addressing 206 low power modes 33

# Μ

master interrupt enable 57 memory data 17 program 15 mode CAPTURE 85, 86 CAPTURE/COMPARE 85 CONTINUOUS 84 COUNTER 84 GATED 85 ONE-SHOT 84 PWM 85 modes 85 MULT 203 multiply 203 multiprocessor mode, UART 103

# Ν

NOP (no operation) 204 notation b 201 cc 201 DA 201 ER 201 IM 201 IR 201 Ir 201 IRR 201 Irr 201 p 201 R 201 r 201 RA 201 RR 201 rr 201 vector 201 X 201 notational shorthand 201

# O OCD

architecture 173 auto-baud detector/generator 176 baud rate limits 177 block diagram 173 breakpoints 178 commands 179 control register 184 data format 176 DBG pin to RS-232 Interface 174 debug mode 175 debugger break 206 interface 174 serial errors 177 status register 185