# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 128 x 8                                                   |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f041ash020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Signal Descriptions**

Table 2 describes the Z8 Encore! XP F082A Series signals. See Pin Configurations on page 9 to determine the signals available for the specific package styles.

| Signal Mnemonic                                     | I/O | Description                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|-----------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| General-Purpose I/O Ports A–D                       |     |                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| PA[7:0]                                             | I/O | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |  |  |  |  |  |

| PB[7:0]                                             | I/O | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |  |  |  |  |  |

| PC[7:0]                                             | I/O | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |  |  |  |  |  |

| PD[0]                                               | I/O | Port D. This pin is used for general-purpose output only.                                                                                                                                                                                                                                               |  |  |  |  |  |

| Note: PB6 and PB7 ar<br>replaced by AV <sub>E</sub> |     | vailable in 28-pin packages without ADC. In 28-pin packages with ADC, they are $V_{\rm SS}.$                                                                                                                                                                                                            |  |  |  |  |  |

| UART Controllers                                    |     |                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| TXD0                                                | 0   | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |  |  |  |  |  |

| RXD0                                                | Ι   | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |  |  |  |  |  |

| CTS0                                                | Ι   | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |  |  |  |  |  |

| DE                                                  | 0   | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 register. The DE signal may be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |  |  |  |  |  |

| Timers                                              |     |                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| T0OUT/T1OUT                                         | 0   | Timer Output 0–1. These signals are outputs from the timers.                                                                                                                                                                                                                                            |  |  |  |  |  |

| T0OUT/T1OUT                                         | 0   | Timer Complement Output 0–1. These signals are output from the timers in PWM Dual Output mode.                                                                                                                                                                                                          |  |  |  |  |  |

| T0IN/T1IN                                           | Ι   | Timer Input 0–1. These signals are used as the capture, gating and counter inputs.                                                                                                                                                                                                                      |  |  |  |  |  |

| Comparator                                          |     |                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| CINP/CINN                                           | Ι   | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |  |  |  |  |  |

| COUT                                                | 0   | Comparator Output.                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

## Table 2. Signal Descriptions

**z**ilog<sup>°</sup>

addresses outside the available Flash memory addresses returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 5 describes the Program Memory Maps for the Z8 Encore! XP F082A Series products.

| Program Memory Address (Hex) | Function                     |  |  |  |  |

|------------------------------|------------------------------|--|--|--|--|

| Z8F082A and Z8F081A Products |                              |  |  |  |  |

| 0000–0001                    | Flash Option Bits            |  |  |  |  |

| 0002–0003                    | Reset Vector                 |  |  |  |  |

| 0004–0005                    | WDT Interrupt Vector         |  |  |  |  |

| 0006–0007                    | Illegal Instruction Trap     |  |  |  |  |

| 0008–0037                    | Interrupt Vectors*           |  |  |  |  |

| 0038–0039                    | Reserved                     |  |  |  |  |

| 003A-003D                    | Oscillator Fail Trap Vectors |  |  |  |  |

| 003E-1FFF                    | Program Memory               |  |  |  |  |

| Z8F042A and Z8F041A Products |                              |  |  |  |  |

| 0000–0001                    | Flash Option Bits            |  |  |  |  |

| 0002–0003                    | Reset Vector                 |  |  |  |  |

| 0004–0005                    | WDT Interrupt Vector         |  |  |  |  |

| 0006–0007                    | Illegal Instruction Trap     |  |  |  |  |

| 0008–0037                    | Interrupt Vectors*           |  |  |  |  |

| 0038–0039                    | Reserved                     |  |  |  |  |

| 003A-003D                    | Oscillator Fail Trap Vectors |  |  |  |  |

| 003E-0FFF                    | Program Memory               |  |  |  |  |

Table 5. Z8 Encore! XP F082A Series Program Memory Maps

Zilog <sub>17</sub>

| Program Memory Address (Hex)                | Function                     |

|---------------------------------------------|------------------------------|

| Z8F022A and Z8F021A Products                |                              |

| 0000–0001                                   | Flash Option Bits            |

| 0002–0003                                   | Reset Vector                 |

| 0004–0005                                   | WDT Interrupt Vector         |

| 0006–0007                                   | Illegal Instruction Trap     |

| 0008–0037                                   | Interrupt Vectors*           |

| 0038–0039                                   | Reserved                     |

| 003A-003D                                   | Oscillator Fail Trap Vectors |

| 003E-07FF                                   | Program Memory               |

| Z8F012A and Z8F011A Products                |                              |

| 0000–0001                                   | Flash Option Bits            |

| 0002–0003                                   | Reset Vector                 |

| 0004–0005                                   | WDT Interrupt Vector         |

| 0006–0007                                   | Illegal Instruction Trap     |

| 0008–0037                                   | Interrupt Vectors*           |

| 0038–0039                                   | Reserved                     |

| 003A-003D                                   | Oscillator Fail Trap Vectors |

| 003E-03FF                                   | Program Memory               |

| * See Table 32 on page 56 for a list of the | interrupt vectors.           |

Table 5. Z8 Encore! XP F082A Series Program Memory Maps (Continued)

## **Data Memory**

The Z8 Encore! XP F082A Series does not use the eZ8 CPU's 64 KB Data Memory address space.

# **Flash Information Area**

Table 6 on page 18 describes the Z8 Encore! XP F082A Series Flash Information Area. This 128 B Information Area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash Information Area is mapped into the Program Memory and overlays the 128 bytes at addresses FE00H to FF7FH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Infor-

## **HALT Mode**

Executing the eZ8 CPU's HALT instruction places the device into HALT mode, which powers down the CPU but leaves all other peripherals active. In HALT mode, the operating characteristics are:

- Primary oscillator is enabled and continues to operate.

- System clock is enabled and continues to operate.

- eZ8 CPU is stopped.

- Program counter (PC) stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate.

- If enabled, the Watchdog Timer continues to operate.

- All other on-chip peripherals continue to operate, if enabled.

The eZ8 CPU can be brought out of HALT mode by any of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brownout reset

- External **RESET** pin assertion

To minimize current in HALT mode, all GPIO pins that are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

## **Peripheral-Level Power Control**

In addition to the STOP and HALT modes, it is possible to disable each peripheral on each of the Z8 Encore! XP F082A Series devices. Disabling a given peripheral minimizes its power consumption.

# **Power Control Register Definitions**

The following sections define the Power Control registers.

## **Power Control Register 0**

Each bit of the following registers disables a peripheral block, either by gating its system clock input or by removing power from the block. The default state of the low-power

zilog<sup>®</sup>

| Port   | Pin | Mnemonic    | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------|-----------------------------------------|-----------------------------------------|

| Port A | PA0 | T0IN/T0OUT* | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|        |     | Reserved    |                                         | -                                       |

|        | PA1 | TOOUT       | Timer 0 Output                          | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA2 | DE0         | UART 0 Driver Enable                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA3 | CTS0        | UART 0 Clear to Send                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA4 | RXD0/IRRX0  | UART 0/IrDA 0 Receive Data              | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA5 | TXD0/IRTX0  | UART 0/IrDA 0 Transmit Data             | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA6 | T1IN/T1OUT* | Timer 1 Input/Timer 1 Output Complement | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA7 | T1OUT       | Timer 1 Output                          | -                                       |

|        |     | Reserved    |                                         | -                                       |

#### Table 14. Port Alternate Function Mapping (Non 8-Pin Parts)

**Note:** Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in Port A–D Alternate Function Sub-Registers on page 47 automatically enables the associated alternate function.

\* Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in Timer Pin Signal Operation on page 82.

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source       |

|----------|-------------------------------------|--------------------------------|

|          | 0034H                               | Port C Pin 1, both input edges |

| Lowest   | 0036H                               | Port C Pin 0, both input edges |

|          | 0038H                               | Reserved                       |

#### Table 32. Trap and Interrupt Vectors in Order of Priority (Continued)

# Architecture

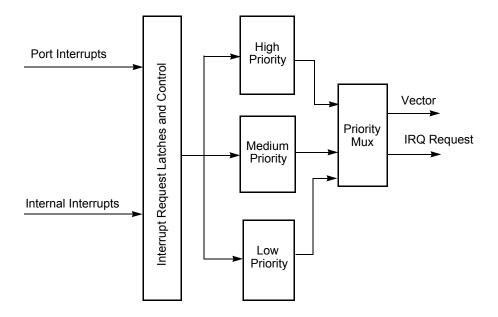

Figure 8 displays the interrupt controller block diagram.

Figure 8. Interrupt Controller Block Diagram

# Operation

## **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control register globally enables and disables interrupts.

zilog<sup>\*</sup>

If the TPOL bit in the Timer Control register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

Follow the steps below for configuring a timer for PWM SINGLE OUTPUT mode and initiating the PWM operation:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for PWM SINGLE OUTPUT mode.

- Set the prescale value.

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM period). The Reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

$PWM Period (s) = \frac{Reload Value \times Prescale}{System Clock Frequency (Hz)}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT mode equation to determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{PWM Value}{Reload Value} \times 100$

## Watchdog Timer Refresh

When first enabled, the Watchdog Timer is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT Reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When the Z8 Encore! XP<sup>®</sup> F082A Series devices are operating in DEBUG mode (using the on-chip debugger), the Watchdog Timer is continuously refreshed to prevent any Watchdog Timer time-outs.

## Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash Option Bit determines the time-out response of the Watchdog Timer. For information on programming the WDT\_RES Flash Option Bit, see Flash Option Bits on page 153.

#### WDT Interrupt in Normal Operation

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Reset Status (RSTSTAT) register (see Reset Status Register on page 30). If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its Reload Value.

The Reset Status (RSTSTAT) register must be read before clearing the WDT interrupt. This read clears the WDT timeout Flag and prevents further WDT interrupts from immediately occurring.

#### WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and the Z8 Encore! XP F082A Series devices are in STOP mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Reset Status (RSTSTAT) register are set to 1 following a WDT time-out in STOP mode. For more information on Stop Mode Recovery, see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address.

1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.

IREN—Infrared Encoder/Decoder Enable

0 =Infrared Encoder/Decoder is disabled. UART operates normally.

1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.

#### **UART Status 0 Register**

The UART Status 0 (UxSTAT0) and Status 1(UxSTAT1) registers (Table 63 and Table 64) identify the current UART operating configuration and status.

Table 63. UART Status 0 Register (U0STAT0)

| BITS  | 7   | 6    | 5  | 4  | 3    | 2    | 1   | 0   |  |

|-------|-----|------|----|----|------|------|-----|-----|--|

| FIELD | RDA | PE   | OE | FE | BRKD | TDRE | TXE | CTS |  |

| RESET | 0   | 0    | 0  | 0  | 0    | 1    | 1   | Х   |  |

| R/W   | R   | R    | R  | R  | R    | R    | R   | R   |  |

| ADDR  |     | F41H |    |    |      |      |     |     |  |

RDA—Receive Data Available

This bit indicates that the UART Receive Data register has received data. Reading the UART Receive Data register clears this bit.

0 = The UART Receive Data register is empty.

1 = There is a byte in the UART Receive Data register.

PE—Parity Error

This bit indicates that a parity error has occurred. Reading the UART Receive Data register clears this bit.

0 = No parity error has occurred.

1 = A parity error has occurred.

OE—Overrun Error

This bit indicates that an overrun error has occurred. An overrun occurs when new data is received and the UART Receive Data register has not been read. If the RDA bit is reset to 0, reading the UART Receive Data register clears this bit.

- 0 = No overrun error occurred.

- 1 = An overrun error occurred.

FE—Framing Error

This bit indicates that a framing error (no Stop bit following data reception) was detected. Reading the UART Receive Data register clears this bit.

MPRX—Multiprocessor Receive

Returns the value of the most recent multiprocessor bit received. Reading from the UART Receive Data register resets this bit to 0.

## **UART Transmit Data Register**

Data bytes written to the UART Transmit Data (UxTXD) register (Table 65) are shifted out on the TXDx pin. The Write-only UART Transmit Data register shares a Register File address with the read-only UART Receive Data register.

| BITS  | 7 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|------|---|---|---|---|---|---|

| FIELD |   | TXD  |   |   |   |   |   |   |

| RESET | Х | Х    | Х | Х | Х | Х | Х | Х |

| R/W   | W | W    | W | W | W | W | W | W |

| ADDR  |   | F40H |   |   |   |   |   |   |

#### Table 65. UART Transmit Data Register (U0TXD)

TXD-Transmit Data

UART transmitter data byte to be shifted out through the TXDx pin.

## **UART Receive Data Register**

Data bytes received through the RXDx pin are stored in the UART Receive Data (UxRXD) register (Table 66). The read-only UART Receive Data register shares a Register File address with the Write-only UART Transmit Data register.

#### Table 66. UART Receive Data Register (U0RXD)

| BITS      | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|----------------|---|---|---|---|---|---|---|

| FIELD     | RXD            |   |   |   |   |   |   |   |

| RESET     | Х              | Х | Х | Х | Х | Х | Х | Х |

| R/W       | R              | R | R | R | R | R | R | R |

| ADDR      | F40H           |   |   |   |   |   |   |   |

| X = Undef | X = Undefined. |   |   |   |   |   |   |   |

RXD—Receive Data

UART receiver data byte from the RXDx pin

zilog <sub>123</sub>

can output values across the entire 11-bit range, from -1024 to +1023. In SINGLE-ENDED mode, the output generally ranges from 0 to +1023, but offset errors can cause small negative values.

The ADC registers actually return 13 bits of data, but the two LSBs are intended for compensation use only. When the software compensation routine is performed on the 13 bit raw ADC value, two bits of resolution are lost because of a rounding error. As a result, the final value is an 11-bit number.

#### Hardware Overflow

When the hardware overflow bit (OVF) is set in ADC Data Low Byte (ADCD\_L) register, all other data bits are invalid. The hardware overflow bit is set for values greater than  $V_{ref}$  and less than  $-V_{ref}$  (DIFFERENTIAL mode).

### **Automatic Powerdown**

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to power up. The ADC powers up when a conversion is requested by the ADC Control register.

## Single-Shot Conversion

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Follow the steps below for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the desired analog inputs by configuring the general-purpose I/O pins for alternate analog function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC.

- Write to BUFMODE [2:0] to select SINGLE-ENDED or DIFFERENTIAL mode, as well as unbuffered or buffered mode.

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is. contained in the ADC Control Register 0.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control register can be written simultaneously (the ADC can be configured and enabled with the same write instruction):

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

204

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| ТСМ      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |

Table 118. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-Increment Addresses       |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

## Table 119. CPU Control Instructions

| Mnemonic | Operands | Instruction           |  |  |  |  |  |

|----------|----------|-----------------------|--|--|--|--|--|

| ATM      | _        | Atomic Execution      |  |  |  |  |  |

| CCF      | _        | Complement Carry Flag |  |  |  |  |  |

| DI       | _        | Disable Interrupts    |  |  |  |  |  |

| EI       | _        | Enable Interrupts     |  |  |  |  |  |

| HALT     | _        | Halt Mode             |  |  |  |  |  |

| NOP      | _        | No Operation          |  |  |  |  |  |

| RCF      | _        | Reset Carry Flag      |  |  |  |  |  |

zilog <sub>247</sub>

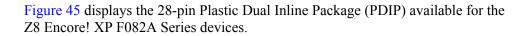

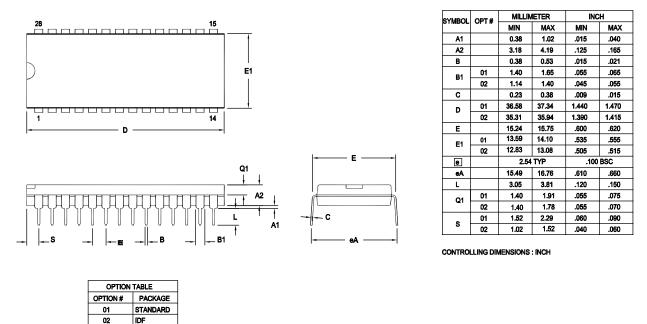

Note: ZILOG supplies both options for production. Component layout PCB design should cover bigger option 01.

#### Figure 45. 28-Pin Plastic Dual Inline Package (PDIP)

zilog | 249

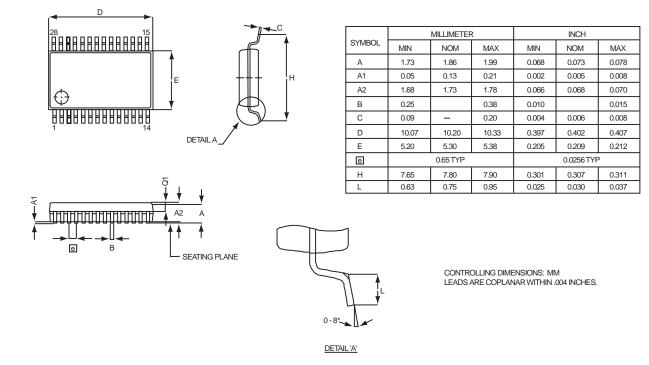

Figure 47 displays the 28-pin Small Shrink Outline Package (SSOP) available for the Z8 Encore! XP F082A Series devices.

Figure 47. 28-Pin Small Shrink Outline Package (SSOP)

zilog 257

| Part Number                                                                                 | Flash     | RAM      | SUVN | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |  |

|---------------------------------------------------------------------------------------------|-----------|----------|------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|--|

| Z8 Encore! XP <sup>®</sup> F082A Series with 1 KB Flash, 10-Bit Analog-to-Digital Converter |           |          |      |           |            |                     |                     |                |            |                    |                     |  |

| Standard Temperatu                                                                          | re: 0 °C  | to 70 °C | ;    |           |            |                     |                     |                |            |                    |                     |  |

| Z8F012APB020SC                                                                              | 1 KB      | 256 B    | 16 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |  |

| Z8F012AQB020SC                                                                              | 1 KB      | 256 B    | 16 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |  |

| Z8F012ASB020SC                                                                              | 1 KB      | 256 B    | 16 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |  |

| Z8F012ASH020SC                                                                              | 1 KB      | 256 B    | 16 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |  |

| Z8F012AHH020SC                                                                              | 1 KB      | 256 B    | 16 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |  |

| Z8F012APH020SC                                                                              | 1 KB      | 256 B    | 16 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |  |

| Z8F012ASJ020SC                                                                              | 1 KB      | 256 B    | 16 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |  |

| Z8F012AHJ020SC                                                                              | 1 KB      | 256 B    | 16 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |  |

| Z8F012APJ020SC                                                                              | 1 KB      | 256 B    | 16 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |  |

| Extended Temperatu                                                                          | re: -40 ° | C to 10  | 5 °C |           |            |                     |                     |                |            |                    |                     |  |

| Z8F012APB020EC                                                                              | 1 KB      | 256 B    | 16 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |  |

| Z8F012AQB020EC                                                                              | 1 KB      | 256 B    | 16 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |  |

| Z8F012ASB020EC                                                                              | 1 KB      | 256 B    | 16 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |  |

| Z8F012ASH020EC                                                                              | 1 KB      | 256 B    | 16 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |  |

| Z8F012AHH020EC                                                                              | 1 KB      | 256 B    | 16 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |  |

| Z8F012APH020EC                                                                              | 1 KB      | 256 B    | 16 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |  |

| Z8F012ASJ020EC                                                                              | 1 KB      | 256 B    | 16 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |  |

| Z8F012AHJ020EC                                                                              | 1 KB      | 256 B    | 16 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |  |

| Z8F012APJ020EC                                                                              | 1 KB      | 256 B    | 16 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |  |