# E·XFL

#### Zilog - Z8F041ASH020EC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | IrDA, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT               |

| Number of I/O              | 17                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | 128 x 8                                                       |

| RAM Size                   | 1K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | -                                                             |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f041ash020ec00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **z**ilog<sup>°</sup>

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, and Z8 Encore! XP are registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

ISO 9001:2000 FS 507510 Zilog products are designed and manufactured under an ISO registered 9001:2000 Quality Management System. For more details, please visit www.zilog.com/quality.

#### Low-Power Operational Amplifier

The optional low-power operational amplifier (LPO) is a general-purpose amplifier primarily targeted for current sense applications. The LPO output may be routed internally to the ADC or externally to a pin.

#### **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

#### **Temperature Sensor**

The optional temperature sensor produces an analog output proportional to the device temperature. This signal can be sent to either the ADC or the analog comparator.

#### **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

### **External Crystal Oscillator**

The crystal oscillator circuit provides highly accurate clock frequencies with the use of an external crystal, ceramic resonator or RC network.

#### Low Voltage Detector

The low voltage detector (LVD) is able to generate an interrupt when the supply voltage drops below a user-programmable level. The LVD is available on 8-pin devices only.

#### **On-Chip Debugger**

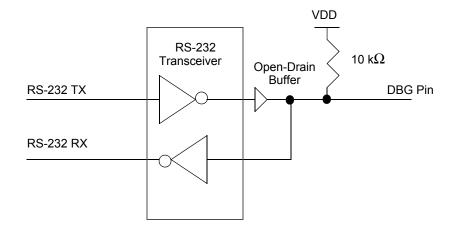

The Z8 Encore! XP<sup>®</sup> F082A Series products feature an integrated on-chip debugger (OCD) accessed via a single-pin interface. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints, and executing code.

### Table 2. Signal Descriptions (Continued)

| Signal Mnemonic     | I/O     | Description                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|---------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Analog              |         |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| ANA[7:0]            | I       | Analog Port. These signals are used as inputs to the analog-to-digital converter (ADC).                                                                                                                                                                                       |  |  |  |  |  |

| VREF                | I/O     | Analog-to-digital converter reference voltage input, or buffered output for internal reference.                                                                                                                                                                               |  |  |  |  |  |

| Low-Power Operation | onal An | nplifier (LPO)                                                                                                                                                                                                                                                                |  |  |  |  |  |

| AMPINP/AMPINN       | Ι       | LPO inputs. If enabled, these pins drive the positive and negative amplifier inputs respectively.                                                                                                                                                                             |  |  |  |  |  |

| AMPOUT              | 0       | LPO output. If enabled, this pin is driven by the on-chip LPO.                                                                                                                                                                                                                |  |  |  |  |  |

| Oscillators         |         |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| XIN                 | I       | External Crystal Input. This is the input pin to the crystal oscillator. A crystal can be connected between it and the <b>XOUT</b> pin to form the oscillator. In addition, this pin is used with external RC networks or external clock drivers to provide the system clock. |  |  |  |  |  |

| XOUT                | 0       | External Crystal Output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the <b>XIN</b> pin to form the oscillator.                                                                                                               |  |  |  |  |  |

| Clock Input         |         |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| CLKIN               | I       | Clock Input Signal. This pin may be used to input a TTL-level signal to be used as the system clock.                                                                                                                                                                          |  |  |  |  |  |

| LED Drivers         |         |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| LED                 | 0       | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                                                                                   |  |  |  |  |  |

| On-Chip Debugger    |         |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| DBG                 | I/O     | Debug. This signal is the control and data input and output to and from the On-Chip Debugger.                                                                                                                                                                                 |  |  |  |  |  |

|                     |         | <b>Caution:</b> The DBG pin is open-drain and requires a pull-up resistor to ensure proper operation.                                                                                                                                                                         |  |  |  |  |  |

| Reset               |         |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| RESET               | I/O     | RESET. Generates a Reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin low when in reset. This pin is open-drain and features an enabled internal pull-up resistor.                                                         |  |  |  |  |  |

12

110 = 64 cycles delay 111 = 128 cycles delay

INPCAP—Input Capture Event

This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.

0 = Previous timer interrupt is not a result of Timer Input Capture Event

1 = Previous timer interrupt is a result of Timer Input Capture Event

#### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode (Table 49).

Table 49. Timer 0–1 Control Register 1 (TxCTL1)

| BITS  | 7          | 6    | 5   | 4    | 3   | 2   | 1     | 0   |  |  |

|-------|------------|------|-----|------|-----|-----|-------|-----|--|--|

| FIELD | TEN        | TPOL |     | PRES |     |     | TMODE |     |  |  |

| RESET | 0          | 0    | 0   | 0    | 0   | 0   | 0     | 0   |  |  |

| R/W   | R/W        | R/W  | R/W | R/W  | R/W | R/W | R/W   | R/W |  |  |

| ADDR  | F07H, F0FH |      |     |      |     |     |       |     |  |  |

TEN-Timer Enable

0 = Timer is disabled.

1 = Timer enabled to count.

TPOL—Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer.

#### **ONE-SHOT mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **CONTINUOUS mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### COUNTER mode

If the timer is enabled the Timer Output signal is complemented after timer reload.

0 = Count occurs on the rising edge of the Timer Input signal.

1 = Count occurs on the falling edge of the Timer Input signal.

## zilog

134

## Low Power Operational Amplifier

## **Overview**

The LPO is a general-purpose low power operational amplifier. Each of the three ports of the amplifier is accessible from the package pins. The LPO contains only one pin configuration: ANA0 is the output/feedback node, ANA1 is the inverting input and ANA2 is the non-inverting input.

## Operation

To use the LPO, it must be enabled in the Power Control Register 0 (PWRCTL0). The default state of the LPO is OFF. To use the LPO, the LPO bit must be cleared, turning it ON (Power Control Register 0 (PWRCTL0) on page 35). When making normal ADC measurements on ANA0 (measurements not involving the LPO output), the LPO bit must be OFF. Turning the LPO bit ON interferes with normal ADC measurements.

**Warning:** The LPO bit enables the amplifier even in STOP mode. If the amplifier is not required in STOP mode, disable it. Failing to perform this results in STOP mode currents higher than necessary.

As with other ADC measurements, any pins used for analog purposes must be configured as such in the GPIO registers (see Port A–D Alternate Function Sub-Registers on page 47).

LPO output measurements are made on ANA0, as selected by the ANAIN[3:0] bits of ADC Control Register 0. It is also possible to make single-ended measurements on ANA1 and ANA2 while the amplifier is enabled, which is often useful for determining offset conditions. Differential measurements between ANA0 and ANA2 may be useful for noise cancellation purposes.

If the LPO output is routed to the ADC, then the BUFFMODE[2:0] bits of ADC Control/Status Register 1 must also be configured for unity-gain buffered operation. Sampling the LPO in an unbuffered mode is not recommended.

When either input is overdriven, the amplifier output saturates at the positive or negative supply voltage. No instability results.

138

Assuming a compensated ADC measurement, the following equation defines the relationship between the ADC reading and the die temperature:

$T = (25/128) \times (ADC - TSCAL[11:2]) + 30$

where, T is the temperature in C; ADC is the 10-bit compensated ADC value; and TSCAL is the temperature sensor calibration value, ignoring the two least significant bits of the 12-bit value.

See Temperature Sensor Calibration Data on page 164 for the location of TSCAL.

#### Calibration

The temperature sensor undergoes calibration during the manufacturing process and is maximally accurate at 30 °C. Accuracy decreases as measured temperatures move further from the calibration point.

**z**ilog<sup>®</sup>

## Flash Status Register

The Flash Status (FSTAT) register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status register shares its Register File address with the Write-only Flash Control register.

Table 79. Flash Status Register (FSTAT)

| BITS  | 7    | 6     | 5     | 4 | 3 | 2 | 1 | 0 |  |

|-------|------|-------|-------|---|---|---|---|---|--|

| FIELD | Rese | erved | FSTAT |   |   |   |   |   |  |

| RESET | 0    | 0     | 0     | 0 | 0 | 0 | 0 | 0 |  |

| R/W   | R    | R     | R     | R | R | R | R | R |  |

| ADDR  | FF8H |       |       |   |   |   |   |   |  |

Reserved—Must be 0.

FSTAT—Flash Controller Status

000000 = Flash Controller locked

000001 = First unlock command received (73H written)

000010 = Second unlock command received (8CH written)

000011 = Flash Controller unlocked

000100 = Sector protect register selected

001xxx = Program operation in progress

010xxx = Page erase operation in progress

100xxx = Mass erase operation in progress

## Flash Page Select Register

The Flash Page Select (FPS) register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7 bits given by FPS[6:0] are chosen for program/erase operation.

# zilog <sub>172</sub>

#### Table 104. NVDS Read Time (Continued)

| Operation              | Minimum<br>Latency | Maximum<br>Latency |

|------------------------|--------------------|--------------------|

| Read (128 byte array)  | 883                | 7609               |

| Write (16 byte array)  | 4973               | 5009               |

| Write (64 byte array)  | 4971               | 5013               |

| Write (128 byte array) | 4984               | 5023               |

| Illegal Read           | 43                 | 43                 |

| Illegal Write          | 31                 | 31                 |

If NVDS read performance is critical to your software architecture, there are some things you can do to optimize your code for speed, listed in order from most helpful to least helpful:

- Periodically refresh all addresses that are used. The optimal use of NVDS in terms of speed is to rotate the writes evenly among all addresses planned to use, bringing all reads closer to the minimum read time. Because the minimum read time is much less than the write time, however, actual speed benefits are not always realized.

- Use as few unique addresses as possible: this helps to optimize the impact of refreshing as well as minimize the requirement for it.

#### Figure 25. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (2)

#### **DEBUG Mode**

The operating characteristics of the devices in DEBUG mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions.

- The system clock operates unless in STOP mode.

- All enabled on-chip peripherals operate unless in STOP mode.

- Automatically exits HALT mode.

- Constantly refreshes the Watchdog Timer, if enabled.

#### **Entering DEBUG Mode**

The operating characteristics of the devices entering DEBUG mode are:

- The device enters DEBUG mode after the eZ8 CPU executes a BRK (Breakpoint) instruction.

- If the DBG pin is held Low during the final clock cycle of system reset, the part enters DEBUG mode immediately (20-/28-pin products only).

- **Note:** Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an Autobaud sequence (see OCD Auto-Baud Detector/Generator on page 176).

zilog | 177

The Auto-Baud Detector/Generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous datastreams, the maximum recommended baud rate is the system clock frequency divided by 8. The maximum possible baud rate for asynchronous datastreams is the system clock frequency divided by 4, but this theoretical maximum is possible only for low noise designs with clean signals. Table 105 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock<br>Frequency (MHz) | Recommended Maximum<br>Baud Rate (Kbps) | Recommended<br>Standard PC<br>Baud Rate (bps) | Minimum Baud<br>Rate (Kbps) |

|---------------------------------|-----------------------------------------|-----------------------------------------------|-----------------------------|

| 20.0                            | 2500.0                                  | 1,843,200                                     | 39                          |

| 1.0                             | 125.0                                   | 115,200                                       | 1.95                        |

| 0.032768 (32 kHz)               | 4.096                                   | 2,400                                         | 0.064                       |

#### Table 105. OCD Baud-Rate Limits

If the OCD receives a Serial Break (nine or more continuous bits Low) the Auto-Baud Detector/Generator resets. Reconfigure the Auto-Baud Detector/Generator by sending 80H.

#### **OCD Serial Errors**

The On-Chip Debugger can detect any of the following error conditions on the DBG pin:

- Serial Break (a minimum of nine continuous bits Low)

- Framing Error (received Stop bit is Low)

- Transmit Collision (OCD and host simultaneous transmission detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long Serial Break back to the host, and resets the Auto-Baud Detector/Generator. A Framing Error or Transmit Collision may be caused by the host sending a Serial Break to the OCD. Because of the open-drain nature of the interface, returning a Serial Break break back to the host only extends the length of the Serial Break if the host releases the Serial Break early.

The host transmits a Serial Break on the DBG pin when first connecting to the Z8 Encore! XP F082A Series devices or when recovering from an error. A Serial Break from the host resets the Auto-Baud Generator/Detector but does not reset the OCD Control register. A Serial Break leaves the device in DEBUG mode if that is the current mode. The OCD is held in Reset until the end of the Serial Break when the DBG pin returns

High. Because of the open-drain nature of the DBG pin, the host can send a Serial Break to the OCD even if the OCD is transmitting a character.

### OCD Unlock Sequence (8-Pin Devices Only)

Because of pin-sharing on the 8-pin device, an unlock sequence must be performed to access the DBG pin. If this sequence is not completed during a system reset, then the PA0/DBG pin functions only as a GPIO pin.

The following sequence unlocks the DBG pin:

- 1. Hold PA2/RESET Low.

- 2. Wait 5ms for the internal reset sequence to complete.

- 3. Send the following bytes serially to the debug pin:

```

DBG \leftarrow 80H (autobaud)

DBG \leftarrow EBH

DBG \leftarrow 5AH

DBG \leftarrow 70H

DBG \leftarrow CDH (32-bit unlock key)

```

4. Release PA2/RESET. The PA0/DBG pin is now identical in function to that of the DBG pin on the 20-/28-pin device. To enter DEBUG mode, re-autobaud and write 80H to the OCD control register (see On-Chip Debugger Commands on page 179).

**Caution:** Between Step 3 and Step 4, there is an interval during which the 8-pin device is neither in RESET nor DEBUG mode. If a device has been erased or has not yet been programmed, all program memory bytes contain FFH. The CPU interprets this as an illegal instruction, so some irregular behavior can occur before entering DEBUG mode, and the register values after entering DEBUG mode differs from their specified reset values. However, none of these irregularities prevent programming the Flash memory. Before beginning system debug, it is recommended that some legal code be programmed into the 8-pin device, and that a RESET occurs.

#### **Breakpoints**

Execution Breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the On-Chip Debugger. If Breakpoints are enabled, the OCD enters DEBUG mode and idles the eZ8 CPU. If Breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

zilog |

Write Memory, Read Memory, Write Register, Read Register, Read Memory CRC, Step Instruction, Stuff Instruction, and Execute Instruction commands.

DBG  $\leftarrow$  03H DBG  $\rightarrow$  RuntimeCounter[15:8] DBG  $\rightarrow$  RuntimeCounter[7:0]

• Write OCD Control Register (04H)—The Write OCD Control Register command writes the data that follows to the OCDCTL register. When the Flash Read Protect Option Bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0 and the only method of returning the device to normal operating mode is to reset the device.

DBG  $\leftarrow$  04H DBG  $\leftarrow$  OCDCTL[7:0]

• **Read OCD Control Register (05H)**—The Read OCD Control Register command reads the value of the OCDCTL register.

```

DBG \leftarrow 05H

DBG \rightarrow OCDCTL[7:0]

```

• Write Program Counter (06H)—The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter (PC). If the device is not in DE-BUG mode or if the Flash Read Protect Option bit is enabled, the Program Counter (PC) values are discarded.

```

DBG ← 06H

DBG ← ProgramCounter[15:8]

DBG ← ProgramCounter[7:0]

```

• **Read Program Counter (07H)**—The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

• Write Register (08H)—The Write Register command writes data to the Register File. Data can be written 1–256 bytes at a time (256 bytes can be written by setting size to 0). If the device is not in DEBUG mode, the address and data values are discarded. If the Flash Read Protect Option bit is enabled, only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

#### 200

## Assembly Language Syntax

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed if manual program coding is preferred or if you intend to implement your own assembler.

**Example 1**: If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Table 112. Assembly Language Syntax Example 1

| Assembly Language<br>Code | ADD | 43H, | 08H | (ADD dst, src) |

|---------------------------|-----|------|-----|----------------|

| Object Code               | 04  | 08   | 43  | (OPC src, dst) |

**Example 2**: In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Table 113. Assembly Language Syntax Example 2

| Assembly Language<br>Code | ADD | 43H, | R8 | (ADD dst, src) |

|---------------------------|-----|------|----|----------------|

| Object Code               | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

## eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is described in Table 114.

**z**ilog<sup>°</sup>

|   |             |             |                     |                     |                     |                 | Lo           | ower Ni       | bble (He        | x)             |              |            |             |             |           |           |

|---|-------------|-------------|---------------------|---------------------|---------------------|-----------------|--------------|---------------|-----------------|----------------|--------------|------------|-------------|-------------|-----------|-----------|

|   | 0           | 1           | 2                   | 3                   | 4                   | 5               | 6            | 7             | 8               | 9              | А            | В          | С           | D           | Е         | F         |

| ~ | 1.1         | 2.2         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            | 2.3          | 2.2        | 2.2         | 3.2         | 1.2       | 1.2       |

| 0 | BRK         | SRP<br>IM   | <b>ADD</b><br>r1,r2 | ADD<br>r1,lr2       | <b>ADD</b><br>R2,R1 | ADD<br>IR2,R1   | ADD<br>R1,IM | ADD<br>IR1,IM | ADDX<br>ER2,ER1 | ADDX<br>IM,ER1 | DJNZ<br>r1,X | JR<br>cc,X | LD<br>r1,IM | JP<br>cc,DA | INC<br>r1 | NO        |

|   | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            | ,            |            | ,           | 00,271      | 1         | See       |

| 1 | RLC         | RLC         | ADC                 | ADC                 | ADC                 | ADC             | ADC          | ADC           | ADCX            | ADCX           |              |            |             |             |           | Орсо      |

|   | R1          | IR1         | r1,r2               | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           | Ma        |

| 2 | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1,        |

| 2 | INC<br>R1   | INC<br>IR1  | <b>SUB</b><br>r1,r2 | SUB<br>r1,lr2       | <b>SUB</b><br>R2,R1 | SUB<br>IR2,R1   | SUB<br>R1,IM | SUB<br>IR1,IM | SUBX<br>ER2,ER1 | SUBX<br>IM,ER1 |              |            |             |             |           | AT        |

|   | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           |           |

| 3 | DEC         | DEC         | SBC                 | SBC                 | SBC                 | SBC             | SBC          | SBC           | SBCX            | SBCX           |              |            |             |             |           |           |

|   | R1          | IR1         | r1,r2               | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           |           |

| 4 | DA          | DA          | OR                  | OR                  | OR                  | OR              | OR           | OR            | ORX             | ORX            |              |            |             |             |           |           |

|   | R1          | IR1         | r1,r2               | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| 5 | 2.2<br>POP  | 2.3<br>POP  | 2.3<br>AND          | 2.4<br>AND          | 3.3<br>AND          | 3.4<br>AND      | 3.3<br>AND   | 3.4<br>AND    | 4.3<br>ANDX     | 4.3<br>ANDX    |              |            |             |             |           | 1.<br>WE  |

| Ŭ | R1          | IR1         | r1,r2               | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.        |

| 6 | СОМ         | COM         | тсм                 | тсм                 | тсм                 | тсм             | тсм          | тсм           | тсмх            | тсмх           |              |            |             |             |           | STO       |

|   | R1          | IR1         | r1,r2               | r1,Ir2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| - | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.1       |

| 7 | PUSH<br>R2  | PUSH<br>IR2 | <b>TM</b><br>r1,r2  | <b>TM</b><br>r1,lr2 | <b>TM</b><br>R2,R1  | TM<br>IR2,R1    | TM<br>R1,IM  | TM<br>IR1,IM  | TMX<br>ER2,ER1  | TMX<br>IM,ER1  |              |            |             |             |           | HA        |

|   | 2.5         | 2.6         | 2.5                 | 2.9                 | 3.2                 | 3.3             | 3.4          | 3.5           | 3.4             | 3.4            |              |            |             |             |           | 1.:       |

| 8 | DECW        |             | LDE                 | LDEI                | LDX                 | LDX             | LDX          | LDX           | LDX             | LDX            |              |            |             |             |           | D         |

|   | RR1         | IRR1        | r1,Irr2             | lr1,lrr2            | r1,ER2              | lr1,ER2         | IRR2,R1      | IRR2,IR1      | r1,rr2,X        | rr1,r2,X       |              |            |             |             |           |           |

|   | 2.2         | 2.3         | 2.5                 | 2.9                 | 3.2                 | 3.3             | 3.4          | 3.5           | 3.3             | 3.5            |              |            |             |             |           | 1.2       |

| 9 | RL          | RL          | LDE                 | LDEI                | LDX                 | LDX             | LDX          | LDX           | LEA             | LEA            |              |            |             |             |           | E         |

|   | R1          | IR1         | r2,Irr1             | lr2,lrr1            | r2,ER1              | Ir2,ER1         |              | IR2,IRR1      | r1,r2,X         | rr1,rr2,X      |              |            |             |             |           | <u> </u>  |

| А | 2.5<br>INCW | 2.6<br>INCW | 2.3<br>CP           | 2.4<br>CP           | 3.3<br>CP           | 3.4<br>CP       | 3.3<br>CP    | 3.4<br>CP     | 4.3<br>CPX      | 4.3<br>CPX     |              |            |             |             |           | 1.4<br>RE |

| ~ | RR1         | IRR1        | r1,r2               | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.        |

| В | CLR         | CLR         | XOR                 | XOR                 | XOR                 | XOR             | XOR          | XOR           | XORX            | XORX           |              |            |             |             |           | IRE       |

|   | R1          | IR1         | r1,r2               | r1,Ir2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| ~ | 2.2         | 2.3         | 2.5                 | 2.9                 | 2.3                 | 2.9             |              | 3.4           | 3.2             |                |              |            |             |             |           | 1.1       |

| С | RRC<br>R1   | IR1         | LDC<br>r1,Irr2      | LDCI<br>Ir1,Irr2    | JP<br>IRR1          | LDC<br>Ir1,Irr2 |              | LD<br>r1,r2,X | PUSHX<br>ER2    |                |              |            |             |             |           | RC        |

|   | 2.2         | 2.3         | 2.5                 | 2.9                 | 2.6                 | 2.2             | 3.3          | 3.4           | 3.2             |                |              |            |             |             |           | 1.:       |

| D | SRA         | SRA         | LDC                 | LDCI                | -                   | BSWAP           |              | LD            | POPX            |                |              |            |             |             |           | SC        |

|   | R1          | IR1         | r2,Irr1             | lr2,Irr1            | IRR1                | R1              | DA           | r2,r1,X       | ER1             |                |              |            |             |             |           |           |

|   | 2.2         | 2.3         | 2.2                 | 2.3                 | 3.2                 | 3.3             | 3.2          | 3.3           | 4.2             | 4.2            |              |            |             |             |           | 1.:       |

| E | RR          | RR          | BIT                 | LD                  | LD                  | LD              | LD           | LD            | LDX             | LDX            |              |            |             |             |           | cc        |

|   | R1          | IR1         | p,b,r1              | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| F | 2.2<br>SWAP | 2.3<br>SWAP | 2.6<br><b>TRAP</b>  | 2.3<br>LD           | 2.8<br>MULT         | 3.3<br>LD       | 3.3<br>BTJ   | 3.4<br>BTJ    |                 |                |              | 4          |             |             |           |           |

|   | R1          | IR1         | Vector              | Ir1,r2              | RR1                 | R2,IR1          | p,b,r1,X     |               |                 |                | V            | V          |             |             |           |           |

Figure 31. First Opcode Map

Upper Nibble (Hex)

218

# zilog

## **Electrical Characteristics**

The data in this chapter is pre-qualification and pre-characterization and is subject to change. Additional electrical characteristics may be found in the individual chapters.

## **Absolute Maximum Ratings**

Stresses greater than those listed in Table 126 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                                      | Minimum | Maximum | Units | Notes |

|----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                 | -40     | +105    | °C    |       |

| Storage temperature                                            | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>             | -0.3    | +5.5    | V     | 1     |

|                                                                | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$               | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin            | -5      | +5      | μA    |       |

| Maximum output current from active output pin                  | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0 °C to 70 °C                |         |         |       |       |

| Total power dissipation                                        |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$               |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0 °C to 70 °C               |         |         |       |       |

| Total power dissipation                                        |         | 430     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub> |         | 120     | mA    |       |

#### Table 126. Absolute Maximum Ratings

zilog

#### 22

#### Table 126. Absolute Maximum Ratings (Continued)

| Parameter                                        | Minimum Maximum | Units | Notes |  |

|--------------------------------------------------|-----------------|-------|-------|--|

| 28-pin Packages Maximum Ratings at 0 °C to 70 °C |                 |       |       |  |

| Total power dissipation                          | 450             | mW    |       |  |

| Maximum current into $V_{DD}$ or out of $V_{SS}$ | 125             | mA    |       |  |

|                                                  |                 |       |       |  |

Operating temperature is specified in DC Characteristics.

This voltage applies to all pins except the following: V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1). On the 8-pin packages, this applies to all pins but V<sub>DD</sub>.

2. This voltage applies to pins on the 20-/28-pin packages supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1).

## **DC Characteristics**

Table 127 lists the DC characteristics of the Z8 Encore!  $XP^{\mathbb{R}}$  F082A Series products. All voltages are referenced to  $V_{SS}$ , the primary system ground.

| Table 127. DC Characteristics |  |

|-------------------------------|--|

|-------------------------------|--|

|                  |                              |                     | 40 °C to +<br>therwise | 105 °C<br>specified) |       |                                                                                                                                                              |  |  |

|------------------|------------------------------|---------------------|------------------------|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol           | Parameter                    | Minimum             | Typical                | Maximum              | Units | Conditions                                                                                                                                                   |  |  |

| V <sub>DD</sub>  | Supply Voltage               | 2.7                 | _                      | 3.6                  | V     |                                                                                                                                                              |  |  |

| V <sub>IL1</sub> | Low Level Input<br>Voltage   | -0.3                | _                      | 0.3*V <sub>DD</sub>  | V     |                                                                                                                                                              |  |  |

| V <sub>IH1</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | 5.5                  | V     | For all input pins without analog<br>or oscillator function. For all<br>signal pins on the 8-pin devices.<br>Programmable pull-ups must<br>also be disabled. |  |  |

| V <sub>IH2</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | V <sub>DD</sub> +0.3 | V     | For those pins with analog or<br>oscillator function (20-/28-pin<br>devices only), or when<br>programmable pull-ups are<br>enabled.                          |  |  |

| V <sub>OL1</sub> | Low Level Output<br>Voltage  | -                   | -                      | 0.4                  | V     | I <sub>OL</sub> = 2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                               |  |  |

| V <sub>OH1</sub> | High Level Output<br>Voltage | 2.4                 | -                      | _                    | V     | I <sub>OH</sub> = -2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                              |  |  |

**z**ilog<sup>°</sup>

## 251

## **Ordering Information**

Order the Z8 Encore! XP<sup>®</sup> F082A Series from Zilog<sup>®</sup>, using the following part numbers. For more information on ordering, please consult your local Zilog sales office. The Zilog website (<u>www.zilog.com</u>) lists all regional offices and provides additional Z8 Encore! XP product information.

| Part Number                                                                                                                       | Flash | RAM  | NVDS | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|-----------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082A Series with 8 KB Flash, 10-Bit Analog-to-Digital Converter<br>Standard Temperature: 0 °C to 70°C |       |      |      |           |            |                     |                     |                |            |                    |                     |

| Z8F082APB020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082APB020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          |                    | PDIP 20-pin package |

| Z8F082ASJ020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperature: -40 °C to 105 °C                                                                                            |       |      |      |           |            |                     |                     |                |            |                    |                     |

| Z8F082APB020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082AQB020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F082ASJ020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging                                                                                          |       |      |      |           |            |                     |                     |                |            |                    |                     |

263

page erase 147 page select register 150, 151 FPS register 150, 151 FSTAT register 150

## G

GATED mode 85 general-purpose I/O 37 GPIO 7, 37 alternate functions 38 architecture 38 control register definitions 45 input data sample timing 234 interrupts 45 port A-C pull-up enable sub-registers 50, 51 port A-H address registers 46 port A-H alternate function sub-registers 47 port A-H control registers 46 port A-H data direction sub-registers 47 port A-H high drive enable sub-registers 49 port A-H input data registers 51 port A-H output control sub-registers 48 port A-H output data registers 52 port A-H stop mode recovery sub-registers 49 port availability by device 37 port input timing 235 port output timing 236

## Η

H 202 HALT 204 halt mode 34, 204 hexadecimal number prefix/suffix 202

## I

I2C 7 IM 201 immediate data 201 immediate operand prefix 202 **INC 203** increment 203 increment word 203 **INCW 203** indexed 201 indirect address prefix 202 indirect register 201 indirect register pair 201 indirect working register 201 indirect working register pair 201 infrared encoder/decoder (IrDA) 117 Instruction Set 199 instruction set. eZ8 CPU 199 instructions ADC 203 ADCX 203 ADD 203 **ADDX 203** AND 205 **ANDX 205** arithmetic 203 **BCLR 204** BIT 204 bit manipulation 204 block transfer 204 **BRK 206 BSET 204** BSWAP 204, 206 **BTJ 206 BTJNZ 206 BTJZ 206 CALL 206** CCF 204 CLR 205 COM 205 CP 203 CPC 203 **CPCX 203** CPU control 204 **CPX 203** DA 203 **DEC 203 DECW 203**

DI 204