# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 128 x 8                                                   |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f041ash020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Port A–C Input Data Registers51Port A–D Output Data Register52LED Drive Enable Register52LED Drive Level High Register53LED Drive Level Low Register53                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt Controller 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Interrupt Vector Listing55Architecture57Operation57Master Interrupt Enable57Interrupt Vectors and Priority58Interrupt Assertion59Watchdog Timer Interrupt Assertion59Watchdog Timer Interrupt Assertion59Interrupt Request 0 Register Definitions60Interrupt Request 1 Register61Interrupt Request 2 Register62IRQ0 Enable High and Low Bit Registers63IRQ2 Enable High and Low Bit Registers65Interrupt Edge Select Register66Shared Interrupt Select Register66Interrupt Control Register66 |

| Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Architecture69Operation70Timer Operating Modes70Reading the Timer Count Values82Timer Pin Signal Operation82Timer Control Register Definitions83Timer 0–1 Control Registers83Timer 0–1 High and Low Byte Registers87Timer 0-1 PWM High and Low Byte Registers88                                                                                                                                                                                                                               |

| Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Operation    91      Watchdog Timer Refresh    92                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## **Address Space**

The eZ8 CPU can access the following three distinct address spaces:

- 1. The Register File contains addresses for the general-purpose registers and the eZ8 CPU, peripheral, and general-purpose I/O port control registers.

- 2. The Program Memory contains addresses for all memory locations having executable code and/or data.

- 3. The Data Memory contains addresses for all memory locations that contain data only.

These three address spaces are covered briefly in the following subsections. For more information on eZ8 CPU and its address space, refer to eZ8 CPU Core User Manual (UM0128) available for download at www.zilog.com.

## **Register File**

The Register File address space in the Z8 Encore!<sup>®</sup> MCU is 4 KB (4096 bytes). The Register File is composed of two sections: control registers and general-purpose registers. When instructions are executed, registers defined as sources are read, and registers defined as destinations are written. The architecture of the eZ8 CPU allows all general-purpose registers to function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

The upper 256 bytes of the 4 KB Register File address space are reserved for control of the eZ8 CPU, the on-chip peripherals, and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256 B control register section are reserved (unavailable). Reading from a reserved Register File address returns an undefined value. Writing to reserved Register File addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address 000H in the Register File address space. The Z8 Encore! XP<sup>®</sup> F082A Series devices contain 256 B to 1 KB of on-chip RAM. Reading from Register File addresses outside the available RAM addresses (and not within the control register address space) returns an undefined value. Writing to these Register File addresses produces no effect.

## **Program Memory**

The eZ8 CPU supports 64 KB of Program Memory address space. The Z8 Encore! XP F082A Series devices contain 1 KB to 8 KB of on-chip Flash memory in the Program Memory address space, depending on the device. Reading from Program Memory

# Zilog <sub>19</sub>

## **Register Map**

Table 7 provides the address map for the Register File of the Z8 Encore! XP<sup>®</sup> F082A Series devices. Not all devices and package styles in the Z8 Encore! XP F082A Series support the ADC, or all of the GPIO Ports. Consider registers for unimplemented peripherals as Reserved.

#### Table 7. Register File Address Map

| Address (Hex) | Register Description              | Mnemonic      | Reset (Hex) | Page No |

|---------------|-----------------------------------|---------------|-------------|---------|

| General-Purpo | se RAM                            |               |             |         |

| Z8F082A/Z8F0  | 81A Devices                       |               |             |         |

| 000–3FF       | General-Purpose Register File RAM | _             | XX          |         |

| 400–EFF       | Reserved                          | —             | XX          |         |

| Z8F042A/Z8F0  | 41A Devices                       |               |             |         |

| 000–3FF       | General-Purpose Register File RAM | _             | XX          |         |

| 400–EFF       | Reserved                          | _             | XX          |         |

| Z8F022A/Z8F0  | 21A Devices                       |               |             |         |

| 000–1FF       | General-Purpose Register File RAM | _             | XX          |         |

| 200–EFF       | Reserved                          | —             | XX          |         |

| Z8F012A/Z8F0  | 11A Devices                       |               |             |         |

| 000–0FF       | General-Purpose Register File RAM | _             | XX          |         |

| 100–EFF       | Reserved                          | —             | XX          |         |

| Timer 0       |                                   |               |             |         |

| F00           | Timer 0 High Byte                 | T0H           | 00          | 87      |

| F01           | Timer 0 Low Byte                  | TOL           | 01          | 87      |

| F02           | Timer 0 Reload High Byte          | T0RH          | FF          | 88      |

| F03           | Timer 0 Reload Low Byte           | T0RL          | FF          | 88      |

| F04           | Timer 0 PWM High Byte             | T0PWMH        | 00          | 88      |

| F05           | Timer 0 PWM Low Byte              | <b>T0PWML</b> | 00          | 89      |

| F06           | Timer 0 Control 0                 | TOCTLO        | 00          | 83      |

| F07           | Timer 0 Control 1                 | T0CTL1        | 00          | 84      |

| Timer 1       |                                   |               |             |         |

| F08           | Timer 1 High Byte                 | T1H           | 00          | 87      |

| F09           | Timer 1 Low Byte                  | T1L           | 01          | 87      |

| F0A           | Timer 1 Reload High Byte          | T1RH          | FF          | 88      |

<mark>z</mark>ilog<sup>°</sup>

#### 44

| Port   | Pin | Mnemonic          | Alternate Function Description            | Alternate<br>Function Select<br>Register AFS1 | Alternate<br>Function<br>Select Register<br>AFS2 |

|--------|-----|-------------------|-------------------------------------------|-----------------------------------------------|--------------------------------------------------|

| Port A | PA0 | TOIN              | Timer 0 Input                             | AFS1[0]: 0                                    | AFS2[0]: 0                                       |

|        |     | Reserved          |                                           | AFS1[0]: 0                                    | AFS2[0]: 1                                       |

|        |     | Reserved          |                                           | AFS1[0]: 1                                    | AFS2[0]: 0                                       |

|        |     | TOOUT             | Timer 0 Output Complement                 | AFS1[0]: 1                                    | AFS2[0]: 1                                       |

|        | PA1 | TOOUT             | Timer 0 Output                            | AFS1[1]: 0                                    | AFS2[1]: 0                                       |

|        |     | Reserved          |                                           | AFS1[1]: 0                                    | AFS2[1]: 1                                       |

|        |     | CLKIN             | External Clock Input                      | AFS1[1]: 1                                    | AFS2[1]: 0                                       |

|        |     | Analog Functions* | ADC Analog Input/VREF                     | AFS1[1]: 1                                    | AFS2[1]: 1                                       |

|        | PA2 | DE0               | UART 0 Driver Enable                      | AFS1[2]: 0                                    | AFS2[2]: 0                                       |

|        |     | RESET             | External Reset                            | AFS1[2]: 0                                    | AFS2[2]: 1                                       |

|        |     | T1OUT             | Timer 1 Output                            | AFS1[2]: 1                                    | AFS2[2]: 0                                       |

|        |     | Reserved          |                                           | AFS1[2]: 1                                    | AFS2[2]: 1                                       |

|        | PA3 | CTS0              | UART 0 Clear to Send                      | AFS1[3]: 0                                    | AFS2[3]: 0                                       |

|        |     | COUT              | Comparator Output                         | AFS1[3]: 0                                    | AFS2[3]: 1                                       |

|        |     | T1IN              | Timer 1 Input                             | AFS1[3]: 1                                    | AFS2[3]: 0                                       |

|        |     | Analog Functions* | ADC Analog Input/LPO Input (P)            | AFS1[3]: 1                                    | AFS2[3]: 1                                       |

|        | PA4 | RXD0              | UART 0 Receive Data                       | AFS1[4]: 0                                    | AFS2[4]: 0                                       |

|        |     | Reserved          |                                           | AFS1[4]: 0                                    | AFS2[4]: 1                                       |

|        |     | Reserved          |                                           | AFS1[4]: 1                                    | AFS2[4]: 0                                       |

|        |     | Analog Functions* | ADC/Comparator Input (N)/LPO<br>Input (N) | AFS1[4]: 1                                    | AFS2[4]: 1                                       |

|        | PA5 | TXD0              | UART 0 Transmit Data                      | AFS1[5]: 0                                    | AFS2[5]: 0                                       |

|        |     | T10UT             | Timer 1 Output Complement                 | AFS1[5]: 0                                    | AFS2[5]: 1                                       |

|        |     | Reserved          |                                           | AFS1[5]: 1                                    | AFS2[5]: 0                                       |

|        |     | Analog Functions* | ADC/Comparator Input (P) LPO<br>Output    | AFS1[5]: 1                                    | AFS2[5]: 1                                       |

|        |     |                   |                                           |                                               |                                                  |

#### Table 15. Port Alternate Function Mapping (8-Pin Parts)

\*Analog Functions include ADC inputs, ADC reference, comparator inputs and LPO ports.

**Note:** Also, alternate function selection as described in Port A–D Alternate Function Sub-Registers on page 47 must be enabled.

## Timers

These Z8 Encore! XP<sup>®</sup> F082A Series products contain two 16-bit reloadable timers that can be used for timing, event counting, or generation of pulse-width modulated (PWM) signals. The timers' feature include:

- 16-bit reload counter.

- Programmable prescaler with prescale values from 1 to 128.

- PWM output generation.

- Capture and compare capability.

- External input pin for timer input, clock gating, or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency.

- Timer output pin.

- Timer interrupt.

In addition to the timers described in this chapter, the Baud Rate Generator of the UART (if unused) may also provide basic timing functionality. For information on using the Baud Rate Generator as an additional timer, see Universal Asynchronous Receiver/Transmitter on page 97.

## Architecture

Figure 9 on page 70 displays the architecture of the timers.

zilog

Timer Reload Low Byte register occurs, the temporary holding register value is written to the Timer High Byte register. This operation allows simultaneous updates of the 16-bit Timer Reload value.

In COMPARE mode, the Timer Reload High and Low Byte registers store the 16-bit Compare value.

#### Table 52. Timer 0–1 Reload High Byte Register (TxRH)

| BITS  | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------------|-----|-----|-----|-----|-----|-----|-----|

| FIELD |            |     |     | TF  | RH  |     |     |     |

| RESET | 1          | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W   | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  | F02H, F0AH |     |     |     |     |     |     |     |

Table 53. Timer 0–1 Reload Low Byte Register (TxRL)

| BITS  | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------------|-----|-----|-----|-----|-----|-----|-----|

| FIELD |            | TRL |     |     |     |     |     |     |

| RESET | 1          | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W   | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  | F03H, F0BH |     |     |     |     |     |     |     |

TRH and TRL—Timer Reload Register High and Low

These two bytes form the 16-bit Reload value, {TRH[7:0], TRL[7:0]}. This value sets the maximum count value which initiates a timer reload to 0001H. In COMPARE mode, these two bytes form the 16-bit Compare value.

### **Timer 0-1 PWM High and Low Byte Registers**

The Timer 0-1 PWM High and Low Byte (TxPWMH and TxPWML) registers (Table 54 and Table 55) control Pulse-Width Modulator (PWM) operations. These registers also store the Capture values for the CAPTURE and CAPTURE/COMPARE modes.

#### Table 54. Timer 0–1 PWM High Byte Register (TxPWMH)

| BITS  | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|------------|-----|-----|-----|-----|-----|-----|

| FIELD |     |            |     | PW  | MH  |     |     |     |

| RESET | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  |     | F04H, F0CH |     |     |     |     |     |     |

#### WDT Reset in Normal Operation

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Reset Status (RSTSTAT) register is set to 1. For more information on system reset, see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23.

#### WDT Reset in STOP Mode

If configured to generate a Reset when a time-out occurs and the device is in STOP mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Reset Status (RSTSTAT) register are set to 1 following WDT time-out in STOP mode.

#### Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer (WDTCTL) Control register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers. Follow the steps below to unlock the Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte register (WDTU) with the desired time-out value.

- 4. Write the Watchdog Timer Reload High Byte register (WDTH) with the desired time-out value.

- 5. Write the Watchdog Timer Reload Low Byte register (WDTL) with the desired time-out value.

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

## Watchdog Timer Calibration

Due to its extremely low operating current, the Watchdog Timer oscillator is somewhat inaccurate. This variation can be corrected using the calibration data stored in the Flash Information Page (see Table 97 and Table 98 on page 165). Loading these values into the

1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.

IREN—Infrared Encoder/Decoder Enable

0 =Infrared Encoder/Decoder is disabled. UART operates normally.

1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.

#### **UART Status 0 Register**

The UART Status 0 (UxSTAT0) and Status 1(UxSTAT1) registers (Table 63 and Table 64) identify the current UART operating configuration and status.

Table 63. UART Status 0 Register (U0STAT0)

| BITS  | 7   | 6             | 5  | 4  | 3    | 2    | 1   | 0   |

|-------|-----|---------------|----|----|------|------|-----|-----|

| FIELD | RDA | PE            | OE | FE | BRKD | TDRE | TXE | CTS |

| RESET | 0   | 0             | 0  | 0  | 0    | 1    | 1   | Х   |

| R/W   | R   | R R R R R R R |    |    |      |      |     |     |

| ADDR  |     | F41H          |    |    |      |      |     |     |

RDA—Receive Data Available

This bit indicates that the UART Receive Data register has received data. Reading the UART Receive Data register clears this bit.

0 = The UART Receive Data register is empty.

1 = There is a byte in the UART Receive Data register.

PE—Parity Error

This bit indicates that a parity error has occurred. Reading the UART Receive Data register clears this bit.

0 = No parity error has occurred.

1 = A parity error has occurred.

OE—Overrun Error

This bit indicates that an overrun error has occurred. An overrun occurs when new data is received and the UART Receive Data register has not been read. If the RDA bit is reset to 0, reading the UART Receive Data register clears this bit.

- 0 = No overrun error occurred.

- 1 = An overrun error occurred.

FE—Framing Error

This bit indicates that a framing error (no Stop bit following data reception) was detected. Reading the UART Receive Data register clears this bit.

Zilog

Endec, and passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's Baud Rate Generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the Infrared Endec. The Infrared Endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

#### **Transmitting IrDA Data**

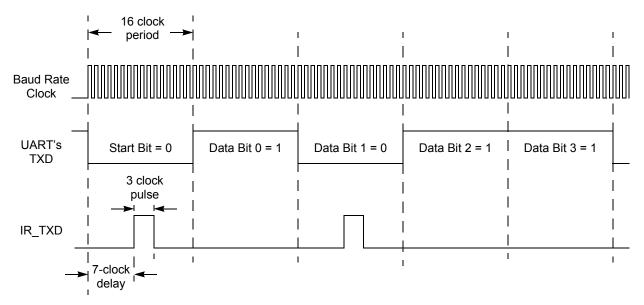

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16 clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16 clock period. If the data to be transmitted is 0, the transmitter first outputs a 7 clock low period, followed by a 3 clock high pulse. Finally, a 6 clock low pulse is output to complete the full 16 clock data period. Figure 17 displays IrDA data transmission. When the Infrared Endec is enabled, the UART's TXD signal is internal to the Z8 Encore! XP<sup>®</sup> F082A Series products while the IR\_TXD signal is output through the TXD pin.

Figure 17. Infrared Data Transmission

## **Flash Memory**

The products in the Z8 Encore! XP<sup>®</sup> F082A Series feature a non-volatile Flash memory of 8 KB (8192), 4 KB (4096), 2 KB (2048 bytes), or 1 KB (1024) with read/write/ erase capability. The Flash Memory can be programmed and erased in-circuit by user code or through the On-Chip Debugger. The features include:

- User controlled read and write protect capability

- Sector-based write protection scheme

- Additional protection schemes against accidental program and erasure

#### Architecture

The Flash memory array is arranged in pages with 512 bytes per page. The 512 byte page is the minimum Flash block size that can be erased. Each page is divided into 8 rows of 64 bytes.

For program or data protection, the Flash memory is also divided into sectors. In the Z8 Encore! XP F082A Series, these sectors are either 1024 bytes (in the 8 KB devices) or 512 bytes (all other memory sizes) in size. Page and sector sizes are not generally equal.

The first 2 bytes of the Flash Program memory are used as Flash Option Bits. For more information about their operation, see Flash Option Bits on page 153.

Table 76 describes the Flash memory configuration for each device in the Z8 Encore! XPF082A Series. Figure 21 displays the Flash memory arrangement.

| Part Number | Flash Size<br>KB (Bytes) | Flash<br>Pages | Program Memory<br>Addresses | Flash Sector<br>Size (Bytes) |

|-------------|--------------------------|----------------|-----------------------------|------------------------------|

| Z8F08xA     | 8 (8192)                 | 16             | 0000H–1FFFH                 | 1024                         |

| Z8F04xA     | 4 (4096)                 | 8              | 0000H-0FFFH                 | 512                          |

| Z8F02xA     | 2 (2048)                 | 4              | 0000H–07FFH                 | 512                          |

| Z8F01xA     | 1 (1024)                 | 2              | 0000H-03FFH                 | 512                          |

#### Table 76. Z8 Encore! XP F082A Series Flash Memory Configurations

## **Non-Volatile Data Storage**

The Z8 Encore! XP<sup>®</sup> F082A Series devices contain a non-volatile data storage (NVDS) element of up to 128 bytes. This memory can perform over 100,000 write cycles.

### Operation

The NVDS is implemented by special purpose Zilog<sup>®</sup> software stored in areas of program memory, which are not user-accessible. These special-purpose routines use the Flash memory to store the data. The routines incorporate a dynamic addressing scheme to maximize the write/erase endurance of the Flash.

Note: Different members of the Z8 Encore! XP F082A Series feature multiple NVDS array sizes. See Z8 Encore! XP<sup>®</sup> F082A Series Family Part Selection Guide on page 3 for details. Also the members containing 8 KB of Flash memory do not include the NVDS feature.

## **NVDS Code Interface**

Two routines are required to access the NVDS: a write routine and a read routine. Both of these routines are accessed with a CALL instruction to a pre-defined address outside of the user-accessible program memory. Both the NVDS address and data are single-byte values. Because these routines disturb the working register set, user code must ensure that any required working register values are preserved by pushing them onto the stack or by changing the working register pointer just prior to NVDS execution.

During both read and write accesses to the NVDS, interrupt service is NOT disabled. Any interrupts that occur during the NVDS execution must take care not to disturb the working register and existing stack contents or else the array may become corrupted. Disabling interrupts before executing NVDS operations is recommended.

Use of the NVDS requires 15 bytes of available stack space. Also, the contents of the working register set are overwritten.

For correct NVDS operation, the Flash Frequency Registers must be programmed based on the system clock frequency (see Flash Operation Timing Using the Flash Frequency Registers on page 145).

#### **Byte Write**

To write a byte to the NVDS array, the user code must first push the address, then the data byte onto the stack. The user code issues a CALL instruction to the address of the byte-write routine (0x10B3). At the return from the sub-routine, the write status byte

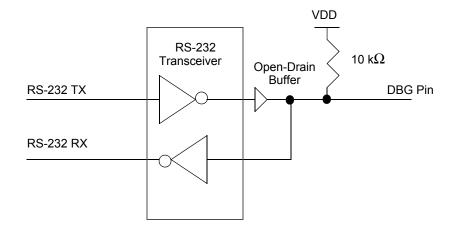

#### Figure 25. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (2)

#### **DEBUG Mode**

The operating characteristics of the devices in DEBUG mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions.

- The system clock operates unless in STOP mode.

- All enabled on-chip peripherals operate unless in STOP mode.

- Automatically exits HALT mode.

- Constantly refreshes the Watchdog Timer, if enabled.

#### **Entering DEBUG Mode**

The operating characteristics of the devices entering DEBUG mode are:

- The device enters DEBUG mode after the eZ8 CPU executes a BRK (Breakpoint) instruction.

- If the DBG pin is held Low during the final clock cycle of system reset, the part enters DEBUG mode immediately (20-/28-pin products only).

- **Note:** Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an Autobaud sequence (see OCD Auto-Baud Detector/Generator on page 176).

High. Because of the open-drain nature of the DBG pin, the host can send a Serial Break to the OCD even if the OCD is transmitting a character.

### OCD Unlock Sequence (8-Pin Devices Only)

Because of pin-sharing on the 8-pin device, an unlock sequence must be performed to access the DBG pin. If this sequence is not completed during a system reset, then the PA0/DBG pin functions only as a GPIO pin.

The following sequence unlocks the DBG pin:

- 1. Hold PA2/RESET Low.

- 2. Wait 5ms for the internal reset sequence to complete.

- 3. Send the following bytes serially to the debug pin:

```

DBG \leftarrow 80H (autobaud)

DBG \leftarrow EBH

DBG \leftarrow 5AH

DBG \leftarrow 70H

DBG \leftarrow CDH (32-bit unlock key)

```

4. Release PA2/RESET. The PA0/DBG pin is now identical in function to that of the DBG pin on the 20-/28-pin device. To enter DEBUG mode, re-autobaud and write 80H to the OCD control register (see On-Chip Debugger Commands on page 179).

**Caution:** Between Step 3 and Step 4, there is an interval during which the 8-pin device is neither in RESET nor DEBUG mode. If a device has been erased or has not yet been programmed, all program memory bytes contain FFH. The CPU interprets this as an illegal instruction, so some irregular behavior can occur before entering DEBUG mode, and the register values after entering DEBUG mode differs from their specified reset values. However, none of these irregularities prevent programming the Flash memory. Before beginning system debug, it is recommended that some legal code be programmed into the 8-pin device, and that a RESET occurs.

#### **Breakpoints**

Execution Breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the On-Chip Debugger. If Breakpoints are enabled, the OCD enters DEBUG mode and idles the eZ8 CPU. If Breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

zilog

194

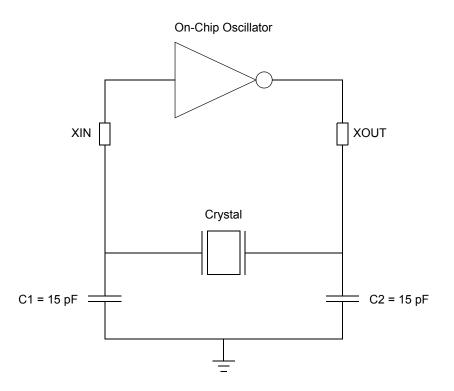

Figure 27 displays a recommended configuration for connection with an external fundamental-mode, parallel-resonant crystal operating at 20 MHz. Recommended 20 MHz crystal specifications are provided in Table 110. Printed circuit board layout must add no more than 4 pF of stray capacitance to either the X<sub>IN</sub> or X<sub>OUT</sub> pins. If oscillation does not occur, reduce the values of capacitors C<sub>1</sub> and C<sub>2</sub> to decrease loading.

#### Figure 27. Recommended 20 MHz Crystal Oscillator Configuration

| Table 110. Recommended Crystal Oscillator Specifications |

|----------------------------------------------------------|

|----------------------------------------------------------|

| Parameter                           | Value       | Units | Comments |

|-------------------------------------|-------------|-------|----------|

| Frequency                           | 20          | MHz   |          |

| Resonance                           | Parallel    |       |          |

| Mode                                | Fundamental |       |          |

| Series Resistance (R <sub>S</sub> ) | 60          | Ω     | Maximum  |

| Load Capacitance (C <sub>L</sub> )  | 30          | pF    | Maximum  |

| Shunt Capacitance (C <sub>0</sub> ) | 7           | pF    | Maximum  |

| Drive Level                         | 1           | mW    | Maximum  |

# zilog

## **Internal Precision Oscillator**

The internal precision oscillator (IPO) is designed for use without external components. You can either manually trim the oscillator for a non-standard frequency or use the automatic factory-trimmed version to achieve a 5.53 MHz frequency. IPO features include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8 kHz (contains both a fast and a slow mode)

- Trimmed through Flash option bits with user override

- Elimination of crystals or ceramic resonators in applications where very high timing accuracy is not required

## Operation

An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed the oscillator frequency is stable and does not require subsequent calibration. Trimming is performed during manufacturing and is not necessary for you to repeat unless a frequency other than 5.53 MHz (fast mode) or 32.8 kHz (slow mode) is required. This trimming is done at +30 °C and a supply voltage of 3.3 V, so accuracy of this operating point is optimal.

If not used, the IPO can be disabled by the Oscillator Control register (see Oscillator Control Register Definitions on page 190).

By default, the oscillator frequency is set by the factory trim value stored in the write-protected Flash information page. However, the user code can override these trim values as described in Trim Bit Address Space on page 158.

Select one of two frequencies for the oscillator: 5.53 MHz and 32.8 kHz, using the OSCSEL bits in the Oscillator Control on page 187.

<mark>z</mark>ilog<sup>°</sup>

| 211 |

|-----|

| Assembly        | Symbolic<br>Operation                                        | Address Mode                    |       | Opcode(s) | Flags                          |   |   |   |   |   | _ Fetch | Instr. |

|-----------------|--------------------------------------------------------------|---------------------------------|-------|-----------|--------------------------------|---|---|---|---|---|---------|--------|

| Mnemonic        |                                                              | dst                             | src   | (Hex)     | С                              | Ζ | S | ۷ | D | Н | Cycles  |        |

| LDC dst, src    | $dst \gets src$                                              | r                               | Irr   | C2        | -                              | _ | - | - | _ | - | 2       | 5      |

|                 |                                                              | lr                              | Irr   | C5        | -                              |   |   |   |   |   | 2       | 9      |

|                 |                                                              | Irr                             | r     | D2        | -                              |   |   |   |   |   | 2       | 5      |

| LDCI dst, src   | $dst \leftarrow src$                                         | lr                              | Irr   | C3        | -                              | - | - | - | - | - | 2       | 9      |

|                 | r ← r + 1<br>rr ← rr + 1                                     | Irr                             | Ir    | D3        | -                              |   |   |   |   |   | 2       | 9      |

| LDE dst, src    | $dst \gets src$                                              | r                               | Irr   | 82        | -                              | _ | - | - | _ | - | 2       | 5      |

|                 |                                                              | Irr                             | r     | 92        | -                              |   |   |   |   |   | 2       | 5      |

| LDEI dst, src   | $dst \gets src$                                              | lr                              | Irr   | 83        | _                              | _ | - | - | - | _ | 2       | 9      |

|                 | r ← r + 1<br>rr ← rr + 1                                     | Irr                             | lr    | 93        | -                              |   |   |   |   |   | 2       | 9      |

| LDWX dst, src   | $dst \gets src$                                              | ER                              | ER    | 1FE8      | _                              | _ | _ | _ | _ | _ | 5       | 4      |

| LDX dst, src    | $dst \gets src$                                              | r                               | ER    | 84        | -                              | - | - | - | - | - | 3       | 2      |

|                 |                                                              | lr                              | ER    | 85        | -                              |   |   |   |   |   | 3       | 3      |

|                 |                                                              | R                               | IRR   | 86        | -                              |   |   |   |   |   | 3       | 4      |

|                 |                                                              | IR                              | IRR   | 87        | -                              |   |   |   |   |   | 3       | 5      |

|                 |                                                              | r                               | X(rr) | 88        | -                              |   |   |   |   |   | 3       | 4      |

|                 |                                                              | X(rr)                           | r     | 89        | -                              |   |   |   |   |   | 3       | 4      |

|                 |                                                              | ER                              | r     | 94        | -                              |   |   |   |   |   | 3       | 2      |

|                 |                                                              | ER                              | Ir    | 95        | -                              |   |   |   |   |   | 3       | 3      |

|                 |                                                              | IRR                             | R     | 96        | -                              |   |   |   |   |   | 3       | 4      |

|                 |                                                              | IRR                             | IR    | 97        | -                              |   |   |   |   |   | 3       | 5      |

|                 |                                                              | ER                              | ER    | E8        | -                              |   |   |   |   |   | 4       | 2      |

|                 |                                                              | ER                              | IM    | E9        | -                              |   |   |   |   |   | 4       | 2      |

| LEA dst, X(src) | $dst \gets src + X$                                          | r                               | X(r)  | 98        | _                              | _ | _ | _ | - | _ | 3       | 3      |

|                 |                                                              | rr                              | X(rr) | 99        | -                              |   |   |   |   |   | 3       | 5      |

| MULT dst        | dst[15:0] ←<br>dst[15:8] * dst[7:0]                          | RR                              |       | F4        | -                              | _ | _ | - | - | - | 2       | 8      |

| NOP             | No operation                                                 |                                 |       | 0F        | _                              | _ | _ | _ | - | _ | 1       | 2      |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined | of the result of the operation. |       |           | 0 = Reset to 0<br>1 = Set to 1 |   |   |   |   |   |         |        |

#### Table 124. eZ8 CPU Instruction Summary (Continued)

**z**ilog<sup>°</sup>

## 215

| Assembly        | Symbolic<br>Operation                                         | Address Mode |          | Opcode(s) | Flags |              |   |           |   |   | Fetch | Instr. |

|-----------------|---------------------------------------------------------------|--------------|----------|-----------|-------|--------------|---|-----------|---|---|-------|--------|

| Mnemonic        |                                                               | dst          | src      | (Hex)     | С     | Ζ            | S | ۷         | D | Н |       |        |

| XOR dst, src    | $dst \gets dst \ XOR \ src$                                   | r            | r        | B2        | -     | *            | * | 0         | _ | - | 2     | 3      |

|                 |                                                               | r            | lr       | B3        | -     |              |   |           |   |   | 2     | 4      |

|                 |                                                               | R            | R        | B4        | -     |              |   |           |   |   | 3     | 3      |

|                 |                                                               | R            | IR       | B5        | -     |              |   |           |   |   | 3     | 4      |

|                 |                                                               | R            | IM       | B6        | -     |              |   |           |   |   | 3     | 3      |

|                 |                                                               | IR           | IM       | B7        | -     |              |   |           |   |   | 3     | 4      |

| XORX dst, src   | $dst \gets dst \ XOR \ src$                                   | ER           | ER       | B8        | -     | *            | * | 0         | _ | - | 4     | 3      |

|                 |                                                               | ER           | IM       | B9        | -     |              |   |           |   |   | 4     | 3      |

| Flags Notation: | * = Value is a function of<br>– = Unaffected<br>X = Undefined | the result   | of the o | peration. | -     | : Re<br>: Se |   | to (<br>1 | C |   |       |        |

#### Table 124. eZ8 CPU Instruction Summary (Continued)

|                           | V <sub>DD</sub> = 2.7 V to 3.6 V                                              |              |                      |          |       |                                                                  |  |  |  |

|---------------------------|-------------------------------------------------------------------------------|--------------|----------------------|----------|-------|------------------------------------------------------------------|--|--|--|

|                           |                                                                               |              | Maximum <sup>2</sup> | _        |       |                                                                  |  |  |  |

| Symbol                    | Parameter                                                                     | Typical $^1$ | Std Temp             | Ext Temp | Units | Conditions                                                       |  |  |  |

| I <sub>DD</sub> Stop      | Supply Current in STOP<br>Mode                                                | 0.1          |                      |          | μA    | No peripherals enabled. All pins driven to $V_{DD}$ or $V_{SS}.$ |  |  |  |

| I <sub>DD</sub> Halt      | Supply Current in HALT<br>Mode (with all<br>peripherals disabled)             | 35           | 55                   | 65       | μA    | 32 kHz                                                           |  |  |  |

|                           |                                                                               | 520          |                      |          | μA    | 5.5 MHz                                                          |  |  |  |

|                           |                                                                               | 2.1          | 2.85                 | 2.85     | mA    | 20 MHz                                                           |  |  |  |

| I <sub>DD</sub>           | Supply Current in                                                             | 2.8          |                      |          | mA    | 32 kHz                                                           |  |  |  |

|                           | ACTIVE Mode (with all peripherals disabled)                                   | 4.5          | 5.2                  | 5.2      | mA    | 5.5 MHz                                                          |  |  |  |

|                           |                                                                               | 5.5          | 6.5                  | 6.5      | mA    | 10 MHz                                                           |  |  |  |

|                           |                                                                               | 7.9          | 11.5                 | 11.5     | mA    | 20 MHz                                                           |  |  |  |

| I <sub>DD</sub> WDT       | Watchdog Timer Supply<br>Current                                              | 0.9          | 1.0                  | 1.1      | μA    |                                                                  |  |  |  |

| I <sub>DD</sub><br>XTAL   | Crystal Oscillator<br>Supply Current                                          | 40           |                      |          | μA    | 32 kHz                                                           |  |  |  |

|                           |                                                                               | 230          |                      |          | μA    | 4 MHz                                                            |  |  |  |

|                           |                                                                               | 760          |                      |          | μA    | 20 MHz                                                           |  |  |  |

| I <sub>DD</sub> IPO       | Internal Precision<br>Oscillator Supply<br>Current                            | 350          | 500                  | 550      | μA    |                                                                  |  |  |  |

| I <sub>DD</sub> VBO       | Voltage Brownout and<br>Low-Voltage Detect<br>Supply Current                  | 50           |                      |          | μA    | For 20-/28-pin devices<br>(VBO only); See Notes 4                |  |  |  |

|                           |                                                                               |              |                      |          |       | For 8-pin devices; See<br>Notes 4                                |  |  |  |

| I <sub>DD</sub> ADC       | Analog to Digital<br>Converter Supply<br>Current (with External<br>Reference) | 2.8          | 3.1                  | 3.2      | mA    | 32 kHz                                                           |  |  |  |

|                           |                                                                               | 3.1          | 3.6                  | 3.7      | mA    | 5.5 MHz                                                          |  |  |  |

|                           |                                                                               | 3.3          | 3.7                  | 3.8      | mA    | 10 MHz                                                           |  |  |  |

|                           |                                                                               | 3.7          | 4.2                  | 4.3      | mA    | 20 MHz                                                           |  |  |  |

| I <sub>DD</sub><br>ADCRef | ADC Internal Reference<br>Supply Current                                      | 0            |                      |          | μA    | See Notes 4                                                      |  |  |  |

| I <sub>DD</sub> CMP       | Comparator supply<br>Current                                                  | 150          | 180                  | 190      | μA    | See Notes 4                                                      |  |  |  |

### Table 128. Power Consumption

zilog

|                   | Parameter         | V <sub>DD</sub> | = 2.7 V to   |            |       |                                                                           |  |

|-------------------|-------------------|-----------------|--------------|------------|-------|---------------------------------------------------------------------------|--|

| Symbol            |                   | Minimum         | Typical      | Maximum    | Units | Conditions                                                                |  |

| T <sub>AERR</sub> | Temperature Error |                 | <u>+</u> 0.5 | <u>+</u> 2 | °C    | Over the range +20 °C<br>to +30 °C (as<br>measured by ADC) <sup>1</sup>   |  |

|                   |                   |                 | <u>+</u> 1   | <u>+</u> 5 | °C    | Over the range +0 °C<br>to +70 °C (as<br>measured by ADC)                 |  |

|                   |                   |                 | <u>+</u> 2   | <u>+</u> 7 | °C    | Over the range +0 °C<br>to +105 °C (as<br>measured by ADC)                |  |

|                   |                   |                 | <u>+</u> 7   |            | °C    | Over the range -40 °C<br>to +105 °C (as<br>measured by ADC)               |  |

| T <sub>AERR</sub> | Temperature Error |                 | TBD          |            | °C    | Over the range -40 °C<br>to +105 °C (as<br>measured by<br>comparator)     |  |

| t <sub>WAKE</sub> | Wakeup Time       |                 | 80           | 100        | μs    | Time required for<br>Temperature Sensor<br>to stabilize after<br>enabling |  |

#### **Table 138. Temperature Sensor Electrical Characteristics**

<sup>1</sup>Devices are factory calibrated at for maximal accuracy between +20 °C and +30 °C, so the sensor is maximally accurate in that range. User re-calibration for a different temperature range is possible and increases accuracy near the new calibration point.

### General Purpose I/O Port Input Data Sample Timing

Figure 34 displays timing of the GPIO Port input sampling. The input value on a GPIO Port pin is sampled on the rising edge of the system clock. The Port value is available to the eZ8 CPU on the second rising clock edge following the change of the Port value.