Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 128 x 8                                                   |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f041asj020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Overview**

Zilog's Z8 Encore!<sup>®</sup> MCU family of products are the first in a line of Zilog<sup>®</sup> microcontroller products based upon the 8-bit eZ8 CPU. Zilog's Z8 Encore! XP<sup>®</sup> F082A Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8<sup>®</sup> instructions. The rich peripheral set of the Z8 Encore! XP F082A Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

### **Features**

The key features of Z8 Encore! XP F082A Series products include:

- 20 MHz eZ8 CPU

- 1 KB, 2 KB, 4 KB, or 8 KB Flash memory with in-circuit programming capability

- 256 B, 512 B, or 1 KB register RAM

- Up to 128 B non-volatile data storage (NVDS)

- Internal precision oscillator trimmed to  $\pm 1\%$  accuracy

- External crystal oscillator, operating up to 20 MHz

- Optional 8-channel, 10-bit analog-to-digital converter (ADC)

- Optional on-chip temperature sensor

- On-chip analog comparator

- Optional on-chip low-power operational amplifier (LPO)

- Full-duplex UART

- The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared Data Association (IrDA)-compliant infrared encoder/decoders, integrated with UART

- Two enhanced 16-bit timers with capture, compare, and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- Up to 20 vectored interrupts

- 6 to 25 I/O pins depending upon package

#### **Universal Asynchronous Receiver/Transmitter**

The full-duplex universal asynchronous receiver/transmitter (UART) is included in all Z8 Encore! XP package types. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

#### Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE and COMPARE, PWM SINGLE OUTPUT and PWM DUAL OUTPUT modes.

#### General-Purpose Input/Output

The Z8 Encore! XP F082A Series features 6 to 25 port pins (Ports A–D) for general- purpose input/output (GPIO). The number of GPIO pins available is a function of package, and each pin is individually programmable. 5 V tolerant input pins are available on all I/Os on 8-pin devices and most I/Os on other package types.

#### **Direct LED Drive**

The 20- and 28-pin devices support controlled current sinking output pins capable of driving LEDs without the need for a current limiting resistor. These LED drivers are independently programmable to four different intensity levels.

#### **Flash Controller**

The Flash Controller programs and erases Flash memory. The Flash Controller supports several protection mechanisms against accidental program and erasure, as well as factory serialization and read protection.

#### Non-Volatile Data Storage

The non-volatile data storage (NVDS) uses a hybrid hardware/software scheme to implement a byte programmable data memory and is capable of over 100,000 write cycles.

**Note:** Devices with 8 KB Flash memory do not include the NVDS feature.

# Zilog <sub>19</sub>

# **Register Map**

Table 7 provides the address map for the Register File of the Z8 Encore! XP<sup>®</sup> F082A Series devices. Not all devices and package styles in the Z8 Encore! XP F082A Series support the ADC, or all of the GPIO Ports. Consider registers for unimplemented peripherals as Reserved.

#### Table 7. Register File Address Map

| Address (Hex) | Register Description              | Mnemonic      | Reset (Hex) | Page No |

|---------------|-----------------------------------|---------------|-------------|---------|

| General-Purpo | se RAM                            |               |             |         |

| Z8F082A/Z8F0  | 81A Devices                       |               |             |         |

| 000–3FF       | General-Purpose Register File RAM | _             | XX          |         |

| 400–EFF       | Reserved                          | —             | XX          |         |

| Z8F042A/Z8F0  | 41A Devices                       |               |             |         |

| 000–3FF       | General-Purpose Register File RAM | _             | XX          |         |

| 400–EFF       | Reserved                          | _             | XX          |         |

| Z8F022A/Z8F0  | 21A Devices                       |               |             |         |

| 000–1FF       | General-Purpose Register File RAM | _             | XX          |         |

| 200–EFF       | Reserved                          | —             | XX          |         |

| Z8F012A/Z8F0  | 11A Devices                       |               |             |         |

| 000–0FF       | General-Purpose Register File RAM | _             | XX          |         |

| 100–EFF       | Reserved                          | —             | XX          |         |

| Timer 0       |                                   |               |             |         |

| F00           | Timer 0 High Byte                 | T0H           | 00          | 87      |

| F01           | Timer 0 Low Byte                  | TOL           | 01          | 87      |

| F02           | Timer 0 Reload High Byte          | T0RH          | FF          | 88      |

| F03           | Timer 0 Reload Low Byte           | T0RL          | FF          | 88      |

| F04           | Timer 0 PWM High Byte             | T0PWMH        | 00          | 88      |

| F05           | Timer 0 PWM Low Byte              | <b>T0PWML</b> | 00          | 89      |

| F06           | Timer 0 Control 0                 | TOCTLO        | 00          | 83      |

| F07           | Timer 0 Control 1                 | T0CTL1        | 00          | 84      |

| Timer 1       |                                   |               |             |         |

| F08           | Timer 1 High Byte                 | T1H           | 00          | 87      |

| F09           | Timer 1 Low Byte                  | T1L           | 01          | 87      |

| F0A           | Timer 1 Reload High Byte          | T1RH          | FF          | 88      |

# **Low-Power Modes**

The Z8 Encore! XP F082A Series products contain power-saving features. The highest level of power reduction is provided by the STOP mode, in which nearly all device functions are powered down. The next lower level of power reduction is provided by the HALT mode, in which the CPU is powered down.

Further power savings can be implemented by disabling individual peripheral blocks while in Active mode (defined as being in neither STOP nor HALT mode).

### **STOP Mode**

Executing the eZ8 CPU's STOP instruction places the device into STOP mode, powering down all peripherals except the Voltage Brownout detector, the Low-power Operational Amplifier and the Watchdog Timer. These three blocks may also be disabled for additional power savings. Specifically, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; XIN and XOUT (if previously enabled) are disabled, and PA0/PA1 revert to the states programmed by the GPIO registers.

- System clock is stopped.

- eZ8 CPU is stopped.

- Program counter (PC) stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control register.

- If enabled, the Watchdog Timer logic continues to operate.

- If enabled for operation in STOP mode by the associated Flash Option Bit, the Voltage Brownout protection circuit continues to operate.

- Low-power operational amplifier continues to operate if enabled by the Power Control register to do so.

- All other on-chip peripherals are idle.

To minimize current in STOP mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP mode using Stop Mode Recovery. For more information on Stop Mode Recovery, see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23.

#### Table 46. Shared Interrupt Select Register (IRQSS)

| BITS  | 7     | 6     | 5                   | 4  | 3  | 2 | 1 | 0 |  |

|-------|-------|-------|---------------------|----|----|---|---|---|--|

| FIELD | PA7VS | PA6CS | Reserved            |    |    |   |   |   |  |

| RESET | 0     | 0     | 0 0 0 0 0           |    | 0  |   |   |   |  |

| R/W   | R/W   | R/W   | R/W R/W R/W R/W R/W |    |    |   |   |   |  |

| ADDR  |       |       |                     | FC | EH |   |   |   |  |

PA7VS—PA7/LVD Selection

0 = PA7 is used for the interrupt for PA7VS interrupt request.

1 = The LVD is used for the interrupt for PA7VS interrupt request.

PA6CS—PA6/Comparator Selection

0 = PA6 is used for the interrupt for PA6CS interrupt request.

1 = The Comparator is used for the interrupt for PA6CS interrupt request.

Reserved—Must be 0.

#### **Interrupt Control Register**

The Interrupt Control (IRQCTL) register (Table 47) contains the master enable bit for all interrupts.

| Table 47. | Interrupt | Control | Register | (IRQCTL) |

|-----------|-----------|---------|----------|----------|

|-----------|-----------|---------|----------|----------|

| BITS  | 7    | 6        | 5             | 4  | 3  | 2 | 1 | 0 |  |

|-------|------|----------|---------------|----|----|---|---|---|--|

| FIELD | IRQE | Reserved |               |    |    |   |   |   |  |

| RESET | 0    | 0        | 0 0 0 0 0 0   |    |    |   |   | 0 |  |

| R/W   | R/W  | R        | R R R R R R R |    |    |   |   |   |  |

| ADDR  |      |          |               | FC | FH |   |   |   |  |

IRQE—Interrupt Request Enable

This bit is set to 1 by executing an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, Reset or by a direct register write of a 0 to this bit.

- 0 = Interrupts are disabled.

- 1 = Interrupts are enabled.

Reserved—Must be 0.

#### WDT Reset in Normal Operation

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Reset Status (RSTSTAT) register is set to 1. For more information on system reset, see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23.

#### WDT Reset in STOP Mode

If configured to generate a Reset when a time-out occurs and the device is in STOP mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Reset Status (RSTSTAT) register are set to 1 following WDT time-out in STOP mode.

#### Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer (WDTCTL) Control register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers. Follow the steps below to unlock the Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte register (WDTU) with the desired time-out value.

- 4. Write the Watchdog Timer Reload High Byte register (WDTH) with the desired time-out value.

- 5. Write the Watchdog Timer Reload Low Byte register (WDTL) with the desired time-out value.

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

### Watchdog Timer Calibration

Due to its extremely low operating current, the Watchdog Timer oscillator is somewhat inaccurate. This variation can be corrected using the calibration data stored in the Flash Information Page (see Table 97 and Table 98 on page 165). Loading these values into the

**Caution:** *The 24-bit WDT Reload Value must not be set to a value less than* 000004H.

#### Table 58. Watchdog Timer Reload Upper Byte Register (WDTU)

| BITS       | 7             | 6          | 5             | 4             | 3             | 2            | 1   | 0 |  |  |

|------------|---------------|------------|---------------|---------------|---------------|--------------|-----|---|--|--|

| FIELD      | LD WDTU       |            |               |               |               |              |     |   |  |  |

| RESET      | 00H           |            |               |               |               |              |     |   |  |  |

| R/W        | R/W*          |            |               |               |               |              |     |   |  |  |

| ADDR       | FF1H          |            |               |               |               |              |     |   |  |  |

| R/W* - Rea | d returns the | current WD | C count value | Write sets th | ne appropriat | e Reload Val | ue. |   |  |  |

R/W\* - Read returns the current WDT count value. Write sets the appropriate Reload Value.

WDTU—WDT Reload Upper Byte

Most-significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value.

#### Table 59. Watchdog Timer Reload High Byte Register (WDTH)

| BITS       | 7              | 6           | 5            | 4              | 3           | 2            | 1 | 0 |  |  |  |

|------------|----------------|-------------|--------------|----------------|-------------|--------------|---|---|--|--|--|

| FIELD      |                | WDTH        |              |                |             |              |   |   |  |  |  |

| RESET      | 04H            |             |              |                |             |              |   |   |  |  |  |

| R/W        | R/W*           |             |              |                |             |              |   |   |  |  |  |

| ADDR       | FF2H           |             |              |                |             |              |   |   |  |  |  |

| R/W* - Rea | ad returns the | current WDT | count value. | Write sets the | appropriate | Reload Value |   |   |  |  |  |

WDTH—WDT Reload High Byte

Middle byte, Bits[15:8], of the 24-bit WDT reload value.

#### Table 60. Watchdog Timer Reload Low Byte Register (WDTL)

| BITS       | 7             | 6           | 5            | 4             | 3             | 2           | 1  | 0 |  |  |  |

|------------|---------------|-------------|--------------|---------------|---------------|-------------|----|---|--|--|--|

| FIELD      |               | WDTL        |              |               |               |             |    |   |  |  |  |

| RESET      | 00H           |             |              |               |               |             |    |   |  |  |  |

| R/W        | R/W*          |             |              |               |               |             |    |   |  |  |  |

| ADDR       | FF3H          |             |              |               |               |             |    |   |  |  |  |

| R/W* - Rea | d returns the | current WDT | count value. | Write sets th | e appropriate | Reload Valu | e. |   |  |  |  |

WDTL—WDT Reload Low

Least significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value.

0 = No framing error occurred. 1 = A framing error occurred.

BRKD—Break Detect

This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data register clears this bit. 0 = No break occurred.

1 = A break occurred.

TDRE—Transmitter Data Register Empty

This bit indicates that the UART Transmit Data register is empty and ready for additional data. Writing to the UART Transmit Data register resets this bit.

0 = Do not write to the UART Transmit Data register.

1 = The UART Transmit Data register is ready to receive an additional byte to be transmitted.

TXE—Transmitter Empty

This bit indicates that the transmit shift register is empty and character transmission is finished.

0 = Data is currently transmitting.

1 = Transmission is complete.

$CTS - \overline{CTS}$  signal

When this bit is read it returns the level of the  $\overline{\text{CTS}}$  signal. This signal is active Low.

#### **UART Status 1 Register**

This register contains multiprocessor control and status bits.

Table 64. UART Status 1 Register (U0STAT1)

| BITS  | 7 | 6                    | 5 | 4 | 3   | 2   | 1 | 0 |  |  |

|-------|---|----------------------|---|---|-----|-----|---|---|--|--|

| FIELD |   | Reserved NEWFRM MPRX |   |   |     |     |   |   |  |  |

| RESET | 0 | 0                    | 0 | 0 | 0   | 0   | 0 | 0 |  |  |

| R/W   | R | R                    | R | R | R/W | R/W | R | R |  |  |

| ADDR  |   | F44H                 |   |   |     |     |   |   |  |  |

Reserved—Must be 0.

NEWFRM—Status bit denoting the start of a new frame. Reading the UART Receive Data register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame.

1 = The current byte is the first data byte of a new frame.

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control register may be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in ADC Control/Status Register 1.

- Set CEN to 1 to start the conversions.

- 4. When the first conversion in continuous operation is complete (after 5129 system clock cycles, plus the 40 cycles for power-up, if necessary), the ADC control logic performs the following operations:

- CEN resets to 0 to indicate the first conversion is complete. CEN remains 0 for all subsequent conversions in continuous operation.

- An interrupt request is sent to the Interrupt Controller to indicate the conversion is complete.

- 5. The ADC writes a new data result every 256 system clock cycles. For each completed conversion, the ADC control logic performs the following operations:

- Writes the 13-bit two's complement result to {ADCD\_H[7:0], ADCD L[7:3]}.

- Sends an interrupt request to the Interrupt Controller denoting conversion complete.

- 6. To disable continuous conversion, clear the CONT bit in the ADC Control Register to 0.

#### Interrupts

The ADC is able to interrupt the CPU when a conversion has been completed. When the ADC is disabled, no new interrupts are asserted; however, an interrupt pending when the ADC is disabled is not cleared.

#### **Calibration and Compensation**

The Z8 Encore! XP<sup>®</sup> F082A Series ADC is factory calibrated for offset error and gain error, with the compensation data stored in Flash memory. Alternatively, you can perform your own calibration, storing the values into Flash themselves. Thirdly, the user code can perform a manual offset calibration during DIFFERENTIAL mode operation.

zilog

#

**Caution:** Although the ADC can be used without the gain and offset compensation, it does exhibit non-unity gain. Designing the ADC with sub-unity gain reduces noise across the ADC range but requires the ADC results to be scaled by a factor of 8/7.

#### **ADC Compensation Details**

High efficiency assembly code that performs this compensation is available for download on <u>www.zilog.com</u>. The following is a bit-specific description of the ADC compensation process used by this code.

The following data bit definitions are used:

0-9, a-f = bit indices in hexadecimal

s = sign bit

v = overflow bit

- = unused

#### Input Data

| MS             | βB           |     |   |     |     | LS | В |   |   |             |                                                   |

|----------------|--------------|-----|---|-----|-----|----|---|---|---|-------------|---------------------------------------------------|

| sba9           | 876          | 5 5 | 4 | 3 2 | 2 1 | 0  | - | - | v | (ADC)       | ADC Output Word; if $v = 1$ , the data is invalid |

|                |              |     | S | 6 5 | 54  | 3  | 2 | 1 | 0 |             | Offset Correction Byte                            |

| <u>s s s s</u> | <u>s 7 6</u> | 5 5 | 4 | 3 2 | 2 1 | 0  | 0 | 0 | 0 | (Offset)    | Offset Byte shifted to align with ADC data        |

| sedc           | b a S        | 98  | 7 | 6 5 | 54  | 3  | 2 | 1 | 0 | (Gain)<br>] | Gain Correction Word                              |

|                |              |     |   |     |     |    |   |   |   | ]           |                                                   |

| [              |              |     |   |     |     |    |   |   |   | 1           |                                                   |

zilog<sup>°</sup>

#### ANAIN[3:0]—Analog Input Select

These bits select the analog input for conversion. Not all Port pins in this list are available in all packages for the Z8 Encore! XP<sup>®</sup> F082A Series. For information on port pins available with each package style, see Pin Description on page 9. Do not enable unavailable analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.

For the reserved values, all input switches are disabled to avoid leakage or other undesirable operation. ADC samples taken with reserved bit settings are undefined.

SINGLE-ENDED:

- 0000 = ANA0 (transimpedance amp output when enabled)

- 0001 = ANA1 (transimpedance amp inverting input)

- 0010 = ANA2 (transimpedance amp non-inverting input)

- 0011 = ANA3

- 0100 = ANA4

- 0101 = ANA5

- 0110 = ANA6

- 0111 = ANA7

- 1000 = Reserved

- 1001 = Reserved

- 1010 = Reserved

- 1011 = Reserved

- 1100 = Hold transimpedance input nodes (ANA1 and ANA2) to ground.

- 1101 = Reserved

- 1110 = Temperature Sensor.

- 1111 = Reserved.

DIFFERENTIAL (non-inverting input and inverting input respectively):

- 0000 = ANA0 and ANA10001 = ANA2 and ANA30010 = ANA4 and ANA50011 = ANA1 and ANA00100 = ANA3 and ANA20101 = ANA5 and ANA40110 = ANA6 and ANA50111 = ANA0 and ANA50111 = ANA0 and ANA21000 = ANA0 and ANA31001 = ANA0 and ANA41010 = ANA0 and ANA51011 = Reserved1100 = Reserved1101 = Reserved1101 = Reserved1110 = Reserved

- 1111 = Manual Offset Calibration Mode

| Info Page<br>Address | Memory<br>Address | Usage                                        |

|----------------------|-------------------|----------------------------------------------|

| 5C                   | FE5C              | Randomized Lot ID Byte 23                    |

| 5D                   | FE5D              | Randomized Lot ID Byte 22                    |

| 5E                   | FE5E              | Randomized Lot ID Byte 21                    |

| 5F                   | FE5F              | Randomized Lot ID Byte 20                    |

| 61                   | FE61              | Randomized Lot ID Byte 19                    |

| 62                   | FE62              | Randomized Lot ID Byte 18                    |

| 64                   | FE64              | Randomized Lot ID Byte 17                    |

| 65                   | FE65              | Randomized Lot ID Byte 16                    |

| 67                   | FE67              | Randomized Lot ID Byte 15                    |

| 68                   | FE68              | Randomized Lot ID Byte 14                    |

| 6A                   | FE6A              | Randomized Lot ID Byte 13                    |

| 6B                   | FE6B              | Randomized Lot ID Byte 12                    |

| 6D                   | FE6D              | Randomized Lot ID Byte 11                    |

| 6E                   | FE6E              | Randomized Lot ID Byte 10                    |

| 70                   | FE70              | Randomized Lot ID Byte 9                     |

| 71                   | FE71              | Randomized Lot ID Byte 8                     |

| 73                   | FE73              | Randomized Lot ID Byte 7                     |

| 74                   | FE74              | Randomized Lot ID Byte 6                     |

| 76                   | FE76              | Randomized Lot ID Byte 5                     |

| 77                   | FE77              | Randomized Lot ID Byte 4                     |

| 79                   | FE79              | Randomized Lot ID Byte 3                     |

| 7A                   | FE7A              | Randomized Lot ID Byte 2                     |

| 7C                   | FE7C              | Randomized Lot ID Byte 1                     |

| 7D                   | FE7D              | Randomized Lot ID Byte 0 (least significant) |

#### Table 102. Randomized Lot ID Locations (Continued)

168

zilog

- **-** 18

- **Read Register (09H)**—The Read Register command reads data from the Register File. Data can be read 1–256 bytes at a time (256 bytes can be read by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for all the data values.

```

DBG \leftarrow 09H

DBG \leftarrow {4'h0,Register Address[11:8]

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-256 data bytes

```

• Write Program Memory (0AH)—The Write Program Memory command writes data to Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

```

DBG \leftarrow 0AH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

• **Read Program Memory (0BH)**—The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1–65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for the data.

```

DBG \leftarrow 0BH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

• Write Data Memory (0CH)—The Write Data Memory command writes data to Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

```

DBG \leftarrow 0CH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

```

**z**ilog<sup>°</sup>

205

#### Table 119. CPU Control Instructions (Continued)

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| SCF      | _        | Set Carry Flag         |

| SRP      | SIC      | Set Register Pointer   |

| STOP     | _        | STOP Mode              |

| WDT      | _        | Watchdog Timer Refresh |

#### Table 120. Load Instructions

| Mnemonic | Operands    | Instruction                                                             |

|----------|-------------|-------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                   |

| LD       | dst, src    | Load                                                                    |

| LDC      | dst, src    | Load Constant to/from Program Memory                                    |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                  |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                     |

| LDX      | dst, src    | Load using Extended Addressing                                          |

| LEA      | dst, X(src) | Load Effective Address                                                  |

| POP      | dst         | Рор                                                                     |

| POPX     | dst         | Pop using Extended Addressing                                           |

| PUSH     | src         | Push                                                                    |

| PUSHX    | src         | Push using Extended Addressing                                          |

|          |             |                                                                         |

#### Table 121. Logical Instructions

| Mnemonic | Operands | Instruction                           |

|----------|----------|---------------------------------------|

| AND      | dst, src | Logical AND                           |

| ANDX     | dst, src | Logical AND using Extended Addressing |

| COM      | dst      | Complement                            |

| OR       | dst, src | Logical OR                            |

zilog

207

#### Table 123. Rotate and Shift Instructions (Continued)

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| SRA      | dst      | Shift Right Arithmetic |

| SRL      | dst      | Shift Right Logical    |

| SWAP     | dst      | Swap Nibbles           |

## eZ8 CPU Instruction Summary

Table 124 summarizes the eZ8 CPU instructions. The table identifies the addressing modes employed by the instruction, the effect upon the Flags register, the number of CPU clock cycles required for the instruction fetch, and the number of CPU clock cycles required for the instruction.

| Assembly<br>Mnemonic | Symbolic<br>Operation                                      | Addres        | Address Mode |                    |   |          | FI | ags       | Fetch | Instr. |   |        |

|----------------------|------------------------------------------------------------|---------------|--------------|--------------------|---|----------|----|-----------|-------|--------|---|--------|

|                      |                                                            | dst           | src          | Opcode(s)<br>(Hex) | С | Ζ        | S  | ۷         | D     | Н      |   | Cycles |

| ADC dst, src         | $dst \gets dst + src + C$                                  | r             | r            | 12                 | * | *        | *  | *         | 0     | *      | 2 | 3      |

|                      |                                                            | r             | lr           | 13                 | - |          |    |           |       |        | 2 | 4      |

|                      |                                                            | R             | R            | 14                 | - |          |    |           |       |        | 3 | 3      |

|                      |                                                            | R             | IR           | 15                 | - |          |    |           |       |        | 3 | 4      |

|                      |                                                            | R             | IM           | 16                 | - |          |    |           |       |        | 3 | 3      |

|                      |                                                            | IR            | IM           | 17                 | - |          |    |           |       |        | 3 | 4      |

| ADCX dst, src        | $dst \gets dst + src + C$                                  | ER            | ER           | 18                 | * | *        | *  | *         | 0     | *      | 4 | 3      |

|                      |                                                            | ER            | IM           | 19                 | - |          |    |           |       |        | 4 | 3      |

| ADD dst, src         | $dst \gets dst + src$                                      | r             | r            | 02                 | * | *        | *  | *         | 0     | *      | 2 | 3      |

|                      |                                                            | r             | lr           | 03                 | _ |          |    |           |       |        | 2 | 4      |

|                      |                                                            | R             | R            | 04                 | - |          |    |           |       |        | 3 | 3      |

|                      |                                                            | R             | IR           | 05                 | - |          |    |           |       |        | 3 | 4      |

|                      |                                                            | R             | IM           | 06                 | _ |          |    |           |       |        | 3 | 3      |

|                      |                                                            | IR            | IM           | 07                 | _ |          |    |           |       |        | 3 | 4      |

| ADDX dst, src        | $dst \gets dst + src$                                      | ER            | ER           | 08                 | * | *        | *  | *         | 0     | *      | 4 | 3      |

|                      |                                                            | ER            | IM           | 09                 | - |          |    |           |       |        | 4 | 3      |

| Flags Notation:      | * = Value is a function<br>– = Unaffected<br>X = Undefined | of the result | of the o     | peration.          |   | Re<br>Se |    | to (<br>1 | )     |        |   |        |

Table 124. eZ8 CPU Instruction Summary

**z**ilog<sup>°</sup>

# 215

| Assembly<br>Mnemonic | Symbolic<br>Operation                                         | Address Mode |          | Opcode(s) |   |              | FI | ags       | Fetch | Instr. |   |        |

|----------------------|---------------------------------------------------------------|--------------|----------|-----------|---|--------------|----|-----------|-------|--------|---|--------|

|                      |                                                               | dst          | src      | (Hex)     | С | Ζ            | S  | ۷         | D     | Н      |   | Cycles |

| XOR dst, src         | $dst \gets dst \ XOR \ src$                                   | r            | r        | B2        | - | *            | *  | 0         | _     | -      | 2 | 3      |

|                      |                                                               | r            | lr       | B3        | - |              |    |           |       |        | 2 | 4      |

|                      |                                                               | R            | R        | B4        | - |              |    |           |       |        | 3 | 3      |

|                      |                                                               | R            | IR       | B5        | - |              |    |           |       |        | 3 | 4      |

|                      |                                                               | R            | IM       | B6        | - |              |    |           |       |        | 3 | 3      |

|                      |                                                               | IR           | IM       | B7        | - |              |    |           |       |        | 3 | 4      |

| XORX dst, src        | $dst \gets dst \ XOR \ src$                                   | ER           | ER       | B8        | - | *            | *  | 0         | _     | -      | 4 | 3      |

|                      |                                                               | ER           | IM       | B9        | - |              |    |           |       |        | 4 | 3      |

| Flags Notation:      | * = Value is a function of<br>– = Unaffected<br>X = Undefined | the result   | of the o | peration. | - | : Re<br>: Se |    | to (<br>1 | C     |        |   |        |

#### Table 124. eZ8 CPU Instruction Summary (Continued)

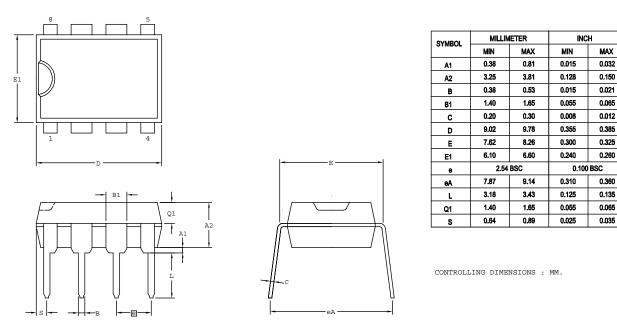

# Packaging

Figure 39 displays the 8-pin Plastic Dual Inline Package (PDIP) available for Z8 Encore!  $XP^{\textcircled{R}}$  F082A Series devices.

Figure 39. 8-Pin Plastic Dual Inline Package (PDIP)

264

**DJNZ 206** EI 204 **HALT 204 INC 203 INCW 203 IRET 206** JP 206 LD 205 LDC 205 LDCI 204, 205 LDE 205 LDEI 204 LDX 205 LEA 205 logical 205 **MULT 203** NOP 204 OR 205 **ORX 206** POP 205 **POPX 205** program control 206 **PUSH 205** PUSHX 205 **RCF 204 RET 206** RL 206 **RLC 206** rotate and shift 206 RR 206 **RRC 206** SBC 203 SCF 204, 205 SRA 207 SRL 207 **SRP 205 STOP 205** SUB 203 SUBX 203 **SWAP 207** TCM 204 **TCMX 204** TM 204 TMX 204

**TRAP 206** Watchdog Timer refresh 205 XOR 206 **XORX 206** instructions, eZ8 classes of 202 interrupt control register 67 interrupt controller 55 architecture 55 interrupt assertion types 58 interrupt vectors and priority 58 operation 57 register definitions 60 software interrupt assertion 59 interrupt edge select register 66 interrupt request 0 register 60 interrupt request 1 register 61 interrupt request 2 register 62 interrupt return 206 interrupt vector listing 55 interrupts **UART 105** IR 201 lr 201 IrDA architecture 117 block diagram 117 control register definitions 120 operation 117 receiving data 119 transmitting data 118 **IRET 206** IRQ0 enable high and low bit registers 62 IRQ1 enable high and low bit registers 63 IRQ2 enable high and low bit registers 65 **IRR 201** Irr 201

### J

JP 206 jump, conditional, relative, and relative conditional 206