# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 4KB (4K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 128 x 8                                                      |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f042ahh020ec    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| General Purpose I/O Port Output Timing | 236 |

|----------------------------------------|-----|

| On-Chip Debugger Timing                | 237 |

| UART Timing                            | 238 |

| Packaging                              | 241 |

| Ordering Information                   | 251 |

| Index                                  | 261 |

| Customer Support                       | 271 |

#### Table 2. Signal Descriptions (Continued)

| Signal Mnemonic  | I/O      | Description                                                                       |

|------------------|----------|-----------------------------------------------------------------------------------|

| Power Supply     |          |                                                                                   |

| V <sub>DD</sub>  | Ι        | Digital Power Supply.                                                             |

| AV <sub>DD</sub> | Ι        | Analog Power Supply.                                                              |

| V <sub>SS</sub>  | I        | Digital Ground.                                                                   |

| AV <sub>SS</sub> | Ι        | Analog Ground.                                                                    |

| Note: The AV     | Vee siar | nals are available only in 28-pin packages with ADC. They are replaced by PB6 and |

**Note:** The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

#### **Pin Characteristics**

Table 3 describes the characteristics for each pin available on the Z8 Encore! XP F082A Series 20- and 28-pin devices. Data in Table 3 is sorted alphabetically by the pin symbol mnemonic.

Table 4 on page 14 provides detailed information about the characteristics for each pin available on the Z8 Encore! XP F082A Series 8-pin devices.

Note:

All six I/O pins on the 8-pin packages are 5 V-tolerant (unless the pull-up devices are enabled). The column in Table 3 below describes 5 V-tolerance for the 20- and 28-pin packages only.

#### Table 3. Pin Characteristics (20- and 28-pin Devices)

| Symbol<br>Mnemonic | Direction | Reset<br>Direction | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal Pull-<br>up<br>or Pull-down | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output | 5 V<br>Tolerance                        |

|--------------------|-----------|--------------------|---------------------------------------|--------------------|--------------------------------------|------------------------------|----------------------|-----------------------------------------|

| AVDD               | N/A       | N/A                | N/A                                   | N/A                | N/A                                  | N/A                          | N/A                  | N/A                                     |

| AVSS               | N/A       | N/A                | N/A                                   | N/A                | N/A                                  | N/A                          | N/A                  | NA                                      |

| DBG                | I/O       | I                  | N/A                                   | Yes                | Yes                                  | Yes                          | Yes                  | No                                      |

| PA[7:0]            | I/O       | I                  | N/A                                   | Yes                | Programmable<br>Pull-up              | Yes                          | Yes,<br>Programmable | PA[7:2]<br>unless<br>pullups<br>enabled |

| PB[7:0]            | I/O       | I                  | N/A                                   | Yes                | Programmable<br>Pull-up              | Yes                          | Yes,<br>Programmable | PB[7:6]<br>unless<br>pullups<br>enabled |

**z**ilog<sup>°</sup>

#### Table 7. Register File Address Map (Continued)

| Address (Hex)   | Register Description                  | Mnemonic | Reset (Hex) | Page No                  |

|-----------------|---------------------------------------|----------|-------------|--------------------------|

| FDF             | Port D Output Data                    | PDOUT    | 00          | 47                       |

| FE0–FEF         | Reserved                              | _        | XX          |                          |

| Watchdog Time   | er (WDT)                              |          |             |                          |

| FF0             | Reset Status (Read-only)              | RSTSTAT  | X0          | 30                       |

|                 | Watchdog Timer Control (Write-only)   | WDTCTL   | N/A         | 94                       |

| FF1             | Watchdog Timer Reload Upper Byte      | WDTU     | 00          | 95                       |

| FF2             | Watchdog Timer Reload High Byte       | WDTH     | 04          | 95                       |

| FF3             | Watchdog Timer Reload Low Byte        | WDTL     | 00          | 95                       |

| FF4–FF5         | Reserved                              | —        | XX          |                          |

| Trim Bit Contro | bl                                    |          |             |                          |

| FF6             | Trim Bit Address                      | TRMADR   | 00          | 155                      |

| FF7             | Trim Bit Data                         | TRMDR    | 00          | 156                      |

| Flash Memory    | Controller                            |          |             |                          |

| FF8             | Flash Control                         | FCTL     | 00          | 149                      |

| FF8             | Flash Status                          | FSTAT    | 00          | 150                      |

| FF9             | Flash Page Select                     | FPS      | 00          | 151                      |

|                 | Flash Sector Protect                  | FPROT    | 00          | 151                      |

| FFA             | Flash Programming Frequency High Byte | FFREQH   | 00          | 152                      |

| FFB             | Flash Programming Frequency Low Byte  | FFREQL   | 00          | 152                      |

| eZ8 CPU         |                                       |          |             |                          |

| FFC             | Flags                                 |          | XX          | Refer to eZ8             |

| FFD             | Register Pointer                      | RP       | XX          | CPU Core                 |

| FFE             | Stack Pointer High Byte               | SPH      | XX          | —User Manual<br>(UM0128) |

| FFF             | Stack Pointer Low Byte                | SPL      | XX          | _(010120)                |

| XX=Undefined    |                                       |          |             |                          |

22

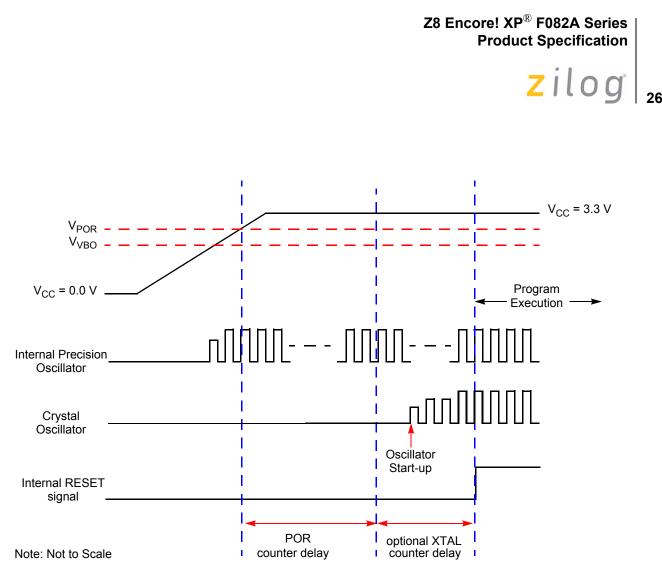

Figure 5. Power-On Reset Operation

#### **Voltage Brownout Reset**

The devices in the Z8 Encore! XP F082A Series provide low Voltage Brownout (VBO) protection. The VBO circuit senses when the supply voltage drops to an unsafe level (below the VBO threshold voltage) and forces the device into the Reset state. While the supply voltage remains below the Power-On Reset voltage threshold ( $V_{POR}$ ), the VBO block holds the device in the Reset.

After the supply voltage again exceeds the Power-On Reset voltage threshold, the device progresses through a full System Reset sequence, as described in the Power-On Reset section. Following Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) register is set to 1. Figure 6 displays Voltage Brownout operation. See Electrical Characteristics on page 221 for the VBO and POR threshold voltages (V<sub>VBO</sub> and V<sub>POR</sub>).

The Voltage Brownout circuit can be either enabled or disabled during STOP mode. Operation during STOP mode is set by the VBO\_AO Flash Option Bit. See Flash Option Bits for information about configuring VBO\_AO.

zilog<sup>®</sup>

| Port   | Pin | Mnemonic    | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------|-----------------------------------------|-----------------------------------------|

| Port A | PA0 | T0IN/T0OUT* | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|        |     | Reserved    |                                         | -                                       |

|        | PA1 | TOOUT       | Timer 0 Output                          | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA2 | DE0         | UART 0 Driver Enable                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA3 | CTS0        | UART 0 Clear to Send                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA4 | RXD0/IRRX0  | UART 0/IrDA 0 Receive Data              | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA5 | TXD0/IRTX0  | UART 0/IrDA 0 Transmit Data             | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA6 | T1IN/T1OUT* | Timer 1 Input/Timer 1 Output Complement | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA7 | T1OUT       | Timer 1 Output                          | -                                       |

|        |     | Reserved    |                                         | -                                       |

#### Table 14. Port Alternate Function Mapping (Non 8-Pin Parts)

**Note:** Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in Port A–D Alternate Function Sub-Registers on page 47 automatically enables the associated alternate function.

\* Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in Timer Pin Signal Operation on page 82.

Follow the steps below for configuring a timer for CAPTURE mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for CAPTURE mode.

- Set the prescale value.

- Set the Capture edge (rising or falling) for the Timer Input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. Clearing these registers allows the software to determine if interrupts were generated by either a capture event or a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

In CAPTURE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **CAPTURE RESTART Mode**

In CAPTURE RESTART mode, the current timer count value is recorded when the acceptable external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte Registers. The timer input is the system clock. The TPOL bit in the Timer Control register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 register is set to indicate the timer interrupt is because of an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED mode. After the first timer reset in GATED mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deassertion and reload events. If appropriate, configure the timer interrupt to be generated only at the input deassertion event or the reload event by setting TICONFIG field of the TxCTL0 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### CAPTURE/COMPARE Mode

In CAPTURE/COMPARE mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte Registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL0 register is set to indicate the timer interrupt is caused by an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 register is cleared to indicate the timer interrupt is not because of an input capture event.

Follow the steps below for configuring a timer for CAPTURE/COMPARE mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for CAPTURE/COMPARE mode.

- Set the prescale value.

- Set the Capture edge (rising or falling) for the Timer Input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

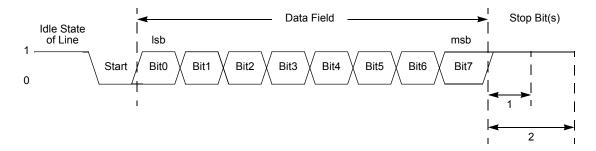

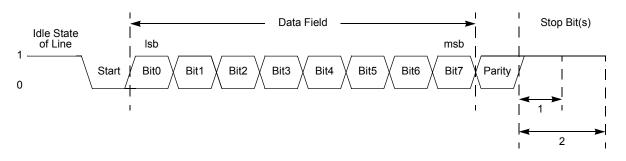

Figure 11. UART Asynchronous Data Format without Parity

Figure 12. UART Asynchronous Data Format with Parity

#### Transmitting Data using the Polled Method

Follow the steps below to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Write to the UART Control 1 register, if MULTIPROCESSOR mode is appropriate, to enable MULTIPROCESSOR (9-bit) mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR mode.

- 5. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR mode is not enabled, and select either even or odd parity (PSEL).

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin.

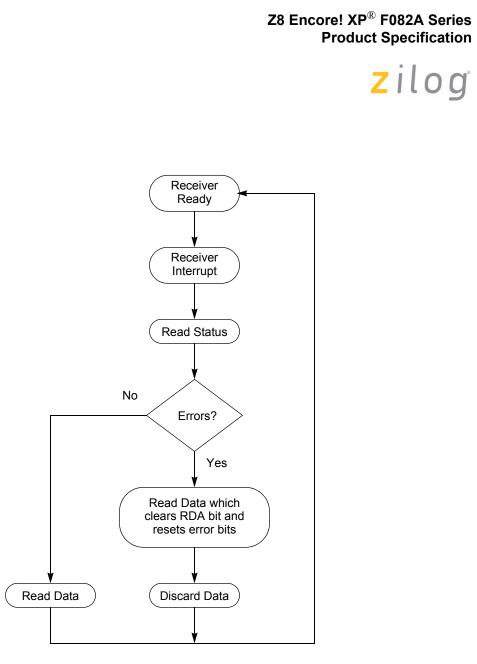

Figure 15. UART Receiver Interrupt Service Routine Flow

#### **Baud Rate Generator Interrupts**

If the baud rate generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud Rate Generator to function as an additional counter if the UART functionality is not employed.

#### **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value

107

# zilog<sup>®</sup> |<sub>11</sub>

The UART data rate is calculated using the following equation:

UART Baud Rate (bits/s) =

$$\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$$

For a given UART data rate, calculate the integer baud rate divisor value using the following equation:

UART Baud Rate Divisor Value (BRG) = Round

$$\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$$

The baud rate error relative to the acceptable baud rate is calculated using the following equation:

UART Baud Rate Error (%) =

$$100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$$

For reliable communication, the UART baud rate error must never exceed 5 percent. Table 70 provides information on the data rate errors for popular baud rates and commonly used crystal oscillator frequencies.

| 10.0 MHz Sy              | stem Clock               |                      |              | 5.5296 MHz System Clock  |                          |                      |              |  |

|--------------------------|--------------------------|----------------------|--------------|--------------------------|--------------------------|----------------------|--------------|--|

| Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) | Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) |  |

| 1250.0                   | N/A                      | N/A                  | N/A          | 1250.0                   | N/A                      | N/A                  | N/A          |  |

| 625.0                    | 1                        | 625.0                | 0.00         | 625.0                    | N/A                      | N/A                  | N/A          |  |

| 250.0                    | 3                        | 208.33               | -16.67       | 250.0                    | 1                        | 345.6                | 38.24        |  |

| 115.2                    | 5                        | 125.0                | 8.51         | 115.2                    | 3                        | 115.2                | 0.00         |  |

| 57.6                     | 11                       | 56.8                 | -1.36        | 57.6                     | 6                        | 57.6                 | 0.00         |  |

| 38.4                     | 16                       | 39.1                 | 1.73         | 38.4                     | 9                        | 38.4                 | 0.00         |  |

| 19.2                     | 33                       | 18.9                 | 0.16         | 19.2                     | 18                       | 19.2                 | 0.00         |  |

| 9.60                     | 65                       | 9.62                 | 0.16         | 9.60                     | 36                       | 9.60                 | 0.00         |  |

| 4.80                     | 130                      | 4.81                 | 0.16         | 4.80                     | 72                       | 4.80                 | 0.00         |  |

| 2.40                     | 260                      | 2.40                 | -0.03        | 2.40                     | 144                      | 2.40                 | 0.00         |  |

| 1.20                     | 521                      | 1.20                 | -0.03        | 1.20                     | 288                      | 1.20                 | 0.00         |  |

| 0.60                     | 1042                     | 0.60                 | -0.03        | 0.60                     | 576                      | 0.60                 | 0.00         |  |

| 0.30                     | 2083                     | 0.30                 | 0.2          | 0.30                     | 1152                     | 0.30                 | 0.00         |  |

|                          |                          |                      |              | -                        |                          |                      |              |  |

#### Table 70. UART Baud Rates

### **Analog-to-Digital Converter**

The analog-to-digital converter (ADC) converts an analog input signal to its digital representation. The features of this sigma-delta ADC include:

- 11-bit resolution in DIFFERENTIAL mode.

- 10-bit resolution in SINGLE-ENDED mode.

- Eight single-ended analog input sources are multiplexed with general-purpose I/O ports.

- 9<sup>th</sup> analog input obtained from temperature sensor peripheral.

- 11 pairs of differential inputs also multiplexed with general-purpose I/O ports.

- Low-power operational amplifier (LPO).

- Interrupt on conversion complete.

- Bandgap generated internal voltage reference with two selectable levels.

- Manual in-circuit calibration is possible employing user code (offset calibration).

- Factory calibrated for in-circuit error compensation.

#### Architecture

Figure 19 displays the major functional blocks of the ADC. An analog multiplexer network selects the ADC input from the available analog pins, ANA0 through ANA7.

The input stage of the ADC allows both differential gain and buffering. The following input options are available:

- Unbuffered input (SINGLE-ENDED and DIFFERENTIAL modes).

- Buffered input with unity gain (SINGLE-ENDED and DIFFERENTIAL modes).

- LPO output with full pin access to the feedback path.

zilog

#### 146

#### Table 77. Flash Code Protection Using the Flash Option Bits

| FWP | Flash Code Protection Description                                                                                                                                                                       |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Programming and erasing disabled for all of Flash Program<br>Memory. In user code programming, Page Erase, and Mass Erase<br>are all disabled. Mass Erase is available through the On-Chip<br>Debugger. |

| 1   | Programming, Page Erase, and Mass Erase are enabled for all of Flash Program Memory.                                                                                                                    |

#### Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, first write the Page Select Register with the target page. Unlock the Flash Controller by making two consecutive writes to the Flash Control register with the values 73H and 8CH, sequentially. The Page Select Register must be rewritten with the target page. If the two Page Select writes do not match, the controller reverts to a locked state. If the two writes match, the selected page becomes active. See Figure 22 on page 144 for details.

After unlocking a specific page, you can enable either Page Program or Erase. Writing the value 95H causes a Page Erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control register locks the Flash Controller. Mass Erase is not allowed in the user code but only in through the Debug Port.

After unlocking a specific page, you can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register cause the active page to revert to a locked state.

#### **Sector Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore!<sup>®</sup> devices are divided into at most 8 sectors. A sector is 1/8 of the total size of the Flash memory, unless this value is smaller than the page size, in which case the sector and page sizes are equal.

The Sector Protect register controls the protection state of each Flash sector. This register is shared with the Page Select Register. It is accessed by writing 73H followed by 5EH to the Flash controller. The next write to the Flash Control Register targets the Sector Protect Register.

The Sector Protect Register is initialized to 0 on reset, putting each sector into an unprotected state. When a bit in the Sector Protect Register is written to 1, the corresponding sector is no longer written or erased by the CPU. External Flash programming through

**z**ilog<sup>®</sup>

#### Flash Status Register

The Flash Status (FSTAT) register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status register shares its Register File address with the Write-only Flash Control register.

Table 79. Flash Status Register (FSTAT)

| BITS  | 7    | 6     | 5     | 4 | 3 | 2 | 1 | 0 |

|-------|------|-------|-------|---|---|---|---|---|

| FIELD | Rese | erved | FSTAT |   |   |   |   |   |

| RESET | 0    | 0     | 0     | 0 | 0 | 0 | 0 | 0 |

| R/W   | R    | R     | R     | R | R | R | R | R |

| ADDR  |      | FF8H  |       |   |   |   |   |   |

Reserved—Must be 0.

FSTAT—Flash Controller Status

000000 = Flash Controller locked

000001 = First unlock command received (73H written)

000010 = Second unlock command received (8CH written)

000011 = Flash Controller unlocked

000100 = Sector protect register selected

001xxx = Program operation in progress

010xxx = Page erase operation in progress

100xxx = Mass erase operation in progress

#### Flash Page Select Register

The Flash Page Select (FPS) register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7 bits given by FPS[6:0] are chosen for program/erase operation.

zilog | 1

#### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a Breakpoint, write 00H to the required break address, overwriting the current instruction. To remove a Breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

#### **Runtime Counter**

The On-Chip Debugger contains a 16-bit Runtime Counter. It counts system clock cycles between Breakpoints. The counter starts counting when the On-Chip Debugger leaves DEBUG mode and stops counting when it enters DEBUG mode again or when it reaches the maximum count of FFFFH.

#### **On-Chip Debugger Commands**

The host communicates to the on-chip debugger by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash Read Protect Option bit (FRP). The Flash Read Protect Option bit prevents the code in memory from being read out of the Z8 Encore! XP F082A Series products. When this option is enabled, several of the OCD commands are disabled. Table 106 on page 184 is a summary of the On-chip debugger commands. Each OCD command is described in further detail in the bulleted list following this table. Table 106 on page 184 also indicates those commands that operate when the device is not in DEBUG mode (normal operation) and those commands that are disabled by programming the Flash Read Protect Option bit.

| Debug Command              | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>mode? | Disabled by<br>Flash Read Protect Option Bit |

|----------------------------|-----------------|---------------------------------------|----------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                   | -                                            |

| Reserved                   | 01H             | -                                     | -                                            |

| Read OCD Status Register   | 02H             | Yes                                   | -                                            |

| Read Runtime Counter       | 03H             | -                                     | -                                            |

| Write OCD Control Register | 04H             | Yes                                   | Cannot clear DBGMODE bit                     |

| Read OCD Control Register  | 05H             | Yes                                   | -                                            |

| Write Program Counter      | 06H             | -                                     | Disabled                                     |

| Read Program Counter       | 07H             | _                                     | Disabled                                     |

zilog

**Caution:** It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! XP F082A Series device ceases functioning and can only be recovered by Power-On-Reset.

#### **Oscillator Control Register Definitions**

#### **Oscillator Control Register**

The Oscillator Control Register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

| BITS  | 7     | 6     | 5     | 4     | 3     | 2      | 1   | 0   |  |

|-------|-------|-------|-------|-------|-------|--------|-----|-----|--|

| FIELD | INTEN | XTLEN | WDTEN | SOFEN | WDFEN | SCKSEL |     |     |  |

| RESET | 1     | 0     | 1     | 0     | 0     | 0      | 0   | 0   |  |

| R/W    | R/W | R/W |  |

| ADDR  |       | F86H  |       |       |       |        |     |     |  |

#### Table 109. Oscillator Control Register (OSCCTL)

INTEN—Internal Precision Oscillator Enable

1 = Internal precision oscillator is enabled

0 = Internal precision oscillator is disabled

XTLEN-Crystal Oscillator Enable; this setting overrides the GPIO register control for PA0 and PA1

1 = Crystal oscillator is enabled

0 = Crystal oscillator is disabled

WDTEN—Watchdog Timer Oscillator Enable

1 = Watchdog Timer oscillator is enabled

0 = Watchdog Timer oscillator is disabled

SOFEN—System Clock Oscillator Failure Detection Enable

1 = Failure detection and recovery of system clock oscillator is enabled

0 = Failure detection and recovery of system clock oscillator is disabled

# zilog

## **Internal Precision Oscillator**

The internal precision oscillator (IPO) is designed for use without external components. You can either manually trim the oscillator for a non-standard frequency or use the automatic factory-trimmed version to achieve a 5.53 MHz frequency. IPO features include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8 kHz (contains both a fast and a slow mode)

- Trimmed through Flash option bits with user override

- Elimination of crystals or ceramic resonators in applications where very high timing accuracy is not required

#### Operation

An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed the oscillator frequency is stable and does not require subsequent calibration. Trimming is performed during manufacturing and is not necessary for you to repeat unless a frequency other than 5.53 MHz (fast mode) or 32.8 kHz (slow mode) is required. This trimming is done at +30 °C and a supply voltage of 3.3 V, so accuracy of this operating point is optimal.

If not used, the IPO can be disabled by the Oscillator Control register (see Oscillator Control Register Definitions on page 190).

By default, the oscillator frequency is set by the factory trim value stored in the write-protected Flash information page. However, the user code can override these trim values as described in Trim Bit Address Space on page 158.

Select one of two frequencies for the oscillator: 5.53 MHz and 32.8 kHz, using the OSCSEL bits in the Oscillator Control on page 187.

**z**ilog<sup>°</sup>

#### 229

### **On-Chip Peripheral AC and DC Electrical Characteristics**

#### Table 131. Power-On Reset and Voltage Brownout Electrical Characteristics and Timing

|                   |                                                                                                                | T <sub>A</sub> = - | 40 °C to +           | 105 °C  |       |                                                                                                       |

|-------------------|----------------------------------------------------------------------------------------------------------------|--------------------|----------------------|---------|-------|-------------------------------------------------------------------------------------------------------|

| Symbol            | Parameter                                                                                                      | Minimum            | Typical <sup>1</sup> | Maximum | Units | Conditions                                                                                            |

| V <sub>POR</sub>  | Power-On Reset<br>Voltage Threshold                                                                            | 2.20               | 2.45                 | 2.70    | V     | V <sub>DD</sub> = V <sub>POR</sub>                                                                    |

| V <sub>VBO</sub>  | Voltage Brownout Reset<br>Voltage Threshold                                                                    | 2.15               | 2.40                 | 2.65    | V     | $V_{DD} = V_{VBO}$                                                                                    |

|                   | $V_{POR}$ to $V_{VBO}$ hysteresis                                                                              |                    | 50                   | 75      | mV    |                                                                                                       |

|                   | Starting V <sub>DD</sub> voltage to<br>ensure valid Power-On<br>Reset.                                         | -                  | $V_{SS}$             | -       | V     |                                                                                                       |

| T <sub>ANA</sub>  | Power-On Reset Analog<br>Delay                                                                                 | -                  | 70                   | -       | μs    | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub> Digital<br>Reset delay follows T <sub>ANA</sub> |

| T <sub>POR</sub>  | Power-On Reset Digital<br>Delay                                                                                |                    | 16                   |         | μs    | 66 Internal Precision<br>Oscillator cycles + IPO<br>startup time (T <sub>IPOST</sub> )                |

| T <sub>POR</sub>  | Power-On Reset Digital<br>Delay                                                                                |                    | 1                    |         | ms    | 5000 Internal Precision<br>Oscillator cycles                                                          |

| T <sub>SMR</sub>  | Stop Mode Recovery<br>with crystal oscillator<br>disabled                                                      |                    | 16                   |         | μs    | 66 Internal Precision<br>Oscillator cycles                                                            |

| T <sub>SMR</sub>  | Stop Mode Recovery<br>with crystal oscillator<br>enabled                                                       |                    | 1                    |         | ms    | 5000 Internal Precision<br>Oscillator cycles                                                          |

| T <sub>VBO</sub>  | Voltage Brownout Pulse<br>Rejection Period                                                                     | _                  | 10                   | -       | μs    | Period of time in which V <sub>DD</sub><br>< V <sub>VBO</sub> without generating<br>a Reset.          |

| T <sub>RAMP</sub> | Time for V <sub>DD</sub> to<br>transition from V <sub>SS</sub> to<br>V <sub>POR</sub> to ensure valid<br>Reset | 0.10               | -                    | 100     | ms    |                                                                                                       |

| T <sub>SMP</sub>  | Stop Mode Recovery pin pulse rejection period                                                                  |                    | 20                   |         | ns    | For any SMR pin or for the Reset pin when it is asserted in STOP mode.                                |

only and are not tested in production.

236

#### General Purpose I/O Port Output Timing

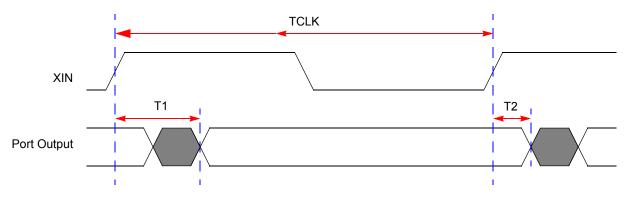

Figure 35 and Table 140 provide timing information for GPIO Port pins.

#### Figure 35. GPIO Port Output Timing

|                |                                     | Delay (ns) |         |  |  |

|----------------|-------------------------------------|------------|---------|--|--|

| Parameter      | Abbreviation                        | Minimum    | Maximum |  |  |

| GPIO Port      | pins                                |            |         |  |  |

| T <sub>1</sub> | XIN Rise to Port Output Valid Delay | _          | 15      |  |  |

| T <sub>2</sub> | XIN Rise to Port Output Hold Time   | 2          | _       |  |  |

#### Table 140. GPIO Port Output Timing

<mark>z</mark>ilog<sup>°</sup>

#### 251

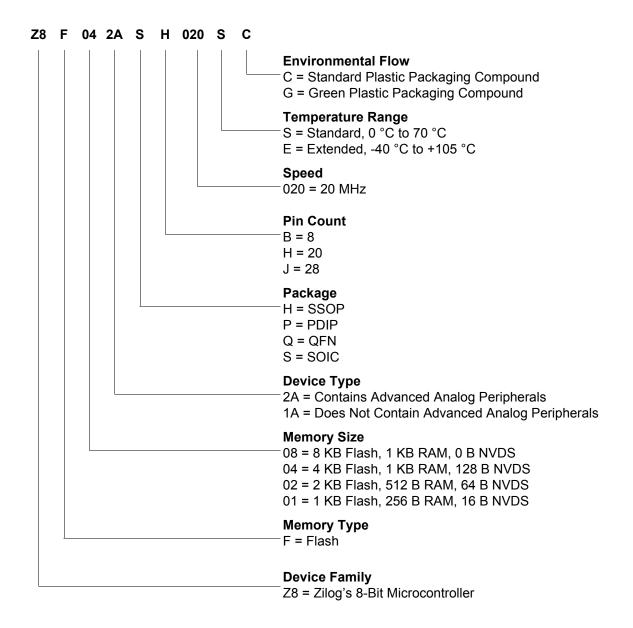

### **Ordering Information**

Order the Z8 Encore! XP<sup>®</sup> F082A Series from Zilog<sup>®</sup>, using the following part numbers. For more information on ordering, please consult your local Zilog sales office. The Zilog website (<u>www.zilog.com</u>) lists all regional offices and provides additional Z8 Encore! XP product information.

| Part Number                                                                                                                       | Flash | RAM  | NVDS | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|-----------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082A Series with 8 KB Flash, 10-Bit Analog-to-Digital Converter<br>Standard Temperature: 0 °C to 70°C |       |      |      |           |            |                     |                     |                |            |                    |                     |

| Z8F082APB020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082APB020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          |                    | PDIP 20-pin package |

| Z8F082ASJ020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperature: -40 °C to 105 °C                                                                                            |       |      |      |           |            |                     |                     |                |            |                    |                     |

| Z8F082APB020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082AQB020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F082ASJ020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging                                                                                          |       |      |      |           |            |                     |                     |                |            |                    |                     |

#### 260

#### Part Number Suffix Designations