## E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 4KB (4K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 128 × 8                                                      |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f042ahh020sc    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Flash Sector Protect Register       1         Flash Frequency High and Low Byte Registers       1                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Flash Option Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53                                                                               |

| Operation11Option Bit Configuration By Reset11Option Bit Types11Reading the Flash Information Page11Flash Option Bit Control Register Definitions11Trim Bit Address Register11Trim Bit Data Register11Flash Option Bit Address Space11Flash Program Memory Address 0000H11Flash Program Memory Address 0001H11Trim Bit Address Space11Trim Bit Address 0000H11Trim Bit Address 0000H11Trim Bit Address 0000H11Trim Bit Address 0001H11Trim Bit Address 0002H11Trim Bit Address 0003H11Trim Bit Address 0004H11 | 53<br>54<br>55<br>55<br>56<br>56<br>56<br>58<br>58<br>58<br>58<br>59<br>59<br>59 |

| Zilog Calibration Data       10         ADC Calibration Data       10         Temperature Sensor Calibration Data       10         Watchdog Timer Calibration Data       10         Serialization Data       10         Randomized Lot Identifier       10                                                                                                                                                                                                                                                     | 61<br>64<br>64<br>65<br>66                                                       |

| Non-Volatile Data Storage 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| NVDS Code Interface       10         Byte Write       10         Byte Read       11                                                                                                                                                                                                                                                                                                                                                                                                                            | 69<br>70<br>71                                                                   |

| On-Chip Debugger1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 74<br>74                                                                         |

**z**ilog<sup>°</sup>

## Table 3. Pin Characteristics (20- and 28-pin Devices) (Continued)

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal Pull-<br>up<br>or Pull-down                    | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                    | 5 V<br>Tolerance                        |

|--------------------|-----------|-----------------------------------|---------------------------------------|--------------------|---------------------------------------------------------|------------------------------|---------------------------------------------------------|-----------------------------------------|

| PC[7:0]            | I/O       | I                                 | N/A                                   | Yes                | Programmable<br>Pull-up                                 | Yes                          | Yes,<br>Programmable                                    | PC[7:3]<br>unless<br>pullups<br>enabled |

| RESET/PD0          | I/O       | I/O <u>(defaults</u><br>to RESET) | Low (in<br>Reset<br>mode)             | Yes (PD0<br>only)  | Programmable<br>for PD0 <u>; always</u><br>on for RESET | Yes                          | Programmable<br>for PD0 <u>; always</u><br>on for RESET | Yes, unless<br>pullups<br>enabled       |

| VDD                | N/A       | N/A                               | N/A                                   | N/A                |                                                         |                              | N/A                                                     | N/A                                     |

| VSS                | N/A       | N/A                               | N/A                                   | N/A                |                                                         |                              | N/A                                                     | N/A                                     |

**Note:** *PB6 and PB7 are available only in those devices without ADC.*

## Table 4. Pin Characteristics (8-Pin Devices)

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                                                      | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal Pull-<br>up<br>or Pull-down            | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                            | 5 V<br>Tolerance                   |

|--------------------|-----------|-------------------------------------------------------------------------|---------------------------------------|--------------------|-------------------------------------------------|------------------------------|-------------------------------------------------|------------------------------------|

| PA0/DBG            | I/O       | I (but can<br>change<br>during reset<br>if key<br>sequence<br>detected) | N/A                                   | Yes                | Programmable<br>Pull-up                         | Yes                          | Yes,<br>Programmable                            | Yes, unless<br>pull-ups<br>enabled |

| PA1                | I/O       | I                                                                       | N/A                                   | Yes                | Programmable<br>Pull-up                         | Yes                          | Yes,<br>Programmable                            | Yes, unless<br>pull-ups<br>enabled |

| RESET/PA2          | I/O       | I/O <u>(defaults</u><br>to RESET)                                       | Low (in<br>Reset<br>mode)             | Yes                | Programmable<br>for PA2; always<br>on for RESET | Yes                          | Programmable<br>for PA2; always<br>on for RESET | Yes, unless<br>pull-ups<br>enabled |

| PA[5:3]            | I/O       | I                                                                       | N/A                                   | Yes                | Programmable<br>Pull-up                         | Yes                          | Yes,<br>Programmable                            | Yes, unless<br>pull-ups<br>enabled |

| V <sub>DD</sub>    | N/A       | N/A                                                                     | N/A                                   | N/A                | N/A                                             | N/A                          | N/A                                             | N/A                                |

| V <sub>SS</sub>    | N/A       | N/A                                                                     | N/A                                   | N/A                | N/A                                             | N/A                          | N/A                                             | N/A                                |

14

# Zilog <sub>19</sub>

## **Register Map**

Table 7 provides the address map for the Register File of the Z8 Encore! XP<sup>®</sup> F082A Series devices. Not all devices and package styles in the Z8 Encore! XP F082A Series support the ADC, or all of the GPIO Ports. Consider registers for unimplemented peripherals as Reserved.

### Table 7. Register File Address Map

| Address (Hex) | Register Description              | Mnemonic      | Reset (Hex) | Page No |

|---------------|-----------------------------------|---------------|-------------|---------|

| General-Purpo | se RAM                            |               |             |         |

| Z8F082A/Z8F0  | 81A Devices                       |               |             |         |

| 000–3FF       | General-Purpose Register File RAM | _             | XX          |         |

| 400–EFF       | Reserved                          | —             | XX          |         |

| Z8F042A/Z8F0  | 41A Devices                       |               |             |         |

| 000–3FF       | General-Purpose Register File RAM | _             | XX          |         |

| 400–EFF       | Reserved                          | _             | XX          |         |

| Z8F022A/Z8F0  | 21A Devices                       |               |             |         |

| 000–1FF       | General-Purpose Register File RAM | _             | XX          |         |

| 200–EFF       | Reserved                          | —             | XX          |         |

| Z8F012A/Z8F0  | 11A Devices                       |               |             |         |

| 000–0FF       | General-Purpose Register File RAM | _             | XX          |         |

| 100–EFF       | Reserved                          | —             | XX          |         |

| Timer 0       |                                   |               |             |         |

| F00           | Timer 0 High Byte                 | T0H           | 00          | 87      |

| F01           | Timer 0 Low Byte                  | TOL           | 01          | 87      |

| F02           | Timer 0 Reload High Byte          | T0RH          | FF          | 88      |

| F03           | Timer 0 Reload Low Byte           | T0RL          | FF          | 88      |

| F04           | Timer 0 PWM High Byte             | T0PWMH        | 00          | 88      |

| F05           | Timer 0 PWM Low Byte              | <b>T0PWML</b> | 00          | 89      |

| F06           | Timer 0 Control 0                 | TOCTLO        | 00          | 83      |

| F07           | Timer 0 Control 1                 | T0CTL1        | 00          | 84      |

| Timer 1       |                                   |               |             |         |

| F08           | Timer 1 High Byte                 | T1H           | 00          | 87      |

| F09           | Timer 1 Low Byte                  | T1L           | 01          | 87      |

| F0A           | Timer 1 Reload High Byte          | T1RH          | FF          | 88      |

## Architecture

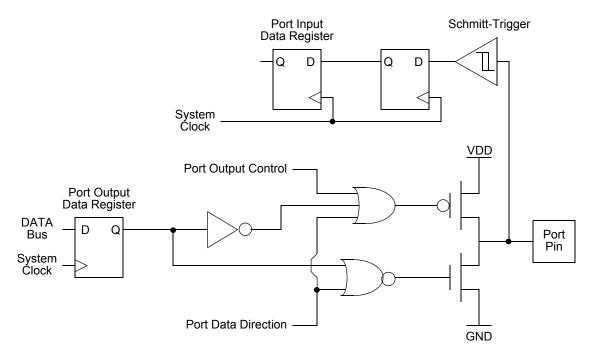

Figure 7 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

## Figure 7. GPIO Port Pin Block Diagram

## **GPIO Alternate Functions**

Many of the GPIO port pins can be used for general-purpose I/O and access to on-chip peripheral functions such as the timers and serial communication devices. The Port A–D Alternate Function sub-registers configure these pins for either General-Purpose I/O or alternate function operation. When a pin is configured for alternate function, control of the port pin direction (input/output) is passed from the Port A–D Data Direction registers to the alternate function assigned to this pin. Table 14 on page 41 lists the alternate functions possible with each port pin. For those pins with more one alternate function, the alternate function is defined through Alternate Function Sets sub-registers AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, those pins function as input and output for the crystal oscillator.

## Port A–D Address Registers

The Port A–D Address registers select the GPIO Port functionality accessible through the Port A–D Control registers. The Port A–D Address and Control registers combine to provide access to all GPIO Port controls (Table 17).

#### Table 17. Port A–D GPIO Address Registers (PxADDR)

| BITS  | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----|-----------------------------|---|---|---|---|---|---|--|

| FIELD |     | PADDR[7:0]                  |   |   |   |   |   |   |  |

| RESET |     | 00H                         |   |   |   |   |   |   |  |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| ADDR  |     | FD0H, FD4H, FD8H, FDCH      |   |   |   |   |   |   |  |

PADDR[7:0]—Port Address

The Port Address selects one of the sub-registers accessible through the Port Control register.

| PADDR[7:0] | Port Control sub-register accessible using the Port A–D Control Registers      |

|------------|--------------------------------------------------------------------------------|

| 00H        | No function. Provides some protection against accidental Port reconfiguration. |

| 01H        | Data Direction.                                                                |

| 02H        | Alternate Function.                                                            |

| 03H        | Output Control (Open-Drain).                                                   |

| 04H        | High Drive Enable.                                                             |

| 05H        | Stop Mode Recovery Source Enable.                                              |

| 06H        | Pull-up Enable.                                                                |

| 07H        | Alternate Function Set 1.                                                      |

| 08H        | Alternate Function Set 2.                                                      |

| 09H–FFH    | No function.                                                                   |

## **Port A–D Control Registers**

The Port A–D Control registers set the GPIO port operation. The value in the corresponding Port A–D Address register determines which sub-register is read from or written to by a Port A–D Control register transaction (Table 18).

Follow the steps below for configuring a timer for COUNTER mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for COUNTER mode.

- Select either the rising edge or falling edge of the Timer Input signal for the count. This selection also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER mode. After the first timer Reload in COUNTER mode, counting always begins at the reset value of 0001H. In COUNTER mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer.

In COUNTER mode, the number of Timer Input transitions since the timer start is given by the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value-Start Value

#### **COMPARATOR COUNTER Mode**

In COMPARATOR COUNTER mode, the timer counts input transitions from the analog comparator output. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the comparator output signal. In COMPAR-ATOR COUNTER mode, the prescaler is disabled.

**Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the comparator output signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

After reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

110 = 64 cycles delay 111 = 128 cycles delay

INPCAP—Input Capture Event

This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.

0 = Previous timer interrupt is not a result of Timer Input Capture Event

1 = Previous timer interrupt is a result of Timer Input Capture Event

#### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode (Table 49).

Table 49. Timer 0–1 Control Register 1 (TxCTL1)

| BITS  | 7   | 6          | 5          | 4                   | 3 | 2 | 1 | 0 |

|-------|-----|------------|------------|---------------------|---|---|---|---|

| FIELD | TEN | TPOL       | PRES TMODE |                     |   |   |   |   |

| RESET | 0   | 0          | 0          | 0                   | 0 | 0 | 0 | 0 |

| R/W   | R/W | R/W        | R/W        | R/W R/W R/W R/W R/W |   |   |   |   |

| ADDR  |     | F07H, F0FH |            |                     |   |   |   |   |

TEN-Timer Enable

0 = Timer is disabled.

1 = Timer enabled to count.

TPOL—Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer.

#### **ONE-SHOT mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **CONTINUOUS mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### COUNTER mode

If the timer is enabled the Timer Output signal is complemented after timer reload.

0 = Count occurs on the rising edge of the Timer Input signal.

1 = Count occurs on the falling edge of the Timer Input signal.

**z**ilog<sup>®</sup>

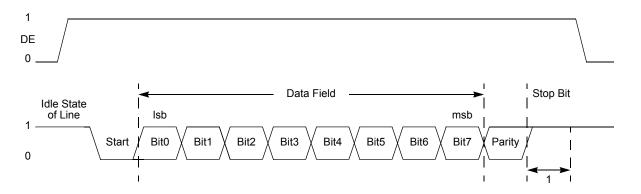

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART Transmit Data register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

#### Figure 14. UART Driver Enable Signal Timing (shown with 1 Stop Bit and Parity)

The Driver Enable to Start bit setup time is calculated as follows:

$$\left(\frac{1}{\text{Baud Rate (Hz)}}\right) \le \text{DE to Start Bit Setup Time (s)} \le \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

## **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

#### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit shift register has shifted the first bit of data out. The Transmit Data register can now be written with the next character to

105

### MPMD[1:0]—MULTIPROCESSOR Mode

If MULTIPROCESSOR (9-bit) mode is enabled,

00 = The UART generates an interrupt request on all received bytes (data and address).

01 = The UART generates an interrupt request only on received address bytes.

10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs.

11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register.

#### MPEN—MULTIPROCESSOR (9-bit) Enable

This bit is used to enable MULTIPROCESSOR (9-bit) mode.

0 = Disable MULTIPROCESSOR (9-bit) mode.

1 = Enable MULTIPROCESSOR (9-bit) mode.

#### MPBT—Multiprocessor Bit Transmit

This bit is applicable only when MULTIPROCESSOR (9-bit) mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.

0 = Send a 0 in the multiprocessor bit location of the data stream (data byte).

1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).

#### DEPOL—Driver Enable Polarity

0 = DE signal is Active High.

1 = DE signal is Active Low.

#### BRGCTL—Baud Rate Control

This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register.

When the UART receiver is **not** enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value 1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.

When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value. 1 = Reads from the Baud Rate High and Low Byte registers return the current BRG count value. Unlike the Timers, there is no mechanism to latch the Low Byte when the High Byte is read.

RDAIRQ—Receive Data Interrupt Enable

0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.

MPRX—Multiprocessor Receive

Returns the value of the most recent multiprocessor bit received. Reading from the UART Receive Data register resets this bit to 0.

## **UART Transmit Data Register**

Data bytes written to the UART Transmit Data (UxTXD) register (Table 65) are shifted out on the TXDx pin. The Write-only UART Transmit Data register shares a Register File address with the read-only UART Receive Data register.

| BITS  | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|-----------------|---|---|---|---|---|---|--|

| FIELD |   | TXD             |   |   |   |   |   |   |  |

| RESET | Х | X X X X X X X X |   |   |   |   |   |   |  |

| R/W   | W | w w w w w w w   |   |   |   |   |   |   |  |

| ADDR  |   | F40H            |   |   |   |   |   |   |  |

### Table 65. UART Transmit Data Register (U0TXD)

TXD-Transmit Data

UART transmitter data byte to be shifted out through the TXDx pin.

## **UART Receive Data Register**

Data bytes received through the RXDx pin are stored in the UART Receive Data (UxRXD) register (Table 66). The read-only UART Receive Data register shares a Register File address with the Write-only UART Transmit Data register.

## Table 66. UART Receive Data Register (U0RXD)

| BITS      | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----------|----------------|---|---|---|---|---|---|---|--|

| FIELD     | RXD            |   |   |   |   |   |   |   |  |

| RESET     | Х              | Х | Х | Х | Х | Х | Х | Х |  |

| R/W       | R              | R | R | R | R | R | R | R |  |

| ADDR      | F40H           |   |   |   |   |   |   |   |  |

| X = Undef | K = Undefined. |   |   |   |   |   |   |   |  |

RXD—Receive Data

UART receiver data byte from the RXDx pin

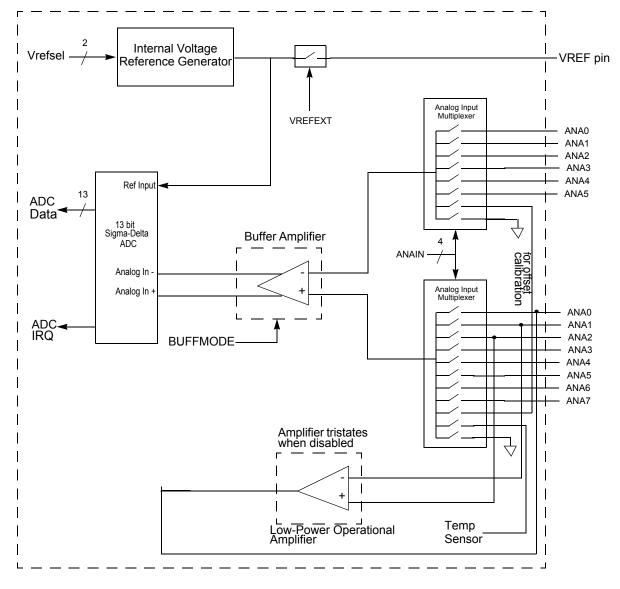

Figure 19. Analog-to-Digital Converter Block Diagram

## Operation

## Data Format

In both SINGLE-ENDED and DIFFERENTIAL modes, the effective output of the ADC is an 11-bit, signed, two's complement digital value. In DIFFERENTIAL mode, the ADC

zilog <sub>123</sub>

can output values across the entire 11-bit range, from -1024 to +1023. In SINGLE-ENDED mode, the output generally ranges from 0 to +1023, but offset errors can cause small negative values.

The ADC registers actually return 13 bits of data, but the two LSBs are intended for compensation use only. When the software compensation routine is performed on the 13 bit raw ADC value, two bits of resolution are lost because of a rounding error. As a result, the final value is an 11-bit number.

## Hardware Overflow

When the hardware overflow bit (OVF) is set in ADC Data Low Byte (ADCD\_L) register, all other data bits are invalid. The hardware overflow bit is set for values greater than  $V_{ref}$  and less than  $-V_{ref}$  (DIFFERENTIAL mode).

## **Automatic Powerdown**

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to power up. The ADC powers up when a conversion is requested by the ADC Control register.

## Single-Shot Conversion

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Follow the steps below for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the desired analog inputs by configuring the general-purpose I/O pins for alternate analog function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC.

- Write to BUFMODE [2:0] to select SINGLE-ENDED or DIFFERENTIAL mode, as well as unbuffered or buffered mode.

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is. contained in the ADC Control Register 0.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control register can be written simultaneously (the ADC can be configured and enabled with the same write instruction):

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

| İ | l | 0 | g | 133 |

|---|---|---|---|-----|

|   |   |   |   | 133 |

| BITS      | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----------|----------------|---|---|---|---|---|---|---|--|

| FIELD     | ADCDH          |   |   |   |   |   |   |   |  |

| RESET     | Х              | Х | Х | Х | Х | Х | Х | Х |  |

| R/W       | R              | R | R | R | R | R | R | R |  |

| ADDR      | F72H           |   |   |   |   |   |   |   |  |

| X = Undef | X = Undefined. |   |   |   |   |   |   |   |  |

#### Table 73. ADC Data High Byte Register (ADCD\_H)

ADCDH—ADC Data High Byte

This byte contains the upper eight bits of the ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the most recent conversion output is held in this register. These bits are undefined after a Reset.

## ADC Data Low Byte Register

The ADC Data Low Byte (ADCD\_L) register contains the lower bits of the ADC output as well as an overflow status bit. The output is a 13-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data Low Byte register is read-only. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

Table 74. ADC Data Low Byte Register (ADCD\_L)

| BITS           | 7    | 6 | 5     | 4    | 3   | 2 | 1 | 0 |  |  |

|----------------|------|---|-------|------|-----|---|---|---|--|--|

| FIELD          |      |   | ADCDL | Rese | OVF |   |   |   |  |  |

| RESET          | Х    | Х | Х     | Х    | Х   | Х | Х | Х |  |  |

| R/W            | R    | R | R     | R    | R   | R | R | R |  |  |

| ADDR           | F73H |   |       |      |     |   |   |   |  |  |

| X = Undefined. |      |   |       |      |     |   |   |   |  |  |

ADCDL—ADC Data Low Bits

These bits are the least significant five bits of the 13-bits of the ADC output. These bits are undefined after a Reset.

Reserved—Must be undefined.

OVF—Overflow Status

0= A hardware overflow did not occur in the ADC for the current sample. 1= A hardware overflow did occur in the ADC for the current sample, therefore the current sample is invalid.

zilog |

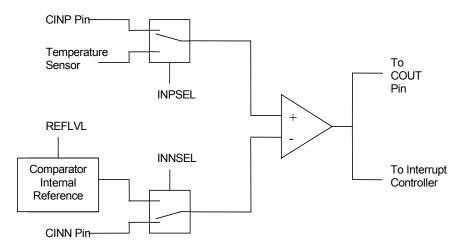

## Comparator

The Z8 Encore! XP<sup>®</sup> F082A Series devices feature a general purpose comparator that compares two analog input signals. These analog signals may be external stimulus from a pin (CINP and/or CINN) or internally generated signals. Both a programmable voltage reference and the temperature sensor output voltage are available internally. The output is available as an interrupt source or can be routed to an external pin.

Figure 20. Comparator Block Diagram

## Operation

When the positive comparator input exceeds the negative input by more than the specified hysteresis, the output is a logic HIGH. When the negative input exceeds the positive by more than the hysteresis, the output is a logic LOW. Otherwise, the comparator output retains its present value. See Table 137 on page 233 for details.

The comparator may be powered down to reduce supply current. See Power Control Register 0 on page 34 for details.

**Caution:** Because of the propagation delay of the comparator, it is not recommended to enable or reconfigure the comparator without first disabling interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts. The following example describes how to safely enable the comparator:

```

di

ld cmp0, r0 ; load some new configuration

nop

```

## **Flash Option Bits**

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore!  $XP^{\text{(R)}}$  F082A Series operation. The feature configuration data is stored in the Flash program memory and loaded into holding registers during Reset. The features available for control through the Flash Option Bits include:

- Watchdog Timer time-out response selection-interrupt or system reset

- Watchdog Timer always on (enabled at Reset)

- The ability to prevent unwanted read access to user code in Program Memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Program Memory

- Voltage Brownout configuration-always enabled or disabled during STOP mode to reduce STOP mode power consumption

- Oscillator mode selection-for high, medium, and low power crystal oscillators, or external RC oscillator

- Factory trimming information for the internal precision oscillator and low voltage detection

- Factory calibration values for ADC, temperature sensor, and Watchdog Timer compensation

- Factory serialization and randomized lot identifier (optional)

## Operation

## **Option Bit Configuration By Reset**

Each time the Flash Option Bits are programmed or erased, the device must be Reset for the change to take effect. During any reset operation (System Reset, Power-On Reset, or Stop Mode Recovery), the Flash Option Bits are automatically read from the Flash Program Memory and written to Option Configuration registers. The Option Configuration registers control operation of the devices within the Z8 Encore! XP F082A Series. Option Bit control is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

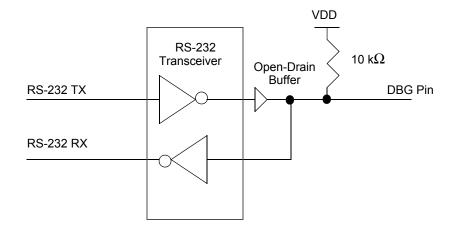

### Figure 25. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (2)

## **DEBUG Mode**

The operating characteristics of the devices in DEBUG mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions.

- The system clock operates unless in STOP mode.

- All enabled on-chip peripherals operate unless in STOP mode.

- Automatically exits HALT mode.

- Constantly refreshes the Watchdog Timer, if enabled.

#### **Entering DEBUG Mode**

The operating characteristics of the devices entering DEBUG mode are:

- The device enters DEBUG mode after the eZ8 CPU executes a BRK (Breakpoint) instruction.

- If the DBG pin is held Low during the final clock cycle of system reset, the part enters DEBUG mode immediately (20-/28-pin products only).

- **Note:** Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an Autobaud sequence (see OCD Auto-Baud Detector/Generator on page 176).

#### Table 128. Power Consumption (Continued)

|                     |                                                      | V <sub>DI</sub> | <sub>o</sub> = 2.7 V to 3 |          |       |                                   |

|---------------------|------------------------------------------------------|-----------------|---------------------------|----------|-------|-----------------------------------|

|                     |                                                      |                 | Maximum <sup>2</sup>      |          |       |                                   |

| Symbol              | Parameter                                            | Typical $^1$    | Std Temp                  | Ext Temp | Units | Conditions                        |

| I <sub>DD</sub> LPO | Low-Power Operational<br>Amplifier Supply<br>Current | 3               | 5                         | 5        | μΑ    | Driving a high-<br>impedance load |

| I <sub>DD</sub> TS  | Temperature Sensor<br>Supply Current                 | 60              |                           |          | μA    | See Notes 4                       |

| I <sub>DD</sub> BG  | Band Gap Supply                                      | 320             | 480                       | 500      | μA    | For 20-/28-pin devices            |

|                     | Current                                              |                 |                           |          |       | For 8-pin devices                 |

#### Notes

1. Typical conditions are defined as  $V_{DD}$  = 3.3 V and +30 °C.

2. Standard temperature is defined as  $T_A = 0$  °C to +70 °C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

3. Extended temperature is defined as T<sub>A</sub> = -40 °C to +105 °C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

zilog

|                   |                   | V <sub>DD</sub> | = 2.7 V to   |            |       |                                                                           |  |

|-------------------|-------------------|-----------------|--------------|------------|-------|---------------------------------------------------------------------------|--|

| Symbol            | Parameter         | Minimum         | Typical      | Maximum    | Units | Conditions                                                                |  |

| T <sub>AERR</sub> | Temperature Error |                 | <u>+</u> 0.5 | <u>+</u> 2 | °C    | Over the range +20 °C<br>to +30 °C (as<br>measured by ADC) <sup>1</sup>   |  |

|                   |                   |                 | <u>+</u> 1   | <u>+</u> 5 | °C    | Over the range +0 °C<br>to +70 °C (as<br>measured by ADC)                 |  |

|                   |                   |                 | <u>+</u> 2   | <u>+</u> 7 | °C    | Over the range +0 °C<br>to +105 °C (as<br>measured by ADC)                |  |

|                   |                   |                 | <u>+</u> 7   |            | °C    | Over the range -40 °C<br>to +105 °C (as<br>measured by ADC)               |  |

| T <sub>AERR</sub> | Temperature Error |                 | TBD          |            | °C    | Over the range -40 °C<br>to +105 °C (as<br>measured by<br>comparator)     |  |

| t <sub>WAKE</sub> | Wakeup Time       |                 | 80           | 100        | μs    | Time required for<br>Temperature Sensor<br>to stabilize after<br>enabling |  |

### **Table 138. Temperature Sensor Electrical Characteristics**

<sup>1</sup>Devices are factory calibrated at for maximal accuracy between +20 °C and +30 °C, so the sensor is maximally accurate in that range. User re-calibration for a different temperature range is possible and increases accuracy near the new calibration point.

## General Purpose I/O Port Input Data Sample Timing

Figure 34 displays timing of the GPIO Port input sampling. The input value on a GPIO Port pin is sampled on the rising edge of the system clock. The Port value is available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

| ג<br>ש<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק | Flash<br>Serie | S Devel                                           | SQ<br>NN<br>Opmen | t Kit | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description |  |

|-------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------|-------------------|-------|------------|---------------------|---------------------|----------------|------------|--------------------|-------------|--|

| Z8F08A28100KITG                                                                                       | ·              |                                                   |                   |       |            |                     |                     |                |            |                    |             |  |

| Z8F04A28100KITG                                                                                       |                | Z8 Encore! XP F042A Series 28-Pin Development Kit |                   |       |            |                     |                     |                |            |                    |             |  |

| Z8F04A08100KITG                                                                                       |                | Z8 Encore! XP F042A Series 8-Pin Development Kit  |                   |       |            |                     |                     |                |            |                    |             |  |

| ZUSBSC00100ZACG                                                                                       |                | USB Smart Cable Accessory Kit                     |                   |       |            |                     |                     |                |            |                    |             |  |

| ZUSBOPTSC01ZACG                                                                                       |                | USB Opto-Isolated Smart Cable Accessory Kit       |                   |       |            |                     |                     |                |            |                    |             |  |

| ZENETSC0100ZACG                                                                                       |                | Ethernet Smart Cable Accessory Kit                |                   |       |            |                     |                     |                |            |                    |             |  |

|                                                                                                       |                |                                                   |                   |       |            |                     |                     |                |            |                    |             |  |