# E·XFL

### Zilog - Z8F042AHH020SC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | IrDA, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT  |

| Number of I/O              | 17                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | 128 x 8                                                       |

| RAM Size                   | 1K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | A/D 7x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                |

| Supplier Device Package    |                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f042ahh020sc00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Up to thirteen 5 V-tolerant input pins

- Up to 8 ports capable of direct LED drive with no current limit resistor required

- On-Chip Debugger (OCD)

- Voltage Brownout (VBO) protection

- Programmable low battery detection (LVD) (8-pin devices only)

- Bandgap generated precision voltage references available for the ADC, comparator, VBO, and LVD

- Power-On Reset (POR)

- 2.7 V to 3.6 V operating voltage

- 8-, 20-, and 28-pin packages

- 0 °C to +70 °C and -40 °C to +105 °C for operating temperature ranges

# **Part Selection Guide**

Table 1 on page 3 identifies the basic features and package styles available for each device within the Z8 Encore!  $XP^{\ensuremath{\mathbb{R}}}$  F082A Series product line.

# **Reset Sources**

Table 9 lists the possible sources of a system reset.

| Operating Mode       | Reset Source                                             | Special Conditions                                                                            |

|----------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| NORMAL or HALT modes | Power-On Reset/Voltage<br>Brownout                       | Reset delay begins after supply voltage exceeds POR level.                                    |

|                      | Watchdog Timer time-out when configured for Reset        | None.                                                                                         |

|                      | RESET pin assertion                                      | All reset pulses less than three system clocks in width are ignored.                          |

|                      | On-Chip Debugger initiated Reset<br>(OCDCTL[0] set to 1) | System Reset, except the On-Chip Debugger is unaffected by the reset.                         |

| STOP mode            | Power-On Reset/Voltage<br>Brownout                       | Reset delay begins after supply voltage exceeds POR level.                                    |

|                      | RESET pin assertion                                      | All reset pulses less than the specified analog delay are ignored. See Table 131 on page 229. |

|                      | DBG pin driven Low                                       | None.                                                                                         |

### Table 9. Reset Sources and Resulting Reset Type

## **Power-On Reset**

Z8 Encore! XP F082A Series devices contain an internal Power-On Reset circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the device is held in the Reset state until the POR Counter has timed out. If the crystal oscillator is enabled by the option bits, this timeout is longer.

After the Z8 Encore! XP F082A Series device exits the Power-On Reset state, the eZ8 CPU fetches the Reset vector. Following Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) register is set to 1.

Figure 5 displays Power-On Reset operation. See Electrical Characteristics on page 221 for the POR threshold voltage ( $V_{POR}$ ).

| BITS  | 7     | 6            | 5     | 4   | 3        | 1 | 0 |   |  |  |  |

|-------|-------|--------------|-------|-----|----------|---|---|---|--|--|--|

| FIELD | POR   | STOP         | WDT   | EXT | Reserved |   |   |   |  |  |  |

| RESET | See d | lescriptions | below | 0   | 0        | 0 | 0 | 0 |  |  |  |

| R/W   | R     | R            | R     | R   | R R R    |   |   |   |  |  |  |

| ADDR  |       | FF0H         |       |     |          |   |   |   |  |  |  |

### Table 11. Reset Status Register (RSTSTAT)

| Reset or Stop Mode Recovery Event                     | POR | STOP | WDT | EXT |

|-------------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                        | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion                       | 0   | 0    | 0   | 1   |

| Reset using Watchdog Timer time-out                   | 0   | 0    | 1   | 0   |

| Reset using the On-Chip Debugger (OCTCTL[1] set to 1) | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low         | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition          | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using Watchdog Timer time-out      | 0   | 1    | 1   | 0   |

### POR—Power-On Reset Indicator

If this bit is set to 1, a Power-On Reset event occurs. This bit is reset to 0 if a WDT time-out or Stop Mode Recovery occurs. This bit is also reset to 0 when the register is read.

### STOP—Stop Mode Recovery Indicator

If this bit is set to 1, a Stop Mode Recovery occurs. If the STOP and WDT bits are both set to 1, the Stop Mode Recovery occurs because of a WDT time-out. If the STOP bit is 1 and the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a Power-On Reset or a WDT time-out that occurred while not in STOP mode. Reading this register also resets this bit.

### WDT—Watchdog Timer Time-Out Indicator

If this bit is set to 1, a WDT time-out occurs. A POR resets this pin. A Stop Mode Recovery from a change in an input pin also resets this bit. Reading this register resets this bit. This read must occur before clearing the WDT interrupt.

### EXT-External Reset Indicator

If this bit is set to 1, a Reset initiated by the external  $\overline{\text{RESET}}$  pin occurs. A Power-On Reset or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register resets this bit.

### Reserved—Must be 0.

LVD—Low Voltage Detection Indicator

If this bit is set to 1 the current state of the supply voltage is below the low voltage detection threshold. This value is not latched but is a real-time indicator of the supply voltage level.

# 63

### Table 37. IRQ0 Enable High Bit Register (IRQ0ENH)

| BITS  | 7        | 6     | 5     | 4      | 3      | 2        | 1        | 0      |  |  |  |  |

|-------|----------|-------|-------|--------|--------|----------|----------|--------|--|--|--|--|

| FIELD | Reserved | T1ENH | T0ENH | U0RENH | U0TENH | Reserved | Reserved | ADCENH |  |  |  |  |

| RESET | 0        | 0     | 0     | 0      | 0      | 0        | 0        | 0      |  |  |  |  |

| R/W   | R/W      | R/W   | R/W   | R/W    | R/W    | R/W      | R/W      | R/W    |  |  |  |  |

| ADDR  |          | FC1H  |       |        |        |          |          |        |  |  |  |  |

Reserved—Must be 0.

T1ENH—Timer 1 Interrupt Request Enable High Bit T0ENH—Timer 0 Interrupt Request Enable High Bit U0RENH—UART 0 Receive Interrupt Request Enable High Bit U0TENH—UART 0 Transmit Interrupt Request Enable High Bit ADCENH—ADC Interrupt Request Enable High Bit

### Table 38. IRQ0 Enable Low Bit Register (IRQ0ENL)

| BITS  | 7        | 6     | 5            | 4             | 3             | 2        | 1        | 0      |  |  |  |  |

|-------|----------|-------|--------------|---------------|---------------|----------|----------|--------|--|--|--|--|

| FIELD | Reserved | T1ENL | <b>T0ENL</b> | <b>U0RENL</b> | <b>U0TENL</b> | Reserved | Reserved | ADCENL |  |  |  |  |

| RESET | 0        | 0     | 0            | 0             | 0             | 0        | 0        | 0      |  |  |  |  |

| R/W   | R        | R/W   | R/W          | R/W           | R/W           | R        | R        | R/W    |  |  |  |  |

| ADDR  |          | FC2H  |              |               |               |          |          |        |  |  |  |  |

Reserved—Must be 0.

T1ENL—Timer 1 Interrupt Request Enable Low Bit T0ENL—Timer 0 Interrupt Request Enable Low Bit U0RENL—UART 0 Receive Interrupt Request Enable Low Bit U0TENL—UART 0 Transmit Interrupt Request Enable Low Bit ADCENL—ADC Interrupt Request Enable Low Bit

# **IRQ1 Enable High and Low Bit Registers**

Table 39 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers (Table 40 and Table 41) form a priority encoded enabling for interrupts in the Interrupt Request 1 register.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In CAPTURE/COMPARE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

### **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte register is read, the contents of the Timer Low Byte register are placed in a holding register. A subsequent read from the Timer Low Byte register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte register returns the actual value in the counter.

### **Timer Pin Signal Operation**

Timer Output is a GPIO Port pin alternate function. The Timer Output is toggled every time the counter is reloaded.

The Timer Input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function Registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

Watchdog Timer Reload Registers results in a one-second timeout at room temperature and 3.3 V supply voltage.

Timeouts other than one second may be obtained by scaling the calibration values up or down as required.

**Note:** *The Watchdog Timer accuracy still degrades as temperature and supply voltage vary. See* Table 133 on page 230 *for* details.

# Watchdog Timer Control Register Definitions

### Watchdog Timer Control Register

The Watchdog Timer Control (WDTCTL) register is a write-only control register. Writing the 55H, AAH unlock sequence to the WDTCTL register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers.

This register address is shared with the read-only Reset Status register.

| BITS      | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|-----------|----------------|---|---|---|---|---|---|---|--|--|--|--|

| FIELD     | WDTUNLK        |   |   |   |   |   |   |   |  |  |  |  |

| RESET     | Х              | Х | Х | Х | Х | Х | Х | Х |  |  |  |  |

| R/W       | W              | W | W | W | W | W | W | W |  |  |  |  |

| ADDR      | FF0H           |   |   |   |   |   |   |   |  |  |  |  |

| X = Undef | X = Undefined. |   |   |   |   |   |   |   |  |  |  |  |

### Table 57. Watchdog Timer Control Register (WDTCTL)

WDTUNLK—Watchdog Timer Unlock

The software must write the correct unlocking sequence to this register before it is allowed to modify the contents of the Watchdog Timer reload registers.

## Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers (Table 58 through Table 60) form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. The 24-bit reload value is {WDTU[7:0], WDTH[7:0]}. Writing to these registers sets the appropriate Reload Value. Reading from these registers returns the current Watchdog Timer count value.

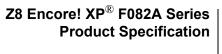

Figure 15. UART Receiver Interrupt Service Routine Flow

### **Baud Rate Generator Interrupts**

If the baud rate generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud Rate Generator to function as an additional counter if the UART functionality is not employed.

# **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value

107

0 = No framing error occurred. 1 = A framing error occurred.

BRKD—Break Detect

This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data register clears this bit. 0 = No break occurred.

1 = A break occurred.

TDRE—Transmitter Data Register Empty

This bit indicates that the UART Transmit Data register is empty and ready for additional data. Writing to the UART Transmit Data register resets this bit.

0 = Do not write to the UART Transmit Data register.

1 = The UART Transmit Data register is ready to receive an additional byte to be transmitted.

TXE—Transmitter Empty

This bit indicates that the transmit shift register is empty and character transmission is finished.

0 = Data is currently transmitting.

1 = Transmission is complete.

$CTS - \overline{CTS}$  signal

When this bit is read it returns the level of the  $\overline{\text{CTS}}$  signal. This signal is active Low.

### **UART Status 1 Register**

This register contains multiprocessor control and status bits.

Table 64. UART Status 1 Register (U0STAT1)

| BITS  | 7                    | 6    | 5 | 4 | 3   | 2   | 1 | 0 |  |  |  |

|-------|----------------------|------|---|---|-----|-----|---|---|--|--|--|

| FIELD | Reserved NEWFRM MPRX |      |   |   |     |     |   |   |  |  |  |

| RESET | 0                    | 0    | 0 | 0 | 0   | 0   | 0 | 0 |  |  |  |

| R/W   | R                    | R    | R | R | R/W | R/W | R | R |  |  |  |

| ADDR  |                      | F44H |   |   |     |     |   |   |  |  |  |

Reserved—Must be 0.

NEWFRM—Status bit denoting the start of a new frame. Reading the UART Receive Data register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame.

1 = The current byte is the first data byte of a new frame.

# **Analog-to-Digital Converter**

The analog-to-digital converter (ADC) converts an analog input signal to its digital representation. The features of this sigma-delta ADC include:

- 11-bit resolution in DIFFERENTIAL mode.

- 10-bit resolution in SINGLE-ENDED mode.

- Eight single-ended analog input sources are multiplexed with general-purpose I/O ports.

- 9<sup>th</sup> analog input obtained from temperature sensor peripheral.

- 11 pairs of differential inputs also multiplexed with general-purpose I/O ports.

- Low-power operational amplifier (LPO).

- Interrupt on conversion complete.

- Bandgap generated internal voltage reference with two selectable levels.

- Manual in-circuit calibration is possible employing user code (offset calibration).

- Factory calibrated for in-circuit error compensation.

# Architecture

Figure 19 displays the major functional blocks of the ADC. An analog multiplexer network selects the ADC input from the available analog pins, ANA0 through ANA7.

The input stage of the ADC allows both differential gain and buffering. The following input options are available:

- Unbuffered input (SINGLE-ENDED and DIFFERENTIAL modes).

- Buffered input with unity gain (SINGLE-ENDED and DIFFERENTIAL modes).

- LPO output with full pin access to the feedback path.

1001 = 1.8 V 1010–1111 = Reserved

For 8-pin devices:

000000 = 0.00 V000001 = 0.05 V000010 = 0.10 V 000011 = 0.15 V 000100 = 0.20 V000101 = 0.25 V000110 = 0.30 V 000111 = 0.35 V 001000 = 0.40 V 001001 = 0.45 V 001010 = 0.50 V 001011 = 0.55 V 001100 = 0.60 V 001101 = 0.65 V 001110 = 0.70 V001111 = 0.75 V 010000 = 0.80 V010001 = 0.85 V010010 = 0.90 V 010011 = 0.95 V 010100 = 1.00 V (Default) 010101 = 1.05 V 010110 = 1.10 V 010111 = 1.15 V 011000 = 1.20 V 011001 = 1.25 V 011010 = 1.30 V 011011 = 1.35 V 011100 = 1.40 V 011101 = 1.45 V 011110 = 1.50 V 011111 = 1.55 V 100000 = 1.60 V100001 = 1.65 V 100010 = 1.70 V 100011 = 1.75 V

# zilog <sub>14</sub>

# Flash Operation Timing Using the Flash Frequency Registers

Before performing either a program or erase operation on Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 32 kHz (32768 Hz) through 20 MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 32 kHz (32768 Hz) or above 20 MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! XP<sup>®</sup> F082A Series devices.

### Flash Code Protection Against External Access

The user code contained within the Flash memory can be protected against external access by the on-chip debugger. Programming the FRP Flash Option Bit prevents reading of the user code with the On-Chip Debugger. See Flash Option Bits on page 153 and On-Chip Debugger on page 173 for more information.

## Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! XP F082A Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash Option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

### Flash Code Protection Using the Flash Option Bits

The FRP and FWP Flash Option Bits combine to provide three levels of Flash Program Memory protection as listed in Table 77. See Flash Option Bits on page 153 for more information.

185

DBGACK—Debug Acknowledge

This bit enables the debug acknowledge feature. If this bit is set to 1, the OCD sends a Debug Acknowledge character (FFH) to the host when a Breakpoint occurs.

0 = Debug Acknowledge is disabled.

1 = Debug Acknowledge is enabled.

Reserved—Must be 0.

RST—Reset

Setting this bit to 1 resets the Z8F04xA family device. The device goes through a normal Power-On Reset sequence with the exception that the On-Chip Debugger is not reset. This bit is automatically cleared to 0 at the end of reset.

0 = No effect.

1 = Reset the Flash Read Protect Option Bit device.

# **OCD Status Register**

The OCD Status register reports status information about the current state of the debugger and the system.

### Table 107. OCD Status Register (OCDSTAT)

| BITS  | 7   | 6    | 5      | 4        | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|-----|------|--------|----------|---|---|---|---|--|--|--|--|

| FIELD | DBG | HALT | FRPENB | Reserved |   |   |   |   |  |  |  |  |

| RESET | 0   | 0    | 0      | 0        | 0 | 0 | 0 | 0 |  |  |  |  |

| R/W   | R   | R    | R      | R        | R | R | R | R |  |  |  |  |

DBG—Debug Status

0 = NORMAL mode

1 = DEBUG mode

HALT—HALT Mode

0 =Not in HALT mode

1 =In HALT mode

FRPENB—Flash Read Protect Option Bit Enable

0 = FRP bit enabled, that allows disabling of many OCD commands

1 = FRP bit has no effect

Reserved-Must be 0

**z**ilog<sup>°</sup>

208

| Assembly             | Symbolic                                                                                  | Addres     | s Mode   | Opcode(s) |   |          | Fla | ags       |   |   | Fetch  | Instr. |

|----------------------|-------------------------------------------------------------------------------------------|------------|----------|-----------|---|----------|-----|-----------|---|---|--------|--------|

| Mnemonic             | Operation                                                                                 | dst        | src      | (Hex)     | С | Ζ        | S   | ۷         | D | Н | Cycles |        |

| AND dst, src         | $dst \gets dst \; AND \; src$                                                             | r          | r        | 52        | - | *        | *   | 0         | _ | - | 2      | 3      |

|                      |                                                                                           | r          | Ir       | 53        | - |          |     |           |   |   | 2      | 4      |

|                      |                                                                                           | R          | R        | 54        | - |          |     |           |   |   | 3      | 3      |

|                      |                                                                                           | R          | IR       | 55        | - |          |     |           |   |   | 3      | 4      |

|                      |                                                                                           | R          | IM       | 56        | - |          |     |           |   |   | 3      | 3      |

|                      |                                                                                           | IR         | IM       | 57        | - |          |     |           |   |   | 3      | 4      |

| ANDX dst, src        | $dst \gets dst \ AND \ src$                                                               | ER         | ER       | 58        | - | *        | *   | 0         | _ | - | 4      | 3      |

|                      |                                                                                           | ER         | IM       | 59        | - |          |     |           |   |   | 4      | 3      |

| ATM                  | Block all interrupt and<br>DMA requests during<br>execution of the next 3<br>instructions |            |          | 2F        | - | _        | _   | _         | _ | _ | 1      | 2      |

| BCLR bit, dst        | $dst[bit] \leftarrow 0$                                                                   | r          |          | E2        | - | -        | _   | _         | _ | - | 2      | 2      |

| BIT p, bit, dst      | $dst[bit] \leftarrow p$                                                                   | r          |          | E2        | - | -        | -   | _         | _ | _ | 2      | 2      |

| BRK                  | Debugger Break                                                                            |            |          | 00        | - | -        | -   | -         | - | - | 1      | 1      |

| BSET bit, dst        | $dst[bit] \leftarrow 1$                                                                   | r          |          | E2        | - | -        | _   | _         | - | - | 2      | 2      |

| BSWAP dst            | $dst[7:0] \leftarrow dst[0:7]$                                                            | R          |          | D5        | Х | *        | *   | 0         | _ | - | 2      | 2      |

| BTJ p, bit, src, dst |                                                                                           |            | r        | F6        | - | -        | -   | -         | - | - | 3      | 3      |

|                      | $PC \gets PC + X$                                                                         |            | lr       | F7        | - |          |     |           |   |   | 3      | 4      |

| BTJNZ bit, src, dst  |                                                                                           |            | r        | F6        | - | _        | _   | _         | _ | - | 3      | 3      |

|                      | $PC \leftarrow PC + X$                                                                    |            | lr       | F7        | - |          |     |           |   |   | 3      | 4      |

| BTJZ bit, src, dst   | if src[bit] = 0                                                                           |            | r        | F6        | - | -        | -   | -         | - | - | 3      | 3      |

|                      | $PC \leftarrow PC + X$                                                                    |            | lr       | F7        | - |          |     |           |   |   | 3      | 4      |

| CALL dst             | $SP \leftarrow SP - 2$                                                                    | IRR        |          | D4        | - | _        | _   | _         | _ | - | 2      | 6      |

|                      | $\begin{array}{l} @SP \leftarrow PC \\ PC \leftarrow dst \end{array}$                     | DA         |          | D6        | - |          |     |           |   |   | 3      | 3      |

| CCF                  | $C \leftarrow \sim C$                                                                     |            |          | EF        | * | _        | _   | _         | _ |   | 1      | 2      |

| CLR dst              | $dst \gets 00H$                                                                           | R          |          | B0        | - | -        | _   | _         | - | - | 2      | 2      |

|                      |                                                                                           | IR         |          | B1        | - |          |     |           |   |   | 2      | 3      |

| Flags Notation:      | * = Value is a function of<br>– = Unaffected<br>X = Undefined                             | the result | of the o | peration. |   | Re<br>Se |     | to (<br>1 | ) |   |        |        |

### Table 124. eZ8 CPU Instruction Summary (Continued)

# zilog

# **Electrical Characteristics**

The data in this chapter is pre-qualification and pre-characterization and is subject to change. Additional electrical characteristics may be found in the individual chapters.

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 126 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                                      | Minimum | Maximum | Units | Notes |

|----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                 | -40     | +105    | °C    |       |

| Storage temperature                                            | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>             | -0.3    | +5.5    | V     | 1     |

|                                                                | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$               | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin            | -5      | +5      | μA    |       |

| Maximum output current from active output pin                  | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0 °C to 70 °C                |         |         |       |       |

| Total power dissipation                                        |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$               |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0 °C to 70 °C               |         |         |       |       |

| Total power dissipation                                        |         | 430     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub> |         | 120     | mA    |       |

### Table 126. Absolute Maximum Ratings

|                           |                                                    | V <sub>DI</sub> | <sub>0</sub> = 2.7 V to 3 | 5.6 V                |       |                                                                  |

|---------------------------|----------------------------------------------------|-----------------|---------------------------|----------------------|-------|------------------------------------------------------------------|

|                           |                                                    |                 | Maximum <sup>2</sup>      | Maximum <sup>3</sup> | _     |                                                                  |

| Symbol                    | Parameter                                          | Typical $^1$    | Std Temp                  | Ext Temp             | Units | Conditions                                                       |

| I <sub>DD</sub> Stop      | Supply Current in STOP<br>Mode                     | 0.1             |                           |                      | μA    | No peripherals enabled. All pins driven to $V_{DD}$ or $V_{SS}.$ |

| I <sub>DD</sub> Halt      | Supply Current in HALT                             | 35              | 55                        | 65                   | μA    | 32 kHz                                                           |

|                           | Mode (with all peripherals disabled)               | 520             |                           |                      | μA    | 5.5 MHz                                                          |

|                           | penpinenale aleases) -                             | 2.1             | 2.85                      | 2.85                 | mA    | 20 MHz                                                           |

| I <sub>DD</sub>           | Supply Current in                                  | 2.8             |                           |                      | mA    | 32 kHz                                                           |

|                           | ACTIVE Mode (with all peripherals disabled)        | 4.5             | 5.2                       | 5.2                  | mA    | 5.5 MHz                                                          |

|                           |                                                    | 5.5             | 6.5                       | 6.5                  | mA    | 10 MHz                                                           |

|                           | -                                                  | 7.9             | 11.5                      | 11.5                 | mA    | 20 MHz                                                           |

| I <sub>DD</sub> WDT       | Watchdog Timer Supply<br>Current                   | 0.9             | 1.0                       | 1.1                  | μA    |                                                                  |

| I <sub>DD</sub>           | Crystal Oscillator                                 | 40              |                           |                      | μA    | 32 kHz                                                           |

| XTAL                      | Supply Current                                     | 230             |                           |                      | μA    | 4 MHz                                                            |

|                           | -                                                  | 760             |                           |                      | μA    | 20 MHz                                                           |

| I <sub>DD</sub> IPO       | Internal Precision<br>Oscillator Supply<br>Current | 350             | 500                       | 550                  | μA    |                                                                  |

| I <sub>DD</sub> VBO       | Low-Voltage Detect                                 | 50              |                           |                      | μA    | For 20-/28-pin devices<br>(VBO only); See Notes 4                |

|                           | Supply Current                                     |                 |                           |                      |       | For 8-pin devices; See<br>Notes 4                                |

| I <sub>DD</sub> ADC       | Analog to Digital                                  | 2.8             | 3.1                       | 3.2                  | mA    | 32 kHz                                                           |

|                           | Converter Supply<br>Current (with External         | 3.1             | 3.6                       | 3.7                  | mA    | 5.5 MHz                                                          |

|                           | Reference)                                         | 3.3             | 3.7                       | 3.8                  | mA    | 10 MHz                                                           |

|                           | -                                                  | 3.7             | 4.2                       | 4.3                  | mA    | 20 MHz                                                           |

| I <sub>DD</sub><br>ADCRef | ADC Internal Reference<br>Supply Current           | 0               |                           |                      | μA    | See Notes 4                                                      |

| I <sub>DD</sub> CMP       | Comparator supply<br>Current                       | 150             | 180                       | 190                  | μA    | See Notes 4                                                      |

# Table 128. Power Consumption

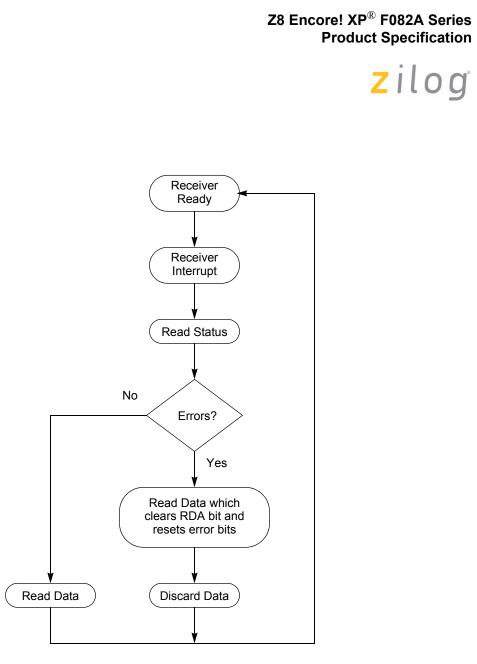

Figure 34. Port Input Sample Timing

|                     |                                                                                                          | Delay (ns) |         |

|---------------------|----------------------------------------------------------------------------------------------------------|------------|---------|

| Parameter           | Abbreviation                                                                                             | Minimum    | Maximum |

| T <sub>S_PORT</sub> | Port Input Transition to XIN Rise Setup Time (Not pictured)                                              | 5          | _       |

| T <sub>H_PORT</sub> | XIN Rise to Port Input Transition Hold Time (Not pictured)                                               | 0          | -       |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to ensure Stop Mode<br>Recovery<br>(for GPIO Port Pins enabled as SMR sources) | 1 µs       |         |

# **On-Chip Debugger Timing**

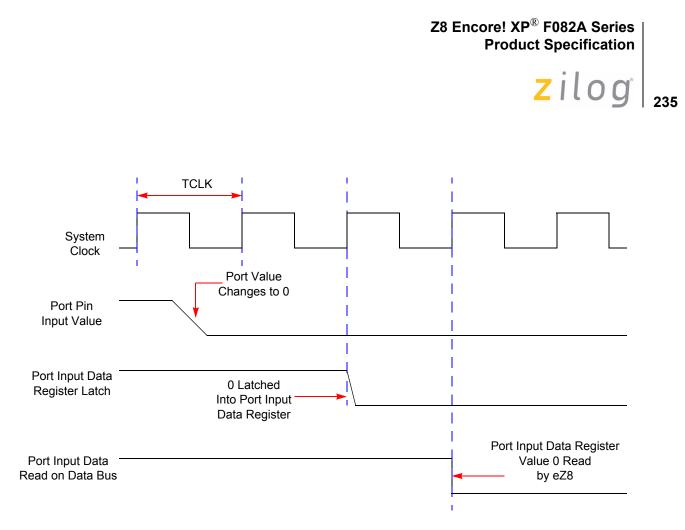

Figure 36 and Table 141 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

Figure 36. On-Chip Debugger Timing

|                |                                  | Delay (ns) |         |

|----------------|----------------------------------|------------|---------|

| Parameter      | Abbreviation                     | Minimum    | Maximum |

| DBG            |                                  |            |         |

| T <sub>1</sub> | XIN Rise to DBG Valid Delay      | -          | 15      |

| T <sub>2</sub> | XIN Rise to DBG Output Hold Time | 2          | _       |

| T <sub>3</sub> | DBG to XIN Rise Input Setup Time | 5          | _       |

| T <sub>4</sub> | DBG to XIN Rise Input Hold Time  | 5          | _       |

### Table 141. On-Chip Debugger Timing

### 260

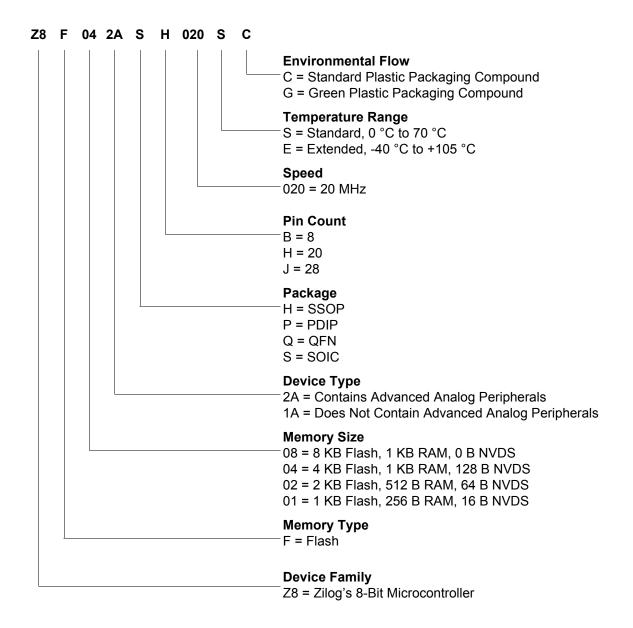

### Part Number Suffix Designations

266

timing 237 OCD commands execute instruction (12H) 183 read data memory (0DH) 183 read OCD control register (05H) 181 read OCD revision (00H) 180 read OCD status register (02H) 180 read program counter (07H) 181 read program memory (0BH) 182 read program memory CRC (0EH) 183 read register (09H) 182 read runtime counter (03H) 180 step instruction (10H) 183 stuff instruction (11H) 183 write data memory (0CH) 182 write OCD control register (04H) 181 write program counter (06H) 181 write program memory (0AH) 182 write register (08H) 181 on-chip debugger (OCD) 173 on-chip debugger signals 12 on-chip oscillator 193 **ONE-SHOT** mode 84 opcode map abbreviations 217 cell description 216 first 218 second after 1FH 219 Operational Description 23, 33, 37, 55, 69, 91, 97, 117, 121, 134, 135, 139, 141, 153, 169, 173, 187, 193, 197 OR 205 ordering information 251 **ORX 206** oscillator signals 12

### Ρ

p 201 packaging 20-pin PDIP 244, 245 20-pin SSOP 246, 249 28-pin PDIP 247 28-pin SOIC 248

8-pin PDIP 241 8-pin SOIC 242 PDIP 248, 249 part selection guide 2 PC 202 PDIP 248, 249 peripheral AC and DC electrical characteristics 229 pin characteristics 13 **Pin Descriptions 9** polarity 201 POP 205 pop using extended addressing 205 **POPX 205** port availability, device 37 port input timing (GPIO) 235 port output timing, GPIO 236 power supply signals 13 power-down, automatic (ADC) 122 Power-on and Voltage Brownout electrical characteristics and timing 229 Power-On Reset (POR) 25 program control instructions 206 program counter 202 program memory 15 **PUSH 205** push using extended addressing 205 PUSHX 205 PWM mode 85 PxADDR register 46 PxCTL register 47

## R

R 201 r 201 RA register address 201 RCF 204 receive IrDA data 119 receiving UART data-interrupt-driven method 102 receiving UART data-polled method 101