Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 6                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 128 x 8                                                      |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 4x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                       |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f042apb020ec    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Up to thirteen 5 V-tolerant input pins

- Up to 8 ports capable of direct LED drive with no current limit resistor required

- On-Chip Debugger (OCD)

- Voltage Brownout (VBO) protection

- Programmable low battery detection (LVD) (8-pin devices only)

- Bandgap generated precision voltage references available for the ADC, comparator, VBO, and LVD

- Power-On Reset (POR)

- 2.7 V to 3.6 V operating voltage

- 8-, 20-, and 28-pin packages

- 0 °C to +70 °C and -40 °C to +105 °C for operating temperature ranges

#### **Part Selection Guide**

Table 1 on page 3 identifies the basic features and package styles available for each device within the Z8 Encore!  $XP^{\ensuremath{\mathbb{R}}}$  F082A Series product line.

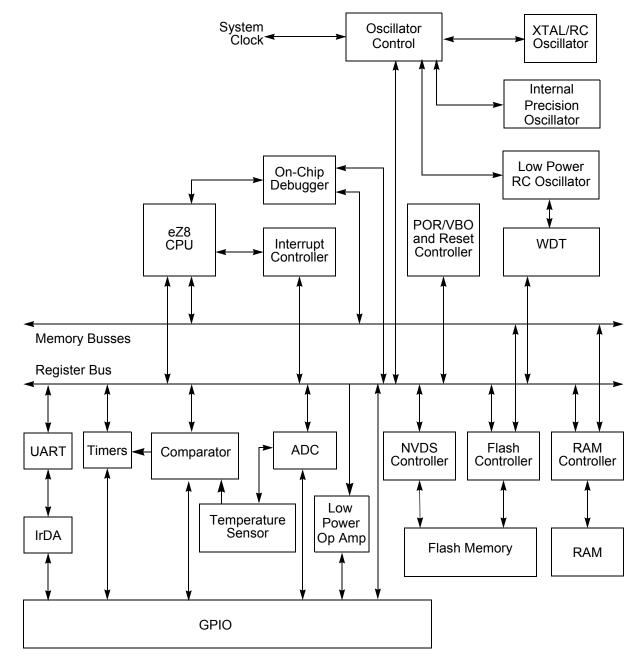

### **Block Diagram**

Figure 1 displays the block diagram of the architecture of the Z8 Encore! XP<sup>®</sup> F082A Series devices.

Figure 1. Z8 Encore! XP F082A Series Block Diagram

#### **Reset Sources**

Table 9 lists the possible sources of a system reset.

| Operating Mode       | Reset Source                                             | Special Conditions                                                                            |

|----------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| NORMAL or HALT modes | Power-On Reset/Voltage<br>Brownout                       | Reset delay begins after supply voltage exceeds POR level.                                    |

|                      | Watchdog Timer time-out when configured for Reset        | None.                                                                                         |

|                      | RESET pin assertion                                      | All reset pulses less than three system clocks in width are ignored.                          |

|                      | On-Chip Debugger initiated Reset<br>(OCDCTL[0] set to 1) | System Reset, except the On-Chip Debugger is unaffected by the reset.                         |

| STOP mode            | Power-On Reset/Voltage<br>Brownout                       | Reset delay begins after supply voltage exceeds POR level.                                    |

|                      | RESET pin assertion                                      | All reset pulses less than the specified analog delay are ignored. See Table 131 on page 229. |

|                      | DBG pin driven Low                                       | None.                                                                                         |

#### Table 9. Reset Sources and Resulting Reset Type

#### **Power-On Reset**

Z8 Encore! XP F082A Series devices contain an internal Power-On Reset circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the device is held in the Reset state until the POR Counter has timed out. If the crystal oscillator is enabled by the option bits, this timeout is longer.

After the Z8 Encore! XP F082A Series device exits the Power-On Reset state, the eZ8 CPU fetches the Reset vector. Following Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) register is set to 1.

Figure 5 displays Power-On Reset operation. See Electrical Characteristics on page 221 for the POR threshold voltage ( $V_{POR}$ ).

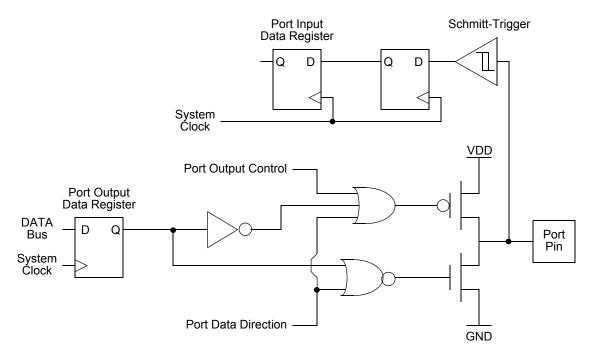

#### Architecture

Figure 7 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

#### Figure 7. GPIO Port Pin Block Diagram

#### **GPIO Alternate Functions**

Many of the GPIO port pins can be used for general-purpose I/O and access to on-chip peripheral functions such as the timers and serial communication devices. The Port A–D Alternate Function sub-registers configure these pins for either General-Purpose I/O or alternate function operation. When a pin is configured for alternate function, control of the port pin direction (input/output) is passed from the Port A–D Data Direction registers to the alternate function assigned to this pin. Table 14 on page 41 lists the alternate functions possible with each port pin. For those pins with more one alternate function, the alternate function is defined through Alternate Function Sets sub-registers AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, those pins function as input and output for the crystal oscillator.

Follow the steps below for configuring a timer for COMPARE mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for COMPARE mode.

- Set the prescale value.

- Set the initial logic level (High or Low) for the Timer Output alternate function, if appropriate.

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In COMPARE mode, the system clock always provides the timer input. The Compare time can be calculated by the following equation:

COMPARE Mode Time (s) =  $\frac{(Compare Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### GATED Mode

In GATED mode, the timer counts only when the Timer Input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control register. When the Timer Input signal is asserted, counting begins. A timer interrupt is generated when the Timer Input signal is deasserted or a timer reload occurs. To determine if a Timer Input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. When reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the Timer Input signal remains asserted). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reset.

Follow the steps below for configuring a timer for GATED mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for GATED mode.

- Set the prescale value.

**z**ilog<sup>°</sup>

configuration bits. In general, the address compare feature reduces the load on the CPU, because it does not require access to the UART when it receives data directed to other devices on the multi-node network. The following three MULTIPROCESSOR modes are available in hardware:

- 1. Interrupt on all address bytes.

- 2. Interrupt on matched address bytes and correctly framed data bytes.

- 3. Interrupt only on correctly framed data bytes.

These modes are selected with MPMD [1:0] in the UART Control 1 Register. For all multiprocessor modes, bit MPEN of the UART Control 1 Register must be set to 1.

The first scheme is enabled by writing 01b to MPMD[1:0]. In this mode, all incoming address bytes cause an interrupt, while data bytes never cause an interrupt. The interrupt service routine must manually check the address byte that caused triggered the interrupt. If it matches the UART address, the software clears MPMD[0]. Each new incoming byte interrupts the CPU. The software is responsible for determining the end of the frame. It checks for the end-of-frame by reading the MPRX bit of the UART Status 1 Register for each incoming byte. If MPRX=1, a new frame has begun. If the address of this new frame is different from the UART's address, MPMD[0] must be set to 1 causing the UART interrupts to go inactive until the next address byte. If the new frame's address matches the UART's, the data in the new frame is processed as well.

The second scheme requires the following: set MPMD[1:0] to 10B and write the UART's address into the UART Address Compare Register. This mode introduces additional hardware control, interrupting only on frames that match the UART's address. When an incoming address byte does not match the UART's address, it is ignored. All successive data bytes in this frame are also ignored. When a matching address byte occurs, an interrupt is issued and further interrupts now occur on each successive data byte. When the first data byte in the frame is read, the NEWFRM bit of the UART Status 1 Register is asserted. All successive data bytes have NEWFRM=0. When the next address byte occurs, the hardware compares it to the UART's address. If there is a match, the interrupts continues and the NEWFRM bit is set for the first byte of the new frame. If there is no match, the UART ignores all incoming bytes until the next address match.

The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second scheme, except that there are no interrupts on address bytes. The first data byte of each frame remains accompanied by a NEWFRM assertion.

#### **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.

IREN—Infrared Encoder/Decoder Enable

0 =Infrared Encoder/Decoder is disabled. UART operates normally.

1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.

#### **UART Status 0 Register**

The UART Status 0 (UxSTAT0) and Status 1(UxSTAT1) registers (Table 63 and Table 64) identify the current UART operating configuration and status.

Table 63. UART Status 0 Register (U0STAT0)

| BITS  | 7   | 6  | 5  | 4  | 3    | 2    | 1   | 0   |

|-------|-----|----|----|----|------|------|-----|-----|

| FIELD | RDA | PE | OE | FE | BRKD | TDRE | TXE | CTS |

| RESET | 0   | 0  | 0  | 0  | 0    | 1    | 1   | Х   |

| R/W   | R   | R  | R  | R  | R    | R    | R   | R   |

| ADDR  |     |    |    | F4 | 1H   |      |     |     |

RDA—Receive Data Available

This bit indicates that the UART Receive Data register has received data. Reading the UART Receive Data register clears this bit.

0 = The UART Receive Data register is empty.

1 = There is a byte in the UART Receive Data register.

PE—Parity Error

This bit indicates that a parity error has occurred. Reading the UART Receive Data register clears this bit.

0 = No parity error has occurred.

1 = A parity error has occurred.

OE—Overrun Error

This bit indicates that an overrun error has occurred. An overrun occurs when new data is received and the UART Receive Data register has not been read. If the RDA bit is reset to 0, reading the UART Receive Data register clears this bit.

- 0 = No overrun error occurred.

- 1 = An overrun error occurred.

FE—Framing Error

This bit indicates that a framing error (no Stop bit following data reception) was detected. Reading the UART Receive Data register clears this bit.

#### **ADC Control/Status Register 1**

The ADC Control/Status Register 1 (ADCCTL1) configures the input buffer stage, enables the threshold interrupts and contains the status of both threshold triggers. It is also used to select the voltage reference configuration.

#### Table 72. ADC Control/Status Register 1 (ADCCTL1)

| BITS  | 7       | 6   | 5    | 4     | 3   | 2   | 1         | 0   |

|-------|---------|-----|------|-------|-----|-----|-----------|-----|

| FIELD | REFSELH |     | Rese | erved |     | В   | UFMODE[2: | 0]  |

| RESET | 1       | 0   | 0    | 0     | 0   | 0   | 0         | 0   |

| R/W   | R/W     | R/W | R/W  | R/W   | R/W | R/W | R/W       | R/W |

| ADDR  |         |     |      | F7    | 1H  |     | ·         |     |

REFSELH—Voltage Reference Level Select High Bit; in conjunction with the Low bit (REFSELL) in ADC Control Register 0, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL}; this reference is independent of the Comparator reference.

00= Internal Reference Disabled, reference comes from external pin

01= Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

11= Reserved

BUFMODE[2:0] - Input Buffer Mode Select

000 =Single-ended, unbuffered input

- 001 = Single-ended, buffered input with unity gain

- 010 = Reserved

- 011 = Reserved

- 100 = Differential, unbuffered input

- 101 = Differential, buffered input with unity gain

- 110 = Reserved

- 111 = Reserved

#### ADC Data High Byte Register

The ADC Data High Byte (ADCD\_H) register contains the upper eight bits of the ADC output. The output is an 13-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

zilog |

## Comparator

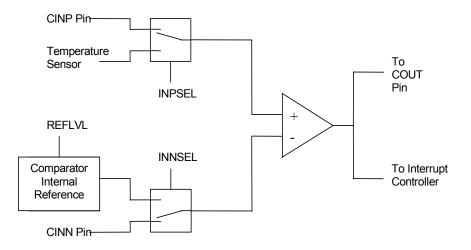

The Z8 Encore! XP<sup>®</sup> F082A Series devices feature a general purpose comparator that compares two analog input signals. These analog signals may be external stimulus from a pin (CINP and/or CINN) or internally generated signals. Both a programmable voltage reference and the temperature sensor output voltage are available internally. The output is available as an interrupt source or can be routed to an external pin.

Figure 20. Comparator Block Diagram

#### Operation

When the positive comparator input exceeds the negative input by more than the specified hysteresis, the output is a logic HIGH. When the negative input exceeds the positive by more than the hysteresis, the output is a logic LOW. Otherwise, the comparator output retains its present value. See Table 137 on page 233 for details.

The comparator may be powered down to reduce supply current. See Power Control Register 0 on page 34 for details.

**Caution:** Because of the propagation delay of the comparator, it is not recommended to enable or reconfigure the comparator without first disabling interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts. The following example describes how to safely enable the comparator:

```

di

ld cmp0, r0 ; load some new configuration

nop

```

138

zilog

162

| Info Page<br>Address | Memory<br>Address | Compensation Usage      | ADC Mode                 | Reference<br>Type |

|----------------------|-------------------|-------------------------|--------------------------|-------------------|

| 60                   | FE60              | Offset                  | Single-Ended Unbuffered  | Internal 2.0 V    |

| 08                   | FE08              | Gain High Byte          | Single-Ended Unbuffered  | Internal 2.0 V    |

| 09                   | FE09              | Gain Low Byte           | Single-Ended Unbuffered  | Internal 2.0 V    |

| 63                   | FE63              | Offset                  | Single-Ended Unbuffered  | Internal 1.0 V    |

| 0A                   | FE0A              | Gain High Byte          | Single-Ended Unbuffered  | Internal 1.0 V    |

| 0B                   | FE0B              | Gain Low Byte           | Single-Ended Unbuffered  | Internal 1.0 V    |

| 66                   | FE66              | Offset                  | Single-Ended Unbuffered  | External 2.0 V    |

| 0C                   | FE0C              | Gain High Byte          | Single-Ended Unbuffered  | External 2.0 V    |

| 0D                   | FE0D              | Gain Low Byte           | Single-Ended Unbuffered  | External 2.0 V    |

| 69                   | FE69              | Offset                  | Single-Ended 1x Buffered | Internal 2.0 V    |

| 0E                   | FE0E              | Gain High Byte          | Single-Ended 1x Buffered | Internal 2.0 V    |

| 0F                   | FE0F              | Gain Low Byte           | Single-Ended 1x Buffered | Internal 2.0 V    |

| 6C                   | FE6C              | Offset                  | Single-Ended 1x Buffered | External 2.0 V    |

| 10                   | FE10              | Gain High Byte          | Single-Ended 1x Buffered | External 2.0 V    |

| 11                   | FE11              | Gain Low Byte           | Single-Ended 1x Buffered | External 2.0 V    |

| 6F                   | FE6F              | Offset                  | Differential Unbuffered  | Internal 2.0 V    |

| 12                   | FE12              | Positive Gain High Byte | Differential Unbuffered  | Internal 2.0 V    |

| 13                   | FE13              | Positive Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V    |

| 30                   | FE30              | Negative Gain High Byte | Differential Unbuffered  | Internal 2.0 V    |

| 31                   | FE31              | Negative Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V    |

| 72                   | FE72              | Offset                  | Differential Unbuffered  | Internal 1.0 V    |

| 14                   | FE14              | Positive Gain High Byte | Differential Unbuffered  | Internal 1.0 V    |

| 15                   | FE15              | Positive Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V    |

| 32                   | FE32              | Negative Gain High Byte | Differential Unbuffered  | Internal 1.0 V    |

| 33                   | FE33              | Negative Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V    |

| 75                   | FE75              | Offset                  | Differential Unbuffered  | External 2.0 V    |

| 16                   | FE16              | Positive Gain High Byte | Differential Unbuffered  | External 2.0 V    |

| 17                   | FE17              | Positive Gain Low Byte  | Differential Unbuffered  | External 2.0 V    |

|                      |                   |                         |                          |                   |

#### Table 94. ADC Calibration Data Location

#### 200

#### Assembly Language Syntax

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed if manual program coding is preferred or if you intend to implement your own assembler.

**Example 1**: If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Table 112. Assembly Language Syntax Example 1

| Assembly Language<br>Code | ADD | 43H, | 08H | (ADD dst, src) |

|---------------------------|-----|------|-----|----------------|

| Object Code               | 04  | 08   | 43  | (OPC src, dst) |

**Example 2**: In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Table 113. Assembly Language Syntax Example 2

| Assembly Language<br>Code | ADD | 43H, | R8 | (ADD dst, src) |

|---------------------------|-----|------|----|----------------|

| Object Code               | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

#### eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is described in Table 114.

**z**ilog<sup>°</sup>

205

#### Table 119. CPU Control Instructions (Continued)

| Mnemonic Operands |     | Instruction            |

|-------------------|-----|------------------------|

| SCF               | _   | Set Carry Flag         |

| SRP               | SIC | Set Register Pointer   |

| STOP              | _   | STOP Mode              |

| WDT               | _   | Watchdog Timer Refresh |

#### Table 120. Load Instructions

| Mnemonic | Operands    | Instruction                                                             |

|----------|-------------|-------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                   |

| LD       | dst, src    | Load                                                                    |

| LDC      | dst, src    | Load Constant to/from Program Memory                                    |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                  |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                     |

| LDX      | dst, src    | Load using Extended Addressing                                          |

| LEA      | dst, X(src) | Load Effective Address                                                  |

| POP      | dst         | Рор                                                                     |

| POPX     | dst         | Pop using Extended Addressing                                           |

| PUSH     | src         | Push                                                                    |

| PUSHX    | src         | Push using Extended Addressing                                          |

|          |             |                                                                         |

#### Table 121. Logical Instructions

| Mnemonic | Operands | Instruction                           |

|----------|----------|---------------------------------------|

| AND      | dst, src | Logical AND                           |

| ANDX     | dst, src | Logical AND using Extended Addressing |

| COM      | dst      | Complement                            |

| OR       | dst, src | Logical OR                            |

zilog <sub>217</sub>

| Abbreviation | Description                           | Abbreviation                                   | Description            |

|--------------|---------------------------------------|------------------------------------------------|------------------------|

| b            | Bit position                          | IRR                                            | Indirect Register Pair |

| сс           | Condition code                        | р                                              | Polarity (0 or 1)      |

| X            | 8-bit signed index or<br>displacement | r                                              | 4-bit Working Register |

| DA           | Destination address                   | R                                              | 8-bit register         |

| ER           | Extended Addressing register          | r1, R1, Ir1, Irr1, IR1,<br>rr1, RR1, IRR1, ER1 | Destination address    |

| IM           | Immediate data value                  | r2, R2, Ir2, Irr2, IR2,<br>rr2, RR2, IRR2, ER2 | Source address         |

| Ir           | Indirect Working Register             | RA                                             | Relative               |

| IR           | Indirect register                     | rr                                             | Working Register Pair  |

| Irr          | Indirect Working Register Pair        | RR                                             | Register Pair          |

#### Table 125. Opcode Map Abbreviations

# zilog

# **Electrical Characteristics**

The data in this chapter is pre-qualification and pre-characterization and is subject to change. Additional electrical characteristics may be found in the individual chapters.

#### **Absolute Maximum Ratings**

Stresses greater than those listed in Table 126 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                                      | Minimum | Maximum | Units | Notes |

|----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                 | -40     | +105    | °C    |       |

| Storage temperature                                            | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>             | -0.3    | +5.5    | V     | 1     |

|                                                                | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$               | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin            | -5      | +5      | μA    |       |

| Maximum output current from active output pin                  | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0 °C to 70 °C                |         |         |       |       |

| Total power dissipation                                        |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$               |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0 °C to 70 °C               |         |         |       |       |

| Total power dissipation                                        |         | 430     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub> |         | 120     | mA    |       |

#### Table 126. Absolute Maximum Ratings

<mark>z</mark>ilog<sup>°</sup>

#### 251

# **Ordering Information**

Order the Z8 Encore! XP<sup>®</sup> F082A Series from Zilog<sup>®</sup>, using the following part numbers. For more information on ordering, please consult your local Zilog sales office. The Zilog website (<u>www.zilog.com</u>) lists all regional offices and provides additional Z8 Encore! XP product information.

| Part Number                                                                                                                       | Flash | RAM  | NVDS | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|-----------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082A Series with 8 KB Flash, 10-Bit Analog-to-Digital Converter<br>Standard Temperature: 0 °C to 70°C |       |      |      |           |            |                     |                     |                |            |                    |                     |

| Z8F082APB020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082APB020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          |                    | PDIP 20-pin package |

| Z8F082ASJ020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020SC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperature: -40 °C to 105 °C                                                                                            |       |      |      |           |            |                     |                     |                |            |                    |                     |

| Z8F082APB020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082AQB020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F082ASJ020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020EC                                                                                                                    | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging                                                                                          |       |      |      |           |            |                     |                     |                |            |                    |                     |

| ג<br>ש<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק | Flash<br>Serie | S Devel                                           | SQ<br>NN<br>Opmen | t Kit | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description |  |  |

|-------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------|-------------------|-------|------------|---------------------|---------------------|----------------|------------|--------------------|-------------|--|--|

| Z8F08A28100KITG                                                                                       | Cono           | Z8 Encore! XP F082A Series 28-Pin Development Kit |                   |       |            |                     |                     |                |            |                    |             |  |  |

| Z8F04A28100KITG                                                                                       |                | Z8 Encore! XP F042A Series 28-Pin Development Kit |                   |       |            |                     |                     |                |            |                    |             |  |  |

| Z8F04A08100KITG                                                                                       |                | Z8 Encore! XP F042A Series 8-Pin Development Kit  |                   |       |            |                     |                     |                |            |                    |             |  |  |

| ZUSBSC00100ZACG                                                                                       |                | USB Smart Cable Accessory Kit                     |                   |       |            |                     |                     |                |            |                    |             |  |  |

| ZUSBOPTSC01ZACG                                                                                       |                | USB Opto-Isolated Smart Cable Accessory Kit       |                   |       |            |                     |                     |                |            |                    |             |  |  |

| ZENETSC0100ZACG                                                                                       |                | Ethernet Smart Cable Accessory Kit                |                   |       |            |                     |                     |                |            |                    |             |  |  |

|                                                                                                       |                |                                                   |                   |       |            |                     |                     |                |            |                    |             |  |  |

RL 206

Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

zilog | 267

register 201 ADC control (ADCCTL) 130, 132 ADC data high byte (ADCDH) 132 ADC data low bits (ADCDL) 133 flash control (FCTL) 149, 155, 156 flash high and low byte (FFREQH and FREEQL) 152 flash page select (FPS) 150, 151 flash status (FSTAT) 150 GPIO port A-H address (PxADDR) 46 GPIO port A-H alternate function sub-registers 48 GPIO port A-H control address (PxCTL) 47 GPIO port A-H data direction sub-registers 47 OCD control 184 OCD status 185 UARTx baud rate high byte (UxBRH) 114 UARTx baud rate low byte (UxBRL) 114 UARTx Control 0 (UxCTL0) 108, 114 UARTx control 1 (UxCTL1) 109 UARTx receive data (UxRXD) 113 UARTx status 0 (UxSTAT0) 111 UARTx status 1 (UxSTAT1) 112 UARTx transmit data (UxTXD) 113 Watchdog Timer control (WDTCTL) 31, 94, 136, 190 Watchdog Timer reload high byte (WDTH) 95 Watchdog Timer reload low byte (WDTL) 95 Watchdog Timer reload upper byte (WD-TU) 95 register file 15 register pair 201 register pointer 202 reset and stop mode characteristics 24 and Stop Mode Recovery 23 carry flag 204 sources 25 **RET 206** return 206

RLC 206 rotate and shift instuctions 206 rotate left 206 rotate left through carry 206 rotate right 206 rotate right through carry 206 RP 202 RR 201, 206 rr 201 RRC 206

#### S

**SBC 203** SCF 204, 205 second opcode map after 1FH 219 set carry flag 204, 205 set register pointer 205 shift right arithmatic 207 shift right logical 207 signal descriptions 11 single-shot conversion (ADC) 123 software trap 206 source operand 202 SP 202 SRA 207 src 202 SRL 207 **SRP 205** stack pointer 202 **STOP 205** STOP mode 33 stop mode 205 Stop Mode Recovery sources 28 using a GPIO port pin transition 29 using Watchdog Timer time-out 29 stop mode recovery sources 30 using a GPIO port pin transition 30 SUB 203 subtract 203 subtract - extended addressing 203 subtract with carry 203