#### Zilog - Z8F042APB020SC2106 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | IrDA, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT  |

| Number of I/O              | 6                                                             |

| Program Memory Size        | 4KB (4K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | 128 x 8                                                       |

| RAM Size                   | 1K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | A/D 4x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Through Hole                                                  |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                        |

| Supplier Device Package    | 8-PDIP                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f042apb020sc2106 |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**z**ilog<sup>°</sup>

| Address (Hex)   | Register Description                 | Mnemonic | Reset (Hex) | Page No |

|-----------------|--------------------------------------|----------|-------------|---------|

| F0B             | Timer 1 Reload Low Byte              | T1RL     | FF          | 88      |

| F0C             | Timer 1 PWM High Byte                | T1PWMH   | 00          | 88      |

| F0D             | Timer 1 PWM Low Byte                 | T1PWML   | 00          | 89      |

| F0E             | Timer 1 Control 0                    | T1CTL0   | 00          | 83      |

| F0F             | Timer 1 Control 1                    | T1CTL1   | 00          | 84      |

| F10–F6F         | Reserved                             |          | XX          |         |

| UART            |                                      |          |             |         |

| F40             | UART Transmit/Receive Data Registers | TXD, RXD | XX          | 113     |

| F41             | UART Status 0 Register               | U0STAT0  | 00          | 111     |

| F42             | UART Control 0 Register              | U0CTL0   | 00          | 108     |

| F43             | UART Control 1 Register              | U0CTL1   | 00          | 108     |

| F44             | UART Status 1 Register               | U0STAT1  | 00          | 112     |

| F45             | UART Address Compare Register        | U0ADDR   | 00          | 114     |

| F46             | UART Baud Rate High Byte Register    | U0BRH    | FF          | 114     |

| F47             | UART Baud Rate Low Byte Register     | U0BRL    | FF          | 114     |

| Analog-to-Digit | tal Converter (ADC)                  |          |             |         |

| F70             | ADC Control 0                        | ADCCTL0  | 00          | 130     |

| F71             | ADC Control 1                        | ADCCTL1  | 80          | 130     |

| F72             | ADC Data High Byte                   | ADCD_H   | XX          | 133     |

| F73             | ADC Data Low Bits                    | ADCD_L   | XX          | 133     |

| F74–F7F         | Reserved                             |          | XX          |         |

| Low Power Co    | ntrol                                |          |             |         |

| F80             | Power Control 0                      | PWRCTL0  | 80          | 35      |

| F81             | Reserved                             | _        | XX          |         |

| LED Controller  |                                      |          |             |         |

| F82             | LED Drive Enable                     | LEDEN    | 00          | 52      |

| F83             | LED Drive Level High Byte            | LEDLVLH  | 00          | 53      |

| F84             | LED Drive Level Low Byte             | LEDLVLL  | 00          | 54      |

| F85             | Reserved                             | _        | XX          |         |

| Oscillator Cont | rol                                  |          |             |         |

| F86             | Oscillator Control                   | OSCCTL   | A0          | 190     |

| F87–F8F         | Reserved                             |          | XX          |         |

| Comparator 0    |                                      |          |             |         |

| F90             | Comparator 0 Control                 | CMP0     | 14          | 136     |

| XX=Undefined    |                                      | ···· ·   |             |         |

## Table 7. Register File Address Map (Continued)

20

zilog | 3

initiate Stop Mode Recovery without being written to the Port Input Data register or without initiating an interrupt (if enabled for that pin).

## Stop Mode Recovery Using the External RESET Pin

When the Z8 Encore! XP F082A Series device is in STOP mode and the external <u>RESET</u> pin is driven Low, a system reset occurs. Because of a glitch filter operating on the <u>RESET</u> pin, the Low pulse must be greater than the minimum width specified, or it is ignored. See Electrical Characteristics on page 221 for details.

## Low Voltage Detection

In addition to the Voltage Brownout (VBO) Reset described above, it is also possible to generate an interrupt when the supply voltage drops below a user-selected value. For details about configuring the Low Voltage Detection (LVD) and the threshold levels available, see Trim Bit Address 0003H on page 159. The LVD function is available on the 8-pin product versions only.

When the supply voltage drops below the LVD threshold, the LVD bit of the Reset Status (RSTSTAT) register is set to one. This bit remains one until the low-voltage condition goes away. Reading or writing this bit does not clear it. The LVD circuit can also generate an interrupt when so enabled, see Interrupt Vectors and Priority on page 58. The LVD bit is NOT latched, so enabling the interrupt is the only way to guarantee detection of a transient low voltage event.

The LVD functionality depends on circuitry shared with the VBO block; therefore, disabling the VBO also disables the LVD.

## **Reset Register Definitions**

The following sections define the Reset registers.

#### **Reset Status Register**

The Reset Status (RSTSTAT) register is a read-only register that indicates the source of the most recent Reset event, indicates a Stop Mode Recovery event, and indicates a Watchdog Timer time-out. Reading this register resets the upper four bits to 0.

This register shares its address with the Watchdog Timer control register, which is write-only (see Table 11 on page 31).

zilog /

tions as a GPIO pin. If it is not present, the debug feature is disabled until/unless another reset event occurs. For more details, see On-Chip Debugger on page 173.

# **Crystal Oscillator Override**

For systems using a crystal oscillator, PA0 and PA1 are used to connect the crystal. When the crystal oscillator is enabled (see Oscillator Control Register Definitions on page 190), the GPIO settings are overridden and PA0 and PA1 are disabled.

# **5 V Tolerance**

All six I/O pins on the 8-pin devices are 5 V-tolerant, unless the programmable pull-ups are enabled. If the pull-ups are enabled and inputs higher than  $V_{DD}$  are applied to these parts, excessive current flows through those pull-up devices and can damage the chip.

**Note:** In the 20- and 28-pin versions of this device, any pin which shares functionality with an ADC, crystal or comparator port is not 5 V-tolerant, including PA[1:0], PB[5:0] and PC[2:0]. All other signal pins are 5 V-tolerant, and can safely handle inputs higher than  $V_{DD}$  except when the programmable pull-ups are enabled.

# **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control (OSCCTL) register (see Oscillator Control Register Definitions on page 190) such that the external oscillator is selected as the system clock. For 8-pin devices use PA1 instead of PB3.

zilog<sup>®</sup>

| Port   | Pin | Mnemonic    | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------|-----------------------------------------|-----------------------------------------|

| Port A | PA0 | T0IN/T0OUT* | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|        |     | Reserved    |                                         | -                                       |

|        | PA1 | TOOUT       | Timer 0 Output                          | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA2 | DE0         | UART 0 Driver Enable                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA3 | CTS0        | UART 0 Clear to Send                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA4 | RXD0/IRRX0  | UART 0/IrDA 0 Receive Data              | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA5 | TXD0/IRTX0  | UART 0/IrDA 0 Transmit Data             | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA6 | T1IN/T1OUT* | Timer 1 Input/Timer 1 Output Complement | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA7 | T1OUT       | Timer 1 Output                          | -                                       |

|        |     | Reserved    |                                         | -                                       |

#### Table 14. Port Alternate Function Mapping (Non 8-Pin Parts)

**Note:** Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in Port A–D Alternate Function Sub-Registers on page 47 automatically enables the associated alternate function.

\* Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in Timer Pin Signal Operation on page 82.

PAFS1[7:0]—Port Alternate Function Set 1 0 = Port Alternate Function selected as defined in Table 14 and Table 15 on page 44. 1 = Port Alternate Function selected as defined in Table 14 and Table 15 on page 44.

#### Port A–D Alternate Function Set 2 Sub-Registers

The Port A–D Alternate Function Set 2 sub-register (Table 26) is accessed through the Port A–D Control register by writing 08H to the Port A–D Address register. The Alternate Function Set 2 sub-registers selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register is defined in Table 15.

• Note: Alternate function selection on port pins must also be enabled as described in Port A–D Alternate Function Sub-Registers on page 47.

| BITS  | 7                                                                                     | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|

| FIELD | PAFS27                                                                                | PAFS26 | PAFS25 | PAFS24 | PAFS23 | PAFS22 | PAFS21 | PAFS20 |

| RESET | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device)                    |        |        |        |        |        |        |        |

| R/W   | R/W R/W R/W R/W R/W R/W R/W                                                           |        |        |        |        |        |        |        |

| ADDR  | If 08H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |        |        |

Table 26. Port A–D Alternate Function Set 2 Sub-Registers (PxAFS2)

PAFS2[7:0]—Port Alternate Function Set 2

0 = Port Alternate Function selected as defined in Table 15.

1 = Port Alternate Function selected as defined in Table 15.

## Port A–C Input Data Registers

Reading from the Port A–C Input Data registers (Table 27) returns the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those missing on the 8- and 28-pin packages, as well as those missing on the ADC-enabled 28-pin packages.

| Table 27. Port A–C Input Data Registers (PxIN) | Table 27. | Port A–C | Input Data | Registers | (PxIN) |

|------------------------------------------------|-----------|----------|------------|-----------|--------|

|------------------------------------------------|-----------|----------|------------|-----------|--------|

| BITS      | 7                | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----------|------------------|------|------|------|------|------|------|------|

| FIELD     | PIN7             | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |

| RESET     | Х                | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| R/W       | R                | R    | R    | R    | R    | R    | R    | R    |

| ADDR      | FD2H, FD6H, FDAH |      |      |      |      |      |      |      |

| X = Undef | X = Undefined.   |      |      |      |      |      |      |      |

**Caution:** The following coding style that clears bits in the Interrupt Request registers is not recommended. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost.

Poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

Caution: To avoid missing interrupts, use the following coding style to clear bits in the Interrupt Request 0 register:

Good coding style that avoids lost interrupt requests:

ANDX IRQ0, MASK

#### Software Interrupt Assertion

Program code can generate interrupts directly. Writing a 1 to the correct bit in the Interrupt Request register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request register is automatically cleared to 0.

**Caution:** The following coding style used to generate software interrupts by setting bits in the Interrupt Request registers is not recommended. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost.

Poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 OR r0, MASK LDX IRQ0, r0

**Caution:** To avoid missing interrupts, use the following coding style to set bits in the Interrupt Request registers:

> Good coding style that avoids lost interrupt requests: ORX IRQO, MASK

#### Watchdog Timer Interrupt Assertion

The Watchdog Timer interrupt behavior is different from interrupts generated by other sources. The Watchdog Timer continues to assert an interrupt as long as the timeout condition continues. As it operates on a different (and usually slower) clock domain than the rest of the device, the Watchdog Timer continues to assert this interrupt for many system clocks until the counter rolls over.

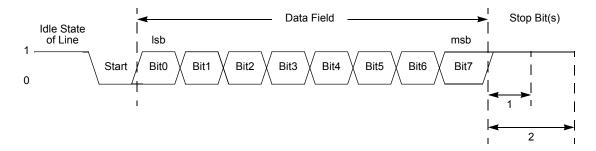

Figure 11. UART Asynchronous Data Format without Parity

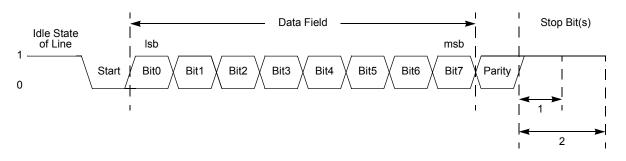

Figure 12. UART Asynchronous Data Format with Parity

#### Transmitting Data using the Polled Method

Follow the steps below to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Write to the UART Control 1 register, if MULTIPROCESSOR mode is appropriate, to enable MULTIPROCESSOR (9-bit) mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR mode.

- 5. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR mode is not enabled, and select either even or odd parity (PSEL).

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin.

1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.

IREN—Infrared Encoder/Decoder Enable

0 =Infrared Encoder/Decoder is disabled. UART operates normally.

1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.

#### **UART Status 0 Register**

The UART Status 0 (UxSTAT0) and Status 1(UxSTAT1) registers (Table 63 and Table 64) identify the current UART operating configuration and status.

Table 63. UART Status 0 Register (U0STAT0)

| BITS  | 7   | 6             | 5  | 4  | 3    | 2    | 1   | 0   |

|-------|-----|---------------|----|----|------|------|-----|-----|

| FIELD | RDA | PE            | OE | FE | BRKD | TDRE | TXE | CTS |

| RESET | 0   | 0             | 0  | 0  | 0    | 1    | 1   | Х   |

| R/W   | R   | R R R R R R R |    |    |      |      |     |     |

| ADDR  |     | F41H          |    |    |      |      |     |     |

RDA—Receive Data Available

This bit indicates that the UART Receive Data register has received data. Reading the UART Receive Data register clears this bit.

0 = The UART Receive Data register is empty.

1 = There is a byte in the UART Receive Data register.

PE—Parity Error

This bit indicates that a parity error has occurred. Reading the UART Receive Data register clears this bit.

0 = No parity error has occurred.

1 = A parity error has occurred.

OE—Overrun Error

This bit indicates that an overrun error has occurred. An overrun occurs when new data is received and the UART Receive Data register has not been read. If the RDA bit is reset to 0, reading the UART Receive Data register clears this bit.

- 0 = No overrun error occurred.

- 1 = An overrun error occurred.

FE—Framing Error

This bit indicates that a framing error (no Stop bit following data reception) was detected. Reading the UART Receive Data register clears this bit.

0 = No framing error occurred. 1 = A framing error occurred.

BRKD—Break Detect

This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data register clears this bit. 0 = No break occurred.

1 = A break occurred.

TDRE—Transmitter Data Register Empty

This bit indicates that the UART Transmit Data register is empty and ready for additional data. Writing to the UART Transmit Data register resets this bit.

0 = Do not write to the UART Transmit Data register.

1 = The UART Transmit Data register is ready to receive an additional byte to be transmitted.

TXE—Transmitter Empty

This bit indicates that the transmit shift register is empty and character transmission is finished.

0 = Data is currently transmitting.

1 = Transmission is complete.

$CTS \longrightarrow \overline{CTS}$  signal

When this bit is read it returns the level of the  $\overline{\text{CTS}}$  signal. This signal is active Low.

#### **UART Status 1 Register**

This register contains multiprocessor control and status bits.

Table 64. UART Status 1 Register (U0STAT1)

| BITS  | 7 | 6                    | 5 | 4 | 3   | 2   | 1 | 0 |

|-------|---|----------------------|---|---|-----|-----|---|---|

| FIELD |   | Reserved NEWFRM MPRX |   |   |     |     |   |   |

| RESET | 0 | 0                    | 0 | 0 | 0   | 0   | 0 | 0 |

| R/W   | R | R                    | R | R | R/W | R/W | R | R |

| ADDR  |   | F44H                 |   |   |     |     |   |   |

Reserved—Must be 0.

NEWFRM—Status bit denoting the start of a new frame. Reading the UART Receive Data register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame.

1 = The current byte is the first data byte of a new frame.

zilog

value 63H to the Flash Control register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

#### **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programming is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information on bypassing the Flash Controller, refer to *Third-Party Flash Pro*gramming Support for Z8 Encore!<sup>®</sup> MCU Application Note (AN0117) available for download at <u>www.zilog.com</u>.

#### Flash Controller Behavior in DEBUG Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored.

- The Flash Sector Protect register is ignored for programming and erase operations.

- Programming operations are not limited to the page selected in the Page Select register.

- Bits in the Flash Sector Protect register can be written to one or zero.

- The second write of the Page Select register to unlock the Flash Controller is not necessary.

- The Page Select register can be written when the Flash Controller is unlocked.

- The Mass Erase command is enabled through the Flash Control register.

**Caution:** For security reasons, the Flash controller allows only a single page to be opened for write/erase. When writing multiple Flash pages, the flash controller must go through the unlock sequence again to select another page.

zilog

152

SPROT7-SPROT0—Sector Protection

Each bit corresponds to a 512 byte Flash sector. For the Z8F08xx devices, the upper 3 bits must be zero. For the Z8F04xx devices all bits are used. For the Z8F02xx devices, the upper 4 bits are unused. For the Z8F01xx devices, the upper 6 bits are unused.

## Flash Frequency High and Low Byte Registers

The Flash Frequency High (FFREQH) and Low Byte (FFREQL) registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:

$FFREQ[15:0] = \{FFREQH[7:0], FFREQL[7:0]\} = \frac{System Clock Frequency}{1000}$

**Caution:** The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper operation of the device. Also, Flash programming and erasure is not supported for system clock frequencies below 20 kHz or above 20 MHz.

#### Table 82. Flash Frequency High Byte Register (FFREQH)

| BITS  | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|-----------------------------|---|---|---|---|---|---|

| FIELD |     | FFREQH                      |   |   |   |   |   |   |

| RESET | 0   | 0                           | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |

| ADDR  |     | FFAH                        |   |   |   |   |   |   |

FFREQH—Flash Frequency High Byte

High byte of the 16-bit Flash Frequency value.

#### Table 83. Flash Frequency Low Byte Register (FFREQL)

| BITS  | 7 | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |

|-------|---|-----------------|--|--|--|--|--|--|--|

| FIELD |   | FFREQL          |  |  |  |  |  |  |  |

| RESET |   | 0               |  |  |  |  |  |  |  |

| R/W   |   | R/W             |  |  |  |  |  |  |  |

| ADDR  |   | FFBH            |  |  |  |  |  |  |  |

FFREQL—Flash Frequency Low Byte Low byte of the 16-bit Flash Frequency value.

zilog

160

Reserved—Must be 1.

LVD TRIM-Low Voltage Detect Trim

This trimming affects the low voltage detection threshold. Each LSB represents a 50 mV change in the threshold level. Alternatively, the low voltage threshold may be computed from the options bit value by the following equation:

LVD\_LVL =  $3.6 \text{ V} - \text{LVD} \text{TRIM} \times 0.05 \text{ V}$

| LV          | /D Threshold ( | (V)                   |

|-------------|----------------|-----------------------|

| LVD_TRIM    | Typical        | Description           |

| 00000       | 3.60           | Maximum LVD threshold |

| 00001       | 3.55           |                       |

| 00010       | 3.50           |                       |

| 00011       | 3.45           |                       |

| 00100       | 3.40           |                       |

| 00101       | 3.35           |                       |

| 00110       | 3.30           |                       |

| 00111       | 3.25           |                       |

| 01000       | 3.20           |                       |

| 01001       | 3.15           |                       |

| 01010       | 3.10           | Default on Reset      |

| 01011       | 3.05           |                       |

| 01100       | 3.00           |                       |

| 01101       | 2.95           |                       |

| 01110       | 2.90           |                       |

| 01111       | 2.85           |                       |

| 10000       | 2.80           |                       |

| 10001       | 2.75           |                       |

| 10010       | 2.70           |                       |

| 10011       | 2.70           |                       |

| to<br>11111 | to<br>1.65     | Minimum LVD threshold |

# zilog <sub>172</sub>

#### Table 104. NVDS Read Time (Continued)

| Operation              | Minimum<br>Latency | Maximum<br>Latency |

|------------------------|--------------------|--------------------|

| Read (128 byte array)  | 883                | 7609               |

| Write (16 byte array)  | 4973               | 5009               |

| Write (64 byte array)  | 4971               | 5013               |

| Write (128 byte array) | 4984               | 5023               |

| Illegal Read           | 43                 | 43                 |

| Illegal Write          | 31                 | 31                 |

If NVDS read performance is critical to your software architecture, there are some things you can do to optimize your code for speed, listed in order from most helpful to least helpful:

- Periodically refresh all addresses that are used. The optimal use of NVDS in terms of speed is to rotate the writes evenly among all addresses planned to use, bringing all reads closer to the minimum read time. Because the minimum read time is much less than the write time, however, actual speed benefits are not always realized.

- Use as few unique addresses as possible: this helps to optimize the impact of refreshing as well as minimize the requirement for it.

# zilog

# **Crystal Oscillator**

The products in the Z8 Encore! XP<sup>®</sup> F082A Series contain an on-chip crystal oscillator for use with external crystals with 32 kHz to 20 MHz frequencies. In addition, the oscillator supports external RC networks with oscillation frequencies up to 4 MHz or ceramic resonators with frequencies up to 8 MHz. The on-chip crystal oscillator can be used to generate the primary system clock for the internal eZ8 CPU and the majority of the on-chip peripherals. Alternatively, the X<sub>IN</sub> input pin can also accept a CMOS-level clock input signal (32 kHz–20 MHz). If an external clock generator is used, the X<sub>OUT</sub> pin must be left unconnected. The Z8 Encore! XP F082A Series products do not contain an internal clock divider. The frequency of the signal on the X<sub>IN</sub> input pin determines the frequency of the system clock.

Note:

Although the XIN pin can be used as an input for an external clock generator, the CLKIN pin is better suited for such use (see System Clock Selection on page 187).

# **Operating Modes**

The Z8 Encore! XP F082A Series products support four oscillator modes:

- Minimum power for use with very low frequency crystals (32 kHz–1 MHz).

- Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 8 MHz).

- Maximum power for use with high frequency crystals (8 MHz to 20 MHz).

- On-chip oscillator configured for use with external RC networks (<4 MHz).

The oscillator mode is selected using user-programmable Flash Option Bits. See Flash Option Bits on page 153 for information.

# **Crystal Oscillator Operation**

The Flash Option bit XTLDIS controls whether the crystal oscillator is enabled during reset. The crystal may later be disabled after reset if a new oscillator has been selected as the system clock. If the crystal is manually enabled after reset through the OSCCTL register, the user code must wait at least 1000 crystal oscillator cycles for the crystal to stabilize. After this, the crystal oscillator may be selected as the system clock.

• Note: The stabilization time varies depending on the crystal or resonator used, as well as on the feedback network. See Table 111 for transconductance values to compute oscillator stabilization times.

PS022825-0908

**z**ilog<sup>°</sup>

205

#### Table 119. CPU Control Instructions (Continued)

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| SCF      | _        | Set Carry Flag         |

| SRP      | SIC      | Set Register Pointer   |

| STOP     | _        | STOP Mode              |

| WDT      | _        | Watchdog Timer Refresh |

#### Table 120. Load Instructions

| Mnemonic | Operands    | Instruction                                                             |

|----------|-------------|-------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                   |

| LD       | dst, src    | Load                                                                    |

| LDC      | dst, src    | Load Constant to/from Program Memory                                    |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                  |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                     |

| LDX      | dst, src    | Load using Extended Addressing                                          |

| LEA      | dst, X(src) | Load Effective Address                                                  |

| POP      | dst         | Рор                                                                     |

| POPX     | dst         | Pop using Extended Addressing                                           |

| PUSH     | src         | Push                                                                    |

| PUSHX    | src         | Push using Extended Addressing                                          |

|          |             |                                                                         |

## Table 121. Logical Instructions

| Mnemonic | Operands | Instruction                           |

|----------|----------|---------------------------------------|

| AND      | dst, src | Logical AND                           |

| ANDX     | dst, src | Logical AND using Extended Addressing |

| COM      | dst      | Complement                            |

| OR       | dst, src | Logical OR                            |

236

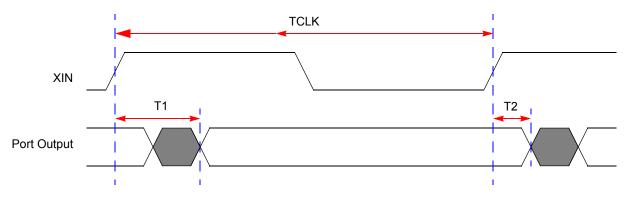

# General Purpose I/O Port Output Timing

Figure 35 and Table 140 provide timing information for GPIO Port pins.

## Figure 35. GPIO Port Output Timing

|                |                                     | Delay (ns) |         |  |  |  |

|----------------|-------------------------------------|------------|---------|--|--|--|

| Parameter      | Abbreviation                        | Minimum    | Maximum |  |  |  |

| GPIO Port      | pins                                |            |         |  |  |  |

| T <sub>1</sub> | XIN Rise to Port Output Valid Delay | _          | 15      |  |  |  |

| T <sub>2</sub> | XIN Rise to Port Output Hold Time   | 2          | _       |  |  |  |

#### Table 140. GPIO Port Output Timing

Zilog 244

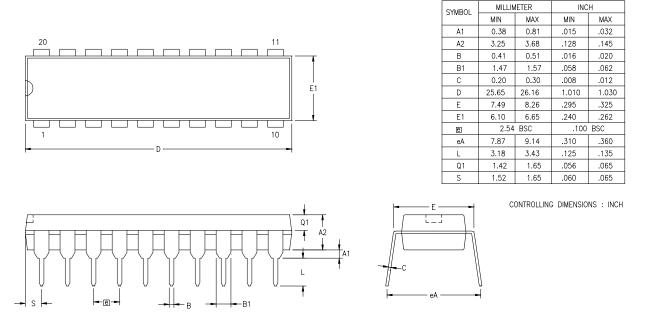

Figure 42 displays the 20-pin Plastic Dual Inline Package (PDIP) available for the Z8 Encore! XP F082A Series devices.

Figure 42. 20-Pin Plastic Dual Inline Package (PDIP)

zilog 257

| Part Number                     | Flash     | RAM      | SUVN   | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------|-----------|----------|--------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082 | A Serie   | s with 1 | KB Fla | ish, 1    | 0-Bit      | Ana                 | log-t               | o-Dig          | jital C    | Conv               | verter              |

| Standard Temperatu              | re: 0 °C  | to 70 °C | ;      |           |            |                     |                     |                |            |                    |                     |

| Z8F012APB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperatu              | re: -40 ° | C to 10  | 5 °C   |           |            |                     |                     |                |            |                    |                     |

| Z8F012APB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| ג<br>ש<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק<br>ע<br>ק | Flash<br>Serie | S Devel                                           | SQ<br>NND | t Kit | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description |  |

|-------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------|-----------|-------|------------|---------------------|---------------------|----------------|------------|--------------------|-------------|--|

| Z8F08A28100KITG                                                                                       | •              |                                                   |           |       |            |                     |                     |                |            |                    |             |  |

| Z8F04A28100KITG                                                                                       |                | Z8 Encore! XP F042A Series 28-Pin Development Kit |           |       |            |                     |                     |                |            |                    |             |  |

| Z8F04A08100KITG                                                                                       |                | Z8 Encore! XP F042A Series 8-Pin Development Kit  |           |       |            |                     |                     |                |            |                    |             |  |

| ZUSBSC00100ZACG                                                                                       |                | USB Smart Cable Accessory Kit                     |           |       |            |                     |                     |                |            |                    |             |  |

| ZUSBOPTSC01ZACG                                                                                       |                | USB Opto-Isolated Smart Cable Accessory Kit       |           |       |            |                     |                     |                |            |                    |             |  |

| ZENETSC0100ZACG                                                                                       |                | Ethernet Smart Cable Accessory Kit                |           |       |            |                     |                     |                |            |                    |             |  |

|                                                                                                       |                |                                                   |           |       |            |                     |                     |                |            |                    |             |  |

263

page erase 147 page select register 150, 151 FPS register 150, 151 FSTAT register 150

# G

GATED mode 85 general-purpose I/O 37 GPIO 7, 37 alternate functions 38 architecture 38 control register definitions 45 input data sample timing 234 interrupts 45 port A-C pull-up enable sub-registers 50, 51 port A-H address registers 46 port A-H alternate function sub-registers 47 port A-H control registers 46 port A-H data direction sub-registers 47 port A-H high drive enable sub-registers 49 port A-H input data registers 51 port A-H output control sub-registers 48 port A-H output data registers 52 port A-H stop mode recovery sub-registers 49 port availability by device 37 port input timing 235 port output timing 236

# Η

H 202 HALT 204 halt mode 34, 204 hexadecimal number prefix/suffix 202

# I

I2C 7 IM 201 immediate data 201 immediate operand prefix 202 **INC 203** increment 203 increment word 203 **INCW 203** indexed 201 indirect address prefix 202 indirect register 201 indirect register pair 201 indirect working register 201 indirect working register pair 201 infrared encoder/decoder (IrDA) 117 Instruction Set 199 instruction set. eZ8 CPU 199 instructions ADC 203 ADCX 203 ADD 203 **ADDX 203** AND 205 **ANDX 205** arithmetic 203 **BCLR 204** BIT 204 bit manipulation 204 block transfer 204 **BRK 206 BSET 204** BSWAP 204, 206 **BTJ 206 BTJNZ 206 BTJZ 206 CALL 206** CCF 204 CLR 205 COM 205 CP 203 CPC 203 **CPCX 203** CPU control 204 **CPX 203** DA 203 **DEC 203 DECW 203**

DI 204