Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 20000                      |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Obsolete                                                     |

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 6                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 128 × 8                                                      |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 4x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 8-VDFN Exposed Pad                                           |

| Supplier Device Package    | 8-QFN (5x6)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f042aqb020sc    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

zilog <sub>21</sub>

| Address (Hex)   | Register Description    | Mnemonic | Reset (Hex) | Page No |

|-----------------|-------------------------|----------|-------------|---------|

| F91–FBF         | Reserved                | —        | XX          |         |

| Interrupt Contr | oller                   |          |             |         |

| FC0             | Interrupt Request 0     | IRQ0     | 00          | 60      |

| FC1             | IRQ0 Enable High Bit    | IRQ0ENH  | 00          | 63      |

| FC2             | IRQ0 Enable Low Bit     | IRQ0ENL  | 00          | 63      |

| FC3             | Interrupt Request 1     | IRQ1     | 00          | 61      |

| FC4             | IRQ1 Enable High Bit    | IRQ1ENH  | 00          | 64      |

| FC5             | IRQ1 Enable Low Bit     | IRQ1ENL  | 00          | 64      |

| FC6             | Interrupt Request 2     | IRQ2     | 00          | 62      |

| FC7             | IRQ2 Enable High Bit    | IRQ2ENH  | 00          | 65      |

| FC8             | IRQ2 Enable Low Bit     | IRQ2ENL  | 00          | 65      |

| FC9–FCC         | Reserved                | —        | XX          |         |

| FCD             | Interrupt Edge Select   | IRQES    | 00          | 67      |

| FCE             | Shared Interrupt Select | IRQSS    | 00          | 67      |

| FCF             | Interrupt Control       | IRQCTL   | 00          | 67      |

| GPIO Port A     |                         |          |             |         |

| FD0             | Port A Address          | PAADDR   | 00          | 45      |

| FD1             | Port A Control          | PACTL    | 00          | 47      |

| FD2             | Port A Input Data       | PAIN     | XX          | 47      |

| FD3             | Port A Output Data      | PAOUT    | 00          | 47      |

| GPIO Port B     |                         |          |             |         |

| FD4             | Port B Address          | PBADDR   | 00          | 45      |

| FD5             | Port B Control          | PBCTL    | 00          | 47      |

| FD6             | Port B Input Data       | PBIN     | XX          | 47      |

| FD7             | Port B Output Data      | PBOUT    | 00          | 47      |

| GPIO Port C     |                         |          |             |         |

| FD8             | Port C Address          | PCADDR   | 00          | 45      |

| FD9             | Port C Control          | PCCTL    | 00          | 47      |

| FDA             | Port C Input Data       | PCIN     | XX          | 47      |

| FDB             | Port C Output Data      | PCOUT    | 00          | 47      |

| GPIO Port D     |                         |          |             |         |

| FDC             | Port D Address          | PDADDR   | 00          | 45      |

| FDD             | Port D Control          | PDCTL    | 00          | 47      |

| FDE             | Reserved                |          | XX          |         |

| XX=Undefined    |                         |          |             |         |

## Table 7. Register File Address Map (Continued)

|                                                       | Reset Characteristics and Latency                      |            |                                                               |  |  |  |  |

|-------------------------------------------------------|--------------------------------------------------------|------------|---------------------------------------------------------------|--|--|--|--|

| Reset Type                                            | Control Registers                                      | eZ8<br>CPU | Reset Latency (Delay)                                         |  |  |  |  |

| System Reset                                          | Reset (as applicable)                                  | Reset      | 66 Internal Precision Oscillator Cycles                       |  |  |  |  |

| System Reset with Crystal Oscillator Enabled          | Reset (as applicable)                                  | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |  |

| Stop Mode Recovery                                    | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |  |  |

| Stop Mode Recovery with<br>Crystal Oscillator Enabled | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |  |

### Table 8. Reset and Stop Mode Recovery Characteristics and Latency

During a System Reset or Stop Mode Recovery, the Internal Precision Oscillator requires 4  $\mu$ s to start up. Then the Z8 Encore! XP F082A Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset (POR), this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled, except PD0 (or PA2 on 8-pin devices) which is shared with the reset pin. On reset, the PD0 is configured as a bidirectional open-drain reset. The pin is internally driven low during port reset, after which the user code may reconfigure this pin as a general purpose output.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

As the control registers are re-initialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

| BITS  | 7     | 6            | 5     | 4   | 3  | 2   | 1 | 0 |

|-------|-------|--------------|-------|-----|----|-----|---|---|

| FIELD | POR   | STOP         | WDT   | EXT |    | LVD |   |   |

| RESET | See d | lescriptions | below | 0   | 0  | 0   | 0 | 0 |

| R/W   | R     | R            | R     | R   | R  | R   |   |   |

| ADDR  |       |              |       | FF  | 0H |     |   |   |

### Table 11. Reset Status Register (RSTSTAT)

| Reset or Stop Mode Recovery Event                     | POR | STOP | WDT | EXT |

|-------------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                        | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion                       | 0   | 0    | 0   | 1   |

| Reset using Watchdog Timer time-out                   | 0   | 0    | 1   | 0   |

| Reset using the On-Chip Debugger (OCTCTL[1] set to 1) | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low         | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition          | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using Watchdog Timer time-out      | 0   | 1    | 1   | 0   |

#### POR—Power-On Reset Indicator

If this bit is set to 1, a Power-On Reset event occurs. This bit is reset to 0 if a WDT time-out or Stop Mode Recovery occurs. This bit is also reset to 0 when the register is read.

#### STOP—Stop Mode Recovery Indicator

If this bit is set to 1, a Stop Mode Recovery occurs. If the STOP and WDT bits are both set to 1, the Stop Mode Recovery occurs because of a WDT time-out. If the STOP bit is 1 and the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a Power-On Reset or a WDT time-out that occurred while not in STOP mode. Reading this register also resets this bit.

#### WDT—Watchdog Timer Time-Out Indicator

If this bit is set to 1, a WDT time-out occurs. A POR resets this pin. A Stop Mode Recovery from a change in an input pin also resets this bit. Reading this register resets this bit. This read must occur before clearing the WDT interrupt.

#### EXT-External Reset Indicator

If this bit is set to 1, a Reset initiated by the external  $\overline{\text{RESET}}$  pin occurs. A Power-On Reset or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register resets this bit.

#### Reserved—Must be 0.

LVD—Low Voltage Detection Indicator

If this bit is set to 1 the current state of the supply voltage is below the low voltage detection threshold. This value is not latched but is a real-time indicator of the supply voltage level.

zilog<sup>®</sup>

Set 1 Sub-Registers on page 50, GPIO Alternate Functions on page 38, and Port A–D Alternate Function Set 2 Sub-Registers on page 51. See GPIO Alternate Functions on page 38 to determine the alternate function associated with each port pin.

Caution:

Do not enable alternate functions for GPIO port pins for which there is no associated alternate function. Failure to follow this guideline can result in unpredictable operation.

| Table 20. Port A–D Alternate Function Sub-Registers | (PxAF) |  |

|-----------------------------------------------------|--------|--|

|                                                     |        |  |

| BITS  | 7        | 6                                                           | 5           | 4             | 3            | 2             | 1            | 0        |  |  |  |  |

|-------|----------|-------------------------------------------------------------|-------------|---------------|--------------|---------------|--------------|----------|--|--|--|--|

| FIELD | AF7      | AF6                                                         | AF5         | AF4           | AF3          | AF2           | AF1          | AF0      |  |  |  |  |

| RESET |          | 00H (Ports A–C); 01H (Port D); 04H (Port A of 8-pin device) |             |               |              |               |              |          |  |  |  |  |

| R/W   |          | R/W                                                         |             |               |              |               |              |          |  |  |  |  |

| ADDR  | lf 02H i | n Port A–D /                                                | Address Reg | gister, acces | sible throug | n the Port A- | –D Control F | Register |  |  |  |  |

AF[7:0]—Port Alternate Function enabled

0 = The port pin is in normal mode and the DDx bit in the Port A–D Data Direction sub-register determines the direction of the pin.

1 = The alternate function selected through Alternate Function Set sub-registers is enabled. Port pin operation is controlled by the alternate function.

## Port A–D Output Control Sub-Registers

The Port A–D Output Control sub-register (Table 21) is accessed through the Port A–D Control register by writing 03H to the Port A–D Address register. Setting the bits in the Port A–D Output Control sub-registers to 1 configures the specified port pins for opendrain operation. These sub-registers affect the pins directly and, as a result, alternate functions are also affected.

## Table 21. Port A–D Output Control Sub-Registers (PxOC)

| BITS  | 7        | 6          | 5           | 4             | 3             | 2             | 1            | 0        |

|-------|----------|------------|-------------|---------------|---------------|---------------|--------------|----------|

| FIELD | POC7     | POC6       | POC5        | POC4          | POC3          | POC2          | POC1         | POC0     |

| RESET |          |            | 001         | H (Ports A-C  | c); 01H (Port | D)            |              |          |

| R/W   | R/W      | R/W        | R/W         | R/W           | R/W           | R/W           | R/W          | R/W      |

| ADDR  | lf 03H i | n Port A–D | Address Reg | gister, acces | sible throug  | n the Port A- | -D Control F | Register |

POC[7:0]—Port Output Control

These bits function independently of the alternate function bit and always disable the drains if set to 1.

0 = The source current is enabled for any output mode (unless overridden by the alternate

function). (Push-pull output)

1 = The source current for the associated pin is disabled (open-drain mode).

## Port A–D High Drive Enable Sub-Registers

The Port A–D High Drive Enable sub-register (Table 22) is accessed through the Port A–D Control register by writing 04H to the Port A–D Address register. Setting the bits in the Port A–D High Drive Enable sub-registers to 1 configures the specified port pins for high current output drive operation. The Port A–D High Drive Enable sub-register affects the pins directly and, as a result, alternate functions are also affected.

Table 22. Port A–D High Drive Enable Sub-Registers (PxHDE)

| BITS  | 7        | 6                                                                                     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|-------|----------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|--|

| FIELD | PHDE7    | PHDE6                                                                                 | PHDE5 | PHDE4 | PHDE3 | PHDE2 | PHDE1 | PHDE0 |  |  |

| RESET | 0        | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| R/W   | R/W      | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |

| ADDR  | lf 04H i | If 04H in Port A–D Address Register, accessible through the Port A–D Control Register |       |       |       |       |       |       |  |  |

PHDE[7:0]—Port High Drive Enabled

0 = The Port pin is configured for standard output current drive.

1 = The Port pin is configured for high output current drive.

## Port A–D Stop Mode Recovery Source Enable Sub-Registers

The Port A–D Stop Mode Recovery Source Enable sub-register (Table 23) is accessed through the Port A–D Control register by writing 05H to the Port A–D Address register. Setting the bits in the Port A–D Stop Mode Recovery Source Enable sub-registers to 1 configures the specified Port pins as a Stop Mode Recovery source. During STOP mode, any logic transition on a Port pin enabled as a Stop Mode Recovery source initiates Stop Mode Recovery.

| BITS  | 7        | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|-------|----------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|

| FIELD | PSMRE7   | PSMRE6                                                                                | PSMRE5 | PSMRE4 | PSMRE3 | PSMRE2 | PSMRE1 | PSMRE0 |  |  |

| RESET | 0        | 0                                                                                     | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W                                                           |        |        |        |        |        |        |  |  |

| ADDR  | lf 05H i | If 05H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |        |  |  |

PSMRE[7:0]—Port Stop Mode Recovery Source Enabled

0 = The Port pin is not configured as a Stop Mode Recovery source. Transitions on this pin

# **Interrupt Controller**

The interrupt controller on the Z8 Encore! XP F082A Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of interrupt controller include:

- 20 possible interrupt sources with 18 unique interrupt vectors:

- Twelve GPIO port pin interrupt sources (two interrupt vectors are shared).

- Eight on-chip peripheral interrupt sources (two interrupt vectors are shared).

- Flexible GPIO interrupts:

- Eight selectable rising and falling edge GPIO interrupts.

- Four dual-edge interrupts.

- Three levels of individually programmable interrupt priority.

- Watchdog Timer and LVD can be configured to generate an interrupt.

- Supports vectored as well as polled interrupts

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt controller has no effect on operation. For more information on interrupt servicing by the eZ8 CPU, refer to *eZ8 CPU Core User Manual (UM0128)* available for download at <u>www.zilog.com</u>.

## Interrupt Vector Listing

Table 32 on page 56 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most-significant byte (MSB) at the even Program Memory address and the least-significant byte (LSB) at the following odd Program Memory address.

**Note:** Some port interrupts are not available on the 8- and 20-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

Follow the steps below for configuring a timer for CAPTURE mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for CAPTURE mode.

- Set the prescale value.

- Set the Capture edge (rising or falling) for the Timer Input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. Clearing these registers allows the software to determine if interrupts were generated by either a capture event or a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

In CAPTURE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

### **CAPTURE RESTART Mode**

In CAPTURE RESTART mode, the current timer count value is recorded when the acceptable external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte Registers. The timer input is the system clock. The TPOL bit in the Timer Control register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 register is set to indicate the timer interrupt is because of an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to

110 = 64 cycles delay 111 = 128 cycles delay

INPCAP—Input Capture Event

This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.

0 = Previous timer interrupt is not a result of Timer Input Capture Event

1 = Previous timer interrupt is a result of Timer Input Capture Event

### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode (Table 49).

Table 49. Timer 0–1 Control Register 1 (TxCTL1)

| BITS  | 7   | 6    | 5    | 4     | 3    | 2     | 1   | 0   |

|-------|-----|------|------|-------|------|-------|-----|-----|

| FIELD | TEN | TPOL | PRES |       |      | TMODE |     |     |

| RESET | 0   | 0    | 0    | 0     | 0    | 0     | 0   | 0   |

| R/W   | R/W | R/W  | R/W  | R/W   | R/W  | R/W   | R/W | R/W |

| ADDR  |     |      |      | F07H, | F0FH |       |     |     |

TEN-Timer Enable

0 = Timer is disabled.

1 = Timer enabled to count.

TPOL—Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer.

#### **ONE-SHOT mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **CONTINUOUS mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

### COUNTER mode

If the timer is enabled the Timer Output signal is complemented after timer reload.

0 = Count occurs on the rising edge of the Timer Input signal.

1 = Count occurs on the falling edge of the Timer Input signal.

Watchdog Timer Reload Registers results in a one-second timeout at room temperature and 3.3 V supply voltage.

Timeouts other than one second may be obtained by scaling the calibration values up or down as required.

**Note:** *The Watchdog Timer accuracy still degrades as temperature and supply voltage vary. See* Table 133 on page 230 *for* details.

## Watchdog Timer Control Register Definitions

## Watchdog Timer Control Register

The Watchdog Timer Control (WDTCTL) register is a write-only control register. Writing the 55H, AAH unlock sequence to the WDTCTL register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers.

This register address is shared with the read-only Reset Status register.

| BITS           | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|----------------|---------|---|---|---|---|---|---|---|--|

| FIELD          | WDTUNLK |   |   |   |   |   |   |   |  |

| RESET          | Х       | Х | Х | Х | Х | Х | Х | Х |  |

| R/W            | W       | W | W | W | W | W | W | W |  |

| ADDR           | FF0H    |   |   |   |   |   |   |   |  |

| X = Undefined. |         |   |   |   |   |   |   |   |  |

## Table 57. Watchdog Timer Control Register (WDTCTL)

WDTUNLK—Watchdog Timer Unlock

The software must write the correct unlocking sequence to this register before it is allowed to modify the contents of the Watchdog Timer reload registers.

## Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers (Table 58 through Table 60) form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. The 24-bit reload value is {WDTU[7:0], WDTH[7:0]}. Writing to these registers sets the appropriate Reload Value. Reading from these registers returns the current Watchdog Timer count value.

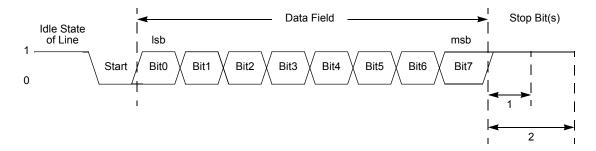

Figure 11. UART Asynchronous Data Format without Parity

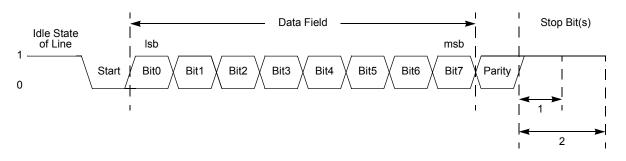

Figure 12. UART Asynchronous Data Format with Parity

## Transmitting Data using the Polled Method

Follow the steps below to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Write to the UART Control 1 register, if MULTIPROCESSOR mode is appropriate, to enable MULTIPROCESSOR (9-bit) mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR mode.

- 5. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR mode is not enabled, and select either even or odd parity (PSEL).

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin.

zilog | 1

The UART is now configured for interrupt-driven data transmission. Because the UART Transmit Data register is empty, an interrupt is generated immediately. When the UART Transmit interrupt is detected, the associated interrupt service routine (ISR) performs the following:

- 1. Write the UART Control 1 register to select the multiprocessor bit for the byte to be transmitted:

- 2. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 3. Write the data byte to the UART Transmit Data register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 4. Clear the UART Transmit interrupt bit in the applicable Interrupt Request register.

- 5. Execute the IRET instruction to return from the interrupt-service routine and wait for the Transmit Data register to again become empty.

### **Receiving Data using the Polled Method**

Follow the steps below to configure the UART for polled data reception:

- 1. Write to the UART Baud Rate High and Low Byte registers to set an acceptable baud rate for the incoming data stream.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Write to the UART Control 1 register to enable MULTIPROCESSOR mode functions, if appropriate.

- 4. Write to the UART Control 0 register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if Multiprocessor mode is not enabled, and select either even or odd parity.

- 5. Check the RDA bit in the UART Status 0 register to determine if the Receive Data register contains a valid data byte (indicated by a 1). If RDA is set to 1 to indicate available data, continue to Step 5. If the Receive Data register is empty (indicated by a 0), continue to monitor the RDA bit awaiting reception of the valid data.

- Read data from the UART Receive Data register. If operating in MULTIPROCESSOR (9-bit) mode, further actions may be required depending on the MULTIPROCESSOR mode bits MPMD[1:0].

- 7. Return to Step 4 to receive additional data.

**z**ilog<sup>®</sup>

## Flash Status Register

The Flash Status (FSTAT) register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status register shares its Register File address with the Write-only Flash Control register.

Table 79. Flash Status Register (FSTAT)

| BITS  | 7    | 6     | 5     | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------|-------|-------|---|---|---|---|---|--|--|

| FIELD | Rese | erved | FSTAT |   |   |   |   |   |  |  |

| RESET | 0    | 0     | 0     | 0 | 0 | 0 | 0 | 0 |  |  |

| R/W   | R    | R     | R     | R | R | R | R | R |  |  |

| ADDR  | FF8H |       |       |   |   |   |   |   |  |  |

Reserved—Must be 0.

FSTAT—Flash Controller Status

000000 = Flash Controller locked

000001 = First unlock command received (73H written)

000010 = Second unlock command received (8CH written)

000011 = Flash Controller unlocked

000100 = Sector protect register selected

001xxx = Program operation in progress

010xxx = Page erase operation in progress

100xxx = Mass erase operation in progress

## Flash Page Select Register

The Flash Page Select (FPS) register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7 bits given by FPS[6:0] are chosen for program/erase operation.

zilog

183

```

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

• **Read Data Memory (0DH)**—The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode, this command returns FFH for the data.

```

DBG \leftarrow 0DH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

• **Read Program Memory CRC (0EH)**—The Read Program Memory CRC command computes and returns the Cyclic Redundancy Check (CRC) of Program Memory using the 16-bit CRC-CCITT polynomial. If the device is not in DEBUG mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program Memory, calculates the CRC value, and returns the result. The delay is a function of the Program Memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program Memory.

DBG  $\leftarrow$  0EH DBG  $\rightarrow$  CRC[15:8] DBG  $\rightarrow$  CRC[7:0]

• Step Instruction (10H)—The Step Instruction command steps one assembly instruction at the current Program Counter (PC) location. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

DBG  $\leftarrow$  10H

• Stuff Instruction (11H)—The Stuff Instruction command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0-4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

• **Execute Instruction (12H)**—The Execute Instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over Breakpoints. The number of bytes to send for the instruction depends on the opcode.

# **Oscillator Control**

The Z8 Encore!  $XP^{\mathbb{R}}$  F082A Series devices uses five possible clocking schemes, each user-selectable:

- Internal precision trimmed RC oscillator (IPO).

- On-chip oscillator using off-chip crystal or resonator.

- On-chip oscillator using external RC network.

- External clock drive.

- On-chip low power Watchdog Timer oscillator.

- Clock failure detection circuitry.

In addition, Z8 Encore! XP F082A Series devices contain clock failure detection and recovery circuitry, allowing continued operation despite a failure of the system clock oscillator.

## Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures.

## **System Clock Selection**

The oscillator control block selects from the available clocks. Table 108 details each clock source and its usage.

# **Opcode Maps**

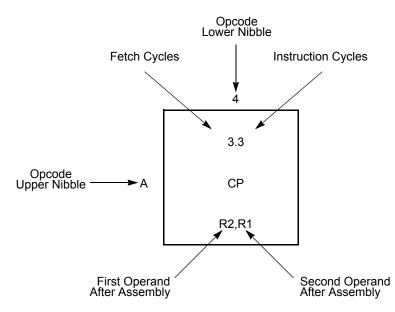

A description of the opcode map data and the abbreviations are provided in Figure 30. Figure 31 and Figure 32 displays the eZ8 CPU instructions. Table 125 lists Opcode Map abbreviations.

Figure 30. Opcode Map Cell Description

223

|                   |                               |         | 40 °C to +<br>therwise | 105 °C<br>specified) |       |                                                                                 |

|-------------------|-------------------------------|---------|------------------------|----------------------|-------|---------------------------------------------------------------------------------|

| Symbol            | Parameter                     | Minimum | Typical                | Maximum              | Units | Conditions                                                                      |

| V <sub>OL2</sub>  | Low Level Output<br>Voltage   | -       | -                      | 0.6                  | V     | I <sub>OL</sub> = 20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.  |

| V <sub>OH2</sub>  | High Level Output<br>Voltage  | 2.4     | _                      | -                    | V     | I <sub>OH</sub> = -20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled. |

| I <sub>IH</sub>   | Input Leakage<br>Current      | -       | <u>+</u> 0.002         | <u>+</u> 5           | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V;$                                          |

| IIL               | Input Leakage<br>Current      | -       | <u>+</u> 0.007         | <u>+</u> 5           | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3 V;$                                          |

| I <sub>TL</sub>   | Tristate Leakage<br>Current   | -       | _                      | <u>+</u> 5           | μA    |                                                                                 |

| I <sub>LED</sub>  | Controlled Current<br>Drive   | 1.8     | 3                      | 4.5                  | mA    | {AFS2,AFS1} = {0,0}                                                             |

|                   |                               | 2.8     | 7                      | 10.5                 | mA    | {AFS2,AFS1} = {0,1}                                                             |

|                   |                               | 7.8     | 13                     | 19.5                 | mA    | {AFS2,AFS1} = {1,0}                                                             |

|                   |                               | 12      | 20                     | 30                   | mA    | {AFS2,AFS1} = {1,1}                                                             |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance  | -       | 8.0 <sup>2</sup>       | -                    | pF    |                                                                                 |

| C <sub>XIN</sub>  | XIN Pad<br>Capacitance        | -       | 8.0 <sup>2</sup>       | _                    | pF    |                                                                                 |

| C <sub>XOUT</sub> | XOUT Pad<br>Capacitance       | -       | 9.5 <sup>2</sup>       | -                    | pF    |                                                                                 |

| I <sub>PU</sub>   | Weak Pull-up<br>Current       | 30      | 100                    | 350                  | μA    | V <sub>DD</sub> = 3.0 V–3.6 V                                                   |

| V <sub>RAM</sub>  | RAM Data<br>Retention Voltage | TBD     |                        |                      | V     | Voltage at which RAM retains static values; no reading or writing is allowed.   |

|                   |                               |         | -                      |                      | -     |                                                                                 |

## Table 127. DC Characteristics (Continued)

#### Notes

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

zilog

|                   |                   | V <sub>DD</sub> | = 2.7 V to   |            |       |                                                                           |

|-------------------|-------------------|-----------------|--------------|------------|-------|---------------------------------------------------------------------------|

| Symbol            | Parameter         | Minimum         | Typical      | Maximum    | Units | Conditions                                                                |

| T <sub>AERR</sub> | Temperature Error |                 | <u>+</u> 0.5 | <u>+</u> 2 | °C    | Over the range +20 °C<br>to +30 °C (as<br>measured by ADC) <sup>1</sup>   |

|                   |                   |                 | <u>+</u> 1   | <u>+</u> 5 | °C    | Over the range +0 °C<br>to +70 °C (as<br>measured by ADC)                 |

|                   |                   |                 | <u>+</u> 2   | <u>+</u> 7 | °C    | Over the range +0 °C<br>to +105 °C (as<br>measured by ADC)                |

|                   |                   |                 | <u>+</u> 7   |            | °C    | Over the range -40 °C<br>to +105 °C (as<br>measured by ADC)               |

| T <sub>AERR</sub> | Temperature Error |                 | TBD          |            | °C    | Over the range -40 °C<br>to +105 °C (as<br>measured by<br>comparator)     |

| t <sub>WAKE</sub> | Wakeup Time       |                 | 80           | 100        | μs    | Time required for<br>Temperature Sensor<br>to stabilize after<br>enabling |

### **Table 138. Temperature Sensor Electrical Characteristics**

<sup>1</sup>Devices are factory calibrated at for maximal accuracy between +20 °C and +30 °C, so the sensor is maximally accurate in that range. User re-calibration for a different temperature range is possible and increases accuracy near the new calibration point.

## General Purpose I/O Port Input Data Sample Timing

Figure 34 displays timing of the GPIO Port input sampling. The input value on a GPIO Port pin is sampled on the rising edge of the system clock. The Port value is available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

INCH

MAX

0.068

0.010

0.061

0.019

0.010

0.196

0.157

0.242

0.016

0.032

.050 BSC

MIN

0.061

0.004

0.055

0.014

0.007

0.189

0.150

0.230

0.010

0.018

MAX

1.73

0.25

1.55

0.48

0.25

4.98

3.99

6.15

0.40

0.81

zilog 242

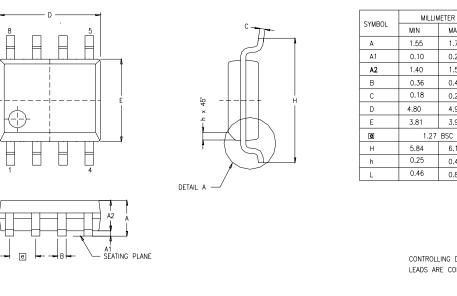

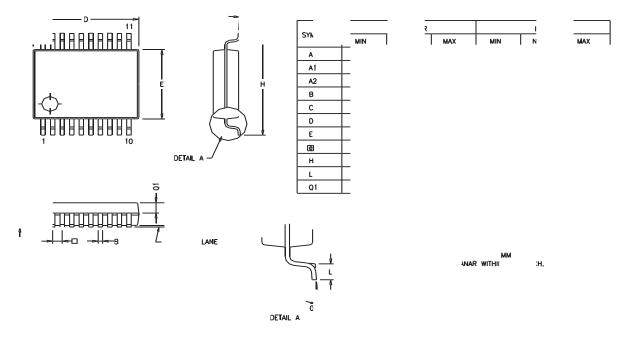

# Figure 40 displays the 8-pin Small Outline Integrated Circuit package (SOIC) available for the Z8 Encore! XP<sup>®</sup> F082A Series devices.

CONTROLLING DIMENSIONS : MM LEADS ARE COPLANAR WITHIN .004 INCH.

Figure 40. 8-Pin Small Outline Integrated Circuit Package (SOIC)

Figure 44 displays the 20-pin Small Shrink Outline Package (SSOP) available for the Z8 Encore! XP F082A Series devices.

Figure 44. 20-Pin Small Shrink Outline Package (SSOP)

262

compare 85 compare - extended addressing 203 COMPARE mode 85 compare with carry 203 compare with carry - extended addressing 203 complement 205 complement carry flag 204 condition code 201 continuous conversion (ADC) 124 CONTINUOUS mode 84 control register definition, UART 108 Control Registers 15, 19 **COUNTER modes 84** CP 203 **CPC 203 CPCX 203** CPU and peripheral overview 5 CPU control instructions 204 **CPX 203** Customer Feedback Form 271

# D

DA 201, 203 data memory 17 DC characteristics 222 debugger, on-chip 173 **DEC 203** decimal adjust 203 decrement 203 decrement and jump non-zero 206 decrement word 203 **DECW 203** destination operand 202 device, port availability 37 DI 204 direct address 201 disable interrupts 204 **DJNZ 206** dst 202

## Ε

EI 204

electrical characteristics 221 ADC 231 flash memory and timing 230 GPIO input data sample timing 234 Watchdog Timer 230, 233 enable interrupt 204 ER 201 extended addressing register 201 external pin reset 27 eZ8 CPU features 5 eZ8 CPU instruction classes 202 eZ8 CPU instruction notation 200 eZ8 CPU instruction set 199 eZ8 CPU instruction summary 207

# F

FCTL register 149, 155, 156 features, Z8 Encore! 1 first opcode map 218 FLAGS 202 flags register 202 flash controller 7 option bit address space 156 option bit configuration - reset 153 program memory address 0000H 156 program memory address 0001H 158 flash memory 141 arrangement 142 byte programming 147 code protection 145 configurations 141 control register definitions 149, 155 controller bypass 148 electrical characteristics and timing 230 flash control register 149, 155, 156 flash option bits 146 flash status register 150 flow chart 144 frequency high and low byte registers 152 mass erase 147 operation 143 operation timing 145