Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 20000                      |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Obsolete                                                     |

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 6                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 128 x 8                                                      |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 4x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f042asb020ec    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

zilog

and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the  $\overline{\text{RESET}}$  input pin is asserted Low, the Z8 Encore! XP<sup>®</sup> F082A Series devices remain in the Reset state. If the  $\overline{\text{RESET}}$  pin is held Low beyond the System Reset time-out, the device exits the Reset state on the system clock rising edge following  $\overline{\text{RESET}}$  pin deassertion. Following a System Reset initiated by the external  $\overline{\text{RESET}}$  pin, the EXT status bit in the Reset Status (RSTSTAT) register is set to 1.

### **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see Port A–D Control Registers on page 46), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows a Z8 Encore! XP F082A Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the RESET pin Low. The RESET pin is held Low by the internal circuitry until the appropriate delay listed in Table 8 has elapsed.

### **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control register. The On-Chip Debugger block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset the POR bit in the Reset Status (RSTSTAT) register is set.

### Stop Mode Recovery

STOP mode is entered by execution of a STOP instruction by the eZ8 CPU. See Low-Power Modes on page 33 for detailed STOP mode information. During Stop Mode Recovery (SMR), the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay (see Table 131 on page 229)  $T_{SMR}$ , also includes the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control register (WDTCTL) and the Oscillator Control register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset

# **Low-Power Modes**

The Z8 Encore! XP F082A Series products contain power-saving features. The highest level of power reduction is provided by the STOP mode, in which nearly all device functions are powered down. The next lower level of power reduction is provided by the HALT mode, in which the CPU is powered down.

Further power savings can be implemented by disabling individual peripheral blocks while in Active mode (defined as being in neither STOP nor HALT mode).

## **STOP Mode**

Executing the eZ8 CPU's STOP instruction places the device into STOP mode, powering down all peripherals except the Voltage Brownout detector, the Low-power Operational Amplifier and the Watchdog Timer. These three blocks may also be disabled for additional power savings. Specifically, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; XIN and XOUT (if previously enabled) are disabled, and PA0/PA1 revert to the states programmed by the GPIO registers.

- System clock is stopped.

- eZ8 CPU is stopped.

- Program counter (PC) stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control register.

- If enabled, the Watchdog Timer logic continues to operate.

- If enabled for operation in STOP mode by the associated Flash Option Bit, the Voltage Brownout protection circuit continues to operate.

- Low-power operational amplifier continues to operate if enabled by the Power Control register to do so.

- All other on-chip peripherals are idle.

To minimize current in STOP mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP mode using Stop Mode Recovery. For more information on Stop Mode Recovery, see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23.

zilog

50

during STOP mode do not initiate Stop Mode Recovery.

1 = The Port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP mode initiates Stop Mode Recovery.

### Port A–D Pull-up Enable Sub-Registers

The Port A–D Pull-up Enable sub-register (Table 24) is accessed through the Port A–D Control register by writing 06H to the Port A–D Address register. Setting the bits in the Port A–D Pull-up Enable sub-registers enables a weak internal resistive pull-up on the specified Port pins.

### Table 24. Port A–D Pull-Up Enable Sub-Registers (PxPUE)

| BITS  | 7        | 6                                                                                     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|----------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|

| FIELD | PPUE7    | PPUE6                                                                                 | PPUE5 | PPUE4 | PPUE3 | PPUE2 | PPUE1 | PPUE0 |

| RESET |          | 00H (Ports A-C); 01H (Port D); 04H (Port A of 8-pin device)                           |       |       |       |       |       |       |

| R/W   | R/W      | R/W         R/W         R/W         R/W         R/W         R/W                       |       |       |       |       |       |       |

| ADDR  | lf 06H i | If 06H in Port A–D Address Register, accessible through the Port A–D Control Register |       |       |       |       |       |       |

PPUE[7:0]—Port Pull-up Enabled

0 = The weak pull-up on the Port pin is disabled.

1 = The weak pull-up on the Port pin is enabled.

### Port A–D Alternate Function Set 1 Sub-Registers

The Port A–D Alternate Function Set1 sub-register (Table 25) is accessed through the Port A–D Control register by writing 07H to the Port A–D Address register. The Alternate Function Set 1 sub-registers selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register are defined in GPIO Alternate Functions on page 38.

**Note:** Alternate function selection on port pins must also be enabled as described in Port A–D Alternate Function Sub-Registers on page 47.

### Table 25. Port A–D Alternate Function Set 1 Sub-Registers (PxAFS1)

| BITS  | 7        | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|----------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|

| FIELD | PAFS17   | PAFS16                                                                                | PAFS15 | PAFS14 | PAFS13 | PAFS12 | PAFS11 | PAFS10 |

| RESET | 0        | 0                                                                                     | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W   | R/W      | R/W                                                                                   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| ADDR  | lf 07H i | If 07H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |        |

zilog

**Caution:** To avoid re-triggerings of the Watchdog Timer interrupt after exiting the associated interrupt service routine, it is recommended that the service routine continues to read from the RSTSTAT register until the WDT bit is cleared as given in the following coding sample:

CLEARWDT: LDX r0, RSTSTAT ; read reset status register to clear wdt bit BTJNZ 5, r0, CLEARWDT ; loop until bit is cleared

# **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap, and the Watchdog Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

## **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) register (Table 33) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 0 register to determine if any interrupt requests are pending.

| BITS  | 7        | 6                           | 5   | 4            | 3     | 2        | 1        | 0    |

|-------|----------|-----------------------------|-----|--------------|-------|----------|----------|------|

| FIELD | Reserved | T1I                         | TOI | <b>U0RXI</b> | U0TXI | Reserved | Reserved | ADCI |

| RESET | 0        | 0                           | 0   | 0            | 0     | 0        | 0        | 0    |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W |     |              |       |          |          |      |

| ADDR  |          | FC0H                        |     |              |       |          |          |      |

Table 33. Interrupt Request 0 Register (IRQ0)

Reserved—Must be 0.

T1I—Timer 1 Interrupt Request

- 0 = No interrupt request is pending for Timer 1.

- 1 = An interrupt request from Timer 1 is awaiting service.

T0I—Timer 0 Interrupt Request

- 0 = No interrupt request is pending for Timer 0.

- 1 = An interrupt request from Timer 0 is awaiting service.

### Table 39. IRQ1 Enable and Priority Encoding

| IRQ1ENH[x] | IRQ1ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Medium      |

| 1          | 1          | Level 3  | High        |

|            |            |          |             |

where x indicates the register bits from 0–7.

### Table 40. IRQ1 Enable High Bit Register (IRQ1ENH)

| BITS  | 7       | 6                           | 5      | 4      | 3             | 2      | 1      | 0      |

|-------|---------|-----------------------------|--------|--------|---------------|--------|--------|--------|

| FIELD | PA7VENH | PA6CENH                     | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |

| RESET | 0       | 0                           | 0      | 0      | 0             | 0      | 0      | 0      |

| R/W   | R/W     | R/W R/W R/W R/W R/W R/W R/W |        |        |               |        |        |        |

| ADDR  |         | FC4H                        |        |        |               |        |        |        |

PA7VENH—Port A Bit[7] or LVD Interrupt Request Enable High Bit PA6CENH—Port A Bit[7] or Comparator Interrupt Request Enable High Bit PAxENH—Port A Bit[x] Interrupt Request Enable High Bit

See Shared Interrupt Select (IRQSS) register for selection of either the LVD or the comparator as the interrupt source.

### Table 41. IRQ1 Enable Low Bit Register (IRQ1ENL)

| BITS  | 7       | 6       | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---------|---------|--------|--------|--------|--------|--------|--------|

| FIELD | PA7VENL | PA6CENL | PA5ENL | PA4ENL | PA3ENL | PA2ENL | PA1ENL | PA0ENL |

| RESET | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W   | R/W     | R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| ADDR  |         | FC5H    |        |        |        |        |        |        |

PA7VENL—Port A Bit[7] or LVD Interrupt Request Enable Low Bit PA6CENL—Port A Bit[6] or Comparator Interrupt Request Enable Low Bit PAxENL—Port A Bit[x] Interrupt Request Enable Low Bit

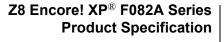

Figure 9. Timer Block Diagram

## Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

## **Timer Operating Modes**

The timers can be configured to operate in the following modes:

### **ONE-SHOT Mode**

In ONE-SHOT mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. The timer is automatically disabled and stops counting.

70

Z8 Encore! XP<sup>®</sup> F082A Series

**Product Specification**

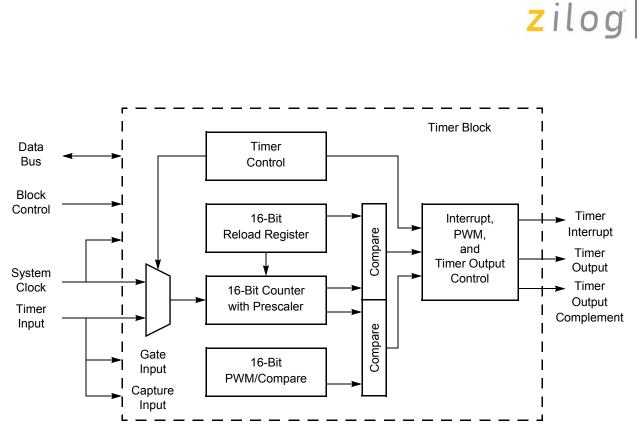

## Operation

### **Data Format**

The UART always transmits and receives data in an 8-bit data format, least-significant bit first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low START bit and ends with either 1 or 2 active High STOP bits. Figure 11 and Figure 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

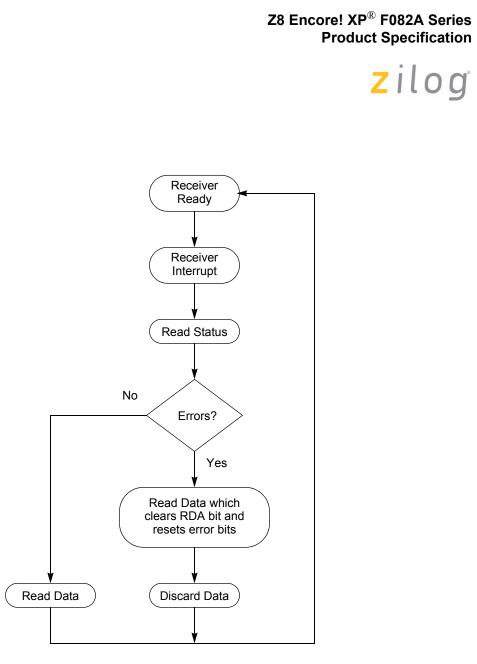

Figure 15. UART Receiver Interrupt Service Routine Flow

### **Baud Rate Generator Interrupts**

If the baud rate generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud Rate Generator to function as an additional counter if the UART functionality is not employed.

## **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value

107

zilog

### 126

### **Factory Calibration**

Devices that have been factory calibrated contain 30 bytes of calibration data in the Flash option bit space. This data consists of 3 bytes for each input mode, one for offset and two for gain correction. For a list of input modes for which calibration data exists, see Zilog Calibration Data on page 161.

### **User Calibration**

If you have precision references available, its own external calibration can be performed using any input modes. This calibration data takes into account buffer offset and non-linearity, so it is recommended that this calibration be performed separately for each of the ADC input modes planned for use.

### **Manual Offset Calibration**

When uncalibrated, the ADC has significant offset (see Table 135 on page 231). Subsequently, manual offset calibration capability is built into the block. When the ADC Control Register 0 sets the input mode (ANAIN[2:0]) to MANUAL OFFSET CALIBRATION mode, the differential inputs to the ADC are shorted together by an internal switch. Reading the ADC value at this point produces 0 in an ideal system. The value actually read is the ADC offset. This value can be stored in non-volatile memory (see Non-Volatile Data Storage on page 169) and accessed by user code to compensate for the input offset error. There is no provision for manual gain calibration.

### Software Compensation Procedure Using Factory Calibration Data

The value read from the ADC high and low byte registers is uncompensated. The user mode software must apply gain and offset correction to this uncompensated value for maximum accuracy. The following equation yields the compensated value:

$ADC_{comp} = (ADC_{uncomp} - OFFCAL) + ((ADC_{uncomp} - OFFCAL) \times GAINCAL)/2^{16}$

where GAINCAL is the gain calibration value, OFFCAL is the offset calibration value and  $ADC_{uncomp}$  is the uncompensated value read from the ADC. All values are in two's complement format.

### Note:

The offset compensation is performed first, followed by the gain compensation. One bit of resolution is lost because of rounding on both the offset and gain computations. As a result the ADC registers read back 13 bits: 1 sign bit, two calibration bits lost to rounding and 10 data bits.

Also note that in the second term, the multiplication must be performed before the division by  $2^{16}$ . Otherwise, the second term incorrectly evaluates to zero.

# **Flash Option Bits**

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore! XP<sup>®</sup> F082A Series operation. The feature configuration data is stored in the Flash program memory and loaded into holding registers during Reset. The features available for control through the Flash Option Bits include:

- Watchdog Timer time-out response selection-interrupt or system reset

- Watchdog Timer always on (enabled at Reset)

- The ability to prevent unwanted read access to user code in Program Memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Program Memory

- Voltage Brownout configuration-always enabled or disabled during STOP mode to reduce STOP mode power consumption

- Oscillator mode selection-for high, medium, and low power crystal oscillators, or external RC oscillator

- Factory trimming information for the internal precision oscillator and low voltage detection

- Factory calibration values for ADC, temperature sensor, and Watchdog Timer compensation

- Factory serialization and randomized lot identifier (optional)

## Operation

### **Option Bit Configuration By Reset**

Each time the Flash Option Bits are programmed or erased, the device must be Reset for the change to take effect. During any reset operation (System Reset, Power-On Reset, or Stop Mode Recovery), the Flash Option Bits are automatically read from the Flash Program Memory and written to Option Configuration registers. The Option Configuration registers control operation of the devices within the Z8 Encore! XP F082A Series. Option Bit control is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

zilog 1

# Operation

## **OCD** Interface

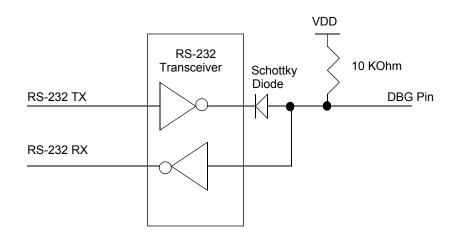

The on-chip debugger uses the DBG pin for communication with an external host. This one-pin interface is a bi-directional, open-drain interface that transmits and receives data. Data transmission is half-duplex, in that transmit and receive cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin creates an interface from the Z8 Encore! XP<sup>®</sup> F082A Series products to the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figure 24 and Figure 25. The recommended method is the buffered implementation displayed in Figure 25. The DBG pin has a internal pull-up resistor which is sufficient for some applications (for more details on the pull-up current, see Electrical Characteristics on page 221). For OCD operation at higher data rates or in noisy systems, an external pull-up resistor is recommended.

## Caution:

For operation of the on-chip debugger, all power pins ( $V_{DD}$  and  $AV_{DD}$ ) must be supplied with power, and all ground pins ( $V_{SS}$  and  $AV_{SS}$ ) must be properly grounded. The DBG pin is open-drain and may require an external pull-up resistor to ensure proper operation.

### Figure 24. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (1)

zilog | 1

### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a Breakpoint, write 00H to the required break address, overwriting the current instruction. To remove a Breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

## **Runtime Counter**

The On-Chip Debugger contains a 16-bit Runtime Counter. It counts system clock cycles between Breakpoints. The counter starts counting when the On-Chip Debugger leaves DEBUG mode and stops counting when it enters DEBUG mode again or when it reaches the maximum count of FFFFH.

# **On-Chip Debugger Commands**

The host communicates to the on-chip debugger by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash Read Protect Option bit (FRP). The Flash Read Protect Option bit prevents the code in memory from being read out of the Z8 Encore! XP F082A Series products. When this option is enabled, several of the OCD commands are disabled. Table 106 on page 184 is a summary of the On-chip debugger commands. Each OCD command is described in further detail in the bulleted list following this table. Table 106 on page 184 also indicates those commands that operate when the device is not in DEBUG mode (normal operation) and those commands that are disabled by programming the Flash Read Protect Option bit.

| Debug Command              | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>mode? | Disabled by<br>Flash Read Protect Option Bit |

|----------------------------|-----------------|---------------------------------------|----------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                   | -                                            |

| Reserved                   | 01H             | -                                     | -                                            |

| Read OCD Status Register   | 02H             | Yes                                   | -                                            |

| Read Runtime Counter       | 03H             | -                                     | -                                            |

| Write OCD Control Register | 04H             | Yes                                   | Cannot clear DBGMODE bit                     |

| Read OCD Control Register  | 05H             | Yes                                   | -                                            |

| Write Program Counter      | 06H             | -                                     | Disabled                                     |

| Read Program Counter       | 07H             | _                                     | Disabled                                     |

# zilog

180

| Debug Command           | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>mode? | Disabled by<br>Flash Read Protect Option Bit                                                                                                                              |

|-------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write Register          | 08H             | -                                     | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only<br>the Mass Erase command is allowed to<br>be written to the Flash Control register. |

| Read Register           | 09H             | _                                     | Disabled                                                                                                                                                                  |

| Write Program Memory    | 0AH             | _                                     | Disabled                                                                                                                                                                  |

| Read Program Memory     | 0BH             | _                                     | Disabled                                                                                                                                                                  |

| Write Data Memory       | 0CH             | _                                     | Yes                                                                                                                                                                       |

| Read Data Memory        | 0DH             | _                                     | -                                                                                                                                                                         |

| Read Program Memory CRC | 0EH             | _                                     | -                                                                                                                                                                         |

| Reserved                | 0FH             | _                                     | -                                                                                                                                                                         |

| Step Instruction        | 10H             | _                                     | Disabled                                                                                                                                                                  |

| Stuff Instruction       | 11H             | _                                     | Disabled                                                                                                                                                                  |

| Execute Instruction     | 12H             | _                                     | Disabled                                                                                                                                                                  |

| Reserved                | 13H–FFH         | _                                     | _                                                                                                                                                                         |

In the following bulleted list of OCD Commands, data and commands sent from the host to the On-Chip Debugger are identified by 'DBG  $\leftarrow$  Command/Data'. Data sent from the On-Chip Debugger back to the host is identified by 'DBG  $\rightarrow$  Data'

• **Read OCD Revision (00H)**—The Read OCD Revision command determines the version of the On-Chip Debugger. If OCD commands are added, removed, or changed, this revision number changes.

```

DBG \leftarrow 00H

DBG \rightarrow OCDRev[15:8] (Major revision number)

DBG \rightarrow OCDRev[7:0] (Minor revision number)

```

• **Read OCD Status Register (02H)**—The Read OCD Status Register command reads the OCDSTAT register.

```

DBG \leftarrow 02H

DBG \rightarrow OCDSTAT[7:0]

```

• **Read Runtime Counter (03H)**—The Runtime Counter counts system clock cycles in between Breakpoints. The 16-bit Runtime Counter counts up from 0000H and stops at the maximum count of FFFFH. The Runtime Counter is overwritten during the

186

202

### Table 115. Additional Symbols

| Definition                   |

|------------------------------|

| Destination Operand          |

| Source Operand               |

| Indirect Address Prefix      |

| Stack Pointer                |

| Program Counter              |

| Flags Register               |

| Register Pointer             |

| Immediate Operand Prefix     |

| Binary Number Suffix         |

| Hexadecimal Number<br>Prefix |

| Hexadecimal Number<br>Suffix |

|                              |

Assignment of a value is indicated by an arrow. For example,

$dst \leftarrow dst + src$

indicates the source data is added to the destination data and the result is stored in the destination location.

# eZ8 CPU Instruction Classes

eZ8 CPU instructions can be divided functionally into the following groups:

- Arithmetic

- Bit Manipulation

- Block Transfer

- CPU Control

- Load

- Logical

- Program Control

- Rotate and Shift

204

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| ТСМ      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |

Table 118. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-Increment Addresses       |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

## Table 119. CPU Control Instructions

| Mnemonic | Operands | Instruction           |  |  |  |  |  |  |

|----------|----------|-----------------------|--|--|--|--|--|--|

| ATM      | _        | Atomic Execution      |  |  |  |  |  |  |

| CCF      | _        | Complement Carry Flag |  |  |  |  |  |  |

| DI       | _        | Disable Interrupts    |  |  |  |  |  |  |

| EI       | _        | Enable Interrupts     |  |  |  |  |  |  |

| HALT     | _        | Halt Mode             |  |  |  |  |  |  |

| NOP      | _        | No Operation          |  |  |  |  |  |  |

| RCF      | _        | Reset Carry Flag      |  |  |  |  |  |  |

**z**ilog<sup>°</sup>

## 229

# **On-Chip Peripheral AC and DC Electrical Characteristics**

### Table 131. Power-On Reset and Voltage Brownout Electrical Characteristics and Timing

|                   |                                                                                                                | T <sub>A</sub> = - | 40 °C to +           | 105 °C  |       | Conditions                                                                                            |  |

|-------------------|----------------------------------------------------------------------------------------------------------------|--------------------|----------------------|---------|-------|-------------------------------------------------------------------------------------------------------|--|

| Symbol            | Parameter                                                                                                      | Minimum            | Typical <sup>1</sup> | Maximum | Units |                                                                                                       |  |

| V <sub>POR</sub>  | Power-On Reset<br>Voltage Threshold                                                                            | 2.20               | 2.45                 | 2.70    | V     | V <sub>DD</sub> = V <sub>POR</sub>                                                                    |  |

| V <sub>VBO</sub>  | Voltage Brownout Reset<br>Voltage Threshold                                                                    | 2.15               | 2.40                 | 2.65    | V     | $V_{DD} = V_{VBO}$                                                                                    |  |

|                   | $V_{POR}$ to $V_{VBO}$ hysteresis                                                                              |                    | 50                   | 75      | mV    |                                                                                                       |  |

|                   | Starting V <sub>DD</sub> voltage to<br>ensure valid Power-On<br>Reset.                                         | -                  | $V_{SS}$             | -       | V     |                                                                                                       |  |

| T <sub>ANA</sub>  | Power-On Reset Analog<br>Delay                                                                                 | -                  | 70                   | -       | μs    | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub> Digital<br>Reset delay follows T <sub>ANA</sub> |  |

| T <sub>POR</sub>  | Power-On Reset Digital<br>Delay                                                                                |                    | 16                   |         | μs    | 66 Internal Precision<br>Oscillator cycles + IPO<br>startup time (T <sub>IPOST</sub> )                |  |

| T <sub>POR</sub>  | Power-On Reset Digital<br>Delay                                                                                |                    | 1                    |         | ms    | 5000 Internal Precision<br>Oscillator cycles                                                          |  |

| T <sub>SMR</sub>  | Stop Mode Recovery<br>with crystal oscillator<br>disabled                                                      |                    | 16                   |         | μs    | 66 Internal Precision<br>Oscillator cycles                                                            |  |

| T <sub>SMR</sub>  | Stop Mode Recovery<br>with crystal oscillator<br>enabled                                                       |                    | 1                    |         | ms    | 5000 Internal Precision<br>Oscillator cycles                                                          |  |

| T <sub>VBO</sub>  | Voltage Brownout Pulse<br>Rejection Period                                                                     | _                  | 10                   | -       | μs    | Period of time in which V <sub>DD</sub><br>< V <sub>VBO</sub> without generating<br>a Reset.          |  |

| T <sub>RAMP</sub> | Time for V <sub>DD</sub> to<br>transition from V <sub>SS</sub> to<br>V <sub>POR</sub> to ensure valid<br>Reset | 0.10               | -                    | 100     | ms    |                                                                                                       |  |

| T <sub>SMP</sub>  | Stop Mode Recovery pin pulse rejection period                                                                  |                    | 20                   |         | ns    | For any SMR pin or for the Reset pin when it is asserted in STOP mode.                                |  |

only and are not tested in production.

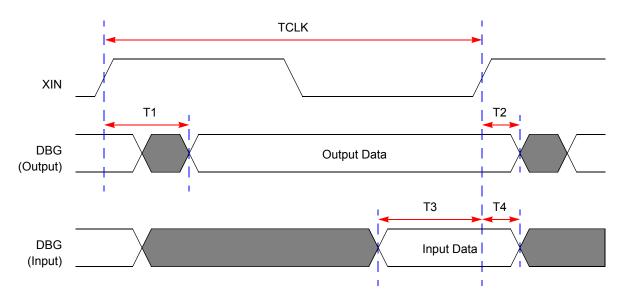

## **On-Chip Debugger Timing**

Figure 36 and Table 141 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

Figure 36. On-Chip Debugger Timing

|                |                                  | Dela    | / (ns)  |  |

|----------------|----------------------------------|---------|---------|--|

| Parameter      | Abbreviation                     | Minimum | Maximum |  |

| DBG            |                                  |         |         |  |

| T <sub>1</sub> | XIN Rise to DBG Valid Delay      | -       | 15      |  |

| T <sub>2</sub> | XIN Rise to DBG Output Hold Time | 2       | _       |  |

| T <sub>3</sub> | DBG to XIN Rise Input Setup Time | 5       | _       |  |

| T <sub>4</sub> | DBG to XIN Rise Input Hold Time  | 5       | _       |  |

### Table 141. On-Chip Debugger Timing

**z**ilog<sup>°</sup>

## 251

# **Ordering Information**

Order the Z8 Encore! XP<sup>®</sup> F082A Series from Zilog<sup>®</sup>, using the following part numbers. For more information on ordering, please consult your local Zilog sales office. The Zilog website (<u>www.zilog.com</u>) lists all regional offices and provides additional Z8 Encore! XP product information.

| Part Number                                              | Flash    | RAM     | NVDS | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|----------------------------------------------------------|----------|---------|------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F0824<br>Standard Temperature |          |         |      | asn, 1    | 0-ЫІ       | Ana                 | iog-t               | טום-ס          |            | Jony               | verter              |

| Z8F082APB020SC                                           | 8 KB     | 1 KB    | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082APB020SC                                           | 8 KB     | 1 KB    | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020SC                                           | 8 KB     | 1 KB    | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020SC                                           | 8 KB     | 1 KB    | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020SC                                           | 8 KB     | 1 KB    | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020SC                                           | 8 KB     | 1 KB    | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F082ASJ020SC                                           | 8 KB     | 1 KB    | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020SC                                           | 8 KB     | 1 KB    | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020SC                                           | 8 KB     | 1 KB    | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperature                                     | e: -40 ° | C to 10 | 5 °C |           |            |                     |                     |                |            |                    |                     |

| Z8F082APB020EC                                           | 8 KB     | 1 KB    | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082AQB020EC                                           | 8 KB     | 1 KB    | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020EC                                           | 8 KB     | 1 KB    | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020EC                                           | 8 KB     | 1 KB    | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020EC                                           | 8 KB     | 1 KB    | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020EC                                           | 8 KB     | 1 KB    | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F082ASJ020EC                                           | 8 KB     | 1 KB    | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020EC                                           | 8 KB     | 1 KB    | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020EC                                           | 8 KB     | 1 KB    | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging                 |          |         |      |           |            |                     |                     |                |            |                    |                     |

| 25 |

|----|

| Part Number                              | Flash     | RAM      | SUVN   | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|------------------------------------------|-----------|----------|--------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082          | A Serie   | s with 1 | KB Fla | ish       |            |                     |                     |                |            |                    |                     |

| Standard Temperatur                      | e: 0 °C   | to 70 °C |        |           |            |                     |                     |                |            |                    |                     |

| Z8F011APB020SC                           | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F011AQB020SC                           | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F011ASB020SC                           | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F011ASH020SC                           | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F011AHH020SC                           | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F011APH020SC                           | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F011ASJ020SC                           | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F011AHJ020SC                           | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F011APJ020SC                           | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperatur                      | re: -40 ° | C to 10  | 5 °C   |           |            |                     |                     |                |            |                    |                     |

| Z8F011APB020EC                           | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F011AQB020EC                           | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F011ASB020EC                           | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F011ASH020EC                           | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F011AHH020EC                           | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F011APH020EC                           | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F011ASJ020EC                           | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F011AHJ020EC                           | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F011APJ020EC                           | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging |           |          |        |           |            |                     |                     |                |            |                    |                     |