Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 6                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 128 x 8                                                      |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 4x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                |

| Supplier Device Package    | •                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f042asb020sc    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Zilog <sub>17</sub>

| Program Memory Address (Hex)                | Function                     |

|---------------------------------------------|------------------------------|

| Z8F022A and Z8F021A Products                |                              |

| 0000–0001                                   | Flash Option Bits            |

| 0002–0003                                   | Reset Vector                 |

| 0004–0005                                   | WDT Interrupt Vector         |

| 0006–0007                                   | Illegal Instruction Trap     |

| 0008–0037                                   | Interrupt Vectors*           |

| 0038–0039                                   | Reserved                     |

| 003A-003D                                   | Oscillator Fail Trap Vectors |

| 003E-07FF                                   | Program Memory               |

| Z8F012A and Z8F011A Products                |                              |

| 0000–0001                                   | Flash Option Bits            |

| 0002–0003                                   | Reset Vector                 |

| 0004–0005                                   | WDT Interrupt Vector         |

| 0006–0007                                   | Illegal Instruction Trap     |

| 0008–0037                                   | Interrupt Vectors*           |

| 0038–0039                                   | Reserved                     |

| 003A-003D                                   | Oscillator Fail Trap Vectors |

| 003E-03FF                                   | Program Memory               |

| * See Table 32 on page 56 for a list of the | interrupt vectors.           |

Table 5. Z8 Encore! XP F082A Series Program Memory Maps (Continued)

# **Data Memory**

The Z8 Encore! XP F082A Series does not use the eZ8 CPU's 64 KB Data Memory address space.

# **Flash Information Area**

Table 6 on page 18 describes the Z8 Encore! XP F082A Series Flash Information Area. This 128 B Information Area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash Information Area is mapped into the Program Memory and overlays the 128 bytes at addresses FE00H to FF7FH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Infor-

**z**ilog<sup>°</sup>

| Address (Hex)   | Register Description                 | Mnemonic | Reset (Hex) | Page No |

|-----------------|--------------------------------------|----------|-------------|---------|

| F0B             | Timer 1 Reload Low Byte              | T1RL     | FF          | 88      |

| F0C             | Timer 1 PWM High Byte                | T1PWMH   | 00          | 88      |

| F0D             | Timer 1 PWM Low Byte                 | T1PWML   | 00          | 89      |

| F0E             | Timer 1 Control 0                    | T1CTL0   | 00          | 83      |

| F0F             | Timer 1 Control 1                    | T1CTL1   | 00          | 84      |

| F10–F6F         | Reserved                             |          | XX          |         |

| UART            |                                      |          |             |         |

| F40             | UART Transmit/Receive Data Registers | TXD, RXD | XX          | 113     |

| F41             | UART Status 0 Register               | U0STAT0  | 00          | 111     |

| F42             | UART Control 0 Register              | U0CTL0   | 00          | 108     |

| F43             | UART Control 1 Register              | U0CTL1   | 00          | 108     |

| F44             | UART Status 1 Register               | U0STAT1  | 00          | 112     |

| F45             | UART Address Compare Register        | U0ADDR   | 00          | 114     |

| F46             | UART Baud Rate High Byte Register    | U0BRH    | FF          | 114     |

| F47             | UART Baud Rate Low Byte Register     | U0BRL    | FF          | 114     |

| Analog-to-Digit | tal Converter (ADC)                  |          |             |         |

| F70             | ADC Control 0                        | ADCCTL0  | 00          | 130     |

| F71             | ADC Control 1                        | ADCCTL1  | 80          | 130     |

| F72             | ADC Data High Byte                   | ADCD_H   | XX          | 133     |

| F73             | ADC Data Low Bits                    | ADCD_L   | XX          | 133     |

| F74–F7F         | Reserved                             |          | XX          |         |

| Low Power Co    | ntrol                                |          |             |         |

| F80             | Power Control 0                      | PWRCTL0  | 80          | 35      |

| F81             | Reserved                             | _        | XX          |         |

| LED Controller  |                                      |          |             |         |

| F82             | LED Drive Enable                     | LEDEN    | 00          | 52      |

| F83             | LED Drive Level High Byte            | LEDLVLH  | 00          | 53      |

| F84             | LED Drive Level Low Byte             | LEDLVLL  | 00          | 54      |

| F85             | Reserved                             | _        | XX          |         |

| Oscillator Cont | rol                                  |          |             |         |

| F86             | Oscillator Control                   | OSCCTL   | A0          | 190     |

| F87–F8F         | Reserved                             |          | XX          |         |

| Comparator 0    |                                      |          |             |         |

| F90             | Comparator 0 Control                 | CMP0     | 14          | 136     |

| XX=Undefined    |                                      | ···· ·   |             |         |

# Table 7. Register File Address Map (Continued)

20

zilog

and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the  $\overline{\text{RESET}}$  input pin is asserted Low, the Z8 Encore! XP<sup>®</sup> F082A Series devices remain in the Reset state. If the  $\overline{\text{RESET}}$  pin is held Low beyond the System Reset time-out, the device exits the Reset state on the system clock rising edge following  $\overline{\text{RESET}}$  pin deassertion. Following a System Reset initiated by the external  $\overline{\text{RESET}}$  pin, the EXT status bit in the Reset Status (RSTSTAT) register is set to 1.

#### **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see Port A–D Control Registers on page 46), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows a Z8 Encore! XP F082A Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the RESET pin Low. The RESET pin is held Low by the internal circuitry until the appropriate delay listed in Table 8 has elapsed.

#### **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control register. The On-Chip Debugger block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset the POR bit in the Reset Status (RSTSTAT) register is set.

## Stop Mode Recovery

STOP mode is entered by execution of a STOP instruction by the eZ8 CPU. See Low-Power Modes on page 33 for detailed STOP mode information. During Stop Mode Recovery (SMR), the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay (see Table 131 on page 229)  $T_{SMR}$ , also includes the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control register (WDTCTL) and the Oscillator Control register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset

## Table 31. LED Drive Level Low Register (LEDLVLL)

| BITS  | 7            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|--------------|-----|-----|-----|-----|-----|-----|-----|--|

| FIELD | LEDLVLL[7:0] |     |     |     |     |     |     |     |  |

| RESET | 0            | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W   | R/W          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR  |              |     |     | F8  | 4H  |     |     |     |  |

LEDLVLL[7:0]—LED Level Low Bit

{LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin.

00 = 3 mA01 = 7 mA10 = 13 mA

11 = 20 mA

## Table 46. Shared Interrupt Select Register (IRQSS)

| BITS  | 7     | 6     | 5        | 4   | 3   | 2   | 1   | 0   |

|-------|-------|-------|----------|-----|-----|-----|-----|-----|

| FIELD | PA7VS | PA6CS | Reserved |     |     |     |     |     |

| RESET | 0     | 0     | 0        | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W   | R/W   | R/W      | R/W | R/W | R/W | R/W | R/W |

| ADDR  |       |       |          | FC  | EH  |     |     |     |

PA7VS—PA7/LVD Selection

0 = PA7 is used for the interrupt for PA7VS interrupt request.

1 = The LVD is used for the interrupt for PA7VS interrupt request.

PA6CS—PA6/Comparator Selection

0 = PA6 is used for the interrupt for PA6CS interrupt request.

1 = The Comparator is used for the interrupt for PA6CS interrupt request.

Reserved—Must be 0.

# **Interrupt Control Register**

The Interrupt Control (IRQCTL) register (Table 47) contains the master enable bit for all interrupts.

| Table 47. | Interrupt | Control | Register | (IRQCTL) |

|-----------|-----------|---------|----------|----------|

|-----------|-----------|---------|----------|----------|

| BITS  | 7    | 6        | 5 | 4  | 3  | 2 | 1 | 0 |

|-------|------|----------|---|----|----|---|---|---|

| FIELD | IRQE | Reserved |   |    |    |   |   |   |

| RESET | 0    | 0        | 0 | 0  | 0  | 0 | 0 | 0 |

| R/W   | R/W  | R        | R | R  | R  | R | R | R |

| ADDR  |      |          |   | FC | FH |   |   |   |

IRQE—Interrupt Request Enable

This bit is set to 1 by executing an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, Reset or by a direct register write of a 0 to this bit.

- 0 = Interrupts are disabled.

- 1 = Interrupts are enabled.

Reserved—Must be 0.

- Set the prescale value.

- If using the Timer Output alternate function, set the initial output level (High or Low).

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS mode. After the first timer Reload in CONTINUOUS mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the Timer Output function) for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In CONTINUOUS mode, the system clock always provides the timer input. The timer period is given by the following equation:

CONTINUOUS Mode Time-Out Period (s) =  $\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT mode equation to determine the first time-out period.

#### **COUNTER Mode**

In COUNTER mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO Port pin Timer Input alternate function. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the Timer Input signal. In COUNTER mode, the prescaler is disabled.

**Caution:** The input frequency of the Timer Input signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the input signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

Upon reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

#### WDT Reset in Normal Operation

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Reset Status (RSTSTAT) register is set to 1. For more information on system reset, see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23.

#### WDT Reset in STOP Mode

If configured to generate a Reset when a time-out occurs and the device is in STOP mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Reset Status (RSTSTAT) register are set to 1 following WDT time-out in STOP mode.

#### Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer (WDTCTL) Control register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers. Follow the steps below to unlock the Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte register (WDTU) with the desired time-out value.

- 4. Write the Watchdog Timer Reload High Byte register (WDTH) with the desired time-out value.

- 5. Write the Watchdog Timer Reload Low Byte register (WDTL) with the desired time-out value.

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

# Watchdog Timer Calibration

Due to its extremely low operating current, the Watchdog Timer oscillator is somewhat inaccurate. This variation can be corrected using the calibration data stored in the Flash Information Page (see Table 97 and Table 98 on page 165). Loading these values into the

# zilog

# Universal Asynchronous Receiver/Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. Features of the UART include:

- 8-bit asynchronous data transfer.

- Selectable even- and odd-parity generation and checking.

- Option of one or two STOP bits.

- Separate transmit and receive interrupts.

- Framing, parity, overrun and break detection.

- Separate transmit and receive enables.

- 16-bit baud rate generator (BRG).

- Selectable MULTIPROCESSOR (9-bit) mode with three configurable interrupt schemes.

- Baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

- Driver enable (DE) output for external bus transceivers.

### Architecture

The UART consists of three primary functional blocks: transmitter, receiver, and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 on page 98 displays the UART architecture.

# 116

| 3.579545 MHz System Clock |                          |                      |              |  |  |  |  |  |

|---------------------------|--------------------------|----------------------|--------------|--|--|--|--|--|

| Acceptable<br>Rate (kHz)  | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) |  |  |  |  |  |

| 1250.0                    | N/A                      | N/A                  | N/A          |  |  |  |  |  |

| 625.0                     | N/A                      | N/A                  | N/A          |  |  |  |  |  |

| 250.0                     | 1                        | 223.72               | -10.51       |  |  |  |  |  |

| 115.2                     | 2                        | 111.9                | -2.90        |  |  |  |  |  |

| 57.6                      | 4                        | 55.9                 | -2.90        |  |  |  |  |  |

| 38.4                      | 6                        | 37.3                 | -2.90        |  |  |  |  |  |

| 19.2                      | 12                       | 18.6                 | -2.90        |  |  |  |  |  |

| 9.60                      | 23                       | 9.73                 | 1.32         |  |  |  |  |  |

| 4.80                      | 47                       | 4.76                 | -0.83        |  |  |  |  |  |

| 2.40                      | 93                       | 2.41                 | 0.23         |  |  |  |  |  |

| 1.20                      | 186                      | 1.20                 | 0.23         |  |  |  |  |  |

| 0.60                      | 373                      | 0.60                 | -0.04        |  |  |  |  |  |

| 0.30                      | 746                      | 0.30                 | -0.04        |  |  |  |  |  |

### Table 70. UART Baud Rates (Continued)

| 1.8432 MHz System Clock  |                          |                      |              |  |  |  |  |  |  |

|--------------------------|--------------------------|----------------------|--------------|--|--|--|--|--|--|

| Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) |  |  |  |  |  |  |

| 1250.0                   | N/A                      | N/A                  | N/A          |  |  |  |  |  |  |

| 625.0                    | N/A                      | N/A                  | N/A          |  |  |  |  |  |  |

| 250.0                    | N/A                      | N/A                  | N/A          |  |  |  |  |  |  |

| 115.2                    | 1                        | 115.2                | 0.00         |  |  |  |  |  |  |

| 57.6                     | 2                        | 57.6                 | 0.00         |  |  |  |  |  |  |

| 38.4                     | 3                        | 38.4                 | 0.00         |  |  |  |  |  |  |

| 19.2                     | 6                        | 19.2                 | 0.00         |  |  |  |  |  |  |

| 9.60                     | 12                       | 9.60                 | 0.00         |  |  |  |  |  |  |

| 4.80                     | 24                       | 4.80                 | 0.00         |  |  |  |  |  |  |

| 2.40                     | 48                       | 2.40                 | 0.00         |  |  |  |  |  |  |

| 1.20                     | 96                       | 1.20                 | 0.00         |  |  |  |  |  |  |

| 0.60                     | 192                      | 0.60                 | 0.00         |  |  |  |  |  |  |

| 0.30                     | 384                      | 0.30                 | 0.00         |  |  |  |  |  |  |

|                          |                          |                      |              |  |  |  |  |  |  |

# Zilog

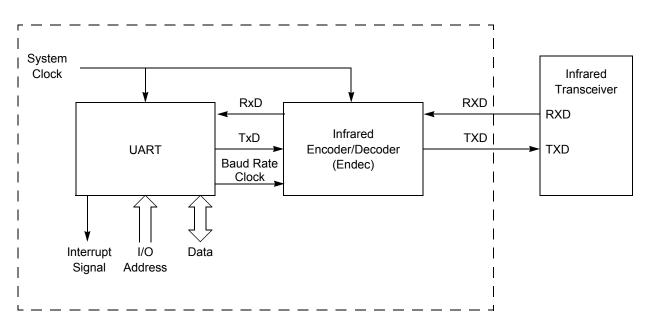

# **Infrared Encoder/Decoder**

The Z8 Encore! XP<sup>®</sup> F082A Series products contain a fully-functional, high-performance UART to Infrared Encoder/Decoder (Endec). The Infrared Endec is integrated with an on-chip UART to allow easy communication between the Z8 Encore! and IrDA Physical Layer Specification, Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers, and other infrared enabled devices.

# Architecture

Figure 16 displays the architecture of the Infrared Endec.

Figure 16. Infrared Data Communication System Block Diagram

# Operation

When the Infrared Endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver through the TXD pin. Likewise, data received from the infrared transceiver is passed to the Infrared Endec through the RXD pin, decoded by the Infrared

Zilog

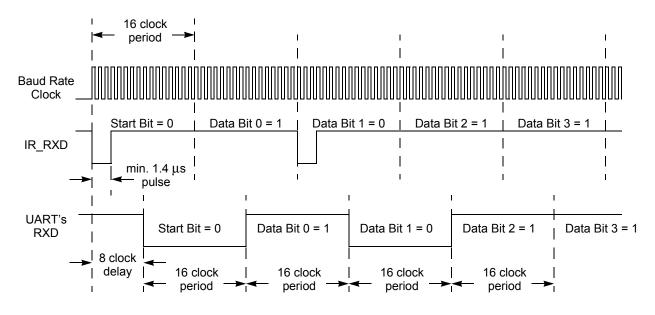

# **Receiving IrDA Data**

Data received from the infrared transceiver using the IR\_RXD signal through the RXD pin is decoded by the Infrared Endec and passed to the UART. The UART's baud rate clock is used by the Infrared Endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 18 displays data reception. When the Infrared Endec is enabled, the UART's RXD signal is internal to the Z8 Encore! XP<sup>®</sup> F082A Series products while the IR\_RXD signal is received through the RXD pin.

Figure 18. IrDA Data Reception

#### **Infrared Data Reception**

**Caution:** The system clock frequency must be at least 1.0 MHz to ensure proper reception of the  $1.4 \,\mu s$  minimum width pulses allowed by the IrDA standard.

#### **Endec Receiver Synchronization**

The IrDA receiver uses a local baud rate clock counter (0 to 15 clock periods) to generate an input stream for the UART and to create a sampling window for detection of incoming pulses. The generated UART input (UART RXD) is delayed by 8 baud rate clock periods with respect to the incoming IrDA data stream. When a falling edge in the input data stream is detected, the Endec counter is reset. When the count reaches a value of 8, the UART RXD value is updated to reflect the value of the decoded data. When the count reaches 12 baud clock periods, the sampling window for the next incoming pulse opens. The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the Endec a sampling window of minus four

# **ADC Control Register Definitions**

# ADC Control Register 0

The ADC Control Register 0 (ADCCTL0) selects the analog input channel and initiates the analog-to-digital conversion. It also selects the voltage reference configuration.

Table 71. ADC Control Register 0 (ADCCTL0)

| BITS  | 7   | 6       | 5      | 4    | 3          | 2   | 1   | 0   |

|-------|-----|---------|--------|------|------------|-----|-----|-----|

| FIELD | CEN | REFSELL | REFOUT | CONT | ANAIN[3:0] |     |     |     |

| RESET | 0   | 0       | 0      | 0    | 0          | 0   | 0   | 0   |

| R/W   | R/W | R/W     | R/W    | R/W  | R/W        | R/W | R/W | R/W |

| ADDR  |     |         |        | F7   | 0H         |     |     |     |

#### CEN—Conversion Enable

0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion is complete.

1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.

REFSELL—Voltage Reference Level Select Low Bit; in conjunction with the High bit (REFSELH) in ADC Control/Status Register 1, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL}; note that this reference is independent of the Comparator reference.

00= Internal Reference Disabled, reference comes from external pin

01= Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

11= Reserved

REFOUT—Internal Reference Output Enable

0 = Reference buffer is disabled; Vref pin is available for GPIO or analog functions

1 = The internal ADC reference is buffered and driven out to the Vref pin

<u>/</u>

**Warning:** When the ADC is used with an external reference ({REFSELH,REFSELL}=00), the REFOUT bit must be set to 0.

#### CONT

0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles (measurements of the internal temperature sensor take twice as long) 1 = Continuous conversion. ADC data updated every 256 system clock cycles after an initial 5129 clock conversion (measurements of the internal temperature sensor take twice as long)

```

Z8 Encore! XP<sup>®</sup> F082A Series

Product Specification

```

136

```

nop ; wait for output to settle

clr irq0 ; clear any spurious interrupts pending

ei

```

# **Comparator Control Register Definitions**

### **Comparator Control Register**

The Comparator Control Register (CMP0) configures the comparator inputs and sets the value of the internal voltage reference.

| Table 75 | . Comparator | Control | Register | (CMP0) |

|----------|--------------|---------|----------|--------|

|----------|--------------|---------|----------|--------|

| BITS  | 7      | 6      | 5   | 4   | 3                    | 2   | 1   | 0   |

|-------|--------|--------|-----|-----|----------------------|-----|-----|-----|

| FIELD | INPSEL | INNSEL |     | REF | Reserved (<br>REFLVI |     |     |     |

| RESET | 0      | 0      | 0   | 1   | 0                    | 1   | 0   | 0   |

| R/W   | R/W    | R/W    | R/W | R/W | R/W                  | R/W | R/W | R/W |

| ADDR  |        | F90H   |     |     |                      |     |     |     |

INPSEL—Signal Select for Positive Input

0 =GPIO pin used as positive comparator input

1 = temperature sensor used as positive comparator input

INNSEL—Signal Select for Negative Input

0 = internal reference disabled, GPIO pin used as negative comparator input

1 = internal reference enabled as negative comparator input

REFLVL—Internal Reference Voltage Level (this reference is independent of the ADC voltage reference). Note that the 8-pin devices contain two additional LSBs for increased resolution.

For 20-/28-pin devices:

$\begin{array}{l} 0000 = 0.0 \ V \\ 0001 = 0.2 \ V \\ 0010 = 0.4 \ V \\ 0011 = 0.6 \ V \\ 0100 = 0.8 \ V \\ 0101 = 1.0 \ V \ (Default) \\ 0110 = 1.2 \ V \\ 0111 = 1.4 \ V \\ 1000 = 1.6 \ V \end{array}$

#### 200

# Assembly Language Syntax

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed if manual program coding is preferred or if you intend to implement your own assembler.

**Example 1**: If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Table 112. Assembly Language Syntax Example 1

| Assembly Language<br>Code | ADD | 43H, | 08H | (ADD dst, src) |

|---------------------------|-----|------|-----|----------------|

| Object Code               | 04  | 08   | 43  | (OPC src, dst) |

**Example 2**: In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Table 113. Assembly Language Syntax Example 2

| Assembly Language<br>Code | ADD | 43H, | R8 | (ADD dst, src) |

|---------------------------|-----|------|----|----------------|

| Object Code               | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

# eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is described in Table 114.

**z**ilog<sup>°</sup>

| 21 | Λ |

|----|---|

| ~  | 4 |

| Assembly        | Symbolic<br>Operation                                                                                                        | Addre        | ss Mode    | Opcode(s) | Flags |          |   |           |   | Fetch | Instr. |   |

|-----------------|------------------------------------------------------------------------------------------------------------------------------|--------------|------------|-----------|-------|----------|---|-----------|---|-------|--------|---|

| Mnemonic        |                                                                                                                              | dst          | src        | (Hex)     | С     | Ζ        | S | ۷         | D | Н     | Cycles |   |

| SUBX dst, src   | $dst \gets dst - src$                                                                                                        | ER           | ER         | 28        | *     | *        | * | *         | 1 | *     | 4      | 3 |

|                 |                                                                                                                              | ER           | IM         | 29        | -     |          |   |           |   |       | 4      | 3 |

| SWAP dst        | $dst[7:4] \leftrightarrow dst[3:0]$                                                                                          | R            |            | F0        | Х     | *        | * | Х         | _ | -     | 2      | 2 |

|                 |                                                                                                                              | IR           |            | F1        | -     |          |   |           |   |       | 2      | 3 |

| TCM dst, src    | (NOT dst) AND src                                                                                                            | r            | r          | 62        | _     | *        | * | 0         | _ | _     | 2      | 3 |

|                 |                                                                                                                              | r            | lr         | 63        | -     |          |   |           |   |       | 2      | 4 |

|                 |                                                                                                                              | R            | R          | 64        | -     |          |   |           |   |       | 3      | 3 |

|                 |                                                                                                                              | R            | IR         | 65        | -     |          |   |           |   |       | 3      | 4 |

|                 |                                                                                                                              | R            | IM         | 66        | -     |          |   |           |   |       | 3      | 3 |

|                 |                                                                                                                              | IR           | IM         | 67        | -     |          |   |           |   |       | 3      | 4 |

| TCMX dst, src   | (NOT dst) AND src                                                                                                            | ER           | ER         | 68        | _     | *        | * | 0         | _ | -     | 4      | 3 |

|                 |                                                                                                                              | ER           | IM         | 69        | -     |          |   |           |   |       | 4      | 3 |

| TM dst, src     | dst AND src                                                                                                                  | r            | r          | 72        | -     | *        | * | 0         | - | -     | 2      | 3 |

|                 |                                                                                                                              | r            | lr         | 73        | -     |          |   |           |   |       | 2      | 4 |

|                 |                                                                                                                              | R            | R          | 74        | -     |          |   |           |   |       | 3      | 3 |

|                 |                                                                                                                              | R            | IR         | 75        | -     |          |   |           |   |       | 3      | 4 |

|                 |                                                                                                                              | R            | IM         | 76        | -     |          |   |           |   |       | 3      | 3 |

|                 |                                                                                                                              | IR           | IM         | 77        | -     |          |   |           |   |       | 3      | 4 |

| TMX dst, src    | dst AND src                                                                                                                  | ER           | ER         | 78        | -     | *        | * | 0         | - | -     | 4      | 3 |

|                 |                                                                                                                              | ER           | IM         | 79        | -     |          |   |           |   |       | 4      | 3 |

| TRAP Vector     | $SP \leftarrow SP - 2$<br>@SP $\leftarrow$ PC<br>$SP \leftarrow SP - 1$<br>@SP $\leftarrow$ FLAGS<br>PC $\leftarrow$ @Vector |              | Vector     | F2        | _     | _        | _ | _         | _ | _     | 2      | 6 |

| WDT             |                                                                                                                              |              |            | 5F        | _     | _        | _ | _         | _ | _     | 1      | 2 |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined                                                                 | of the resul | t of the o | peration. |       | Re<br>Se |   | to (<br>1 | ) |       |        |   |

### Table 124. eZ8 CPU Instruction Summary (Continued)

220

**z**ilog<sup>°</sup>

# 229

# **On-Chip Peripheral AC and DC Electrical Characteristics**

#### Table 131. Power-On Reset and Voltage Brownout Electrical Characteristics and Timing

|                   |                                                                                                                | T <sub>A</sub> = - | 40 °C to +           | 105 °C  |       |                                                                                                       |  |

|-------------------|----------------------------------------------------------------------------------------------------------------|--------------------|----------------------|---------|-------|-------------------------------------------------------------------------------------------------------|--|

| Symbol            | Parameter                                                                                                      | Minimum            | Typical <sup>1</sup> | Maximum | Units | Conditions                                                                                            |  |

| V <sub>POR</sub>  | Power-On Reset<br>Voltage Threshold                                                                            | 2.20               | 2.45                 | 2.70    | V     | V <sub>DD</sub> = V <sub>POR</sub>                                                                    |  |

| V <sub>VBO</sub>  | Voltage Brownout Reset<br>Voltage Threshold                                                                    | 2.15               | 2.40                 | 2.65    | V     | $V_{DD} = V_{VBO}$                                                                                    |  |

|                   | $V_{POR}$ to $V_{VBO}$ hysteresis                                                                              |                    | 50                   | 75      | mV    |                                                                                                       |  |

|                   | Starting V <sub>DD</sub> voltage to<br>ensure valid Power-On<br>Reset.                                         | -                  | $V_{SS}$             | -       | V     |                                                                                                       |  |

| T <sub>ANA</sub>  | Power-On Reset Analog<br>Delay                                                                                 | -                  | 70                   | -       | μs    | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub> Digital<br>Reset delay follows T <sub>ANA</sub> |  |

| T <sub>POR</sub>  | Power-On Reset Digital<br>Delay                                                                                |                    | 16                   |         | μs    | 66 Internal Precision<br>Oscillator cycles + IPO<br>startup time (T <sub>IPOST</sub> )                |  |

| T <sub>POR</sub>  | Power-On Reset Digital<br>Delay                                                                                |                    | 1                    |         | ms    | 5000 Internal Precision<br>Oscillator cycles                                                          |  |

| T <sub>SMR</sub>  | Stop Mode Recovery<br>with crystal oscillator<br>disabled                                                      |                    | 16                   |         | μs    | 66 Internal Precision<br>Oscillator cycles                                                            |  |

| T <sub>SMR</sub>  | Stop Mode Recovery<br>with crystal oscillator<br>enabled                                                       |                    | 1                    |         | ms    | 5000 Internal Precision<br>Oscillator cycles                                                          |  |

| T <sub>VBO</sub>  | Voltage Brownout Pulse<br>Rejection Period                                                                     | _                  | 10                   | -       | μs    | Period of time in which V <sub>DD</sub><br>< V <sub>VBO</sub> without generating<br>a Reset.          |  |

| T <sub>RAMP</sub> | Time for V <sub>DD</sub> to<br>transition from V <sub>SS</sub> to<br>V <sub>POR</sub> to ensure valid<br>Reset | 0.10               | _                    | 100     | ms    |                                                                                                       |  |

| T <sub>SMP</sub>  | Stop Mode Recovery pin pulse rejection period                                                                  |                    | 20                   |         | ns    | For any SMR pin or for the Reset pin when it is asserted in STOP mode.                                |  |

only and are not tested in production.

230

|                                               | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C<br>(unless otherwise stated) |         |         |        |                                                                                                                                                                   |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------|---------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                     | Minimum                                                                                             | Typical | Maximum | Units  | Notes                                                                                                                                                             |

| Flash Byte Read Time                          | 100                                                                                                 | _       | -       | ns     |                                                                                                                                                                   |

| Flash Byte Program Time                       | 20                                                                                                  | _       | 40      | μs     |                                                                                                                                                                   |

| Flash Page Erase Time                         | 10                                                                                                  | -       | -       | ms     |                                                                                                                                                                   |

| Flash Mass Erase Time                         | 200                                                                                                 | -       | -       | ms     |                                                                                                                                                                   |

| Writes to Single Address<br>Before Next Erase | -                                                                                                   | _       | 2       |        |                                                                                                                                                                   |

| Flash Row Program Time                        | -                                                                                                   | _       | 8       | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This<br>parameter is only an issue<br>when bypassing the Flash<br>Controller. |

| Data Retention                                | 100                                                                                                 | _       | _       | years  | 25 °C                                                                                                                                                             |

| Endurance                                     | 10,000                                                                                              | _       | _       | cycles | Program/erase cycles                                                                                                                                              |

#### Table 132. Flash Memory Electrical Characteristics and Timing

#### Table 133. Watchdog Timer Electrical Characteristics and Timing

| V <sub>DD</sub> = 2.7 V to 3.6 V   |  |

|------------------------------------|--|

| T <sub>A</sub> = -40 °C to +105 °C |  |

| (unless otherwise stated)          |  |

| Symbol              | Parameter                | Minimum | Typical | Maximum     | Units | Conditions                                                      |

|---------------------|--------------------------|---------|---------|-------------|-------|-----------------------------------------------------------------|

| F <sub>WDT</sub>    | WDT Oscillator Frequency |         | 10      |             | kHz   |                                                                 |

| F <sub>WDT</sub>    | WDT Oscillator Error     |         |         | <u>+</u> 50 | %     |                                                                 |

| T <sub>WDTCAL</sub> | WDT Calibrated Timeout   | 0.98    | 1       | 1.02        | S     | V <sub>DD</sub> = 3.3 V;<br>T <sub>A</sub> = 30 °C              |

|                     |                          | 0.70    | 1       | 1.30        | S     | $V_{DD}$ = 2.7 V to 3.6 V<br>T <sub>A</sub> = 0 °C to 70 °C     |

|                     |                          | 0.50    | 1       | 1.50        | S     | $V_{DD}$ = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C |

|                    |                                             |         | = 2.7 V to<br>-40 °C to - |            |       |                                 |

|--------------------|---------------------------------------------|---------|---------------------------|------------|-------|---------------------------------|

| Symbol             | Parameter                                   | Minimum | Typical                   | Maximum    | Units | Conditions                      |

| Av                 | Open loop voltage gain                      |         | 80                        |            | dB    |                                 |

| GBW                | Gain/Bandwidth product                      |         | 500                       |            | kHz   |                                 |

| РМ                 | Phase Margin                                |         | 50                        |            | deg   | Assuming 13 pF load capacitance |

| V <sub>osLPO</sub> | Input Offset Voltage                        |         | <u>+</u> 1                | <u>+</u> 4 | mV    |                                 |

| V <sub>osLPO</sub> | Input Offset Voltage<br>(Temperature Drift) |         | 1                         | 10         | μV/C  |                                 |

| V <sub>IN</sub>    | Input Voltage Range                         | 0.3     |                           | Vdd - 1    | V     |                                 |

| V <sub>OUT</sub>   | Output Voltage Range                        | 0.3     |                           | Vdd - 1    | V     | I <sub>OUT</sub> = 45 μA        |

#### Table 136. Low Power Operational Amplifier Electrical Characteristics

### Table 137. Comparator Electrical Characteristics

|                   |                       |                 | = 2.7 V to<br>40 °C to + |                    |               |                    |

|-------------------|-----------------------|-----------------|--------------------------|--------------------|---------------|--------------------|

| Symbol            | Parameter             | Minimum         | Typical                  | Maximum            | Units         | Conditions         |

| V <sub>OS</sub>   | Input DC Offset       |                 | 5                        |                    | mV            |                    |

| V <sub>CREF</sub> | Programmable Internal |                 | <u>+</u> 5               |                    | %             | 20-/28-pin devices |

| Reference Voltage |                       | <u>+</u> 3      |                          | %                  | 8-pin devices |                    |

| T <sub>PROP</sub> | Propagation Delay     |                 | 200                      |                    | ns            |                    |

| V <sub>HYS</sub>  | Input Hysteresis      |                 | 4                        |                    | mV            |                    |

| V <sub>IN</sub>   | Input Voltage Range   | V <sub>SS</sub> |                          | V <sub>DD</sub> -1 | V             |                    |