# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 4KB (4K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 128 x 8                                                      |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f042ash020ec    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| General Purpose I/O Port Output Timing | 236 |

|----------------------------------------|-----|

| On-Chip Debugger Timing                | 237 |

| UART Timing                            | 238 |

| Packaging                              | 241 |

| Ordering Information                   | 251 |

| Index                                  | 261 |

| Customer Support                       | 271 |

zilog

vector address. Following Stop Mode Recovery, the STOP bit in the Reset Status (RSTSTAT) Register is set to 1. Table 10 lists the Stop Mode Recovery sources and resulting actions. The text following provides more detailed information about each of the Stop Mode Recovery sources.

| Operating Mode | Stop Mode Recovery Source                                                         | Action                                                                    |  |  |  |  |

|----------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|

| STOP mode      | Watchdog Timer time-out when configured for Reset                                 | Stop Mode Recovery                                                        |  |  |  |  |

|                | Watchdog Timer time-out when configured for interrupt                             | Stop Mode Recovery followed b<br>interrupt (if interrupts are<br>enabled) |  |  |  |  |

|                | Data transition on any GPIO Port<br>pin enabled as a Stop Mode<br>Recovery source | Stop Mode Recovery                                                        |  |  |  |  |

|                | Assertion of external RESET Pin                                                   | System Reset                                                              |  |  |  |  |

|                | Debug Pin driven Low                                                              | System Reset                                                              |  |  |  |  |

### Table 10. Stop Mode Recovery Sources and Resulting Action

## Stop Mode Recovery Using Watchdog Timer Time-Out

If the Watchdog Timer times out during STOP mode, the device undergoes a Stop Mode Recovery sequence. In the Reset Status (RSTSTAT) register, the WDT and STOP bits are set to 1. If the Watchdog Timer is configured to generate an interrupt upon time-out and the Z8 Encore! XP F082A Series device is configured to respond to interrupts, the eZ8 CPU services the Watchdog Timer interrupt request following the normal Stop Mode Recovery sequence.

## Stop Mode Recovery Using a GPIO Port Pin Transition

Each of the GPIO Port pins may be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a Stop Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery.

**Note:** The SMR pulses shorter than specified does not trigger a recovery (see Table 131 on page 229). When this happens, the STOP bit in the Reset Status (RSTSTAT) register is set to 1.

**Caution:** In STOP mode, the GPIO Port Input Data registers (PxIN) are disabled. The Port Input Data registers record the Port transition only if the signal stays on the Port pin through the end of the Stop Mode Recovery delay. As a result, short pulses on the Port pin can

zilog /

tions as a GPIO pin. If it is not present, the debug feature is disabled until/unless another reset event occurs. For more details, see On-Chip Debugger on page 173.

# **Crystal Oscillator Override**

For systems using a crystal oscillator, PA0 and PA1 are used to connect the crystal. When the crystal oscillator is enabled (see Oscillator Control Register Definitions on page 190), the GPIO settings are overridden and PA0 and PA1 are disabled.

# **5 V Tolerance**

All six I/O pins on the 8-pin devices are 5 V-tolerant, unless the programmable pull-ups are enabled. If the pull-ups are enabled and inputs higher than  $V_{DD}$  are applied to these parts, excessive current flows through those pull-up devices and can damage the chip.

**Note:** In the 20- and 28-pin versions of this device, any pin which shares functionality with an ADC, crystal or comparator port is not 5 V-tolerant, including PA[1:0], PB[5:0] and PC[2:0]. All other signal pins are 5 V-tolerant, and can safely handle inputs higher than  $V_{DD}$  except when the programmable pull-ups are enabled.

# **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control (OSCCTL) register (see Oscillator Control Register Definitions on page 190) such that the external oscillator is selected as the system clock. For 8-pin devices use PA1 instead of PB3.

PIN[7:0]—Port Input Data

Sampled data from the corresponding port pin input.

0 = Input data is logical 0 (Low).

1 = Input data is logical 1 (High).

## Port A–D Output Data Register

The Port A–D Output Data register (Table 28) controls the output data to the pins.

| BITS  | 7     | 6     | 5     | 4          | 3         | 2     | 1     | 0     |

|-------|-------|-------|-------|------------|-----------|-------|-------|-------|

| FIELD | POUT7 | POUT6 | POUT5 | POUT4      | POUT3     | POUT2 | POUT1 | POUT0 |

| RESET | 0     | 0     | 0     | 0          | 0         | 0     | 0     | 0     |

| R/W   | R/W   | R/W   | R/W   | R/W        | R/W       | R/W   | R/W   | R/W   |

| ADDR  |       |       | FI    | D3H, FD7H, | FDBH, FDF | Ή     |       |       |

### Table 28. Port A–D Output Data Register (PxOUT)

POUT[7:0]—Port Output Data

These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 = Drive a logical 0 (Low).

1= Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control register bit to 1.

# LED Drive Enable Register

The LED Drive Enable register (Table 29) activates the controlled current drive. The Port C pin must first be enabled by setting the Alternate Function register to select the LED function.

| BITS  | 7          | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|-------|------------|------|-----|-----|-----|-----|-----|-----|--|--|--|--|

| FIELD | LEDEN[7:0] |      |     |     |     |     |     |     |  |  |  |  |

| RESET | 0          | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |  |

| R/W   | R/W        | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| ADDR  |            | F82H |     |     |     |     |     |     |  |  |  |  |

### Table 29. LED Drive Enable (LEDEN)

zilog<sup>°</sup>.

### **PWM DUAL OUTPUT Mode**

In PWM DUAL OUTPUT mode, the timer outputs a Pulse-Width Modulated (PWM) output signal pair (basic PWM signal and its complement) through two GPIO Port pins. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

If the TPOL bit in the Timer Control register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

The timer also generates a second PWM output signal Timer Output Complement. The Timer Output Complement is the complement of the Timer Output PWM signal. A programmable deadband delay can be configured to time delay (0 to 128 system clock cycles) PWM output transitions on these two pins from a low to a high (inactive to active). This ensures a time gap between the deassertion of one PWM output to the assertion of its complement.

Follow the steps below for configuring a timer for PWM DUAL OUTPUT mode and initiating the PWM operation:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for PWM DUAL OUTPUT mode by writing the TMODE bits in the TxCTL1 register and the TMODEHI bit in TxCTL0 register.

- Set the prescale value.

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the PWM Control register to set the PWM dead band delay value. The deadband delay must be less than the duration of the positive phase of the PWM signal (as defined by the PWM high and low byte registers). It must also be less than the

138

zilog

| BITS  | 7       | 6   | 5    | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-------|---------|-----|------|-----|-----|-----|-----|-----|--|--|--|

| FIELD | INFO_EN |     | PAGE |     |     |     |     |     |  |  |  |

| RESET | 0       | 0   | 0    | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W   | R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W |  |  |  |

| ADDR  |         |     |      | FF  | 9H  |     |     |     |  |  |  |

### Table 80. Flash Page Select Register (FPS)

INFO\_EN—Information Area Enable

0 = Information Area us not selected.

1 = Information Area is selected. The Information Area is mapped into the Program Memory address space at addresses FE00H through FFFFH.

PAGE—Page Select

This 7-bit field identifies the Flash memory page for Page Erase and page unlocking. Program Memory Address[15:9] = PAGE[6:0]. For the Z8F08xx devices, the upper 3 bits must be zero. For the Z8F04xx devices, the upper 4 bits must be zero. For Z8F02xx devices, the upper 5 bits must always be 0. For the Z8F01xx devices, the upper 6 bits must always be 0.

## **Flash Sector Protect Register**

The Flash Sector Protect (FPROT) register is shared with the Flash Page Select Register. When the Flash Control Register is written with 73H followed by 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the 8 available Flash memory sectors to be protected. The reset state of each Sector Protect bit is an unprotected state. After a sector is protected by setting its corresponding register bit, it cannot be unprotected (the register bit cannot be cleared) without powering down the device.

| Table 81. Flash S | ector Protect | Register ( | FPROI) |  |

|-------------------|---------------|------------|--------|--|

|                   |               |            |        |  |

| BITS  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| FIELD | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |

| RESET | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| ADDR  |        |        |        | FF     | 9H     |        |        |        |

# **Oscillator Control**

The Z8 Encore!  $XP^{\mathbb{R}}$  F082A Series devices uses five possible clocking schemes, each user-selectable:

- Internal precision trimmed RC oscillator (IPO).

- On-chip oscillator using off-chip crystal or resonator.

- On-chip oscillator using external RC network.

- External clock drive.

- On-chip low power Watchdog Timer oscillator.

- Clock failure detection circuitry.

In addition, Z8 Encore! XP F082A Series devices contain clock failure detection and recovery circuitry, allowing continued operation despite a failure of the system clock oscillator.

# Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures.

# **System Clock Selection**

The oscillator control block selects from the available clocks. Table 108 details each clock source and its usage.

**z**ilog<sup>®</sup>

| Mode         | Crystal<br>Frequency Range | Function                            | Transconductance<br>(mA/V)<br>Use this range for<br>calculations |      |      |  |  |

|--------------|----------------------------|-------------------------------------|------------------------------------------------------------------|------|------|--|--|

| Low Gain*    | 32 kHz–1 MHz               | Low Power/Frequency Applications    | 0.02                                                             | 0.04 | 0.09 |  |  |

| Medium Gain* | 0.5 MHz–10 MHz             | Medium Power/Frequency Applications | 0.84                                                             | 1.7  | 3.1  |  |  |

| High Gain*   | 8 MHz–20 MHz               | High Power/Frequency Applications   | 1.1                                                              | 2.3  | 4.2  |  |  |

### Table 111. Transconductance Values for Low, Medium, and High Gain Operating Modes

**Note:** \*Printed circuit board layout must not add more than 4 pF of stray capacitance to either XIN or XOUT pins. if no Oscillation occurs, reduce the values of the capacitors C1 and C2 to decrease the loading.

# **Oscillator Operation with an External RC Network**

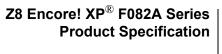

Figure 28 displays a recommended configuration for connection with an external resistor-capacitor (RC) network.

### Figure 28. Connecting the On-Chip Oscillator to an External RC Network

An external resistance value of 45 k $\Omega$  is recommended for oscillator operation with an external RC network. The minimum resistance value to ensure operation is 40 k $\Omega$ . The typical oscillator frequency can be estimated from the values of the resistor (*R* in k $\Omega$ ) and capacitor (*C* in pF) elements using the following equation:

Oscillator Frequency (kHz) =

$$\frac{1 \times 10^{6}}{(0.4 \times R \times C) + (4 \times C)}$$

195

**z**ilog<sup>°</sup>

| 2 | n | 0 |

|---|---|---|

| 4 | υ | 3 |

| Assembly        | Symbolic                                                                                         | Addres        | s Mode   | Opcode(s) |   |          | Fla | ags |   |   | Fetch  | Instr. |

|-----------------|--------------------------------------------------------------------------------------------------|---------------|----------|-----------|---|----------|-----|-----|---|---|--------|--------|

| Mnemonic        | Operation                                                                                        | dst           | src      | (Hex)     | С | Ζ        | S   | ۷   | D | Н | Cycles |        |

| COM dst         | $dst \gets \simdst$                                                                              | R             |          | 60        | - | *        | *   | 0   | - | - | 2      | 2      |

|                 |                                                                                                  | IR            |          | 61        | - |          |     |     |   |   | 2      | 3      |

| CP dst, src     | dst - src                                                                                        | r             | r        | A2        | * | *        | *   | *   | - | - | 2      | 3      |

|                 |                                                                                                  | r             | lr       | A3        | - |          |     |     |   |   | 2      | 4      |

|                 |                                                                                                  | R             | R        | A4        | - |          |     |     |   |   | 3      | 3      |

|                 |                                                                                                  | R             | IR       | A5        | - |          |     |     |   |   | 3      | 4      |

|                 |                                                                                                  | R             | IM       | A6        | - |          |     |     |   |   | 3      | 3      |

|                 |                                                                                                  | IR            | IM       | A7        | - |          |     |     |   |   | 3      | 4      |

| CPC dst, src    | dst - src - C                                                                                    | r             | r        | 1F A2     | * | *        | *   | *   | - | _ | 3      | 3      |

|                 |                                                                                                  | r             | lr       | 1F A3     | - |          |     |     |   |   | 3      | 4      |

|                 |                                                                                                  | R             | R        | 1F A4     | - |          |     |     |   |   | 4      | 3      |

|                 |                                                                                                  | R             | IR       | 1F A5     | - |          |     |     |   |   | 4      | 4      |

|                 |                                                                                                  | R             | IM       | 1F A6     | - |          |     |     |   |   | 4      | 3      |

|                 |                                                                                                  | IR            | IM       | 1F A7     | - |          |     |     |   |   | 4      | 4      |

| CPCX dst, src   | dst - src - C                                                                                    | ER            | ER       | 1F A8     | * | *        | *   | *   | _ | _ | 5      | 3      |

|                 |                                                                                                  | ER            | IM       | 1F A9     | - |          |     |     |   |   | 5      | 3      |

| CPX dst, src    | dst - src                                                                                        | ER            | ER       | A8        | * | *        | *   | *   | _ | _ | 4      | 3      |

|                 |                                                                                                  | ER            | IM       | A9        | - |          |     |     |   |   | 4      | 3      |

| DA dst          | $dst \gets DA(dst)$                                                                              | R             |          | 40        | * | *        | *   | Х   | _ | _ | 2      | 2      |

|                 |                                                                                                  | IR            |          | 41        | - |          |     |     |   |   | 2      | 3      |

| DEC dst         | $dst \gets dst \text{ - } 1$                                                                     | R             |          | 30        | _ | *        | *   | *   | _ | _ | 2      | 2      |

|                 |                                                                                                  | IR            |          | 31        | - |          |     |     |   |   | 2      | 3      |

| DECW dst        | $dst \gets dst \text{ - } 1$                                                                     | RR            |          | 80        | _ | *        | *   | *   | _ | _ | 2      | 5      |

|                 |                                                                                                  | IRR           |          | 81        | - |          |     |     |   |   | 2      | 6      |

| DI              | $IRQCTL[7] \leftarrow 0$                                                                         |               |          | 8F        | _ | _        | _   | _   | _ | _ | 1      | 2      |

| DJNZ dst, RA    | $\begin{array}{l} dst \leftarrow dst - 1 \\ if \ dst \neq 0 \\ PC \leftarrow PC + X \end{array}$ | r             |          | 0A-FA     | _ | _        | _   | _   | _ | _ | 2      | 3      |

| EI              | $IRQCTL[7] \leftarrow 1$                                                                         |               |          | 9F        | _ | -        | _   | _   | - | - | 1      | 2      |

| Flags Notation: | * = Value is a function<br>– = Unaffected<br>X = Undefined                                       | of the result | of the o | peration. |   | Re<br>Se |     |     | ) |   |        |        |

## Table 124. eZ8 CPU Instruction Summary (Continued)

**z**ilog<sup>°</sup>

# 215

| Assembly        | Symbolic<br>Operation                                         | Addres     | s Mode   | Opcode(s) |   |              | FI | ags       |   |   | Fetch | Instr. |

|-----------------|---------------------------------------------------------------|------------|----------|-----------|---|--------------|----|-----------|---|---|-------|--------|

| Mnemonic        |                                                               | dst        | src      | (Hex)     | С | Ζ            | S  | ۷         | D | Н |       | Cycles |

| XOR dst, src    | $dst \gets dst \ XOR \ src$                                   | r          | r        | B2        | _ | *            | *  | 0         | _ | - | 2     | 3      |

|                 |                                                               | r          | lr       | B3        | - |              |    |           |   |   | 2     | 4      |

|                 |                                                               | R          | R        | B4        | - |              |    |           |   |   | 3     | 3      |

|                 |                                                               | R          | IR       | B5        | - |              |    |           |   |   | 3     | 4      |

|                 |                                                               | R          | IM       | B6        | - |              |    |           |   |   | 3     | 3      |

|                 |                                                               | IR         | IM       | B7        | - |              |    |           |   |   | 3     | 4      |

| XORX dst, src   | $dst \gets dst \ XOR \ src$                                   | ER         | ER       | B8        | - | *            | *  | 0         | _ | - | 4     | 3      |

|                 |                                                               | ER         | IM       | B9        | - |              |    |           |   |   | 4     | 3      |

| Flags Notation: | * = Value is a function of<br>– = Unaffected<br>X = Undefined | the result | of the o | peration. | - | : Re<br>: Se |    | to (<br>1 | C |   |       |        |

## Table 124. eZ8 CPU Instruction Summary (Continued)

**z**ilog<sup>°</sup>

|   |             |              |                     |                  |                     |               | Lo           | ower Ni       | bble (He        | x)             |              |            |             |             |           |           |

|---|-------------|--------------|---------------------|------------------|---------------------|---------------|--------------|---------------|-----------------|----------------|--------------|------------|-------------|-------------|-----------|-----------|

|   | 0           | 1            | 2                   | 3                | 4                   | 5             | 6            | 7             | 8               | 9              | А            | В          | С           | D           | Е         | F         |

| • | 1.1         | 2.2          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            | 2.3          | 2.2        | 2.2         | 3.2         | 1.2       | 1.2       |

| 0 | BRK         | SRP<br>IM    | <b>ADD</b><br>r1,r2 | ADD<br>r1,lr2    | <b>ADD</b><br>R2,R1 | ADD<br>IR2,R1 | ADD<br>R1,IM | ADD<br>IR1,IM | ADDX<br>ER2,ER1 | ADDX<br>IM,ER1 | DJNZ<br>r1,X | JR<br>cc,X | LD<br>r1,IM | JP<br>cc,DA | INC<br>r1 | NO        |

|   | 2.2         | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            | ,            |            |             | 00,271      | 1         | See       |

| 1 | RLC         | RLC          | ADC                 | ADC              | ADC                 | ADC           | ADC          | ADC           | ADCX            | ADCX           |              |            |             |             |           | Орсо      |

|   | R1          | IR1          | r1,r2               | r1,lr2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           | Ma        |

| • | 2.2         | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1,        |

| 2 | INC<br>R1   | INC<br>IR1   | <b>SUB</b><br>r1,r2 | SUB<br>r1,lr2    | <b>SUB</b><br>R2,R1 | SUB<br>IR2,R1 | SUB<br>R1,IM | SUB<br>IR1,IM | SUBX<br>ER2,ER1 | SUBX<br>IM,ER1 |              |            |             |             |           | AT        |

|   | 2.2         | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           |           |

| 3 | DEC         | DEC          | SBC                 | SBC              | SBC                 | SBC           | SBC          | SBC           | SBCX            | SBCX           |              |            |             |             |           |           |

| - | R1          | IR1          | r1,r2               | r1,lr2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2         | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           |           |

| 4 | DA          | DA           | OR                  | OR               | OR                  | OR            | OR           | OR            | ORX             | ORX            |              |            |             |             |           |           |

|   | R1          | IR1          | r1,r2               | r1,Ir2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| 5 | 2.2<br>POP  | 2.3<br>POP   | 2.3<br>AND          | 2.4<br>AND       | 3.3<br>AND          | 3.4<br>AND    | 3.3<br>AND   | 3.4<br>AND    | 4.3<br>ANDX     | 4.3<br>ANDX    |              |            |             |             |           | 1.:<br>WE |

| 5 | R1          | IR1          | r1,r2               | r1,lr2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           | VVL       |

|   | 2.2         | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.3       |

| 6 | COM         | COM          | ТСМ                 | TCM              | TCM                 | TCM           | тсм          | TCM           | тсмх            | тсмх           |              |            |             |             |           | STO       |

|   | R1          | IR1          | r1,r2               | r1,lr2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2         | 2.3          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.2       |

| 7 | PUSH        | PUSH         | ТМ                  | TM               | TM                  | TM            | ТМ           | TM            | TMX             | TMX            |              |            |             |             |           | HA        |

|   | R2          | IR2          | r1,r2               | r1,lr2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| 8 | 2.5<br>DECW | 2.6<br>DECW  | 2.5<br>LDE          | 2.9<br>LDEI      | 3.2<br>LDX          | 3.3<br>LDX    | 3.4<br>LDX   | 3.5<br>LDX    | 3.4<br>LDX      | 3.4<br>LDX     |              |            |             |             |           | 1.:<br>D  |

| 0 | RR1         | IRR1         | r1,Irr2             | lr1,lrr2         | r1,ER2              | Ir1,ER2       | IRR2,R1      | IRR2,IR1      | r1,rr2,X        | rr1,r2,X       |              |            |             |             |           | -         |

|   | 2.2         | 2.3          | 2.5                 | 2.9              | 3.2                 | 3.3           | 3.4          | 3.5           | 3.3             | 3.5            |              |            |             |             |           | 1.2       |

| 9 | RL          | RL           | LDE                 | LDEI             | LDX                 | LDX           | LDX          | LDX           | LEA             | LEA            |              |            |             |             |           | E         |

|   | R1          | IR1          | r2,Irr1             | lr2,lrr1         | r2,ER1              | Ir2,ER1       | R2,IRR1      | IR2,IRR1      | r1,r2,X         | rr1,rr2,X      |              |            |             |             |           |           |

|   | 2.5         | 2.6          | 2.3                 | 2.4              | 3.3                 | 3.4           | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.4       |

| A | RR1         | INCW<br>IRR1 | CP                  | CP<br>r1,lr2     | CP<br>D2 D1         | CP            |              |               | CPX<br>ER2,ER1  |                |              |            |             |             |           | RE        |

|   | 2.2         |              | r1,r2<br>2.3        | 2.4              | R2,R1<br>3.3        | IR2,R1<br>3.4 | R1,IM<br>3.3 | IR1,IM<br>3.4 | 4.3             | IM,ER1<br>4.3  |              |            |             |             |           | 1.3       |

| в | CLR         | 2.3<br>CLR   | XOR                 | XOR              | XOR                 | XOR           | XOR          | XOR           | XORX            | XORX           |              |            |             |             |           | IRE       |

|   | R1          | IR1          | r1,r2               | r1,lr2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2         | 2.3          | 2.5                 | 2.9              | 2.3                 | 2.9           |              | 3.4           | 3.2             |                |              |            |             |             |           | 1.2       |

| С | RRC         | RRC          | LDC                 | LDCI             | JP                  | LDC           |              | LD            | PUSHX           |                |              |            |             |             |           | RC        |

|   | R1          | IR1          | r1,Irr2             | lr1,lrr2         | IRR1                | lr1,lrr2      |              | r1,r2,X       | ER2             |                |              |            |             |             |           |           |

| D | 2.2         | 2.3          | 2.5                 | 2.9              | 2.6                 | 2.2           | 3.3          | 3.4<br>LD     | 3.2<br>POPX     |                |              |            |             |             |           | 1.2<br>SC |

| J | SRA<br>R1   | IR1          | LDC<br>r2,Irr1      | LDCI<br>Ir2,Irr1 | IRR1                | BSWAP<br>R1   | DA           | r2,r1,X       | ER1             |                |              |            |             |             |           | 30        |

|   | 2.2         | 2.3          | 2.2                 | 2.3              | 3.2                 | 3.3           | 3.2          | 3.3           | 4.2             | 4.2            |              |            |             |             |           | 1.2       |

| Е | RR          | RR           | BIT                 | LD               | LD                  | LD            | LD           | LD            | LDX             | LDX            |              |            |             |             |           | cc        |

|   | R1          | IR1          | p,b,r1              | r1,Ir2           | R2,R1               | IR2,R1        | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2         | 2.3          | 2.6                 | 2.3              | 2.8                 | 3.3           | 3.3          | 3.4           |                 |                |              | $\bot$     |             |             |           |           |

| F | SWAP        | SWAP         | TRAP                | LD               | MULT                | LD            | BTJ          | BTJ           |                 |                |              | V          |             |             |           |           |

|   | R1          | IR1          | Vector              | lr1,r2           | RR1                 | R2,IR1        | p,b,r1,X     | p,b,lr1,X     |                 |                | 1            | 1          | 1           | 1           | Ţ         | 1         |

Figure 31. First Opcode Map

Upper Nibble (Hex)

218

zilog <sub>226</sub>

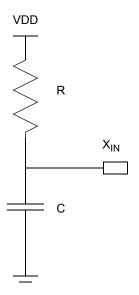

Figure 33 displays the typical current consumption while operating with all peripherals disabled, at 30 °C, versus the system clock frequency.

Figure 33. Typical Active Mode I<sub>DD</sub> Versus System Clock Frequency

zilog

|                   |                   | V <sub>DD</sub> | = 2.7 V to   | 3.6 V      |       |                                                                           |  |  |

|-------------------|-------------------|-----------------|--------------|------------|-------|---------------------------------------------------------------------------|--|--|

| Symbol            | Parameter         | Minimum         | Typical      | Maximum    | Units | Conditions                                                                |  |  |

| T <sub>AERR</sub> | Temperature Error |                 | <u>+</u> 0.5 | <u>+</u> 2 | °C    | Over the range +20 °C<br>to +30 °C (as<br>measured by ADC) <sup>1</sup>   |  |  |

|                   |                   |                 | <u>+</u> 1   | <u>+</u> 5 | °C    | Over the range +0 °C<br>to +70 °C (as<br>measured by ADC)                 |  |  |

|                   |                   |                 | <u>+</u> 2   | <u>+</u> 7 | °C    | Over the range +0 °C<br>to +105 °C (as<br>measured by ADC)                |  |  |

|                   |                   |                 | <u>+</u> 7   |            | °C    | Over the range -40 °C<br>to +105 °C (as<br>measured by ADC)               |  |  |

| T <sub>AERR</sub> | Temperature Error |                 | TBD          |            | °C    | Over the range -40 °C<br>to +105 °C (as<br>measured by<br>comparator)     |  |  |

| t <sub>WAKE</sub> | Wakeup Time       |                 | 80           | 100        | μs    | Time required for<br>Temperature Sensor<br>to stabilize after<br>enabling |  |  |

### **Table 138. Temperature Sensor Electrical Characteristics**

<sup>1</sup>Devices are factory calibrated at for maximal accuracy between +20 °C and +30 °C, so the sensor is maximally accurate in that range. User re-calibration for a different temperature range is possible and increases accuracy near the new calibration point.

## General Purpose I/O Port Input Data Sample Timing

Figure 34 displays timing of the GPIO Port input sampling. The input value on a GPIO Port pin is sampled on the rising edge of the system clock. The Port value is available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

# **On-Chip Debugger Timing**

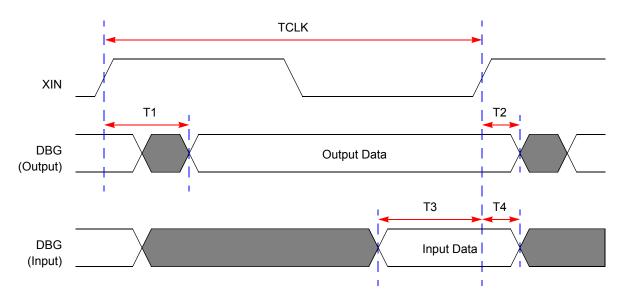

Figure 36 and Table 141 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

Figure 36. On-Chip Debugger Timing

|                |                                  | Delay (ns) |         |  |  |  |

|----------------|----------------------------------|------------|---------|--|--|--|

| Parameter      | Abbreviation                     | Minimum    | Maximum |  |  |  |

| DBG            |                                  |            |         |  |  |  |

| T <sub>1</sub> | XIN Rise to DBG Valid Delay      | -          | 15      |  |  |  |

| T <sub>2</sub> | XIN Rise to DBG Output Hold Time | 2          | _       |  |  |  |

| T <sub>3</sub> | DBG to XIN Rise Input Setup Time | 5          | _       |  |  |  |

| T <sub>4</sub> | DBG to XIN Rise Input Hold Time  | 5          | _       |  |  |  |

### Table 141. On-Chip Debugger Timing

Zilog 239

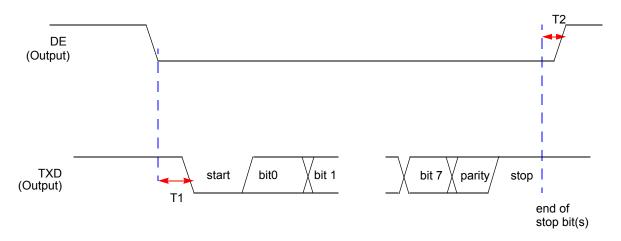

Figure 38 and Table 143 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the transmit data register has been written. DE remains asserted for multiple characters as long as the transmit data register is written with the next character before the current character has completed.

Figure 38. UART Timing Without CTS

| Table | 143. | UART | Timing | Without CTS |

|-------|------|------|--------|-------------|

|-------|------|------|--------|-------------|

|                |                                                                        | Delay (ns)        |            |  |  |  |

|----------------|------------------------------------------------------------------------|-------------------|------------|--|--|--|

| Parameter      | Abbreviation                                                           | Minimum           | Maximum    |  |  |  |

| UART           |                                                                        |                   |            |  |  |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * XIN<br>period | 1 bit time |  |  |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx data register is empty) | ± 5               |            |  |  |  |

| u | 21  |

|---|-----|

|   | 1 7 |

| Part Number                                             | Flash           | RAM       | SOVN | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | <b>Temperature Sensor</b> | Description         |

|---------------------------------------------------------|-----------------|-----------|------|-----------|------------|---------------------|---------------------|----------------|------------|---------------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082A Series with 2 KB Flash |                 |           |      |           |            |                     |                     |                |            |                           |                     |

| Standard Temperature                                    | 9: 0 °C         | to 70 °C  | ;    |           |            |                     |                     |                |            |                           |                     |

| Z8F021APB020SC                                          | 2 KB            | 512 B     | 64 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 8-pin package  |

| Z8F021AQB020SC                                          | 2 KB            | 512 B     | 64 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | QFN 8-pin package   |

| Z8F021ASB020SC                                          | 2 KB            | 512 B     | 64 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 8-pin package  |

| Z8F021ASH020SC                                          | 2 KB            | 512 B     | 64 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 20-pin package |

| Z8F021AHH020SC                                          | 2 KB            | 512 B     | 64 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SSOP 20-pin package |

| Z8F021APH020SC                                          | 2 KB            | 512 B     | 64 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 20-pin package |

| Z8F021ASJ020SC                                          | 2 KB            | 512 B     | 64 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 28-pin package |

| Z8F021AHJ020SC                                          | 2 KB            | 512 B     | 64 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SSOP 28-pin package |

| Z8F021APJ020SC                                          | 2 KB            | 512 B     | 64 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 28-pin package |

| Extended Temperature                                    | e: <b>-40</b> ° | °C to 10  | 5 °C |           |            |                     |                     |                |            |                           |                     |

| Z8F021APB020EC                                          | 2 KB            | 512 B     | 64 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 8-pin package  |

| Z8F021AQB020EC                                          | 2 KB            | 512 B     | 64 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | QFN 8-pin package   |

| Z8F021ASB020EC                                          | 2 KB            | 512 B     | 64 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 8-pin package  |

| Z8F021ASH020EC                                          | 2 KB            | 512 B     | 64 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 20-pin package |

| Z8F021AHH020EC                                          | 2 KB            | 512 B     | 64 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SSOP 20-pin package |

| Z8F021APH020EC                                          | 2 KB            | 512 B     | 64 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 20-pin package |

| Z8F021ASJ020EC                                          | 2 KB            | 512 B     | 64 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 28-pin package |

| Z8F021AHJ020EC                                          | 2 KB            | 512 B     | 64 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SSOP 28-pin package |

| Z8F021APJ020EC                                          | 2 KB            | 512 B     | 64 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 28-pin package |

| Replace C with G for Lead                               | d-Free F        | Packaging | 1    |           |            |                     |                     |                |            |                           |                     |