Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 4KB (4K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 128 x 8                                                      |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f042asj020ec    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

zilog

and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the  $\overline{\text{RESET}}$  input pin is asserted Low, the Z8 Encore! XP<sup>®</sup> F082A Series devices remain in the Reset state. If the  $\overline{\text{RESET}}$  pin is held Low beyond the System Reset time-out, the device exits the Reset state on the system clock rising edge following  $\overline{\text{RESET}}$  pin deassertion. Following a System Reset initiated by the external  $\overline{\text{RESET}}$  pin, the EXT status bit in the Reset Status (RSTSTAT) register is set to 1.

#### **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see Port A–D Control Registers on page 46), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows a Z8 Encore! XP F082A Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the RESET pin Low. The RESET pin is held Low by the internal circuitry until the appropriate delay listed in Table 8 has elapsed.

#### **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control register. The On-Chip Debugger block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset the POR bit in the Reset Status (RSTSTAT) register is set.

#### Stop Mode Recovery

STOP mode is entered by execution of a STOP instruction by the eZ8 CPU. See Low-Power Modes on page 33 for detailed STOP mode information. During Stop Mode Recovery (SMR), the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay (see Table 131 on page 229)  $T_{SMR}$ , also includes the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control register (WDTCTL) and the Oscillator Control register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset

## **Low-Power Modes**

The Z8 Encore! XP F082A Series products contain power-saving features. The highest level of power reduction is provided by the STOP mode, in which nearly all device functions are powered down. The next lower level of power reduction is provided by the HALT mode, in which the CPU is powered down.

Further power savings can be implemented by disabling individual peripheral blocks while in Active mode (defined as being in neither STOP nor HALT mode).

#### **STOP Mode**

Executing the eZ8 CPU's STOP instruction places the device into STOP mode, powering down all peripherals except the Voltage Brownout detector, the Low-power Operational Amplifier and the Watchdog Timer. These three blocks may also be disabled for additional power savings. Specifically, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; XIN and XOUT (if previously enabled) are disabled, and PA0/PA1 revert to the states programmed by the GPIO registers.

- System clock is stopped.

- eZ8 CPU is stopped.

- Program counter (PC) stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control register.

- If enabled, the Watchdog Timer logic continues to operate.

- If enabled for operation in STOP mode by the associated Flash Option Bit, the Voltage Brownout protection circuit continues to operate.

- Low-power operational amplifier continues to operate if enabled by the Power Control register to do so.

- All other on-chip peripherals are idle.

To minimize current in STOP mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP mode using Stop Mode Recovery. For more information on Stop Mode Recovery, see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23.

zilog

**Caution:** To avoid re-triggerings of the Watchdog Timer interrupt after exiting the associated interrupt service routine, it is recommended that the service routine continues to read from the RSTSTAT register until the WDT bit is cleared as given in the following coding sample:

CLEARWDT: LDX r0, RSTSTAT ; read reset status register to clear wdt bit BTJNZ 5, r0, CLEARWDT ; loop until bit is cleared

#### **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap, and the Watchdog Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

#### **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) register (Table 33) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 0 register to determine if any interrupt requests are pending.

| BITS  | 7        | 6   | 5   | 4            | 3     | 2        | 1        | 0    |

|-------|----------|-----|-----|--------------|-------|----------|----------|------|

| FIELD | Reserved | T1I | TOI | <b>U0RXI</b> | U0TXI | Reserved | Reserved | ADCI |

| RESET | 0        | 0   | 0   | 0            | 0     | 0        | 0        | 0    |

| R/W   | R/W      | R/W | R/W | R/W          | R/W   | R/W      | R/W      | R/W  |

| ADDR  |          |     |     | FC           | 0H    |          |          |      |

Table 33. Interrupt Request 0 Register (IRQ0)

Reserved—Must be 0.

T1I—Timer 1 Interrupt Request

- 0 = No interrupt request is pending for Timer 1.

- 1 = An interrupt request from Timer 1 is awaiting service.

T0I—Timer 0 Interrupt Request

- 0 = No interrupt request is pending for Timer 0.

- 1 = An interrupt request from Timer 0 is awaiting service.

Reserved—Must be 0.

C3ENL—Port C3 Interrupt Request Enable Low Bit C2ENL—Port C2 Interrupt Request Enable Low Bit C1ENL—Port C1 Interrupt Request Enable Low Bit C0ENL—Port C0 Interrupt Request Enable Low Bit

#### Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) register (Table 45) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A input pin.

Table 45. Interrupt Edge Select Register (IRQES)

| BITS  | 7    | 6    | 5                 | 4    | 3    | 2    | 1    | 0    |

|-------|------|------|-------------------|------|------|------|------|------|

| FIELD | IES7 | IES6 | IES5              | IES4 | IES3 | IES2 | IES1 | IES0 |

| RESET | 0    | 0    | 0                 | 0    | 0    | 0    | 0    | 0    |

| R/W   | R/W  | R/W  | R/W R/W R/W R/W F |      |      |      | R/W  |      |

| ADDR  |      |      |                   | FC   | DH   |      |      |      |

IES*x*—Interrupt Edge Select *x*

0 = An interrupt request is generated on the falling edge of the PAx input.

1 = An interrupt request is generated on the rising edge of the PAx input.

where *x* indicates the specific GPIO Port pin number (0 through 7).

#### **Shared Interrupt Select Register**

The Shared Interrupt Select (IRQSS) register (Table 46) determines the source of the PADxS interrupts. The Shared Interrupt Select register selects between Port A and alternate sources for the individual interrupts.

Because these shared interrupts are edge-triggered, it is possible to generate an interrupt just by switching from one shared source to another. For this reason, an interrupt must be disabled before switching between sources.

zilog<sup>°</sup>.

(BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with interrupt on time-out. Follow the steps below to configure the Baud Rate Generator as a timer with interrupt on time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 register to 0.

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BRGCTL bit in the UART Control 1 register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval(s) = System Clock Period (s)  $\times$  BRG[15:0]

#### **UART Control Register Definitions**

The UART control registers support the UART and the associated Infrared Encoder/ Decoders. For more information on infrared operation, see Infrared Encoder/Decoder on page 117.

#### **UART Control 0 and Control 1 Registers**

The UART Control 0 (UxCTL0) and Control 1 (UxCTL1) registers (Table 61 and Table 62) configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

| BITS  | 7   | 6   | 5    | 4   | 3    | 2    | 1    | 0    |

|-------|-----|-----|------|-----|------|------|------|------|

| FIELD | TEN | REN | CTSE | PEN | PSEL | SBRK | STOP | LBEN |

| RESET | 0   | 0   | 0    | 0   | 0    | 0    | 0    | 0    |

| R/W   | R/W | R/W | R/W  | R/W | R/W  | R/W  | R/W  | R/W  |

| ADDR  |     |     |      | F4  | 2H   |      |      |      |

Table 61. UART Control 0 Register (U0CTL0)

TEN—Transmit Enable

This bit enables or disables the transmitter. The enable is also controlled by the  $\overline{\text{CTS}}$  signal

and the CTSE bit. If the  $\overline{\text{CTS}}$  signal is Low and the CTSE bit is 1, the transmitter is enabled.

0 = Transmitter disabled.

1 = Transmitter enabled.

REN—Receive Enable

This bit enables or disables the receiver.

0 = Receiver disabled.

1 =Receiver enabled.

CTSE—CTS Enable

$0 = \text{The }\overline{\text{CTS}}$  signal has no effect on the transmitter.

1 = The UART recognizes the  $\overline{\text{CTS}}$  signal as an enable control from the transmitter.

PEN—Parity Enable

This bit enables or disables parity. Even or odd is determined by the PSEL bit.

0 =Parity is disabled.

1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit.

PSEL—Parity Select

0 = Even parity is transmitted and expected on all received data.

1 = Odd parity is transmitted and expected on all received data.

SBRK—Send Break

This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit. 0 = No break is sent.

0 = No break is sent.

1 = Forces a break condition by setting the output of the transmitter to zero.

STOP—Stop Bit Select

0 = The transmitter sends one stop bit.

1 = The transmitter sends two stop bits.

LBEN—Loop Back Enable

0 = Normal operation.

1 = All transmitted data is looped back to the receiver.

#### Table 62. UART Control 1 Register (U0CTL1)

| BITS  | 7       | 6    | 5       | 4    | 3               | 2      | 1      | 0    |

|-------|---------|------|---------|------|-----------------|--------|--------|------|

| FIELD | MPMD[1] | MPEN | MPMD[0] | MPBT | DEPOL           | BRGCTL | RDAIRQ | IREN |

| RESET | 0       | 0    | 0       | 0    | 0               | 0      | 0      | 0    |

| R/W   | R/W     | R/W  | R/W     | R/W  | R/W R/W R/W R/W |        |        |      |

| ADDR  |         |      |         | F4   | 3H              |        |        |      |

#### MPMD[1:0]—MULTIPROCESSOR Mode

If MULTIPROCESSOR (9-bit) mode is enabled,

00 = The UART generates an interrupt request on all received bytes (data and address).

01 = The UART generates an interrupt request only on received address bytes.

10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs.

11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register.

#### MPEN—MULTIPROCESSOR (9-bit) Enable

This bit is used to enable MULTIPROCESSOR (9-bit) mode.

0 = Disable MULTIPROCESSOR (9-bit) mode.

1 = Enable MULTIPROCESSOR (9-bit) mode.

#### MPBT—Multiprocessor Bit Transmit

This bit is applicable only when MULTIPROCESSOR (9-bit) mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.

0 = Send a 0 in the multiprocessor bit location of the data stream (data byte).

1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).

#### DEPOL—Driver Enable Polarity

0 = DE signal is Active High.

1 = DE signal is Active Low.

#### BRGCTL—Baud Rate Control

This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register.

When the UART receiver is **not** enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value 1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.

When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value. 1 = Reads from the Baud Rate High and Low Byte registers return the current BRG count value. Unlike the Timers, there is no mechanism to latch the Low Byte when the High Byte is read.

RDAIRQ—Receive Data Interrupt Enable

0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.

# zilog | 11

#### **UART Address Compare Register**

The UART Address Compare (UxADDR) register stores the multi-node network address of the UART (see Table 67). When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare register. Receive interrupts and RDA assertions only occur in the event of a match.

#### Table 67. UART Address Compare Register (U0ADDR)

| BITS  | 7   | 6 | 5 | 4    | 3     | 2 | 1 | 0   |

|-------|-----|---|---|------|-------|---|---|-----|

| FIELD |     |   |   | COMP | _ADDR |   |   |     |

| RESET | 0   |   |   |      |       |   |   | 0   |

| R/W   | R/W |   |   |      |       |   |   | R/W |

| ADDR  |     |   |   | F4   | 5H    |   |   |     |

COMP\_ADDR—Compare Address

This 8-bit value is compared to incoming address bytes.

#### UART Baud Rate High and Low Byte Registers

The UART Baud Rate High (UxBRH) and Low Byte (UxBRL) registers (Table 68 and Table 69) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART.

#### Table 68. UART Baud Rate High Byte Register (U0BRH)

| BITS  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| FIELD |     |     |     | BF  | RH  |     |     |     |

| RESET | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  |     |     |     | F4  | 6H  |     |     |     |

#### Table 69. UART Baud Rate Low Byte Register (U0BRL)

| BITS  | 7   | 6                                         | 5                  | 4  | 3  | 2 | 1 | 0   |

|-------|-----|-------------------------------------------|--------------------|----|----|---|---|-----|

| FIELD |     |                                           |                    | BI | ٦L |   |   |     |

| RESET | 1   | 1         1         1         1         1 |                    |    |    |   | 1 |     |

| R/W   | R/W | R/W                                       | R/W R/W R/W R/W R/ |    |    |   |   | R/W |

| ADDR  |     |                                           |                    | F4 | 7H |   |   |     |

Compensation Steps:

1. Correct for Offset

#3

| ADC MSB     | ADC LSB    |

|-------------|------------|

| -           |            |

| Offset MSB  | Offset LSB |

| Oliset widd | Oliser LOD |

| =           |            |

| #1 MSB      | #1 LSB     |

2. Take absolute value of the offset corrected ADC value *if negative*—the gain correction factor is computed assuming positive numbers, with sign restoration afterward.

| #2 MSB #2 LS |

|--------------|

|--------------|

Also take absolute value of the gain correction word *if negative*.

| AGain MSB | AGain LSB |

|-----------|-----------|

|-----------|-----------|

3. Multiply by Gain Correction Word. If in DIFFERENTIAL mode, there are two gain correction values: one for positive ADC values, another for negative ADC values. Based on the sign of #2, use the appropriate Gain Correction Word.

|   | #2 MSB    | #2 LSB    |

|---|-----------|-----------|

| * |           |           |

| Γ | AGain MSB | AGain LSB |

|   |           |           |

| = |           |           |

#3

4. Round the result and discard the least significant two bytes (this is equivalent to dividing by  $2^{16}$ ).

#3

| #3   | #3   | #3   | #3   |

|------|------|------|------|

| -    |      |      |      |

| 0x00 | 0x00 | 0x80 | 0x00 |

| =    |      |      |      |

|      |      | 7    |      |

|--|

5. Determine sign of the gain correction factor using the sign bits from Step 2. If the offset corrected ADC value AND the gain correction word have the same sign, then the factor is positive and is left unchanged. If they have differing signs, then the factor is negative and must be multiplied by -1.

#3

High. Because of the open-drain nature of the DBG pin, the host can send a Serial Break to the OCD even if the OCD is transmitting a character.

#### OCD Unlock Sequence (8-Pin Devices Only)

Because of pin-sharing on the 8-pin device, an unlock sequence must be performed to access the DBG pin. If this sequence is not completed during a system reset, then the PA0/DBG pin functions only as a GPIO pin.

The following sequence unlocks the DBG pin:

- 1. Hold PA2/RESET Low.

- 2. Wait 5ms for the internal reset sequence to complete.

- 3. Send the following bytes serially to the debug pin:

```

DBG \leftarrow 80H (autobaud)

DBG \leftarrow EBH

DBG \leftarrow 5AH

DBG \leftarrow 70H

DBG \leftarrow CDH (32-bit unlock key)

```

4. Release PA2/RESET. The PA0/DBG pin is now identical in function to that of the DBG pin on the 20-/28-pin device. To enter DEBUG mode, re-autobaud and write 80H to the OCD control register (see On-Chip Debugger Commands on page 179).

**Caution:** Between Step 3 and Step 4, there is an interval during which the 8-pin device is neither in RESET nor DEBUG mode. If a device has been erased or has not yet been programmed, all program memory bytes contain FFH. The CPU interprets this as an illegal instruction, so some irregular behavior can occur before entering DEBUG mode, and the register values after entering DEBUG mode differs from their specified reset values. However, none of these irregularities prevent programming the Flash memory. Before beginning system debug, it is recommended that some legal code be programmed into the 8-pin device, and that a RESET occurs.

#### **Breakpoints**

Execution Breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the On-Chip Debugger. If Breakpoints are enabled, the OCD enters DEBUG mode and idles the eZ8 CPU. If Breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

186

zilog

**Caution:** It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! XP F082A Series device ceases functioning and can only be recovered by Power-On-Reset.

#### **Oscillator Control Register Definitions**

#### **Oscillator Control Register**

The Oscillator Control Register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

| BITS  | 7     | 6     | 5     | 4     | 3     | 2   | 1      | 0   |

|-------|-------|-------|-------|-------|-------|-----|--------|-----|

| FIELD | INTEN | XTLEN | WDTEN | SOFEN | WDFEN |     | SCKSEL |     |

| RESET | 1     | 0     | 1     | 0     | 0     | 0   | 0      |     |

| R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W | R/W    | R/W |

| ADDR  |       |       |       | F8    | 6H    |     |        |     |

#### Table 109. Oscillator Control Register (OSCCTL)

INTEN—Internal Precision Oscillator Enable

1 = Internal precision oscillator is enabled

0 = Internal precision oscillator is disabled

XTLEN-Crystal Oscillator Enable; this setting overrides the GPIO register control for PA0 and PA1

1 = Crystal oscillator is enabled

0 = Crystal oscillator is disabled

WDTEN—Watchdog Timer Oscillator Enable

1 = Watchdog Timer oscillator is enabled

0 = Watchdog Timer oscillator is disabled

SOFEN—System Clock Oscillator Failure Detection Enable

1 = Failure detection and recovery of system clock oscillator is enabled

0 = Failure detection and recovery of system clock oscillator is disabled

**z**ilog<sup>°</sup>

### 215

| Assembly        | Symbolic                                                      | Addres     | s Mode   | Opcode(s) |   |              | FI | ags       |   |   | Fetch | Instr. |

|-----------------|---------------------------------------------------------------|------------|----------|-----------|---|--------------|----|-----------|---|---|-------|--------|

| Mnemonic        | Operation                                                     | dst        | src      | (Hex)     | С | Ζ            | S  | ۷         | D | Н |       | Cycles |

| XOR dst, src    | $dst \gets dst \ XOR \ src$                                   | r          | r        | B2        | - | *            | *  | 0         | _ | - | 2     | 3      |

|                 |                                                               | r          | lr       | B3        | - |              |    |           |   |   | 2     | 4      |

|                 |                                                               | R          | R        | B4        | - |              |    |           |   |   | 3     | 3      |

|                 |                                                               | R          | IR       | B5        | - |              |    |           |   |   | 3     | 4      |

|                 |                                                               | R          | IM       | B6        | - |              |    |           |   |   | 3     | 3      |

|                 |                                                               | IR         | IM       | B7        | - |              |    |           |   |   | 3     | 4      |

| XORX dst, src   | $dst \gets dst \ XOR \ src$                                   | ER         | ER       | B8        | - | *            | *  | 0         | _ | - | 4     | 3      |

|                 |                                                               | ER         | IM       | B9        | - |              |    |           |   |   | 4     | 3      |

| Flags Notation: | * = Value is a function of<br>– = Unaffected<br>X = Undefined | the result | of the o | peration. | - | : Re<br>: Se |    | to (<br>1 | C |   |       |        |

#### Table 124. eZ8 CPU Instruction Summary (Continued)

zilog 226

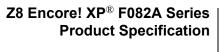

Figure 33 displays the typical current consumption while operating with all peripherals disabled, at 30 °C, versus the system clock frequency.

Figure 33. Typical Active Mode I<sub>DD</sub> Versus System Clock Frequency

<mark>z</mark>ilog<sup>°</sup>

#### **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs.

#### Table 129. AC Characteristics

|                     |                              | T <sub>A</sub> = -40 °C<br>(unless o | V to 3.6 V<br>to +105 °C<br>otherwise<br>ted) |       |                                                                                                         |  |  |  |

|---------------------|------------------------------|--------------------------------------|-----------------------------------------------|-------|---------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol              | Parameter                    | Minimum                              | Maximum                                       | Units | Conditions                                                                                              |  |  |  |

| F <sub>SYSCLK</sub> | System Clock Frequency       | _                                    | 20.0                                          | MHz   | Read-only from Flash memory                                                                             |  |  |  |

|                     |                              | 0.032768                             | 20.0                                          | MHz   | Program or erasure of the<br>Flash memory                                                               |  |  |  |

| F <sub>XTAL</sub>   | Crystal Oscillator Frequency | -                                    | 20.0                                          | MHz   | System clock frequencies<br>below the crystal oscillator<br>minimum require an external<br>clock driver |  |  |  |

| T <sub>XIN</sub>    | System Clock Period          | 50                                   | _                                             | ns    | T <sub>CLK</sub> = 1/F <sub>syscik</sub>                                                                |  |  |  |

| T <sub>XINH</sub>   | System Clock High Time       | 20                                   | 30                                            | ns    | T <sub>CLK</sub> = 50 ns                                                                                |  |  |  |

| T <sub>XINL</sub>   | System Clock Low Time        | 20                                   | 30                                            | ns    | T <sub>CLK</sub> = 50 ns                                                                                |  |  |  |

| T <sub>XINR</sub>   | System Clock Rise Time       | -                                    | 3                                             | ns    | T <sub>CLK</sub> = 50 ns                                                                                |  |  |  |

| T <sub>XINF</sub>   | System Clock Fall Time       | -                                    | 3                                             | ns    | T <sub>CLK</sub> = 50 ns                                                                                |  |  |  |

|                    |                                             |         | = 2.7 V to<br>-40 °C to - |            |       |                                 |

|--------------------|---------------------------------------------|---------|---------------------------|------------|-------|---------------------------------|

| Symbol             | Parameter                                   | Minimum | Typical                   | Maximum    | Units | Conditions                      |

| Av                 | Open loop voltage gain                      |         | 80                        |            | dB    |                                 |

| GBW                | Gain/Bandwidth product                      |         | 500                       |            | kHz   |                                 |

| РМ                 | Phase Margin                                |         | 50                        |            | deg   | Assuming 13 pF load capacitance |

| V <sub>osLPO</sub> | Input Offset Voltage                        |         | <u>+</u> 1                | <u>+</u> 4 | mV    |                                 |

| V <sub>osLPO</sub> | Input Offset Voltage<br>(Temperature Drift) |         | 1                         | 10         | μV/C  |                                 |

| V <sub>IN</sub>    | Input Voltage Range                         | 0.3     |                           | Vdd - 1    | V     |                                 |

| V <sub>OUT</sub>   | Output Voltage Range                        | 0.3     |                           | Vdd - 1    | V     | I <sub>OUT</sub> = 45 μA        |

#### Table 136. Low Power Operational Amplifier Electrical Characteristics

#### Table 137. Comparator Electrical Characteristics

|                   |                       |                 | = 2.7 V to<br>40 °C to + |                    |               |                    |

|-------------------|-----------------------|-----------------|--------------------------|--------------------|---------------|--------------------|

| Symbol            | Parameter             | Minimum         | Typical                  | Maximum            | Units         | Conditions         |

| V <sub>OS</sub>   | Input DC Offset       |                 | 5                        |                    | mV            |                    |

| V <sub>CREF</sub> | Programmable Internal |                 | <u>+</u> 5               |                    | %             | 20-/28-pin devices |

|                   | Reference Voltage     |                 | <u>+</u> 3               | %                  | 8-pin devices |                    |

| T <sub>PROP</sub> | Propagation Delay     |                 | 200                      |                    | ns            |                    |

| V <sub>HYS</sub>  | Input Hysteresis      |                 | 4                        |                    | mV            |                    |

| V <sub>IN</sub>   | Input Voltage Range   | V <sub>SS</sub> |                          | V <sub>DD</sub> -1 | V             |                    |

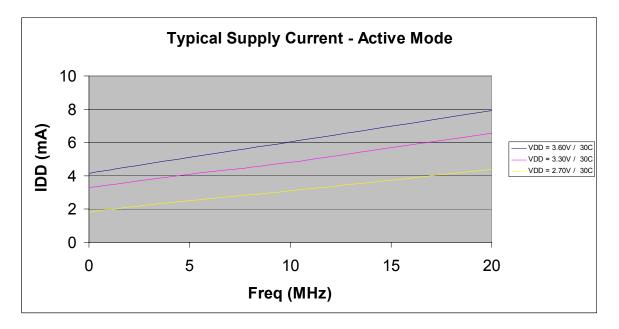

Figure 44 displays the 20-pin Small Shrink Outline Package (SSOP) available for the Z8 Encore! XP F082A Series devices.

Figure 44. 20-Pin Small Shrink Outline Package (SSOP)

# **z**ilog<sup>°</sup>

255

| Part Number                                                                                                                        | Flash     | RAM      | SOVN | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082A Series with 2 KB Flash, 10-Bit Analog-to-Digital Converter<br>Standard Temperature: 0 °C to 70 °C |           |          |      |           |            |                     |                     |                |            |                    |                     |

|                                                                                                                                    |           |          |      |           |            |                     |                     |                |            |                    |                     |

| Z8F022APB020SC                                                                                                                     |           | 512 B    | 64 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F022AQB020SC                                                                                                                     | 2 KB      | 512 B    | 64 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F022ASB020SC                                                                                                                     | 2 KB      | 512 B    | 64 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F022ASH020SC                                                                                                                     | 2 KB      | 512 B    | 64 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F022AHH020SC                                                                                                                     | 2 KB      | 512 B    | 64 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F022APH020SC                                                                                                                     | 2 KB      | 512 B    | 64 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F022ASJ020SC                                                                                                                     | 2 KB      | 512 B    | 64 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F022AHJ020SC                                                                                                                     | 2 KB      | 512 B    | 64 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F022APJ020SC                                                                                                                     | 2 KB      | 512 B    | 64 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperatur                                                                                                                | 'e: -40 ° | C to 10  | 5 °C |           |            |                     |                     |                |            |                    |                     |

| Z8F022APB020EC                                                                                                                     | 2 KB      | 512 B    | 64 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F022AQB020EC                                                                                                                     | 2 KB      | 512 B    | 64 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F022ASB020EC                                                                                                                     | 2 KB      | 512 B    | 64 B | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F022ASH020EC                                                                                                                     | 2 KB      | 512 B    | 64 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F022AHH020EC                                                                                                                     | 2 KB      | 512 B    | 64 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F022APH020EC                                                                                                                     | 2 KB      | 512 B    | 64 B | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F022ASJ020EC                                                                                                                     | 2 KB      | 512 B    | 64 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F022AHJ020EC                                                                                                                     | 2 KB      | 512 B    | 64 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F022APJ020EC                                                                                                                     | 2 KB      | 512 B    | 64 B | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Replace C with G for Lead                                                                                                          | d-Free F  | ackaging |      |           |            |                     |                     |                |            |                    |                     |

| 25 |

|----|

| Part Number                     | Flash     | RAM      | SUVN   | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------|-----------|----------|--------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082 | A Serie   | s with 1 | KB Fla | ish       |            |                     |                     |                |            |                    |                     |

| Standard Temperatur             | e: 0 °C   | to 70 °C |        |           |            |                     |                     |                |            |                    |                     |

| Z8F011APB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F011AQB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F011ASB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F011ASH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F011AHH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F011APH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F011ASJ020SC                  | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F011AHJ020SC                  | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F011APJ020SC                  | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperatur             | re: -40 ° | C to 10  | 5 °C   |           |            |                     |                     |                |            |                    |                     |

| Z8F011APB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F011AQB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F011ASB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F011ASH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F011AHH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F011APH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F011ASJ020EC                  | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F011AHJ020EC                  | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F011APJ020EC                  | 1 KB      | 256 B    | 16 B   | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Replace C with G for Lea        | d-Free P  | ackaging |        |           |            |                     |                     |                |            |                    |                     |