# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | IrDA, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT  |

| Number of I/O              | 23                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | 128 × 8                                                       |

| RAM Size                   | 1K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | A/D 8x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f042asj020ec00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Overview**

Zilog's Z8 Encore!<sup>®</sup> MCU family of products are the first in a line of Zilog<sup>®</sup> microcontroller products based upon the 8-bit eZ8 CPU. Zilog's Z8 Encore! XP<sup>®</sup> F082A Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8<sup>®</sup> instructions. The rich peripheral set of the Z8 Encore! XP F082A Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

#### **Features**

The key features of Z8 Encore! XP F082A Series products include:

- 20 MHz eZ8 CPU

- 1 KB, 2 KB, 4 KB, or 8 KB Flash memory with in-circuit programming capability

- 256 B, 512 B, or 1 KB register RAM

- Up to 128 B non-volatile data storage (NVDS)

- Internal precision oscillator trimmed to  $\pm 1\%$  accuracy

- External crystal oscillator, operating up to 20 MHz

- Optional 8-channel, 10-bit analog-to-digital converter (ADC)

- Optional on-chip temperature sensor

- On-chip analog comparator

- Optional on-chip low-power operational amplifier (LPO)

- Full-duplex UART

- The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared Data Association (IrDA)-compliant infrared encoder/decoders, integrated with UART

- Two enhanced 16-bit timers with capture, compare, and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- Up to 20 vectored interrupts

- 6 to 25 I/O pins depending upon package

#### **Interrupt Controller**

The Z8 Encore! XP<sup>®</sup> F082A Series products support up to 20 interrupts. These interrupts consist of 8 internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

#### **Reset Controller**

The Z8 Encore! XP F082A Series products can be reset using the  $\overline{\text{RESET}}$  pin, Power-On Reset, Watchdog Timer (WDT) time-out, STOP mode exit, or Voltage Brownout (VBO) warning signal. The  $\overline{\text{RESET}}$  pin is bi-directional, that is, it functions as reset source as well as a reset indicator.

# **Pin Description**

The Z8 Encore! XP<sup>®</sup> F082A Series products are available in a variety of packages styles and pin configurations. This chapter describes the signals and available pin configurations for each of the package styles. For information on physical package specifications, see Packaging on page 241.

#### **Available Packages**

The following package styles are available for each device in the Z8 Encore! XP F082A Series product line:

- SOIC

- 8-, 20-, and 28-pin

- PDIP

- 8-, 20-, and 28-pin

- SSOP

- 20- and 28- pin

- QFN (this is an MLF-S, a QFN style package with an 8-pin SOIC footprint)

- 8-pin

In addition, the Z8 Encore! XP F082A Series devices are available both with and without advanced analog capability (ADC, temperature sensor and op amp). Devices Z8F082A, Z8F042A, Z8F022A, and Z8F012A contain the advanced analog, while devices Z8F081A, Z8F041A, Z8F021A, and Z8F011A do not have the advanced analog capability.

#### **Pin Configurations**

Figure 2 through Figure 4 display the pin configurations for all the packages available in the Z8 Encore! XP F082A Series. See Table 2 on page 11 for a description of the signals. The analog input alternate functions (ANAx) are not available on the Z8F081A, Z8F041A, Z8F021A, and Z8F011A devices. The analog supply pins (AV<sub>DD</sub> and AV<sub>SS</sub>) are also not available on these parts, and are replaced by PB6 and PB7.

At reset, all Port A, B and C pins default to an input state. In addition, any alternate functionality is not enabled, so the pins function as general purpose input ports until programmed otherwise. At powerup, the PD0 pin defaults to the RESET alternate function.

mation Area data rather than the Program Memory data. Access to the Flash Information Area is read-only.

| Program Memory Address (Hex) | Function                                                                                  |

|------------------------------|-------------------------------------------------------------------------------------------|

| FE00–FE3F                    | Zilog Option Bits/Calibration Data                                                        |

| FE40-FE53                    | Part Number<br>20-character ASCII alphanumeric code<br>Left justified and filled with FFH |

| FE54–FE5F                    | Reserved                                                                                  |

| FE60–FE7F                    | Zilog Calibration Data                                                                    |

| FE80–FFFF                    | Reserved                                                                                  |

Table 6. Z8 Encore! XP F082A Series Flash Memory Information Area Map

|                                                       | Reset Characteristics and Latency                      |            |                                                               |  |  |  |  |  |

|-------------------------------------------------------|--------------------------------------------------------|------------|---------------------------------------------------------------|--|--|--|--|--|

| Reset Type                                            | Control Registers                                      | eZ8<br>CPU | Reset Latency (Delay)                                         |  |  |  |  |  |

| System Reset                                          | Reset (as applicable)                                  | Reset      | 66 Internal Precision Oscillator Cycles                       |  |  |  |  |  |

| System Reset with Crystal Oscillator Enabled          | Reset (as applicable)                                  | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |  |  |

| Stop Mode Recovery                                    | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |  |  |  |

| Stop Mode Recovery with<br>Crystal Oscillator Enabled | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |  |  |

#### Table 8. Reset and Stop Mode Recovery Characteristics and Latency

During a System Reset or Stop Mode Recovery, the Internal Precision Oscillator requires 4  $\mu$ s to start up. Then the Z8 Encore! XP F082A Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset (POR), this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled, except PD0 (or PA2 on 8-pin devices) which is shared with the reset pin. On reset, the PD0 is configured as a bidirectional open-drain reset. The pin is internally driven low during port reset, after which the user code may reconfigure this pin as a general purpose output.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

As the control registers are re-initialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

# **Interrupt Controller**

The interrupt controller on the Z8 Encore! XP F082A Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of interrupt controller include:

- 20 possible interrupt sources with 18 unique interrupt vectors:

- Twelve GPIO port pin interrupt sources (two interrupt vectors are shared).

- Eight on-chip peripheral interrupt sources (two interrupt vectors are shared).

- Flexible GPIO interrupts:

- Eight selectable rising and falling edge GPIO interrupts.

- Four dual-edge interrupts.

- Three levels of individually programmable interrupt priority.

- Watchdog Timer and LVD can be configured to generate an interrupt.

- Supports vectored as well as polled interrupts

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt controller has no effect on operation. For more information on interrupt servicing by the eZ8 CPU, refer to *eZ8 CPU Core User Manual (UM0128)* available for download at <u>www.zilog.com</u>.

#### Interrupt Vector Listing

Table 32 on page 56 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most-significant byte (MSB) at the even Program Memory address and the least-significant byte (LSB) at the following odd Program Memory address.

**Note:** Some port interrupts are not available on the 8- and 20-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

#### Table 39. IRQ1 Enable and Priority Encoding

| IRQ1ENH[x] | IRQ1ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Medium      |

| 1          | 1          | Level 3  | High        |

|            |            |          |             |

where x indicates the register bits from 0–7.

#### Table 40. IRQ1 Enable High Bit Register (IRQ1ENH)

| BITS  | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |  |  |

|-------|---------|---------|--------|--------|---------------|--------|--------|--------|--|--|

| FIELD | PA7VENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |  |  |

| RESET | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |  |  |

| R/W   | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |  |  |

| ADDR  |         | FC4H    |        |        |               |        |        |        |  |  |

PA7VENH—Port A Bit[7] or LVD Interrupt Request Enable High Bit PA6CENH—Port A Bit[7] or Comparator Interrupt Request Enable High Bit PAxENH—Port A Bit[x] Interrupt Request Enable High Bit

See Shared Interrupt Select (IRQSS) register for selection of either the LVD or the comparator as the interrupt source.

#### Table 41. IRQ1 Enable Low Bit Register (IRQ1ENL)

| BITS  | 7       | 6       | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |

|-------|---------|---------|--------|--------|--------|--------|--------|--------|--|--|--|

| FIELD | PA7VENL | PA6CENL | PA5ENL | PA4ENL | PA3ENL | PA2ENL | PA1ENL | PA0ENL |  |  |  |

| RESET | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      |  |  |  |

| R/W   | R/W     | R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |  |

| ADDR  |         | FC5H    |        |        |        |        |        |        |  |  |  |

PA7VENL—Port A Bit[7] or LVD Interrupt Request Enable Low Bit PA6CENL—Port A Bit[6] or Comparator Interrupt Request Enable Low Bit PAxENL—Port A Bit[x] Interrupt Request Enable Low Bit

zilog<sup>\*</sup>

If the TPOL bit in the Timer Control register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

Follow the steps below for configuring a timer for PWM SINGLE OUTPUT mode and initiating the PWM operation:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for PWM SINGLE OUTPUT mode.

- Set the prescale value.

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM period). The Reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

$PWM Period (s) = \frac{Reload Value \times Prescale}{System Clock Frequency (Hz)}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT mode equation to determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{PWM Value}{Reload Value} \times 100$

zilog<sup>°</sup>

duration of the negative phase of the PWM signal (as defined by the difference between the PWM registers and the Timer Reload registers).

- 5. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM period). The Reload value must be greater than the PWM value.

- 6. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 7. Configure the associated GPIO port pin for the Timer Output and Timer Output Complement alternate functions. The Timer Output Complement function is shared with the Timer Input function for both timers. Setting the timer mode to Dual PWM automatically switches the function from Timer In to Timer Out Complement.

- 8. Write to the Timer Control register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

PWM Period (s) = Reload Value xPrescale System Clock Frequency (Hz)

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT mode equation determines the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{PWM Value}}{\text{Reload Value}} \times 100$

#### **CAPTURE Mode**

In CAPTURE mode, the current timer count value is recorded when the appropriate external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte Registers. The timer input is the system clock. The TPOL bit in the Timer Control register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in TxCTL0 register is set to indicate the timer interrupt is because of an input capture event.

The timer continues counting up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt and continues counting. The INPCAP bit in TxCTL0 register clears indicating the timer interrupt is not because of an input capture event.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In CAPTURE/COMPARE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte register is read, the contents of the Timer Low Byte register are placed in a holding register. A subsequent read from the Timer Low Byte register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte register returns the actual value in the counter.

#### **Timer Pin Signal Operation**

Timer Output is a GPIO Port pin alternate function. The Timer Output is toggled every time the counter is reloaded.

The Timer Input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function Registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

zilog | 1

- 6. Check the TDRE bit in the UART Status 0 register to determine if the Transmit Data register is empty (indicated by a 1). If empty, continue to Step 7. If the Transmit Data register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data register becomes available to receive new data.

- 7. Write the UART Control 1 register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR mode is enabled.

- 11. To transmit additional bytes, return to Step 5.

#### Transmitting Data using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data register to accept new data for transmission. Follow the steps below to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 register to enable MULTIPROCESSOR (9-bit) mode functions, if MULTIPROCESSOR mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR mode.

- 7. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Enable parity, if appropriate and if MULTIPROCESSOR mode is not enabled, and select either even or odd parity.

- Set or clear CTSE to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin.

- 8. Execute an EI instruction to enable interrupts.

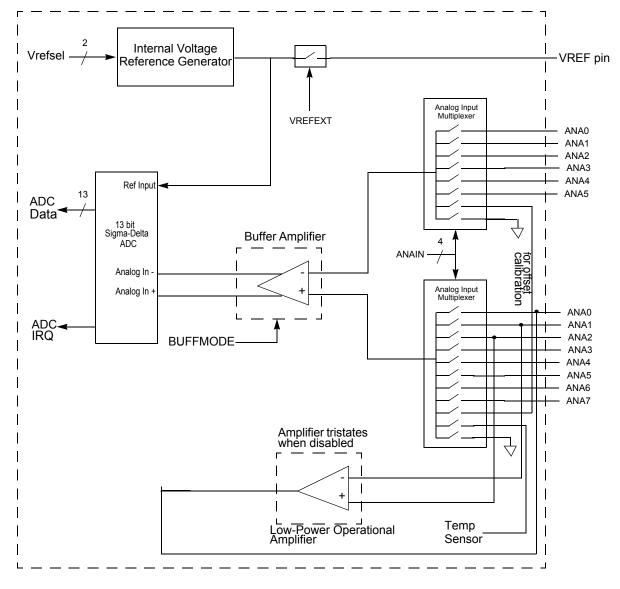

Figure 19. Analog-to-Digital Converter Block Diagram

### Operation

#### Data Format

In both SINGLE-ENDED and DIFFERENTIAL modes, the effective output of the ADC is an 11-bit, signed, two's complement digital value. In DIFFERENTIAL mode, the ADC

# zilog

# **Internal Precision Oscillator**

The internal precision oscillator (IPO) is designed for use without external components. You can either manually trim the oscillator for a non-standard frequency or use the automatic factory-trimmed version to achieve a 5.53 MHz frequency. IPO features include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8 kHz (contains both a fast and a slow mode)

- Trimmed through Flash option bits with user override

- Elimination of crystals or ceramic resonators in applications where very high timing accuracy is not required

#### Operation

An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed the oscillator frequency is stable and does not require subsequent calibration. Trimming is performed during manufacturing and is not necessary for you to repeat unless a frequency other than 5.53 MHz (fast mode) or 32.8 kHz (slow mode) is required. This trimming is done at +30 °C and a supply voltage of 3.3 V, so accuracy of this operating point is optimal.

If not used, the IPO can be disabled by the Oscillator Control register (see Oscillator Control Register Definitions on page 190).

By default, the oscillator frequency is set by the factory trim value stored in the write-protected Flash information page. However, the user code can override these trim values as described in Trim Bit Address Space on page 158.

Select one of two frequencies for the oscillator: 5.53 MHz and 32.8 kHz, using the OSCSEL bits in the Oscillator Control on page 187.

zilog

206

### Table 121. Logical Instructions (Continued)

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| ORX      | dst, src | Logical OR using Extended Addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

#### Table 122. Program Control Instructions

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      | _               | On-Chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | _               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | _               | Return                        |

| TRAP     | vector          | Software Trap                 |

#### Table 123. Rotate and Shift Instructions

| Mnemonic | Operands | Instruction                |

|----------|----------|----------------------------|

| BSWAP    | dst      | Bit Swap                   |

| RL       | dst      | Rotate Left                |

| RLC      | dst      | Rotate Left through Carry  |

| RR       | dst      | Rotate Right               |

| RRC      | dst      | Rotate Right through Carry |

**z**ilog<sup>°</sup>

| 2 | n | 0 |

|---|---|---|

| 4 | υ | 3 |

| Assembly        | Symbolic                                                                                         | Addres        | s Mode   | Opcode(s) |   |          | Fla | ags |   |   | Fetch  | Instr. |

|-----------------|--------------------------------------------------------------------------------------------------|---------------|----------|-----------|---|----------|-----|-----|---|---|--------|--------|

| Mnemonic        | Operation                                                                                        | dst           | src      | (Hex)     | С | Ζ        | S   | ۷   | D | Н | Cycles |        |

| COM dst         | $dst \gets \simdst$                                                                              | R             |          | 60        | - | *        | *   | 0   | - | - | 2      | 2      |

|                 |                                                                                                  | IR            |          | 61        | - |          |     |     |   |   | 2      | 3      |

| CP dst, src     | dst - src                                                                                        | r             | r        | A2        | * | *        | *   | *   | - | - | 2      | 3      |

|                 |                                                                                                  | r             | lr       | A3        | - |          |     |     |   |   | 2      | 4      |

|                 |                                                                                                  | R             | R        | A4        | - |          |     |     |   |   | 3      | 3      |

|                 |                                                                                                  | R             | IR       | A5        | - |          |     |     |   |   | 3      | 4      |

|                 |                                                                                                  | R             | IM       | A6        | - |          |     |     |   |   | 3      | 3      |

|                 |                                                                                                  | IR            | IM       | A7        | - |          |     |     |   |   | 3      | 4      |

| CPC dst, src    | dst - src - C                                                                                    | r             | r        | 1F A2     | * | *        | * * | *   | - | - | 3      | 3      |

|                 |                                                                                                  | r             | lr       | 1F A3     | - |          |     |     |   |   | 3      | 4      |

|                 |                                                                                                  | R             | R        | 1F A4     | - |          |     |     |   |   | 4      | 3      |

|                 |                                                                                                  | R             | IR       | 1F A5     | - |          |     |     |   |   | 4      | 4      |

|                 |                                                                                                  | R             | IM       | 1F A6     | - |          |     |     |   |   | 4      | 3      |

|                 |                                                                                                  | IR            | IM       | 1F A7     | - |          |     |     |   |   | 4      | 4      |

| CPCX dst, src   | dst - src - C                                                                                    | ER            | ER       | 1F A8     | * | *        | *   | *   | _ | _ | 5      | 3      |

|                 |                                                                                                  | ER            | IM       | 1F A9     | - |          |     |     |   |   | 5      | 3      |

| CPX dst, src    | dst - src                                                                                        | ER            | ER       | A8        | * | *        | *   | *   | _ | _ | 4      | 3      |

|                 |                                                                                                  | ER            | IM       | A9        | - |          |     |     |   |   | 4      | 3      |

| DA dst          | $dst \gets DA(dst)$                                                                              | R             |          | 40        | * | *        | *   | Х   | _ | _ | 2      | 2      |

|                 |                                                                                                  | IR            |          | 41        | - |          |     |     |   |   | 2      | 3      |

| DEC dst         | $dst \gets dst \text{ - } 1$                                                                     | R             |          | 30        | _ | *        | *   | *   | _ | _ | 2      | 2      |

|                 |                                                                                                  | IR            |          | 31        | - |          |     |     |   |   | 2      | 3      |

| DECW dst        | $dst \gets dst \text{ - } 1$                                                                     | RR            |          | 80        | _ | *        | *   | *   | _ | _ | 2      | 5      |

|                 |                                                                                                  | IRR           |          | 81        | - |          |     |     |   |   | 2      | 6      |

| DI              | $IRQCTL[7] \leftarrow 0$                                                                         |               |          | 8F        | _ | _        | _   | _   | _ | _ | 1      | 2      |

| DJNZ dst, RA    | $\begin{array}{l} dst \leftarrow dst - 1 \\ if \ dst \neq 0 \\ PC \leftarrow PC + X \end{array}$ | r             |          | 0A-FA     | _ | _        | _   | _   | _ | _ | 2      | 3      |

| EI              | $IRQCTL[7] \leftarrow 1$                                                                         |               |          | 9F        | _ | -        | _   | _   | - | - | 1      | 2      |

| Flags Notation: | * = Value is a function<br>– = Unaffected<br>X = Undefined                                       | of the result | of the o | peration. |   | Re<br>Se |     |     | ) |   |        |        |

#### Table 124. eZ8 CPU Instruction Summary (Continued)

#### Table 128. Power Consumption (Continued)

|                     |                                                      | V <sub>DD</sub> = 2.7 V to 3.6 V |                      |                      |       |                                   |

|---------------------|------------------------------------------------------|----------------------------------|----------------------|----------------------|-------|-----------------------------------|

|                     |                                                      |                                  | Maximum <sup>2</sup> | Maximum <sup>3</sup> |       |                                   |

| Symbol              | Parameter                                            | Typical $^1$                     | Std Temp             | Ext Temp             | Units | Conditions                        |

| I <sub>DD</sub> LPO | Low-Power Operational<br>Amplifier Supply<br>Current | 3                                | 5                    | 5                    | μΑ    | Driving a high-<br>impedance load |

| I <sub>DD</sub> TS  | Temperature Sensor<br>Supply Current                 | 60                               |                      |                      | μA    | See Notes 4                       |

| I <sub>DD</sub> BG  | Band Gap Supply                                      | 320                              | 480                  | 500                  | μA    | For 20-/28-pin devices            |

|                     | Current -                                            |                                  |                      |                      |       | For 8-pin devices                 |

#### Notes

1. Typical conditions are defined as  $V_{DD}$  = 3.3 V and +30 °C.

2. Standard temperature is defined as  $T_A = 0$  °C to +70 °C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

3. Extended temperature is defined as T<sub>A</sub> = -40 °C to +105 °C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

|                    |                                             |         | = 2.7 V to<br>-40 °C to - |            |       |                                 |

|--------------------|---------------------------------------------|---------|---------------------------|------------|-------|---------------------------------|

| Symbol             | Parameter                                   | Minimum | Typical                   | Maximum    | Units | Conditions                      |

| Av                 | Open loop voltage gain                      |         | 80                        |            | dB    |                                 |

| GBW                | Gain/Bandwidth product                      |         | 500                       |            | kHz   |                                 |

| РМ                 | Phase Margin                                |         | 50                        |            | deg   | Assuming 13 pF load capacitance |

| V <sub>osLPO</sub> | Input Offset Voltage                        |         | <u>+</u> 1                | <u>+</u> 4 | mV    |                                 |

| V <sub>osLPO</sub> | Input Offset Voltage<br>(Temperature Drift) |         | 1                         | 10         | μV/C  |                                 |

| V <sub>IN</sub>    | Input Voltage Range                         | 0.3     |                           | Vdd - 1    | V     |                                 |

| V <sub>OUT</sub>   | Output Voltage Range                        | 0.3     |                           | Vdd - 1    | V     | I <sub>OUT</sub> = 45 μA        |

#### Table 136. Low Power Operational Amplifier Electrical Characteristics

#### Table 137. Comparator Electrical Characteristics

|                   |                                            | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C |            |                    |       |                    |

|-------------------|--------------------------------------------|------------------------------------------------------------------------|------------|--------------------|-------|--------------------|

| Symbol            | Parameter                                  | Minimum                                                                | Typical    | Maximum            | Units | Conditions         |

| V <sub>OS</sub>   | Input DC Offset                            |                                                                        | 5          |                    | mV    |                    |

| V <sub>CREF</sub> | Programmable Internal<br>Reference Voltage |                                                                        | <u>+</u> 5 |                    | %     | 20-/28-pin devices |

|                   |                                            |                                                                        | <u>+</u> 3 |                    | %     | 8-pin devices      |

| T <sub>PROP</sub> | Propagation Delay                          |                                                                        | 200        |                    | ns    |                    |

| V <sub>HYS</sub>  | Input Hysteresis                           |                                                                        | 4          |                    | mV    |                    |

| V <sub>IN</sub>   | Input Voltage Range                        | V <sub>SS</sub>                                                        |            | V <sub>DD</sub> -1 | V     |                    |

261

# Index

#### **Symbols**

# 202 % 202 @ 202

#### **Numerics**

10-bit ADC 7 40-lead plastic dual-inline package 248, 249

### Α

absolute maximum ratings 221 AC characteristics 227 ADC 203 architecture 121 automatic power-down 122 block diagram 122 continuous conversion 124 control register 130, 132 control register definitions 130 data high byte register 132 data low bits register 133 electrical characteristics and timing 231 operation 122 single-shot conversion 123 ADCCTL register 130, 132 ADCDH register 132 ADCDL register 133 ADCX 203 ADD 203 add - extended addressing 203 add with carry 203 add with carry - extended addressing 203 additional symbols 202 address space 15 ADDX 203 analog signals 12 analog-to-digital converter (ADC) 121 AND 205

ANDX 205 arithmetic instructions 203 assembly language programming 199 assembly language syntax 200

### В

B 202 b 201 baud rate generator, UART 107 **BCLR 204** binary number suffix 202 **BIT 204** bit 201 clear 204 manipulation instructions 204 set 204 set or clear 204 swap 204 test and jump 206 test and jump if non-zero 206 test and jump if zero 206 bit jump and test if non-zero 206 bit swap 206 block diagram 4 block transfer instructions 204 **BRK 206** BSET 204 BSWAP 204, 206 **BTJ 206 BTJNZ 206 BTJZ 206**

#### С

CALL procedure 206 CAPTURE mode 85, 86 CAPTURE/COMPARE mode 85 cc 201 CCF 204 characteristics, electrical 221 clear 205 CLR 205 COM 205