Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status     Obsolete       Core Processor     eZ8 |                 |

|----------------------------------------------------------|-----------------|

| Core Processor eZ8                                       |                 |

|                                                          |                 |

| Core Size 8-Bit                                          |                 |

| Speed 20MHz                                              |                 |

| Connectivity IrDA, UART/USART                            |                 |

| Peripherals Brown-out Detect/Reset, LED, LVD, POR, P     | WM, WDT         |

| Number of I/O 17                                         |                 |

| Program Memory Size 8KB (8K x 8)                         |                 |

| Program Memory Type FLASH                                |                 |

| EEPROM Size -                                            |                 |

| RAM Size 1K x 8                                          |                 |

| Voltage - Supply (Vcc/Vdd) 2.7V ~ 3.6V                   |                 |

| Data Converters -                                        |                 |

| Oscillator Type Internal                                 |                 |

| Operating Temperature -40°C ~ 105°C (TA)                 |                 |

| Mounting Type Through Hole                               |                 |

| Package / Case 20-DIP (0.300", 7.62mm)                   |                 |

| Supplier Device Package -                                |                 |

| Purchase URL https://www.e-xfl.com/product-detail/zilog/ | /z8f081aph020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

viii

| Hardware Overflow         Automatic Powerdown         Single-Shot Conversion         Continuous Conversion         Interrupts         Calibration and Compensation         ADC Compensation Details         Input Buffer Stage         ADC Control Register Definitions         ADC Control Register 1         ADC Control/Status Register 1         ADC Data High Byte Register         ADC Data Low Byte Register | 123<br>124<br>125<br>125<br>127<br>129<br>130<br>130<br>132<br>132 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Low Power Operational Amplifier                                                                                                                                                                                                                                                                                                                                                                                     | 134                                                                |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                            | 134                                                                |

| Comparator                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

| Operation                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

| Temperature Sensor                                                                                                                                                                                                                                                                                                                                                                                                  | 139                                                                |

| Temperature Sensor Operation                                                                                                                                                                                                                                                                                                                                                                                        | 139                                                                |

| Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                        | 141                                                                |

| Architecture                                                                                                                                                                                                                                                                                                                                                                                                        | 141                                                                |

| Flash Information Area                                                                                                                                                                                                                                                                                                                                                                                              |                                                                    |

| Operation                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

| Flash Operation Timing Using the Flash Frequency Registers                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

| Flash Code Protection Against External Access                                                                                                                                                                                                                                                                                                                                                                       |                                                                    |

| 6 6                                                                                                                                                                                                                                                                                                                                                                                                                 | 147                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                     | 147                                                                |

| Mass Erase                                                                                                                                                                                                                                                                                                                                                                                                          | 147                                                                |

| Flash Controller Bypass                                                                                                                                                                                                                                                                                                                                                                                             | 148                                                                |

| Flash Controller Behavior in DEBUG Mode                                                                                                                                                                                                                                                                                                                                                                             | 148                                                                |

| Flash Control Register Definitions                                                                                                                                                                                                                                                                                                                                                                                  | 149                                                                |

| Flash Control Register                                                                                                                                                                                                                                                                                                                                                                                              | 149                                                                |

| Flash Status Register                                                                                                                                                                                                                                                                                                                                                                                               | 150                                                                |

| Flash Page Select Register                                                                                                                                                                                                                                                                                                                                                                                          | 150                                                                |

**z**ilog<sup>°</sup>

addresses outside the available Flash memory addresses returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 5 describes the Program Memory Maps for the Z8 Encore! XP F082A Series products.

| Program Memory Address (Hex) | Function                     |

|------------------------------|------------------------------|

| Z8F082A and Z8F081A Products |                              |

| 0000–0001                    | Flash Option Bits            |

| 0002–0003                    | Reset Vector                 |

| 0004–0005                    | WDT Interrupt Vector         |

| 0006–0007                    | Illegal Instruction Trap     |

| 0008–0037                    | Interrupt Vectors*           |

| 0038–0039                    | Reserved                     |

| 003A-003D                    | Oscillator Fail Trap Vectors |

| 003E-1FFF                    | Program Memory               |

| Z8F042A and Z8F041A Products |                              |

| 0000–0001                    | Flash Option Bits            |

| 0002–0003                    | Reset Vector                 |

| 0004–0005                    | WDT Interrupt Vector         |

| 0006–0007                    | Illegal Instruction Trap     |

| 0008–0037                    | Interrupt Vectors*           |

| 0038–0039                    | Reserved                     |

| 003A-003D                    | Oscillator Fail Trap Vectors |

| 003E-0FFF                    | Program Memory               |

Table 5. Z8 Encore! XP F082A Series Program Memory Maps

16

# Zilog <sub>19</sub>

# **Register Map**

Table 7 provides the address map for the Register File of the Z8 Encore! XP<sup>®</sup> F082A Series devices. Not all devices and package styles in the Z8 Encore! XP F082A Series support the ADC, or all of the GPIO Ports. Consider registers for unimplemented peripherals as Reserved.

#### Table 7. Register File Address Map

| Address (Hex) | Register Description              | Mnemonic      | Reset (Hex) | Page No |

|---------------|-----------------------------------|---------------|-------------|---------|

| General-Purpo | se RAM                            |               |             |         |

| Z8F082A/Z8F0  | 81A Devices                       |               |             |         |

| 000–3FF       | General-Purpose Register File RAM | _             | XX          |         |

| 400–EFF       | Reserved                          | —             | XX          |         |

| Z8F042A/Z8F0  | 41A Devices                       |               |             |         |

| 000–3FF       | General-Purpose Register File RAM | _             | XX          |         |

| 400–EFF       | Reserved                          | _             | XX          |         |

| Z8F022A/Z8F0  | 21A Devices                       |               |             |         |

| 000–1FF       | General-Purpose Register File RAM | _             | XX          |         |

| 200–EFF       | Reserved                          | —             | XX          |         |

| Z8F012A/Z8F0  | 11A Devices                       |               |             |         |

| 000–0FF       | General-Purpose Register File RAM | _             | XX          |         |

| 100–EFF       | Reserved                          | —             | XX          |         |

| Timer 0       |                                   |               |             |         |

| F00           | Timer 0 High Byte                 | T0H           | 00          | 87      |

| F01           | Timer 0 Low Byte                  | TOL           | 01          | 87      |

| F02           | Timer 0 Reload High Byte          | T0RH          | FF          | 88      |

| F03           | Timer 0 Reload Low Byte           | T0RL          | FF          | 88      |

| F04           | Timer 0 PWM High Byte             | T0PWMH        | 00          | 88      |

| F05           | Timer 0 PWM Low Byte              | <b>T0PWML</b> | 00          | 89      |

| F06           | Timer 0 Control 0                 | TOCTLO        | 00          | 83      |

| F07           | Timer 0 Control 1                 | T0CTL1        | 00          | 84      |

| Timer 1       |                                   |               |             |         |

| F08           | Timer 1 High Byte                 | T1H           | 00          | 87      |

| F09           | Timer 1 Low Byte                  | T1L           | 01          | 87      |

| F0A           | Timer 1 Reload High Byte          | T1RH          | FF          | 88      |

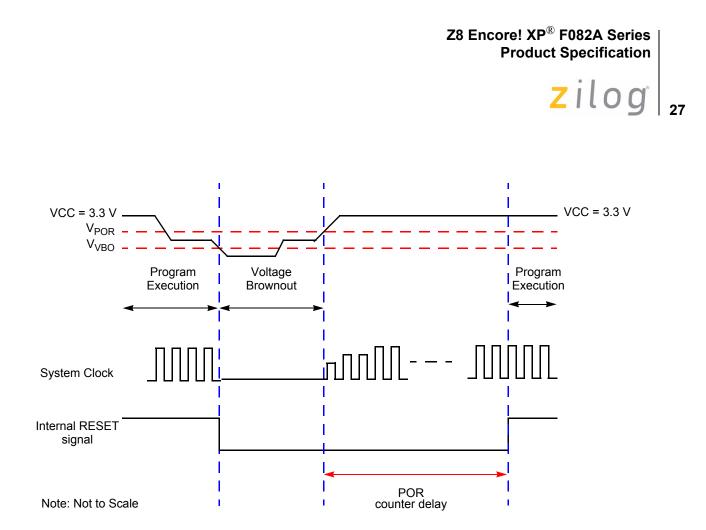

Figure 6. Voltage Brownout Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a Power-On Reset after recovering from a VBO condition.

# Watchdog Timer Reset

If the device is in NORMAL or HALT mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash Option Bit is programmed to 1. This is the unprogrammed state of the WDT\_RES Flash Option Bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT bit in the Reset Status (RSTSTAT) register is set to signify that the reset was initiated by the Watchdog Timer.

### **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system clock and reset signals, the required reset duration may be as short as three clock periods

zilog<sup>®</sup>

Set 1 Sub-Registers on page 50, GPIO Alternate Functions on page 38, and Port A–D Alternate Function Set 2 Sub-Registers on page 51. See GPIO Alternate Functions on page 38 to determine the alternate function associated with each port pin.

Caution:

Do not enable alternate functions for GPIO port pins for which there is no associated alternate function. Failure to follow this guideline can result in unpredictable operation.

| Table 20. Port A–D Alternate Function Sub-Registers | (PxAF) |  |

|-----------------------------------------------------|--------|--|

|                                                     |        |  |

| BITS  | 7                                                           | 6            | 5           | 4             | 3            | 2             | 1            | 0        |

|-------|-------------------------------------------------------------|--------------|-------------|---------------|--------------|---------------|--------------|----------|

| FIELD | AF7                                                         | AF6          | AF5         | AF4           | AF3          | AF2           | AF1          | AF0      |

| RESET | 00H (Ports A–C); 01H (Port D); 04H (Port A of 8-pin device) |              |             |               |              |               |              |          |

| R/W   |                                                             | R/W          |             |               |              |               |              |          |

| ADDR  | lf 02H i                                                    | n Port A–D / | Address Reg | gister, acces | sible throug | n the Port A- | –D Control F | Register |

AF[7:0]—Port Alternate Function enabled

0 = The port pin is in normal mode and the DDx bit in the Port A–D Data Direction sub-register determines the direction of the pin.

1 = The alternate function selected through Alternate Function Set sub-registers is enabled. Port pin operation is controlled by the alternate function.

#### Port A–D Output Control Sub-Registers

The Port A–D Output Control sub-register (Table 21) is accessed through the Port A–D Control register by writing 03H to the Port A–D Address register. Setting the bits in the Port A–D Output Control sub-registers to 1 configures the specified port pins for opendrain operation. These sub-registers affect the pins directly and, as a result, alternate functions are also affected.

#### Table 21. Port A–D Output Control Sub-Registers (PxOC)

| BITS  | 7                             | 6                           | 5           | 4             | 3            | 2             | 1            | 0        |

|-------|-------------------------------|-----------------------------|-------------|---------------|--------------|---------------|--------------|----------|

| FIELD | POC7                          | POC6                        | POC5        | POC4          | POC3         | POC2          | POC1         | POC0     |

| RESET | 00H (Ports A-C); 01H (Port D) |                             |             |               |              |               |              |          |

| R/W   | R/W                           | R/W R/W R/W R/W R/W R/W R/W |             |               |              |               |              |          |

| ADDR  | lf 03H i                      | n Port A–D                  | Address Reg | gister, acces | sible throug | n the Port A- | -D Control F | Register |

POC[7:0]—Port Output Control

These bits function independently of the alternate function bit and always disable the drains if set to 1.

0 = The source current is enabled for any output mode (unless overridden by the alternate

# zilog

# Universal Asynchronous Receiver/Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. Features of the UART include:

- 8-bit asynchronous data transfer.

- Selectable even- and odd-parity generation and checking.

- Option of one or two STOP bits.

- Separate transmit and receive interrupts.

- Framing, parity, overrun and break detection.

- Separate transmit and receive enables.

- 16-bit baud rate generator (BRG).

- Selectable MULTIPROCESSOR (9-bit) mode with three configurable interrupt schemes.

- Baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

- Driver enable (DE) output for external bus transceivers.

#### Architecture

The UART consists of three primary functional blocks: transmitter, receiver, and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 on page 98 displays the UART architecture.

1001 = 1.8 V 1010–1111 = Reserved

For 8-pin devices:

000000 = 0.00 V000001 = 0.05 V000010 = 0.10 V 000011 = 0.15 V 000100 = 0.20 V000101 = 0.25 V000110 = 0.30 V 000111 = 0.35 V 001000 = 0.40 V 001001 = 0.45 V 001010 = 0.50 V 001011 = 0.55 V 001100 = 0.60 V 001101 = 0.65 V 001110 = 0.70 V001111 = 0.75 V 010000 = 0.80 V010001 = 0.85 V010010 = 0.90 V 010011 = 0.95 V 010100 = 1.00 V (Default) 010101 = 1.05 V 010110 = 1.10 V 010111 = 1.15 V 011000 = 1.20 V 011001 = 1.25 V 011010 = 1.30 V 011011 = 1.35 V 011100 = 1.40 V 011101 = 1.45 V 011110 = 1.50 V 011111 = 1.55 V 100000 = 1.60 V100001 = 1.65 V 100010 = 1.70 V 100011 = 1.75 V

Zilog 14

the OCD or via the Flash Controller Bypass mode are unaffected. After a bit of the Sector Protect Register has been set, it cannot be cleared except by powering down the device.

### **Byte Programming**

The Flash Memory is enabled for byte programming after unlocking the Flash Controller and successfully enabling either Mass Erase or Page Erase. When the Flash Controller is unlocked and Mass Erase is successfully completed, all Program Memory locations are available for byte programming. In contrast, when the Flash Controller is unlocked and Page Erase is successfully completed, only the locations of the selected page are available for byte programming. An erased Flash byte contains all 1's (FFH). The programming operation can only be used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from 0 to 1 requires execution of either the Page Erase or Mass Erase commands.

Byte Programming can be accomplished using the On-Chip Debugger's Write Memory command or eZ8 CPU execution of the LDC or LDCI instructions. Refer to the *eZ8 CPU User Manual* (available for download at <u>www.zilog.com</u>) for a description of the LDC and LDCI instructions. While the Flash Controller programs the Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. To exit programming mode and lock the Flash, write any value to the Flash Control register, except the Mass Erase or Page Erase commands.

**Caution:** The byte at each address of the Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs. Doing so may result in corrupted data at the target byte.

#### Page Erase

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

#### Mass Erase

The Flash memory can also be Mass Erased using the Flash Controller, but only by using the On-Chip Debugger. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the Mass Erase successfully enabled, writing the

155

#### **Randomized Lot Identification Bits**

As an optional feature, Zilog is able to provide a factory-programmed random lot identifier. With this feature, all devices in a given production lot are programmed with the same random number. This random number is uniquely regenerated for each successive production lot and is not likely to be repeated.

The randomized lot identifier is a 32 byte binary value, stored in the Flash information page (see Reading the Flash Information Page on page 155 and Randomized Lot Identifier on page 166 for more details) and is unaffected by mass erasure of the device's Flash memory.

## **Reading the Flash Information Page**

The following code example shows how to read data from the Flash information area.

; get value at info address 60 (FE60h)

ldx FPS, #%80 ; enable access to flash info page

ld R0, #%FE

ld R1, #%60

ldc R2, @RR0 ; R2 now contains the calibration value

# **Flash Option Bit Control Register Definitions**

### **Trim Bit Address Register**

The Trim Bit Address (TRMADR) register contains the target address for an access to the trim option bits (Table 84).

| BITS  | 7   | 6   | 5      | 4              | 3           | 2         | 1   | 0   |

|-------|-----|-----|--------|----------------|-------------|-----------|-----|-----|

| FIELD |     |     | TRMADF | R - Trim Bit A | ddress (00H | H to 1FH) |     |     |

| RESET | 0   | 0   | 0      | 0              | 0           | 0         | 0   | 0   |

| R/W   | R/W | R/W | R/W    | R/W            | R/W         | R/W       | R/W | R/W |

| ADDR  |     |     |        | FF             | 6H          |           |     |     |

Table 84. Trim Bit Address Register (TRMADR)

zilog

163

| Info Page<br>Address | Memory<br>Address | Compensation Usage      | ADC Mode                 | Reference<br>Type |

|----------------------|-------------------|-------------------------|--------------------------|-------------------|

| 34                   | FE34              | Negative Gain High Byte | Differential Unbuffered  | External 2.0 V    |

| 35                   | FE35              | Negative Gain Low Byte  | Differential Unbuffered  | External 2.0 V    |

| 78                   | FE78              | Offset                  | Differential 1x Buffered | Internal 2.0 V    |

| 18                   | FE18              | Positive Gain High Byte | Differential 1x Buffered | Internal 2.0 V    |

| 19                   | FE19              | Positive Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V    |

| 36                   | FE36              | Negative Gain High Byte | Differential 1x Buffered | Internal 2.0 V    |

| 37                   | FE37              | Negative Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V    |

| 7B                   | FE7B              | Offset                  | Differential 1x Buffered | External 2.0 V    |

| 1A                   | FE1A              | Positive Gain High Byte | Differential 1x Buffered | External 2.0 V    |

| 1B                   | FE1B              | Positive Gain Low Byte  | Differential 1x Buffered | External 2.0 V    |

| 38                   | FE38              | Negative Gain High Byte | Differential 1x Buffered | External 2.0 V    |

| 39                   | FE39              | Negative Gain Low Byte  | Differential 1x Buffered | External 2.0 V    |

#### Table 94. ADC Calibration Data Location (Continued)

# zilog

180

| Debug Command           | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>mode? | Disabled by<br>Flash Read Protect Option Bit                                                                                                                              |

|-------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write Register          | 08H             | -                                     | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only<br>the Mass Erase command is allowed to<br>be written to the Flash Control register. |

| Read Register           | 09H             | _                                     | Disabled                                                                                                                                                                  |

| Write Program Memory    | 0AH             | _                                     | Disabled                                                                                                                                                                  |

| Read Program Memory     | 0BH             | _                                     | Disabled                                                                                                                                                                  |

| Write Data Memory       | 0CH             | _                                     | Yes                                                                                                                                                                       |

| Read Data Memory        | 0DH             | _                                     | -                                                                                                                                                                         |

| Read Program Memory CRC | 0EH             | _                                     | -                                                                                                                                                                         |

| Reserved                | 0FH             | _                                     | -                                                                                                                                                                         |

| Step Instruction        | 10H             | _                                     | Disabled                                                                                                                                                                  |

| Stuff Instruction       | 11H             | _                                     | Disabled                                                                                                                                                                  |

| Execute Instruction     | 12H             | _                                     | Disabled                                                                                                                                                                  |

| Reserved                | 13H–FFH         | _                                     | _                                                                                                                                                                         |

In the following bulleted list of OCD Commands, data and commands sent from the host to the On-Chip Debugger are identified by 'DBG  $\leftarrow$  Command/Data'. Data sent from the On-Chip Debugger back to the host is identified by 'DBG  $\rightarrow$  Data'

• **Read OCD Revision (00H)**—The Read OCD Revision command determines the version of the On-Chip Debugger. If OCD commands are added, removed, or changed, this revision number changes.

```

DBG \leftarrow 00H

DBG \rightarrow OCDRev[15:8] (Major revision number)

DBG \rightarrow OCDRev[7:0] (Minor revision number)

```

• **Read OCD Status Register (02H)**—The Read OCD Status Register command reads the OCDSTAT register.

```

DBG \leftarrow 02H

DBG \rightarrow OCDSTAT[7:0]

```

• **Read Runtime Counter (03H)**—The Runtime Counter counts system clock cycles in between Breakpoints. The 16-bit Runtime Counter counts up from 0000H and stops at the maximum count of FFFFH. The Runtime Counter is overwritten during the

zilog

183

```

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

• **Read Data Memory (0DH)**—The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode, this command returns FFH for the data.

```

DBG \leftarrow 0DH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

• **Read Program Memory CRC (0EH)**—The Read Program Memory CRC command computes and returns the Cyclic Redundancy Check (CRC) of Program Memory using the 16-bit CRC-CCITT polynomial. If the device is not in DEBUG mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program Memory, calculates the CRC value, and returns the result. The delay is a function of the Program Memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program Memory.

DBG  $\leftarrow$  0EH DBG  $\rightarrow$  CRC[15:8] DBG  $\rightarrow$  CRC[7:0]

• Step Instruction (10H)—The Step Instruction command steps one assembly instruction at the current Program Counter (PC) location. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

DBG  $\leftarrow$  10H

• Stuff Instruction (11H)—The Stuff Instruction command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0-4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

• **Execute Instruction (12H)**—The Execute Instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over Breakpoints. The number of bytes to send for the instruction depends on the opcode.

zilog

194

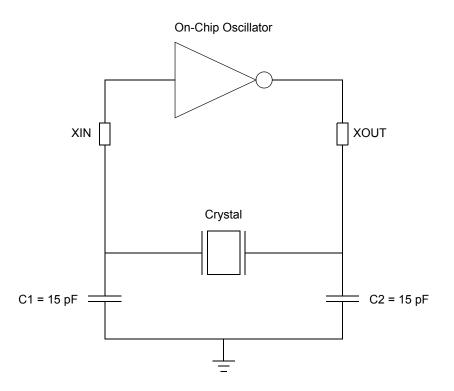

Figure 27 displays a recommended configuration for connection with an external fundamental-mode, parallel-resonant crystal operating at 20 MHz. Recommended 20 MHz crystal specifications are provided in Table 110. Printed circuit board layout must add no more than 4 pF of stray capacitance to either the X<sub>IN</sub> or X<sub>OUT</sub> pins. If oscillation does not occur, reduce the values of capacitors C<sub>1</sub> and C<sub>2</sub> to decrease loading.

#### Figure 27. Recommended 20 MHz Crystal Oscillator Configuration

| Table 110. Recommended Crystal Oscillator Specifications |

|----------------------------------------------------------|

|----------------------------------------------------------|

| Parameter                           | Value       | Units | Comments |

|-------------------------------------|-------------|-------|----------|

| Frequency                           | 20          | MHz   |          |

| Resonance                           | Parallel    |       |          |

| Mode                                | Fundamental |       |          |

| Series Resistance (R <sub>S</sub> ) | 60          | Ω     | Maximum  |

| Load Capacitance (C <sub>L</sub> )  | 30          | pF    | Maximum  |

| Shunt Capacitance (C <sub>0</sub> ) | 7           | pF    | Maximum  |

| Drive Level                         | 1           | mW    | Maximum  |

**z**ilog<sup>®</sup>

| Mode         | Crystal<br>Frequency Range | Function                            | Use  | sconduo<br>(mA/V)<br>this ran<br>alculatio | ge for |

|--------------|----------------------------|-------------------------------------|------|--------------------------------------------|--------|

| Low Gain*    | 32 kHz–1 MHz               | Low Power/Frequency Applications    | 0.02 | 0.04                                       | 0.09   |

| Medium Gain* | 0.5 MHz–10 MHz             | Medium Power/Frequency Applications | 0.84 | 1.7                                        | 3.1    |

| High Gain*   | 8 MHz–20 MHz               | High Power/Frequency Applications   | 1.1  | 2.3                                        | 4.2    |

#### Table 111. Transconductance Values for Low, Medium, and High Gain Operating Modes

**Note:** \*Printed circuit board layout must not add more than 4 pF of stray capacitance to either XIN or XOUT pins. if no Oscillation occurs, reduce the values of the capacitors C1 and C2 to decrease the loading.

# **Oscillator Operation with an External RC Network**

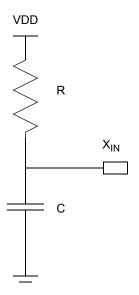

Figure 28 displays a recommended configuration for connection with an external resistor-capacitor (RC) network.

#### Figure 28. Connecting the On-Chip Oscillator to an External RC Network

An external resistance value of 45 k $\Omega$  is recommended for oscillator operation with an external RC network. The minimum resistance value to ensure operation is 40 k $\Omega$ . The typical oscillator frequency can be estimated from the values of the resistor (*R* in k $\Omega$ ) and capacitor (*C* in pF) elements using the following equation:

Oscillator Frequency (kHz) =

$$\frac{1 \times 10^{6}}{(0.4 \times R \times C) + (4 \times C)}$$

195

zilog

207

#### Table 123. Rotate and Shift Instructions (Continued)

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| SRA      | dst      | Shift Right Arithmetic |

| SRL      | dst      | Shift Right Logical    |

| SWAP     | dst      | Swap Nibbles           |

# eZ8 CPU Instruction Summary

Table 124 summarizes the eZ8 CPU instructions. The table identifies the addressing modes employed by the instruction, the effect upon the Flags register, the number of CPU clock cycles required for the instruction fetch, and the number of CPU clock cycles required for the instruction.

| Assembly<br>Mnemonic | Symbolic                                                   | Addres        | s Mode   | Opcode(s) |   |          | FI | ags       | Fetch | Instr. |   |   |

|----------------------|------------------------------------------------------------|---------------|----------|-----------|---|----------|----|-----------|-------|--------|---|---|

|                      | Operation                                                  | dst           | src      | (Hex)     | С | Ζ        | S  | ۷         | D     | Н      |   |   |

| ADC dst, src         | $dst \gets dst + src + C$                                  | r             | r        | 12        | * | *        | *  | *         | 0     | *      | 2 | 3 |

|                      |                                                            | r             | lr       | 13        | - |          |    |           |       |        | 2 | 4 |

|                      |                                                            | R             | R        | 14        | - |          |    |           |       |        | 3 | 3 |

|                      |                                                            | R             | IR       | 15        | - |          |    |           |       |        | 3 | 4 |

|                      |                                                            | R             | IM       | 16        | - |          |    |           |       |        | 3 | 3 |

|                      |                                                            | IR            | IM       | 17        | - |          |    |           |       |        | 3 | 4 |

| ADCX dst, src        | $dst \gets dst + src + C$                                  | ER            | ER       | 18        | * | *        | *  | *         | 0     | *      | 4 | 3 |

|                      |                                                            | ER            | IM       | 19        | - |          |    |           |       |        | 4 | 3 |

| ADD dst, src         | $dst \gets dst + src$                                      | r             | r        | 02        | * | *        | *  | *         | 0     | *      | 2 | 3 |

|                      |                                                            | r             | lr       | 03        | - |          |    |           |       |        | 2 | 4 |

|                      |                                                            | R             | R        | 04        | - |          |    |           |       |        | 3 | 3 |

|                      |                                                            | R             | IR       | 05        | - |          |    |           |       |        | 3 | 4 |

|                      |                                                            | R             | IM       | 06        | - |          |    |           |       |        | 3 | 3 |

|                      |                                                            | IR            | IM       | 07        | - |          |    |           |       |        | 3 | 4 |

| ADDX dst, src        | $dst \gets dst + src$                                      | ER            | ER       | 08        | * | *        | *  | *         | 0     | *      | 4 | 3 |

|                      |                                                            | ER            | IM       | 09        | - |          |    |           |       |        | 4 | 3 |

| Flags Notation:      | * = Value is a function<br>– = Unaffected<br>X = Undefined | of the result | of the o | peration. |   | Re<br>Se |    | to (<br>1 | )     |        |   |   |

Table 124. eZ8 CPU Instruction Summary

**z**ilog<sup>°</sup>

# 215

| Assembly        | Symbolic                                                      | Addres     | s Mode   | Opcode(s) |   |              | FI | ags       | Fetch | Instr. |   |        |

|-----------------|---------------------------------------------------------------|------------|----------|-----------|---|--------------|----|-----------|-------|--------|---|--------|

| Mnemonic        | Operation                                                     | dst        | src      | (Hex)     | С | Ζ            | S  | ۷         | D     | Н      |   | Cycles |

| XOR dst, src    | $dst \gets dst \ XOR \ src$                                   | r          | r        | B2        | _ | *            | *  | 0         | _     | -      | 2 | 3      |

|                 |                                                               | r          | lr       | B3        | - |              |    |           |       |        | 2 | 4      |

|                 |                                                               | R          | R        | B4        | - |              |    |           |       |        | 3 | 3      |

|                 |                                                               | R          | IR       | B5        | - |              |    |           |       |        | 3 | 4      |

|                 |                                                               | R          | IM       | B6        | - |              |    |           |       |        | 3 | 3      |

|                 |                                                               | IR         | IM       | B7        | - |              |    |           |       |        | 3 | 4      |

| XORX dst, src   | $dst \gets dst \ XOR \ src$                                   | ER         | ER       | B8        | - | *            | *  | 0         | _     | -      | 4 | 3      |

|                 |                                                               | ER         | IM       | B9        | - |              |    |           |       |        | 4 | 3      |

| Flags Notation: | * = Value is a function of<br>– = Unaffected<br>X = Undefined | the result | of the o | peration. | - | : Re<br>: Se |    | to (<br>1 | C     |        |   |        |

#### Table 124. eZ8 CPU Instruction Summary (Continued)

zilog

228

|                    |                                                         | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C<br>(unless otherwise stated) |            |            |       |                                                   |  |

|--------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------|------------|-------|---------------------------------------------------|--|

| Symbol             | Parameter                                               | Minimum                                                                                             | Typical    | Maximum    | Units | Conditions                                        |  |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (High Speed) |                                                                                                     | 5.53       |            | MHz   | V <sub>DD</sub> = 3.3 V<br>T <sub>A</sub> = 30 °C |  |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (Low Speed)  |                                                                                                     | 32.7       |            | kHz   | V <sub>DD</sub> = 3.3 V<br>T <sub>A</sub> = 30 °C |  |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Error                  |                                                                                                     | <u>+</u> 1 | <u>+</u> 4 | %     |                                                   |  |

| T <sub>IPOST</sub> | Internal Precision Oscillator<br>Startup Time           |                                                                                                     | 3          |            | μs    |                                                   |  |

#### Table 130. Internal Precision Oscillator Electrical Characteristics

**z**ilog<sup>°</sup>

## 251

# **Ordering Information**

Order the Z8 Encore! XP<sup>®</sup> F082A Series from Zilog<sup>®</sup>, using the following part numbers. For more information on ordering, please consult your local Zilog sales office. The Zilog website (<u>www.zilog.com</u>) lists all regional offices and provides additional Z8 Encore! XP product information.

| Part Number                                                                                                                       | Flash    | RAM      | NVDS | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|-----------------------------------------------------------------------------------------------------------------------------------|----------|----------|------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082A Series with 8 KB Flash, 10-Bit Analog-to-Digital Converter<br>Standard Temperature: 0 °C to 70°C |          |          |      |           |            |                     |                     |                |            | verter             |                     |

| Z8F082APB020SC                                                                                                                    | 8 KB     | 1 KB     | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082APB020SC                                                                                                                    | 8 KB     | 1 KB     | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020SC                                                                                                                    | 8 KB     | 1 KB     | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020SC                                                                                                                    | 8 KB     | 1 KB     | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020SC                                                                                                                    | 8 KB     | 1 KB     | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020SC                                                                                                                    | 8 KB     | 1 KB     | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          |                    | PDIP 20-pin package |

| Z8F082ASJ020SC                                                                                                                    | 8 KB     | 1 KB     | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020SC                                                                                                                    | 8 KB     | 1 KB     | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020SC                                                                                                                    | 8 KB     | 1 KB     | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperature                                                                                                              | e: -40 ° | C to 10  | 5 °C |           |            |                     |                     |                |            |                    |                     |

| Z8F082APB020EC                                                                                                                    | 8 KB     | 1 KB     | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082AQB020EC                                                                                                                    | 8 KB     | 1 KB     | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020EC                                                                                                                    | 8 KB     | 1 KB     | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020EC                                                                                                                    | 8 KB     | 1 KB     | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020EC                                                                                                                    | 8 KB     | 1 KB     | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020EC                                                                                                                    | 8 KB     | 1 KB     | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F082ASJ020EC                                                                                                                    | 8 KB     | 1 KB     | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020EC                                                                                                                    | 8 KB     | 1 KB     | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020EC                                                                                                                    | 8 KB     | 1 KB     | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Replace C with G for Lead                                                                                                         | d-Free P | ackaging |      |           |            |                     |                     |                |            |                    |                     |

RL 206

Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

zilog | 267

register 201 ADC control (ADCCTL) 130, 132 ADC data high byte (ADCDH) 132 ADC data low bits (ADCDL) 133 flash control (FCTL) 149, 155, 156 flash high and low byte (FFREQH and FREEQL) 152 flash page select (FPS) 150, 151 flash status (FSTAT) 150 GPIO port A-H address (PxADDR) 46 GPIO port A-H alternate function sub-registers 48 GPIO port A-H control address (PxCTL) 47 GPIO port A-H data direction sub-registers 47 OCD control 184 OCD status 185 UARTx baud rate high byte (UxBRH) 114 UARTx baud rate low byte (UxBRL) 114 UARTx Control 0 (UxCTL0) 108, 114 UARTx control 1 (UxCTL1) 109 UARTx receive data (UxRXD) 113 UARTx status 0 (UxSTAT0) 111 UARTx status 1 (UxSTAT1) 112 UARTx transmit data (UxTXD) 113 Watchdog Timer control (WDTCTL) 31, 94, 136, 190 Watchdog Timer reload high byte (WDTH) 95 Watchdog Timer reload low byte (WDTL) 95 Watchdog Timer reload upper byte (WD-TU) 95 register file 15 register pair 201 register pointer 202 reset and stop mode characteristics 24 and Stop Mode Recovery 23 carry flag 204 sources 25 **RET 206** return 206

RLC 206 rotate and shift instuctions 206 rotate left 206 rotate left through carry 206 rotate right 206 rotate right through carry 206 RP 202 RR 201, 206 rr 201 RRC 206

# S

**SBC 203** SCF 204, 205 second opcode map after 1FH 219 set carry flag 204, 205 set register pointer 205 shift right arithmatic 207 shift right logical 207 signal descriptions 11 single-shot conversion (ADC) 123 software trap 206 source operand 202 SP 202 SRA 207 src 202 SRL 207 **SRP 205** stack pointer 202 **STOP 205** STOP mode 33 stop mode 205 Stop Mode Recovery sources 28 using a GPIO port pin transition 29 using Watchdog Timer time-out 29 stop mode recovery sources 30 using a GPIO port pin transition 30 SUB 203 subtract 203 subtract - extended addressing 203 subtract with carry 203